МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РЕСПУБЛИКИ КАЗАХСТАН

Некоммерческое акционерное общество

“Алматинский университет энергетики и связи”

О.Т. Шанаев

ЦИФРОВЫЕ СИСТЕМЫ. МОДЕЛИРОВАНИЕ

Учебное пособие

Алматы 2013

УДК 681.3.06

ББК 32.973.202 Я73

Ш20 Цифровые системы. Моделирование;

Учебное пособие / Шанаев О.Т. Алматы: АУЭС, 2013. – 82 с.

ISBN 978-601-7327-45-3

В первой и второй частях учебного пособия излагаются математические и структурные основы цифровых систем. Также описаны различные структурные принципы построения устройств памяти, применяемые в производстве соответствующих микросхем.

Изложению структуры микропроцессоров и основных структурных принципов построения микропроцессорных систем посвящена третья часть учебного пособия, где на примере микропроцессора Intel 8085 и соответствующей микропроцессорной системы, рассматриваются структурные компоненты и принципы организации работы микропроцессоров и микропроцессорных систем.

В четвертой части учебного пособия описываются различные программные структуры, составленные на основе применения разнообразных (по размеру и по способу адресации) команд и предназначенных для организации работы микропроцессорной системы на основе микропроцессора Intel 8085.

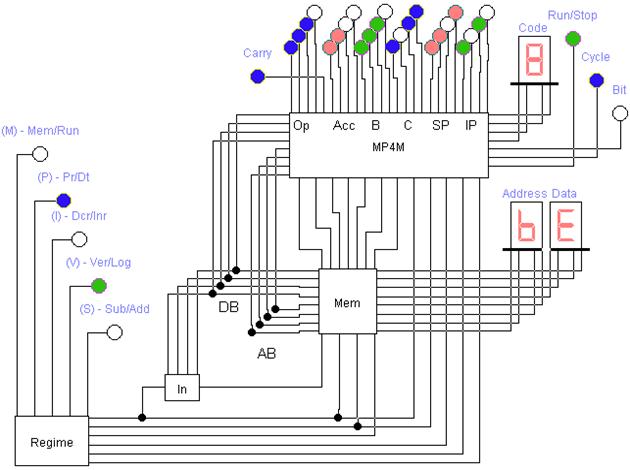

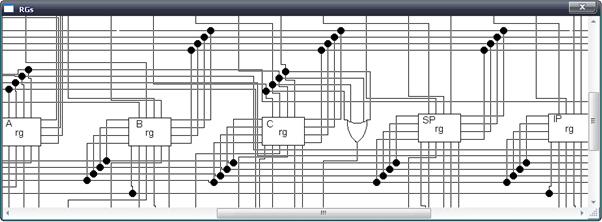

Пятый раздел учебного пособия посвящен рассмотрению возможностей практической реализации общих принципов построения микропроцессорной системы, на примере разработки модели такой системы, разработанной в программной среде схемотехнического моделирования Electronics Workbench, предназначенной для моделирования и анализа электрических схем.

Ил. 41, табл. 35, библиогр. 10 назв.

ББК 32.973.202 Я73

РЕЦЕНЗЕНТЫ:

АУЭС, д-р. физ-мат. наук, профессор С.Б. Бимурзаев

КазНТУ, канд. тех. наук, доцент, А.К. Шайхин

Печатается по плану издания Министерства образования и науки Республики Казахстан на 2012 г.

ISBN 978-601-7327-45-3

© НАО “Алматинский университет энергетики и связи”, 2013 г.

Введение

Известно, что управление разнообразными техническими средствами, применяемыми в различных областях производства и в быту, осуществляется на основе цифровой техники. Функционирование этих устройств в определенном порядке (т.е. в соответствии с определенным алгоритмом) реализуется путем измерения определенных параметров объекта (или технологического процесса), соответствующей обработки полученных данных и формирования управляющих сигналов, изменяющих состояния объекта в нужном направлении. Такие контрольно-измерительные и управляющие системы обобщенно называют цифровыми системами.

В традиционных цифровых системах, называемых системами с “жесткой логикой”, алгоритм обработки и хранения информации определяется схемотехникой системы, т.е. для перехода на другой алгоритм необходимо полностью перестроить всю систему, а это требует времени и расходов. Основным достоинством таких систем является их быстродействие, определяемое технологией изготовления ее составных элементов (например, микросхем).

В цифровых системах, называемых системами с “гибкой логикой”, изменение алгоритма работы осуществляется путем установки новой программы работы системы. Примером таких систем являются микропроцессорные системы (МПС), в число которых входит и компьютеры. “Универсальность” таких систем достигается за счет ее аппаратной избыточности, что, соответственно, отрицательно сказывается на скорости работы всей системы и удорожает ее.

При разработке сложных цифровых систем (в том числе и МПС) учитываются два взаимосвязанных и взаимообусловленных фактора: конструирование аппаратной части системы (hardware), обеспечивающей физическую реализацию решения поставленной задачи, и определение системы команд (software), позволяющего составить программу действий и взаимодействий функциональных компонентов системы по решению задачи. Следовательно, для получения наиболее полного знания о современных цифровых системах требуется освоение как принципов их аппаратного построения, так и принципов реализации различных программных структур.

В первой части учебного пособия излагаются математические основы цифровых систем, в частности, приводятся оригинальные методы кодовых преобразований, применяемые автором на практике. Во второй части описываются принципы построения и работы различных типов комбинационных и последовательностных устройств, составляющих структурную основу цифровых систем, и приводятся практические примеры их оригинального использования. Здесь же описаны различные структурные принципы построения устройств памяти, применяемые в производстве соответствующих микросхем.

Изложению структуры микропроцессоров и основных структурных принципов построения микропроцессорных систем посвящена третья часть учебного пособия, где на примере микропроцессора Intel 8085 и соответствующей микропроцессорной системы, рассматриваются внутренние составные компоненты, сигналы управления, система команд и общий порядок организации работы микропроцессоров и принципы построения микропроцессорных систем.

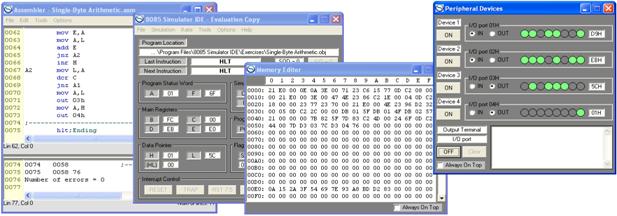

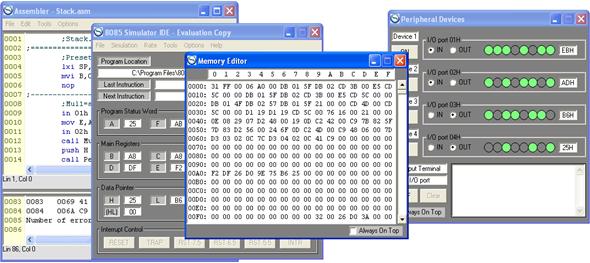

В четвертой части учебного пособия описываются различные программные структуры, составленные на основе применения разнообразных (по размеру и по способу адресации) команд и предназначенных для организации работы микропроцессорной системы на основе микропроцессора Intel 8085. Также здесь рассматриваются воможности применения соответствующего программного симулятора (8085 Simulator IDE) и его инструментального набора для проверки работоспособности предлагаемых программ.

Пятый раздел учебного пособия посвящен рассмотрению возможностей практической реализации общих принципов построения микропроцессорной системы, на примере разработки модели такой системы, разработанной в программной среде схемотехнического моделирования Electronics Workbench, предназначенной для моделирования и анализа электрических схем.

Данное учебное пособие составлено на основе многолетней педагогической деятельности автора и предназначено студентам, обучающимся по специальности 5В070400 – Вычислительная техника и программное обеспечение.

1 Математические основы цифровых систем

1.1 Двоичные коды

Работа цифровых систем осуществляется посредством обработки логической информации или физических величин, представленных двоичными кодами. Другими словами, арифметические и логические операции, выполняемые в цифровых системах, осуществляются в двоичной системе счисления.

Двоичная система счисления, применяемая в цифровых системах, относится к позиционным системам счисления. Следовательно, как для представления чисел в двоичной системе счисления, так и при выполнении арифметических операций над числами, представленными в этой системе счисления, применяются соответствующие принципы, привычной нам, десятичной системы счисления, которая также относится к позиционным системам счисления. Поэтому при дальнейших пояснениях относительно двоичной системы счисления, будем исходить из аналогичных положений, применяемых в десятичной системе счисления.

В десятичной системе счисления для представления любых чисел используются десять символов (0 … 9), поэтому она и называется десятичной и основанием этой системы является число 10. Каждому разряду числа, представленного в позиционной системе счисления, назначается определенный вес, выражаемый степенью (соответствующей номеру разряда) основания системы (при этом необходимо иметь в виду, что нумерация разрядов начинается с нуля). Следовательно, вес самого младшего (нулевого) разряда десятичного числа – 1 (100), вес следующего (первого) разряда – 10 (101), вес второго разряда – 10 (102) и т.д. Значение символа, размещенного в определенном разряде числа, выражает количество повторения веса этого разряда в значении представленного числа. Поясним сказанное следующим примером:

![]() .

.

Итак, в составе представленного числа содержатся 7 единиц, 5 сотен, 3 тысячных, а десятков нет (0).

В двоичной системе счисления для представления числа используются два символа (0 и 1) и соответственно, вес разряда выражается степенью двойки. В этом случае вес самого младшего (нулевого) разряда десятичного числа – 1 (20), вес следующего (первого) разряда – 2 (21), вес второго разряда – 4 (22) и т.д. Значение символа (0 или 1), размещенного в определенном разряде числа, выражает учитываемость веса этого разряда в значении представленного числа. Сказанное поясняет следующий пример:

![]() .

.

В составе этого числа содержатся единица, двойка и восьмерка (1), а четверки нет (0).

1.1.1 Преобразования десятичных чисел.

Для обработки в цифровой системе числа, представленного в привычной нам десятичной системе счисления, необходимо представить его в виде соответствующего двоичного кода. Представим предлагаемую в соответствующей литературе методику такого преобразования. По этой методике преобразуемое десятичное число и последующие частные последовательно делятся на два (т.е. на основание новой системы счисления) до получения нулевого значения частного. Остатки, полученные в результате последовательных делений и записанные в порядке, обратном их получению, дают двоичный код искомого числа (данную методику определения двоичного кода десятичного числа назовем методом деления). В качестве примера покажем процесс получения двоичного кода, соответствующего десятичному числу 75:

7510 = 10010112.

Разумется, представленным способом можно получить двоичный код любого десятичного числа. Но автор не считает этот способ легко реализуемым и единственным способом: во-первых, последовательно осуществляемые операции деления занимают достаточно продолжительное время (например, попробуйте получить этим способом двоичный код десятичного числа 1000); во-вторых, из-за продолжительности последовательно выполняемых операций деления вероятность совершения ошибок тоже увеличивается. С целью избавления от перечисленных недостатков представленного способа, автор предлагает свои способы получения двоичного кода десятичного числа, используемые им на практике.

Опишем порядок получения двоичного кода десятичного числа по первому способу (в качестве иллюстративного примера используем то же самое число 75):

- сначала определяется (и записывается) значение числа, выражаемого максимальной степенью двойки (степени основания системы счисления) в пределах искомого десятичного числа (6410 = 26 = 10000002, это число, для удобства дальнейшего пояснения, назовем кодом первого шага);

- на следующем шаге определенное на первом шаге число вычитается от исходного преобраземого числа (75 – 64 = 11) и относительно полученного результата вычитания выполняется действие, аналогичное действию первого шага, т.е. определяется значение числа, выражаемого максимальной степенью двойки в пределах результата вычитания (810 = 23 = 10002, это число назовем кодом второго шага);

- аналогично продолжая описанные действия, достигаем значения числа, код которого нам известен (11 – 8 = 3, 310 = 112);

- складывая между собой коды различных шагов, получаем двоичный код искомого десятичного числа:

.

.

Действия, выполняемые на каждом шаге при описанном способе получения двоичного кода десятичного числа (назовем этот способ методом сложения), а именно: запись кодов, выражаемых степенью двойки (1 и несколько нулей, число которых определяется значением степени двойки) и их поразрядное сложение (сложение нескольких нулей и одной единицы в каждом разряде) являются легко выполняемыми операциями, что и характеризует достоинство данного метода.

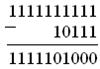

В некоторых случаях может оказаться удобным применение другого способа получения двоичного кода десятичного числа. Например, определение двоичного кода числа 1000 описанным выше способом (методом сложения) растягивается на шесть шагов (512 + 256 + 128 + 64 + 32 + 8). Искомо число ближе к 1024 (210), чем к 512, поэтому возникает мысль, что в данном случае было бы легче вычесть код числа 24 из кода числа 1024. Но операция вычитания, выполняемая между соответствующими двоичными кодами этих чисел (10000000000 и 11000 соответственно), не относится к легко реализуемым операциям (из-за необходимости применения поразрядных заемов). Но в то же время заметим, что двоичный код числа 1023 представляется через 10 единиц (1111111111) и вычитание из него 10111 (код числа 23) весьма легко выполняется:

.

.

Данный способ получения двоичного кода десятичного числа (назовем этот способ методом вычитания) удобно применять в случаях, когда значение искомого десятичного числа немного меньше ближайшего числа, выражаемого степенью двойки. Получение двоичного кода десятичного числа методом вычитания осуществляется в следующем порядке:

- сначала определяется значение числа, выражаемого степенью двойки и немного большего искомого десятичного числа (назовем это число ближайшим числом), и записывается двоичный код числа на единицу меньшего этого числа (назовем это число первым приближением), который представляется несколькими единицами, число которых определяется степенью двойки в ближайшем числе;

- вычисляется разница между выбранным на первом шаге числом (в качестве первого приближения) и искомым числом. Далее путем применения одного из предложенных способов (метода сложения или вычитания) определяется код полученного результата (разницы);

- и, наконец, путем вычитания кода разницы из кода числа, принятого в качестве первого приближения, определяется двоичный код искомого десятичного числа.

Обратное преобразование, т.е. определение десятичного значения по представленному его двоичному коду, осуществляется путем сложения весов значимых разрядов (т.е. с единичными значениями) этого кода:

1101100012 = 28 + 27 + 25 + 24 + 20 = 256 + 128 + 32 + 16 + 1 = 43310.

Цифровые системы работают с двоичными числами, но для пользователя работа (например, при определении машинного кода программы, первоначально составленного на языке Ассемблер, или для представления констант, необходимых для работы программы) с этими числами является весьма затруднительной задачей. В таких случаях используется шестнадцатеричная система счисления. В соответствии с названием системы, для представления чисел в этой системе счисления используются 16 символов (1 … 9, A, B, C, D, E, F).

Для получения шестадцатеричного кода десятичного числа, конечно, можно воспользоваться методом деления, описанным выше (только путем деления на 16). Но имеется более легкий способ решения этой задачи:

- сначала определяется двоичный код десятичного случая;

- затем символы в полученном двоичном группируются по четыре, начиная с младших разрядов;

- последовательная записью шестнадцатеричных символов, соответствующих кодам каждой группы, определяется шестадцатеричный код искомого десятичного числа.

Описанную методику иллюстрирует следующий пример:

![]() .

.

1.1.2 Арифметические операции над двоичными числами.

Операция сложения двоичных чисел осуществляется аналогично тому, как это осуществляется в десятичной системе счисления:

.

.

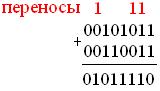

Операции вычитания между двоичными числами осуществляются путем сложения этих чисел в дополнительном коде. Дополнительный код положительного числа совпадает с его прямым кодом, а отрицательного числа получается путем инвертирования значений разрядов искомого двоичного числа и добавления к нему единицы. При этом значение последнего разряда числа, представленного в дополнительном коде, определяет знак числа: 0 – положительный знак, 1 – отрицательный знак. Процесс выполнения операции вычитания проиллюстрируем двумя примерами:

.

.

Операции умножения в цифровых системах выполняются программным путем или с помощью специального устройства (аппаратного умножителя). Относительно операции деления можно сказать то же самое.

1.2 Логические функции

1.2.1 Основные функции.

Значения сигналов на входах и выходах цифровых (логических) устройств характеризуются двумя уровнями напряжений, называемых лог.0 и лог.1. Эта особенность логических устройств позволяет использовать для их проектирования принципы алгебры логики (или алгебры Буля).

Работа цифровых устройств описывается соответствующими логическими функциями. Любую по сложности логическую функцию можно выразить с помощью трех логических функций, называемых основными логическими функциями, это – функции НЕ, ИЛИ, И. Логику их работы можно описать в табличном виде (таблицей истинности) или с помощью соответствующих логических выражений.

Одноаргументная функция НЕ инвертирует

значение ее аргумента (см. таблицу 1.1) и часто называется инверсией (inversion

– отрицание). Эта функция выражается выражением Y=![]() .

.

Т а б л и ц а 1.1

|

Х |

|

|

0 |

1 |

|

1 |

0 |

![]()

Многоаргументная функция ИЛИ выдает 0 только в

случае, когда все аргументы принимают значение 0, а в остальных случаях (т.е. в

случаях, когда хотя бы один из аргументов принимает значение 1) (см. таблицу 1.2).

Эта функция называется дизъюнкцией (disjunction) или логическим сложением (logical

addition) и описывается выражением Y=Х1![]() Х0.

Х0.

Т а б л и ц а 1.2

|

Х1 |

Х0 |

Х1 |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

![]()

Многоаргументная функция И выдает

1 только в случае, когда все аргументы принимают значение 1, а в остальных случаях (т.е. в случаях, когда хотя бы один из

аргументов принимает значение 0 (см. таблицу 1.3). Эта функция называется конъюнкцией (conjunction)

или логическим умножением (logical multiplication) и описывается выражением Y= Х1![]() Х0 (или Х1Х0).

Х0 (или Х1Х0).

Т а б л и ц а 1.3

|

Х1 |

Х0 |

Х1Х0 |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

Ввиду того что с помощью функций НЕ, ИЛИ, И можно описать любую сложную функцию, они составляют функционально полный набор (core set).

1.2.2 Универсальные функции.

Кроме функций НЕ, ИЛИ, И, совместно

составляющих функционально полный набор, существуют две функции, каждая из

которых также составляет функционально полный набор, это – функции ИЛИ-НЕ и

И-НЕ. Функцию ИЛИ-НЕ также называют функцией Пирса, а функцию И-НЕ – функцией

Шеффера. Они описываются выражениями ![]() и

и ![]() соооответственно, и логика их работы

представлена в таблице 1.4.

соооответственно, и логика их работы

представлена в таблице 1.4.

Т а б л и ц а 1.4

|

Х1 |

Х0 |

|

|

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1.2.3 Функции эквивалентности и неэквивалентности.

Опишем еще две функции, предназначенные для

использования в специальных случаях, это – функция эквивалентности (или

арифметического сложения) и функция неэквивалентности, инверсная относительно

первой функции. Они описываются выражениями ![]() и

и ![]() соооответственно, и логика их работы

представлена в таблице 1.5.

соооответственно, и логика их работы

представлена в таблице 1.5.

Т а б л и ц а 1.5

|

Х1 |

Х0 |

|

|

|

0 |

0 |

0 |

1 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

1.3 Законы и соотношения алгебры логики

В процессе разработки схем цифровых устройств возникает необходимость преобразования логических функций (например, с целью их минимизации), описывающих эти устройства. Такие преобразования осуществляются на основе законов и соотношений алгебры логики (см. таблицу 1.6).

Т а б л и ц а 1.6

|

Законы |

|

|

Коммутативный (commutativity) закон |

|

|

Х1 |

Х1Х0 = Х0Х1 |

|

Ассоциативный (associativity) закон |

|

|

Х2 |

Х2 (Х1Х0) = (Х2Х1)Х0 |

|

Дистрибутивный (distributivity) закон |

|

|

Х2Х1 |

(Х2 |

|

Закон де Моргана |

|

|

|

|

|

Соотношения |

|

|

X |

X |

|

X |

X |

|

X |

X |

|

X |

X |

|

X1 |

X1(X1 |

|

X1 |

X1( |

|

|

|

Эти законы и соотношения симметричны, т.е. они имеют как дизъюнктивные, так и конъюнктивные формы. Некоторые из этих законов подобны соответствующим законам классической алгебры, поэтому их достоверность не вызывает сомнений. Что касается законов и соотношений, не типичных для классической алгебры, то в их достоверности можно убедиться путем подстановки различных значений (0 и 1) аргументов в соответствующие выражения.

1.4 Сложные функции

1.4.1 Формы представления сложных функций.

Функция устройства, в большинстве случаев, задается в табличном виде. Разумеется, она может быть представлена и в виде соответствующего словесного описания логики работы устройства, в таком случае на основе словесного описания устройства составляется соответствующая таблица. Итак, считаем, что логика работы устройства задана в табличном виде. Опишем порядок составления логического выражения на примере устройства, логика работы которого задана таблицей 1.7.

Т а б л и ц а 1.7

|

X2 |

X1 |

X0 |

Y |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

Имеются два способа составления логического выражения таблично заданной функции: в виде дизъюнкции конъюнкций и в виде конъюнкции дизъюнкций. Соответствующие формы записи логического выражения называются дизъюнктивной и конъюнктивной формами. Будем описывать их параллельно.

Составление логического выражения по первому способу, т.е. в дизъюнктивной форме, осуществляется в следующем порядке:

- для наборов аргументов, где функция (Y) принимает единичное значение, записываются соответствующие конънкции, т.е соответствующие логические произведения аргументов;

- при записи соответствующих конънкций (они называются конъюнктивными термами) аргументы с единичными значениями представляются в прямом виде, а аргументы с нулевыми значениями – в инверсном виде;

- записанные конъюнктивные термы объединяются дизъюнкцией.

Таким образом, получаем следующее логическое выражение таблично заданной функции:

|

|

(1.1) |

Составление логического выражения по второму способу, т.е. в конъюнктивной форме, осуществляется в следующем порядке:

- для наборов аргументов, где функция (Y) принимает нулевое значение, записываются соответствующие дизънкции, т.е соответствующие логические суммы аргументов;

- при записи соответствующих дизънкций (они называются дизъюнктивными термами), аргументы с нулевыми значениями представляются в прямом виде, а аргументы с единичными значениями – в инверсном виде;

- записанные дизъюнктивные термы объединяются конъюнкцией.

Составленное этим способом логическое выражение устройства выглядит следующим образом:

|

|

(1.2) |

1.4.2 Минимизация логических выражений.

По любому из полученных выше выражений можно построить схему устройства, но ввиду сложности выражений, схемы также сложные (точнее, объемные). Поэтому желательно их минимизировать. Минимизацию логического выражения можно осуществить двумя способами: методом прямого преобразования и с помощью карты Карно.

Прямое преобразование логического выражения осуществляется путем непосредственного применения законов и соотношений алгебры логики для объединения соседних конъюнктивных (дизъюнктивных) термов. К соседним термам относятся термы, отличающиеся значениями только одного аргумента.

Ниже представлены все осуществленные преобразования для выражений (1.1) и (1.2) соответственно.

Для выражения (1.1):

![]()

![]()

![]()

![]()

Для выражения (1.2):

![]()

![]()

![]()

Опишем минимизацию логической функции с помощью карты Карно. Карта Карно – особый способ табличного представления функции, по которой весьма удобно (и наглядно) осуществляется минимизация логической функции. Карта Карно, составленная для предсталенной функции, представлена на рисунке 1.1.

|

|

X1 |

|

||

|

X2 |

0 6 |

1 7 |

1 5 |

1 4 |

|

|

0 2 |

1 3 |

1 1 |

0 0 |

|

|

|

X0 |

|

|

Рисунок 1.1

Соседние термы на карте Карно разполагаются, в буквальном смысле, по соседству: в представленной карте видно, что 1-, 3-, 5-, 7-ячейки можно объединить, в результате которого остается только X0, а также видно, что 4-ячейку можно объединить только с 5-ячейкой. На рисунке 1.2 представлен вид карты Карно для функции со четырьмя аргументами.

|

|

X2 |

|

|

||

|

X3 |

12 |

13 |

9 |

8 |

|

|

14 |

15 |

11 |

10 |

X1

|

|

|

|

6 |

7 |

3 |

2 |

|

|

4 |

5 |

1 |

0 |

|

|

|

|

|

X0 |

|

|

|

Рисунок 1.2

В составе программы программы Electronics Workbench имеется специальный преобразователь (Logic Converter), который позволяет получить логическое выражение таблично заданной функции в полной и минимизированной форме (см.рисунок 1.3).

Рисунок 1.3

2 Структурные основы цифровых систем

Устройства, входящие в состав цифровых систем, делятся на два типа, называемые комбинационными и последовательностными. К комбинационным устройствам относятся устройства, выходной сигнал (или выходные сигналы) которых определяется текущими значениями их входных сигналов, а выходной сигнал (или выходные сигналы) последовательностных устройств определяется не только их входными сигналами, но и зависит от предыдущего состояния устройства, т.е они обладают свойством памяти.

2.1 Логические элементы

Основу построения комбинационных (в принципе, и последовательностных) устройств составляют логические элементы.

Логические элементы – устройства, предназначенные для реализации логических функций. На рисунке 2.1 представлены условно-графические обозначения логических элементов, реализующих рассмотренные ранее логические функции.

|

NOT |

OR |

AND |

NOR |

NAND |

XOR |

XNOR |

|

|

|

|

|

|

|

|

Рисунок 2.1

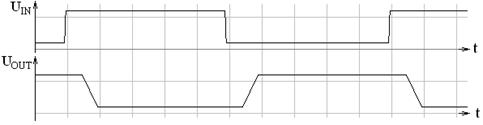

Логические элементы характеризуются своим быстродействием, которое характеризует быстроту изменения его состояния. На рисунке 2.2 представлена временная диаграмма процесса прохождения сигнала прямоугольной формы через элемент НЕ.

Рисунок 2.2

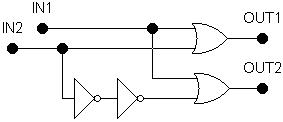

Здесь видна определенная задержка изменения выходного сигнала относительно изменения входного сигнала. По измерениям, проведенным в системе моделирования Electronics Workbench, длительность этой задержки составляет порядка 10 ns, что соответствует аналогичному параметру элементов, изготовленных по технолргии ТТЛ. На устройства, работающие со статическими сигналами, такая задержка не оказывает влияния, но в некоторых случаях (например, в последовательностных устройствах), задержка прохождения сигнала может оказать серьезное влияние на работу устройства и его необходимо учитывать. С целью иллюстрации действия задержки рассмотрим логическую сумму двух сигналов, параллельно поданных на входы двух элементов ИЛИ (см. рисунок 2.3). Как показано на схеме, один из сигналов подается на вход второго элемента через два элемента НЕ, что обеспечивает соответствующую задержку.

Рисунок 2.3

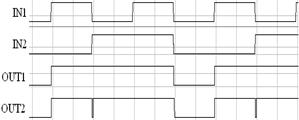

В идеальном случае, т.е. при отсутствии задержек на элементах НЕ, сигналы на выходах (OUT1 и OUT2) соответствующих элементов были бы одинаковы (см. рисунок 2.4, a). Эта диаграмма получена с помощью логического анализатора (Logic Analyzer) из состава системы моделирования Electronics Workbench, которому свойственна некоторая инерционность.

|

|

|

|

a |

b |

Рисунок 2.4

На диаграмме, полученной с помощью чувствительного осциллографа (см. рисунок 2.4, b), видны паразитные импульсы, возникшие из-за влияния задержки сигнала (продолжительностью 20 ns) на элементах НЕ. Появление таких паразитных импульсов в составе выходного сигнала может отрицательно повлиять на работу устройства, подключаемого на этот выход, из-за чего возникает необходимость их исключения.

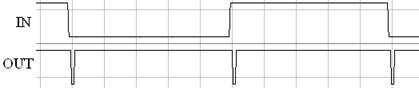

Задержку сигнала на элементах можно использовать и с пользой. Например, для формирования узкого сигнала (продолжительностью 10 ns) от каждого нажатия отдельной клавишы (изменения ее состояния) клавиатуры, можно использовать схему на рисунке 2.5.

|

|

|

|

a |

b |

Рисунок 2.5

2.2 Комбинационные устройства

Разработка схемы комбинационного устройства осуществляется поэтапно, т.е. путем последовательного выполнения следующих действий:

- на основе словесного пояснения к разрабатываемому устройству составляется соответствующая таблица истинности;

- на основе табличных данных записывается соответствующее логическое выражение;

- в случае необходимости (и возможности) полученное логическое выражение минимизируется;

- производится преобразование полученного минимизированного выражения к виду, составленному на основе запланированного базовового набора элементов (core set);

- по конечному логическому выражению осуществляется построение схемы устройства.

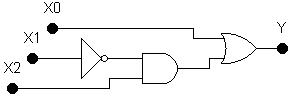

Первые три этапа приведенного порядка разработки комбинационного устройства были рассмотрены ранее (в разделе 1.4), остается только построение схемы на основе определенного базового набора элементов. Cхема устройства (заданного таблицей 1.7), построенная на основе элементов НЕ, И, ИЛИ, представлена на рисунке 2.6, a.

|

|

|

|

a |

b |

Рисунок 2.6

На практике часто возникает необходимость построения схемы устройства на основе однотипных элементов (например, на основе элементов И-НЕ). В таких случаях производится соответствующее преобразование логического выражения (4-этап) по закону де Моргана:

![]()

Соответствующая этому выражению схема устройства представлена на рисунке 2.6, b.

2.3 Типовые комбинационные узлы цифровых систем

Разработка цифровых систем, как правило, осуществляется на основе отдельных типовых функциональных узлов. Функциональные узлы цифровых систем, в общем виде, делятся на комбинационные и последовательностные устройства. В этом разделе будут рассмотрены структурные принципы построения и порядок работы типовых комбинационных узлов (шифратор, дешифратор, мультиплексор, демультиплексор, сумматор) цифровых систем.

2.3.1 Шифраторы.

Шифратор (Coder) – устройство, формирующее двоичный код, соответствующий поступившему сигналу (т.е. соответствующий входу, на который поступил сигнал), т.е. он преобразует унитарный код в позиционный код. В качестве примера рассмотрим порядок построения схемы восьмивходового (X7 … X0) шифратора. В соответствии с числом входов (8), он должен формировать трехразрядный код (C2 … C0, CODE) и сигнал квитирования (O, OUT), посредством которого осуществляется запись сформированного кода в буфер памяти. Организация работы отдельных функциональных узлов цифровой системы, как правило, осушествляется в мультиплексном режиме (т.е. по очереди) с помощью соответствующих сигналов инициализации. Соответствующий вход сигнала инициализации (I, Initialization) должен быть и в нашем шифраторе. Необходимо учесть, что в качестве активизирующего уровня сигнала инициализации (также и квитирования), как правило, принимают нулевой уровень. Для практической реализации шифратора желательно, чтобы активизирующий уровень сигналов, поступающих на информационные входы шифратора, также был нулевым.

Приведенное словесное описание шифратора предоставляет достаточно сведений для составления таблицы истинности (см. таблицу 2.1) этого устройства.

Т а б л и ц а 2.1

|

I |

Xi |

C2 |

C1 |

C0 |

O |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

|

2 |

0 |

1 |

0 |

0 |

|

|

3 |

0 |

1 |

1 |

0 |

|

|

4 |

1 |

0 |

0 |

0 |

|

|

5 |

1 |

0 |

1 |

0 |

|

|

6 |

1 |

1 |

0 |

0 |

|

|

7 |

1 |

1 |

1 |

0 |

|

|

1 |

* |

0 |

0 |

0 |

1 |

На основе табличных данных можно написать логические выражения для соответствующих выходов шифратора:

![]() ;

;

![]() ;

;

![]() ;

;

![]()

![]() .

.

Эти выражения сначала были написаны в дизъюнктивной форме, а затем преобразованы ( по закону де Моргана) к виду, предназначенному для построения схемы с помощью элементов И-НЕ. Одним из преимуществ построения схем на основе элементов И-НЕ является то, что они обладают более высоким быстродействием (это определяется их внутренней структурой) по сравнению с другими типами элементов. На рисунке 2.7, a представлена схема шифратора, построенная на основе полученных логических выражений.

Шифраторы на схемах цифровых систем, в состав которых они входят, изображаются условно-графическим обозначением (см. рисунок 2.7, b). На рисунке 2.7, c приведен результат оформления построенной ранее схемы шифратора в виде подсхемы (Subcircuit), созданной с использованием возможностей программы Electronics Workbench (выводы этой подсхемы размещены в соответствии с их расположением в разразработанной схеме).

![]()

|

a |

b |

c |

Рисунок 2.7

Разработанная выше схема шифратора обладает некоторым недостатком, который заключается в том, что в случае наличия двух информационных сигналов формируется код, не относящийся ни к одному из поступивших сигналов. С целью исключения таких случаев, микросхемы шифраторов (например, микросхема 74148) выпускаются на производстве в виде приоритетных шифраторов, т.е. они формируют код, соответствующий старшему по приоритету сигналу.

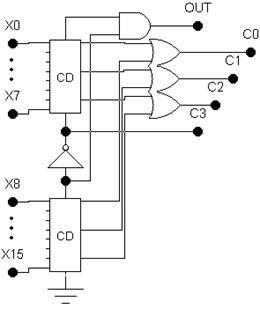

В некоторых случаях размерность (число входов) выбранной микросхемы шифратора может не соответствовать поставленным требованиям, что вызывает необходимость расширения ее размерности. Например, микросхема 74148 выполняет функцию восьмивходового шифратора. На основе таких микросхем (или созданных ранее подсхем) можно построить шифратор с удвоенным числом входов (см. рисунок 2.8).

Рисунок 2.8

2.3.2 Дешифраторы.

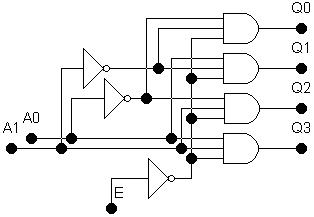

Дешифратор (Decoder) – устройство, формирующее сигнал на выходе, соответствующем поступившему входному коду сигналу, т.е. он преобразует позиционный код в унитарный код. В качестве примера рассмотрим порядок построения схемы дешифратора со четырьмя выходами (Q3 … Q0), формирующего на этих выходах инверсные сигналы. В соответствии с числом выходов (4), к его входам должен подаваться двухразрядный код (A1A0). Активизирующий уровень сигнала инициализации (E, Enable) примем нулевым.

По приведенному словесному описанию дешифратора построим таблицу истинности (см. таблицу 2.2) этого устройства.

Т а б л и ц а 2.2

|

E |

A1 |

A0 |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

1 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

1 |

|

|

1 |

0 |

1 |

0 |

1 |

1 |

|

|

1 |

1 |

0 |

1 |

1 |

1 |

|

|

1 |

* |

* |

1 |

1 |

1 |

1 |

Логические выражения для соответствующих выходов дешифратора, определенные на основе табличных данных, выглядят следующим образом:

![]() ;

;

![]() ;

;

![]() ;

;

![]() .

.

Схема дешифратора, построенная по этим выражениям, приведена на рисунке 2.9, a.

![]()

|

a |

b |

c |

Рисунок 2.9

Дешифраторы на схемах цифровых систем, в состав которых они входят, изображаются условно-графическим обозначением (см. рисунок 2.9, b). На рисунке 2.9, c приведен результат оформления построенной выше схемы дешифратора в виде подсхемы в программе Electronics Workbench.

Если обратимся к логическому выражению (1.1), описывающему состояния выходного сигнала рассмотренного в разделе 1.4 комбинационного устройства, можно заметить, что конъюнктивные термы, входящие в его состав, соответствуют логическим выражениям выходов восьмивходового дешифратора с прямыми выходами, а само выражение, фактически, определяет логику работу соответствующего дешифратора Следовательно, объединяя соответствующие выходы дешифратора с прямыми выходами с помощью элемента ИЛИ, можно реализовать это устройство. В случае использования дешифратора с инверсными выходами (как в нашем случае) необходимо преобразовать выражение (1.1) с помощью закона де Моргана:

![]() .

.

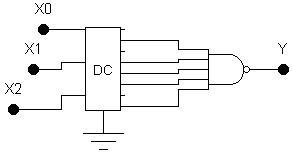

По полученному в результате преобразования выражению нетрудно догадаться, что в данном случае для объединения соответствующих выходов дешифратора необходимо использовать элемент И-НЕ (см. рисунок 2.10).

Реализация схемы комбинационного устройства с помощью дешифратора – весьма удобный способ: во-первых, нет необходимости в минимизации логического выражения (точнее говоря, и самого выражения тоже не нужно, т.к. все необходимые соединения можно выяснить и по таблице), во-вторых, на основе одного единственного дешифратора можно реализовать несколько функций параллельно.

Рисунок 2.10

2.3.3 Мультиплексоры.

Мультиплексор (Multiplexer) – устройство, направляющее один из информационных сигналов к устройству, подключенному к его выходу, в зависимости от поступившего адресного кода. Соответственно этому определению, различают две группы входов мультиплексора: информационные и адресные; разумеется, должен быть еще вход сигнала инициализации.

Схема мультиплексора, реализованная с помощью дешифратора, и его условно-графическое обозначение приведены на рисунке 2.11.

|

|

|

|

a |

b |

Рисунок 2.11

Соединяя параллельно несколько мультиплексоров, можно построить так называемый канальный мультиплексор, который отправляет один из информационных слов на выходной канал.

На основе мультиплексоров также можно реализовать работу комбинационного устройства. Рассмотрим два способа реализации этого.

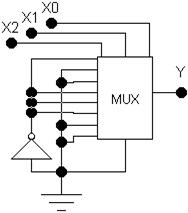

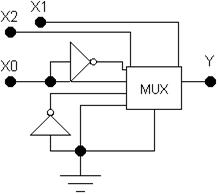

Первый способ применяется для реализации функции с помощью мультиплексора, количество адресных входов которого совпадает с числом аргументов реализуемой функции. В этом случае информационные входы мультиплексора устанавливаются в состояния, соответствующие значениям функции при соответствующих наборах аргументов, а на его адресные входы подаются сигналы, соответствующие значениям аргументов. Реализация функции этим способом, на основе мультиплексора с восемью информационными входами, представлена на рисунке 2.12, a. Заметим, что информационные входы использованной здесь подсхемы мультиплексора выведены на правую сторону, а его адресные входы размещены сверху.

Т а б л и ц а 2.3

|

X2 |

X1 |

X0 |

Y |

|

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

0 |

|

|

|

|

a |

b |

Рисунок 2.12

Второй способ применяется для реализации функции с помощью мультиплексора, количество адресных входов которого меньше числа аргументов реализуемой функции. В этом случае на адресные входы мультиплексора подаются сигналы, соответствующие значениям части аргументов, а остальные используются для настройки информационных входов мультиплексора. Реализация функции этим способом, на основе мультиплексора со четырьмя информационными входами, представлена на рисунке 2.12, b.

2.3.4 Демультиплексоры.

Демультиплексор (Demultiplexer) – устройство, направляющее информационный сигнал к одному из устройств, подключенных к его выходам, в зависимости от поступившего адресного кода.

Схема демультиплексора, реализованная с помощью дешифратора, и его условно-грфическое обозначение приведены на рисунке 2.13.

|

|

|

|

a |

b |

Рисунок 2.13

2.3.5 Сумматоры.

Сумматор – устройство, реализующее выполнение операции арифметического сложения двух чисел. Сложение многоразрядных чисел осуществляется с помощью соответствующего числа одноразрядных сумматоров. Поэтому сначала рассмотрим принципы построения одноразрядных сумматоров.

В процессе сложения двух одноразрядных чисел должны быть получены результат их суммирования (S, Sum) и перенос (C, Carry) на следующий разряд, следовательно, работу одноразрядного сумматора можно представить таблицей 2.4.

Т а б л и ц а 2.4

|

A |

B |

S |

C |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

Логические выражения для соответствующих выходов сумматора, определенные на основе табличных данных, выглядят следующим образом:

![]() ;

; ![]() .

.

Схема сумматора, построенная по этим выражениям, и соответствующая подсхема, подготовленная в программе Electronics Workbench, представлены на рисунке 2.14, a.

|

|

|

|

|

|

a |

b |

||

Рисунок 2.14

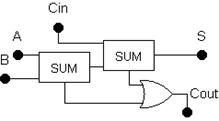

Этот сумматор пригоден только для суммирования значений первых разрядов многоразрядных чисел (поэтому он называется полусумматором), а для суммирования значений остальных разрядов чисел используются полные одноразрядные сумматоры, у которых имеется третий вход, куда поступает перенос из предыдущего разряда. Схема такого сумматора, реализованная на основе полусумматоров, и соответствующая подсхема представлены на рисунке 2.14, b.

Схема четырехразрядного сумматора, реализованная на основе одноразрядных сумматоров, соответствующая подсхема и условно-графическое обозначение представлены на рисунке 2.15.

|

|

|

|

|

a |

b |

c |

Рисунок 2.15

2.4 Последовательностные устройства

Как указано в приведенном выше определении последовательностных устройств, к ним относятся устройства, обладающие памятью, т.е. устройства со способностью сохранять предыдущее состояние. Поэтому сначала ознакомимся с разновидностями элементов памяти (триггеров) и принципами их построения и работы.

2.4.1 Триггеры.

Триггеры – устройства с двумя устойчивыми состояниями, предназначенные для хранения значений одноразрядных чисел. Одно из их состояний соответствует состоянию лог.1, а другое – лог.0. Как правило, триггеры снабжаются двумя выходами, один из которых называется прямым выходом, а другой – инверсным. Состояние триигера определяется состоянием его прямого выхода, т.е. уровнем сигнала на этом выходе.

В зависимости от порядка осуществления записи триггеры делятся на асинхронные и синхронные.

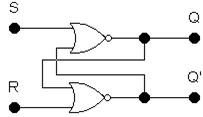

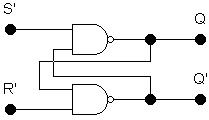

Изменение состояний асинхронных триггеров определяется изменениями информационных сигналов, подаваемых на их входы. Асинхронные RS-триггеры можно реализовать на основе элементов ИЛИ-НЕ или И-НЕ. Схема асинхронного RS-триггера, реализованная на основе элементов ИЛИ-НЕ, приведена на рисунке 2.16, a.

|

|

|

|

a |

b |

Рисунок 2.16

Работу устройства рассмотрим в порядке записи данных в таблице 2.5.

Т а б л и ц а 2.5

|

|

R |

S |

Q |

Q’ |

|

1 |

0 |

0 |

? |

? |

|

2 |

1 |

0 |

1 |

|

|

3 |

0 |

1 |

1 |

|

|

4 |

1 |

1 |

0 |

|

|

5 |

0 |

1 |

0 |

|

|

6 |

1 |

1 |

0 |

0 |

|

7 |

0 |

0 |

??? |

??? |

На первой строке таблицы: R = 0, S = 0; на одном из входов обоих элементов – лог.0, а уровни сигналов на входах обратной связи неизвестны, следовательно неизвестны уровни сигналов на выходах (Q и Q’).

На второй строке: R = 1, S = 0; ввиду того, что на одном из входов верхнего элемента – лог.1, и в соответствии с логикой работы этого элемента, на его выходе (Q), а также на верхнем входе нижнего элемента, будет лог.0, в результате чего на выходе нижнего элемента (Q’) будет лог.1; Итак, триггер устанавливается в состояние лог.0.

На третьей строке: R = 0, S = 0; изменение сигнала на входе R на 0 не повлияет на состояние триггера, так как уровни сигналов на остальных входах элементов не изменились, следовательно, триггер остается в предыдущем состоянии.

На четвертой строке: R = 0, S = 1; ввиду того, что на одном из входов нижнего элемента – лог.1, и в соответствии с логикой работы этого элемента, на его выходе (Q’), а также на нижнем входе верхнего элемента, будет лог.0, в результате чего на выходе верхнего элемента (Q) будет лог.1; Итак, триггер устанавливается в состояние лог.1.

На пятой строке: R = 0, S = 0; изменение сигнала на входе S на 0 не повлияет на состояние триггера, так как уровни сигналов на остальных входах элементов не изменились, следовательно, триггер остается в предыдущем состоянии.

Из рассмотренных случаев можно сделать следующий вывод: случай подачи R = 1, S = 0 соответствует записи в триггер нуля (установки его в состояние лог.0); случай R = 0, S = 1 – записи 1 (установки его в состояние лог.1); а случай R = 0, S = 0 – режиму хранения триггера.

В случае подачи на входы триггера R = 1, S = 1 (шестая строка), на выходах обоих элементов будет лог.0, и когда триггер переводится в режим хранения (седьмая строка), неизвестно, в какое состояние он установится, это – случайный процесс. Следовательно, необходимо исключить такой случай; поэтому данный случай называется запрещенным режимом триггера.

Итак, рабочие режимы рассмотренного триггера кратко можно представить в виде таблицы 2.6.

Т а б л и ц а 2.6

|

R |

S |

Q |

Q’ |

Режимы работы |

|

0 |

0 |

Q0 |

Q0’ |

Режим хранения |

|

0 |

1 |

1 |

0 |

Режим записи ‘1’ |

|

1 |

0 |

0 |

1 |

Режим записи ‘0’ |

|

1 |

1 |

– |

– |

Запрещенный режим |

Ввиду того что режимы записи рассмотренного триггера реализуются единичным уровнем соответствующего сигнала (S – Set, R – Reset), такой триггер называется триггером с прямыми входами. Его условно-графическое обозначение приведено на рисунке 2.16, b.

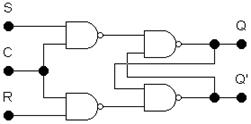

Схема асинхронного RS-триггера, реализованная на основе элементов И-НЕ, приведена на рисунке 2.17, a.

|

|

|

|

a |

b |

Рисунок 2.17

Работу устройства рассмотрим в порядке записи данных в таблице 2.7.

Т а б л и ц а 2.7

|

|

R |

S |

Q |

Q’ |

|

1 |

1 |

1 |

? |

? |

|

2 |

0 |

0 |

1 |

|

|

3 |

1 |

0 |

1 |

|

|

4 |

0 |

1 |

0 |

|

|

5 |

1 |

1 |

0 |

|

|

6 |

0 |

0 |

1 |

1 |

|

7 |

1 |

1 |

??? |

??? |

На первой строке таблицы: R = 1, S = 1; на одном из входов обоих элементов – лог.1, а уровни сигналов на входах обратной связи неизвестны, следовательно неизвестны уровни сигналов на выходах (Q и Q’).

На второй строке: R = 0, S = 1; ввиду того, что на одном из входов нижнего элемента – лог.0, и в соответствии с логикой работы этого элемента, на его выходе (Q’), а также на нижнем входе верхнего элемента, будет лог.0, в результате чего на выходе нижнего элемента (Q) будет лог.1, а на выходе верхнего элемента (Q) будет лог.0; Итак, триггер устанавливается в состояние лог.0.

На третьей строке: R = 1, S = 1; изменение сигнала на входе R на 1 не повлияет на состояние триггера, так как уровни сигналов на остальных входах элементов не изменились, следовательно, триггер остается в предыдущем состоянии.

На четвертой строке: R = 1, S = 0; ввиду того, что на одном из входов нижнего элемента – лог.0, и в соответствии с логикой работы этого элемента, на его выходе (Q), а также на верхнем входе нижнего элемента, будет лог.1, в результате чего на выходе верхнего элемента (Q’) будет лог.0; Итак, триггер устанавливается в состояние лог.1.

На пятой строке: R = 1, S = 1; изменение сигнала на входе S на 1 не повлияет на состояние триггера, так как уровни сигналов на остальных входах элементов не изменились, следовательно, триггер остается в предыдущем состоянии.

Из рассмотренных случаев можно сделать следующий вывод: случай подачи R = 0, S = 1 соответствует записи в триггер нуля (установки его в состояние лог.0); случай R = 1, S = 0 – записи 1 (установки его в состояние лог.1); а случай R = 1, S = 1 – режиму хранения триггера.

В случае подачи на входы триггера R = 0, S = 0 (шестая строка), на выходах обоих элементов будет лог.1, и когда триггер переводится в режим хранения (седьмая строка), неизвестно, в какое состояние он установится, это – случайный процесс. Следовательно, необходимо исключить такой случай; поэтому данный случай называется запрещенным режимом триггера.

Итак, рабочие режимы рассмотренного триггера кратко можно представить в виде таблицы 2.8.

Т а б л и ц а 2.8

|

R |

S |

Q |

Q’ |

Режимы работы |

|

0 |

0 |

– |

– |

Запрещенный режим |

|

0 |

1 |

1 |

0 |

Режим записи ‘0’ |

|

1 |

0 |

0 |

1 |

Режим записи ‘1’ |

|

1 |

1 |

Q0 |

Q0’ |

Режим хранения |

Ввиду того что режимы записи рассмотренного триггера реализуются нулевым уровнем соответствующего сигнала (S – Set, R – Reset), такой триггер называется триггером с инвверсными входами. Его условно-графическое обозначение приведено на рисунке 2.17, b.

Переходим к рассмотрению синхронных триггеров. Перевод синхронных триггеров в состояние, соответствующее информационным сигналам, осуществляется специальными сигналами управления. В зависимости от характера сигналов управления различают триггеры со статическим управлением и триггеры с динамическим управлением.

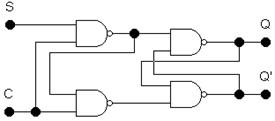

Схему триггера со статическим управлением (т.е. управляемого уровнем сигнала) можно построить построить путем присоединения схемы управления, составленного из двух элементов И-НЕ (см. рисунок 2.18, a).

|

|

|

|

a |

b |

Рисунок 2.18

Режимы работы этого триггера представлены в таблице 2.9.

Т а б л и ц а 2.9

|

С |

R |

S |

Q |

Q’ |

Режимы работы |

|

0 |

x |

x |

Q0 |

Q0’ |

Режим хранения |

|

1 |

0 |

0 |

– |

– |

Режим хранения |

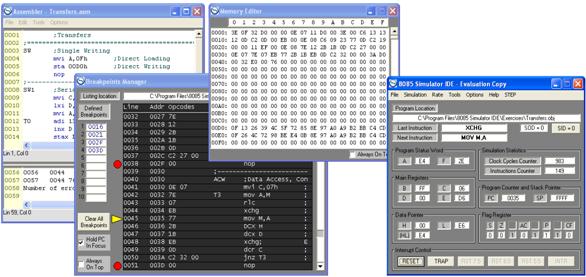

|

0 |

1 |

1 |

0 |

Режим записи ‘1’ |

|

|

1 |

0 |

0 |

1 |

Режим записи ‘0’ |

|

|

1 |

1 |

Q0 |

Q0’ |

Запрещенный режим |

При C = 0 триггер находится в режиме хранения. Изменение состояния триггера в соответствии с уровнями сигналов на входах R и S осуществляется при С = 1. Условно-графическое обозначение синхронного RS-триггера приведено на рисунке 2.18, b.

Схема и условно-графическое обозначение D-триггера (Delay) приведена на рисунке 2.19, а режимы его работы представлены в таблице 2.10.

|

|

|

|

a |

b |

Рисунок 2.19

Т а б л и ц а 2.10

|

С |

D |

Q |

Q’ |

Режимы работы |

|

0 |

x |

Q0 |

Q0’ |

Режим хранения |

|

1 |

0 |

0 |

1 |

Режим записи ‘0’ |

|

1 |

1 |

0 |

Режим записи ‘1’ |

В дальнейшем рассмотрим три разновидности триггеров с динамическим управлением: D-триггер, JK-триггер и T-триггер.

Перевод триггеров с динамическим управлением в новое состояние осуществляется соответствующим перепадом (фронтом или срезом) сигнала управления. Триггеры с динамическим управлением обычно строят, по так называемой, трехтриггерной структуре. Не останавливаясь на схемной реализации триггеров с динамическим управлением, ознакомимся только с режимами их работы.

Условно-графическое обозначение D-триггера с динамическим управлением приведено на рисунке 2.20, a, а режимы его работы представлены в таблице 2.11.

|

|

|

|

a |

b |

Рисунок 2.20

Т а б л и ц а 2.11

|

С |

D |

Q |

Q’ |

Режимы работы |

|

|

0 |

0 |

1 |

Режим хранения |

|

1 |

1 |

0 |

Режим записи |

Изменение состояния этого триггера в соответствии уровнем информационного сигнала (D) осуществляется по положительному перепаду (фронту) управляющего сигнала (С), что отмечено соответствующим знаком на условно-графическом обозначении (а также в таблице).

JK-триггер имеет четыыре рабочих режима (см. таблицу 2.12): три его режима аналогичны соответствущим режимам (запись ‘0’, запись ‘1’, хранение) RS-триггера, а четвертый режим называют счетным режимом; в этом режиме триггер изменяет свое текущее состояние на противоположное. На условно-графическом обозначении JK-триггера (см. рисунок 2.20, b) и в таблице режимов его работы (см. таблицу 2.12) имеются соответствующие знаки о том, что управление работой этого триггера осуществляется по отрицательному перепаду (по срезу).

Т а б л и ц а 2.12

|

С |

J |

K |

Q |

Q’ |

Режимы работы |

|

|

0 |

0 |

Q0 |

Q0’ |

Режим хранения |

|

0 |

1 |

0 |

1 |

Режим записи ‘0’ |

|

|

1 |

0 |

1 |

0 |

Режим записи ‘1’ |

|

|

1 |

1 |

Q0’ |

Q0 |

Счетный режим |

T-триггер – триггер, работающий только в счетном режиме. На рисунке 2.21 представлены схемные реализации работы Т-триггера на основе D-триггера и JK-триггера.

|

|

|

|

a |

b |

Рисунок 2.21

В виде микросхем выпускаются только D-триггеры и JK-триггеры. В их микросхемах, кроме выводов для информационных и управляющих сигналов, устанавливаются выводы для подачи сигналов предварительной установки (см. рисунок 2.22). Асинхронные сигналы, подаваемые на эти входы, имеют более высокий приоритет по сравнению с остальными сигналами.

|

|

|

|

a |

b |

Рисунок 2.22

2.4.2 Регистры.

Регистр – устройство, предназначенное для хранения слова, представленного в виде многоразрядного двоичного числа. Они могут быть построены на основе триггеров (например, D-триггеров). В зависимости от способа записи слова в регистр различают регистры с последовательным вводом и с параллельной записью.

В регистрах с последовательным вводом выход каждого триггера подключен к информационному входу следующего триггера. Значения разрядов слова, представленного в виде многоразрядного двоичного числа, последовательно вводятся на первый триггер соответствующим перепадом тактового сигнала, а значения ранее записанных в триггеры разрядов сдвигаются на следующие триггеры. Разумеется, что для записи всего слова требуется столько тактовых сигналов, сколькими разрядами представлено слово.

В регистрах с параллельной записью значения разрядов слова параллельно подаются на информационные входы регистра, и запись осуществляется одним тактовым сигналом.

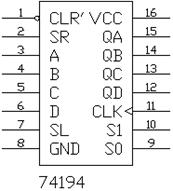

Имеются универсальные регистры, где охвачены оба способа ввода информации. Примером такого регистра может служить микросхема 74194, выполняющая функцию четырехразрядного универсального регистра (см. рисунок 2.23).

Рисунок 2.23

Функции выводов (т.е. соответствующих сигналов) микросхемы 74194:

- VCC, GND – выводы подключения источника питания и земли;

- A, B, C, D – выводы для параллельного ввода информации;

- QA, QB, QC, QD – выходы регистра;

- SR – вывод для ввода информации при сдвиге налево;

- SL – вывод для ввода информации при сдвиге направо;

- S1, S0 – выводы для сигналов, определяющих режимы работы регистра: S1 = 0, S0 = 0 – режим хранения; S1 = 0, S0 = 1 – режим сдвига налево; S1 = 1, S0 = 0 – режим сдвига направо; S1 = 1, S0 = 1 – режим параллельного ввода информации;

- CLK – вывод тактового сигнала;

- CLR’ – вывод сигнала очистки.

2.4.3 Счетчики.

Счетчик – устройство, изменяющее свое содержимое на единицу при каждом соответствующем перепаде (по фронту или по срезу) поступающих импульсов. В зависимости от направления изменения содержимого, счетчики разделяют на суммирующие, вычитающие и реверсивные (или универсальные). Счетчики строят на основе Т-триггеров.

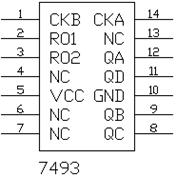

Примером простого счетчика может служить микросхема 7493, выполняющая функцию 4-разрядного суммирующего (см. рисунок 2.24, a).

|

|

|

|

a |

b |

Рисунок 2.24

В его составе имеются одноразрядный и трехразрядный счетчики.

Функции выводов микросхемы 7493:

- VCC, GND – выводы подключения источника питания и земли;

- CKA, QA – вход и выход одноразрядного счетчика;

- CKB, QB, QC, QD – вход и выходы трехразрядного счетчика;

- R01, R02 – вывод сигнала очистки счетчика.

Счетчики в составе этой микросхемы можно использовать и самостоятельно, в качестве четырехразрядного счетчика, соединив их друг к другу.

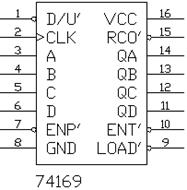

Примером реверсивного (универсального) счетчика может служить микросхема 74169 (см. рисунок 2.24, b).

Функции выводов микросхемы 74169:

- VCC, GND – выводы подключения источника питания и земли;

- A, B, C, D – выводы для параллельного ввода информации;

- LOAD’ – вывод сигнала параллельного ввода информации;

- QA, QB, QC, QD – выводы счетчика;

- D/U’ – вывод сигнала, определяющего направление счета;

- ENP’, ENT’ – выводы сигналов инициализации;

- CLK – вывод тактового сигнала;

- RCO’ – сигнал достижения модуля счета.

2.5 Устройства памяти

Устройства памяти (или по-другому, запоминающие устройства) служат для хранения информации в цифровых системах, в состав которых они входят. Цифровые системы, в зависимости от выполняемых ими функций, могут включать в свой состав различные типы устройств памяти: регистровая память, являющаяся составной частью микропроцессоров; кэш-память, позволяющая повысить быстродействие цифровых систем; основная память (оперативная, постоянная), работающая в режиме непосредственного обмена с процессором и согласованная с ним по быстродействию; внешняя память, предназначенная для хранения больших объемов информации и др.

2.5.1 Характеристики устройств памяти.

Важнейшими параметрами, описывающими функциональные возможности устройств памяти, являются:

- информационная емкость – максимально возможный объем хранимой информации, выражаемой в битах, в байтах или в словах. Чаще всего этот параметр представляют в виде произведения числа хранимых слов на их разрядность;

- быстродействие устройств памяти, оцениваемой временами считывания, записи и длительностями циклов чтения/записи. Время считывания (или записи) – интервал между моментами подачи сигнала управления (чтения/записи) и завершения соответствующей операции. Длительность циклов чтения/записи – минимально допустимый интервал между последовательными операциями.

Кроме перечисленных традиционных временных параметров, для описания работы некоторых систем памяти могут быть использованы дополнитеьные параметры. Например, для описания систем памяти, работающих с пакетами данных, вводят параметр времени доступа при первом обращении (Latency) и темпа передач для последующих слов пакета (Bandwidth).

Помимо указанных выше динамических параметров, существует ряд режимных параметров, определяющих взаимное расположение нескольких сигналов управления во времени и их длительности.

Управление работой устройств памяти осуществляется следующими сигналами:

- A (Address) – адрес, разрядность которого (n) определяется числом ячеек устройства памяти, т.е. максимально возможным числом хранимых в нем слов (N=2n);

- CS (Chip Select) или CE (Chip Enable) – сигнал выбора микросхемы или ее инициализации;

- R/W (Read/Write) – сигнал выполнения соответствующей операции;

- DI (Data Input) и DO (Data Output) – шины входных и выходных данных. В некоторых системах памяти эти линии могут быть объединены.

В зависимости от способа доступа к данным, устройства памяти делятся на устройства с адресным доступом, устройства с последовательным доступом и устройства с ассоциативным доступом.

При адресном доступе код на адресных входах устройства памяти указывает ячейку, с которой ведется обмен. Такие устройства памяти наиболее разработаны, и другие виды памяти часто строят на их основе с соответствующими модификациями.

Адресные устройства памяти, в свою очередь, делятся на RAM (Random Access Memory) и ROM (Read-Only Memory). В RAM хранятся данные, участвующие в обмене при исполнении текущей программы, и которые могут быть изменены в произвольный момент времени. Запоминающие элементы RAM, как правило, не обладают энергонезависимостью.

По характеру элементов памяти RAM делятся на статические (SRAM, Static RAM) и динамические (DRAM, Dynamic RAM). Элементами памяти SRAM являются триггеры, а в DRAM данные хранятся в виде зарядов конденсаторов, образуемых элементами МОП-структур. Саморазряд конденсаторов ведет к разрушению данных, поэтому они должны периодически (каждые несколько миллисекунд) регенерироваться. В то же время плотность упаковки динамических элементов памяти в несколько раз превышает плотность упаковки, достижимую в статических RAM.

Динамические RAM характеризуются наибольшей информационной емкостью и невысокой стоимостью, поэтому именно они используются как основная память ЭВМ. Статические RAM в несколько раз дороже (из-за сложности элементов памяти) динамических и приблизительно во столько же раз меньше по информационной емкости. Их достоинством является высокое быстродействие, а типичной областью использования – схемы кэш-памяти.

Устройства памяти типа ROM характеризуются тем, что информация в них в рабочем режиме никогда не изменяется. В некоторых их разновидностях информация может изменяться, но только не в оперативном режиме.

В зависимости от способа (и места) программирования, различают несколько разновидностей ROM: ROM(M), PROM, EPROM и EEPROM.

Устройства типа ROM(M) программируются при изготовлении методами интегральной технологии с помощью одной определенной маски (Mask).

Устройства типа PROM (Programmable ROM) программируются (но однократно) самим пользователем.

В устройствах типа EPROM (Electrically Programmable ROM) и EEPROM (Electrically Erasable Programmable ROM) можно стереть старую информацию и записать новую (перепрограммировать). В устройствах EPROM предварительное стирание информации осуществляется с помощью ультрафиолетового излучения (на специальных устройствах), а EEPROM – электрическими сигналами. Запись данных в обоих случаях производится электрическими сигналами.

В устройствах памяти с последовательным доступом считывание осуществляется слово за словом либо в порядке записи, либо в обратном порядке. Прямой порядок считывания имеет место в буферах FIFO, работающих по принципу “первый пришел – первый вышел” (First In – First Out), а также в файловых и циклических системах памяти. Считывание в обратном порядке свойственно стековым организациям памяти, для которых реализуется принцип “последний пришел – первый вышел”. Такие устройства памяти называют буферами LIFO (Last In – First Out).

В устройствах памяти с ассоциативным доступом поиск информации осуществляется по некоторому признаку (tag), а не по ее расположению в памяти (адресу или месту в очереди). Основная область применения ассоциативной памяти в больших цифровых системах (например, в современных ЭВМ) – кэширование данных.

2.5.2 Структура устройств памяти типа RAM.

Построение статических RAM осуществляется по структурам 2D, 3D и 2DM.

В структуре 2D (см. рисунок 2.25) m-разрядные элементы памяти присоединены к соответствующим выходам дешифратора, т.е. они размещены линейно относительно друг друга, поэтому такую структуру часто называют линейной структурой.

Рисунок 2.25

Дешифратор адресного кода DC при наличии разрешающего сигнала CS (Chip Select – сигнал выбора микросхемы) активизирует одну из выходных линий, осуществляя доступ к соответствующей ячейке. Соответствующие элементы столбцов (разрядов) соединены вертикальной линией – внутренней линией данных (разрядной линией, линией записи/считывания). Элементы столбца хранят одноименные биты всех слов. Направление обмена определяется усилителями чтения/записи под воздействием сигнала R/W (Read – чтение, Write – запись).

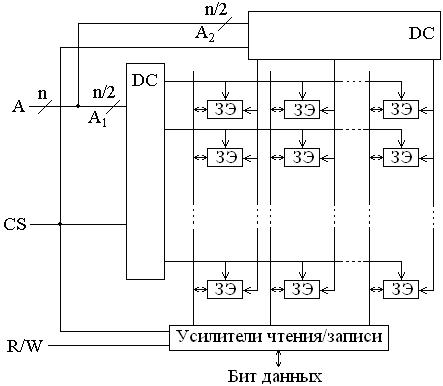

Структура 3D (также называемая матричной структурой) позволяет резко упростить дешифраторы адреса с помощью двухкоординатной выборки запоминающих элементов (см. рисунок 2.26).

Здесь код адреса разрядностью n делится на две половины, каждая из которых декодируется отдельно. Выбирается запоминающий элемент (или ячейка), находящийся на пересечении активных линий выходов обоих дешифраторов. Число таких пересечений будет 2n/2 х 2n/2 = 2n. Суммарное число выходов обоих дешифраторов составляет 2n/2 + 2n/2 = 2n/2+1, что гораздо меньше, чем число выходов дешифратора в структуре 2D (2n).

Рисунок 2.26

В структурах типа 2DM (2D модифицированная), предназначенной для организации систем памяти в больших цифровых системах (в частности, в компьютерах), сочетаются достоинства структур 2D и 3D – упрощается дешифрация адреса и не требуются запоминающие элементы с двухкоординатной выборкой.

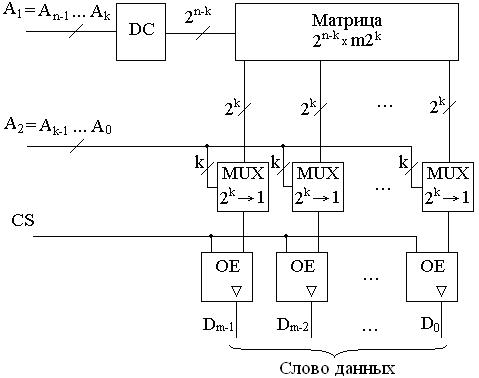

Матрица ЗЭ структуры 2DM (см. рисунок 2.27) имеет как бы характер структуры 2D: возбужденный выход дешифратора выбирает целую строку. Однако в отличие от структуры 2D, длина строки не равна разрядности хранимых слов, а многократно ее превышает. Для выбора одной из строк служат часть адресного кода An–1... Ak. Остальные разряды адреса (от Ak–1... A0) используются, чтобы выбрать необходимое слово из того множества слов, которое содержится в строке и которое выполняется с помощью мультиплексоров. На выходах мультиплексоров формируется выходное слово и по разрешению сигнала CS, поступающего на входы ОЕ управляемых буферов с тремя состояниями, это слово передается на внешнюю шину.

Рисунок 2.27

2.5.3 Элементы устройств памяти типа ROM.

Устройства памяти типа ROM (Read Only Memory) хранят информацию, которая либо вообще не изменяется (в ЗУ типов ROM(M) и PROM), либо изменяется редко и не в оперативном режиме (в ЗУ типов EPROM и EEPROM).

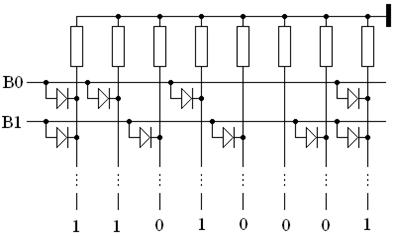

Программирование постоянной памяти заключается в том или ином размещении элементов связи между горизонтальными и вертикальными линиями матрицы запоминающих элементов. В матрице ROM(M), как правило, в качестве элементов памяти, размещаемыых в узлах координатной сетки, применяются биполярные диоды, МОП-транзисторы и др. В матрице диодного ROM(M) (см. рисунок 2.28) горизонтальные линии являются линиями выборки слов, а вертикальные – линиями считывания. Считываемое слово определяется расположением диодов в узлах координатной сетки. При наличии диода высокий потенциал выбранной горизонтальной линии передается на соответствующую вертикальную линию, и в данном разряде слова появляется сигнал логической единицы. При отсутствии диода потенциал близок к нулевому, так как вертикальная линия через резистор связана с землей. В изображенной матрице при возбуждении линии выборки В0 считывается слово 11010001, а при возбуждении линии В1 – 10101011. Шины выборки являются выходами дешифратора адреса, каждая адресная комбинация возбуждает свой выход дешифратора, что приводит к считыванию слова из адресуемой ячейки (строки).

Рисунок 2.28

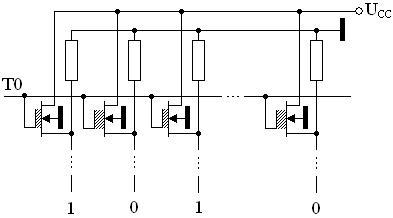

В матрице ROM(M), изготовленных по технологии МОП, в качестве элементов памяти, размещаемыых в узлах координатной сетки, применяются МОП-транзисторы, (см. рисунок 2.29). В МОП-транзисторах, соответствующих хранению нуля, увеличивают толщину подзатворного окисла, что ведет к увеличению порогового напряжения транзистора. В этом случае рабочие напряжения системы не в состоянии открыть транзистор. Постоянно закрытое состояние транзистора аналогично его отсутствию. В МОП-транзисторах, соответствующих хранению единицы, толщину подзатворного окисла уменьшают до таких размеров, чтобы они могли открываться сигналом выборки, поступающих от дешифратора,

Рисунок 2.29

Устройства памяти типа ROM(M) отличаются компактностью элементов памяти и, следовательно, высоким уровнем интеграции. При больших объемах производства масочное программирование предпочтительно, однако при недостаточной их тиражности затраты на проектирование и изготовление шаблона для технологического программирования устройств памяти окажутся чрезмерно высокими. Отсюда видна и область применения устройств памяти типа ROM(M) – хранение стандартной информации, имеющей широкий круг потребителей. В частности, устройства памяти типа ROM(M) имеют в качестве “прошивки” коды букв алфавитов (русского и латинского), таблицы типовых функций (синуса, квадратичной функции и др.), стандартное программное обеспечение и т. п.

Микросхемы памяти типа PROM программируются устранением или созданием специальных перемычек. В исходной заготовке имеются (или отсутствуют) все перемычки. После программирования остаются или возникают только необходимые.

Устранение части перемычек свойственно ЗУ с плавкими перемычками (см. рисунок 2.30, a). При этом в исходном состоянии перемычки установлены во всех узлах матрицы, а при программировании часть их ликвидируется путем расплавления импульсами тока достаточно большой амплитуды и длительности. Итак, в исходном состоянии все элементы хранят логическую единицу, логический нуль можно записать, расплавляя перемычку.

Создание части перемычек соответствует схемам, которые в исходном состоянии имеют непроводящие перемычки в виде пары встречно включенных диодов (см. рисунок 2.30, b). В исходном состоянии сопротивление такой цепочки настолько велико, что практически равноценно разомкнутой цепи, и элемент памяти хранит логический нуль. Для записи единицы к диодам прикладывают повышенное напряжение, пробивающее диод, смещенный в обратном направлении. Диод пробивается с образованием в нем короткого замыкания и играет роль появившейся проводящей перемычки.

|

|

|

|

a |

b |

Рисунок 2.30

В репрограммируемых устройствах памяти типов EPROM и EEPROM возможно стирание старой информации и замена ее новой в результате специального процесса, для проведения которого ЗУ выводится из рабочего режима. Рабочий режим (чтение данных) – процесс, выполняемый с относительно высокой скоростью. Замена же содержимого памяти требует выполнения гораздо более длительных операций.

Элементами памяти в устройствах памяти типов EPROM и EEPROM являются транзисторы типов МНОП ((Металл, Нитрид, Окисел, Полупроводник)) и ЛИЗМОП (добавление ЛИЗ к обозначению МОП происходит от слов Лавинная Инжекция Заряда), работа которых основана на создании плавучих затворов [1].

3 Микропроцессоры и микропроцессорные системы

3.1 Структурные принципы микропроцессорных систем

Микропроцессор (МП) является центральным устройством в составе вычислительных, контрольно-измерительных и управляющих систем, обобщенно называемых микропроцессорной системой (МПС), осуществляющим обработку и всевозможную пересылку информации. Процесс выполнения микропроцессором поставленной задачи определяется соответствующей программой, составленной в виде последовательности команд из системы команд данного микропроцессора.

В состав микропроцессорной системы, наряду с микропроцессором, входят устройства памяти и устройства ввода/вывода информации. Набор микросхем, пригодных (по техническим и информационным параметрам) для применения в составе микропроцессорной системы, называют микропроцессорным набором.

При определении структуры микропроцессорной системы учитывается реализация трех основных принципов, это – принцип магистральности, принцип модульности и принцип микропрограммного управления.

Магистральный принцип определяет характер связи между различными функциональными блоками МПС; все блоки системы соединены к общей системной магистрали и обмениваются между собой информацией через эту магистраль.

Модульный принцип обусловливает построение МПС на основе отдельных, функционально законченных модулей. Каждый модуль снабжается входом, уровнем сигнала на котором, управляется инициализация данного модуля, т.е. подключение его к магистали, или перевод его в третье (высокоимпедансное) состояние.

Принцип микропрограммного управления характеризует возможности реализации элементарных операций – микрокоманд (пересылки информации, арифметических операций, сдвигов и др.).

В состав системной магистрали входят три основных информационных шин: это – адресная шина АВ (Address Bus), шина данных DB (Data Bus) и шина управления СВ (Control Bus).

Шина данных – основная (и двунаправленная) шина, по которой осуществляется обмен данными между модулями системы.

Адресная шина – шина, обеспечивающая связь с памятью (или с внешними усиройствами).

С целью уменьшения полного числа линий связи магистрали, часто применяют мультиплексирование передачи адрес и данных (в начале цикла – адрес, в конце цикла – данные).

Сигналы на линиях шины управления определяют тип цикла и отмечают временные моменты, соответствующие различным его частям и зонам. Наряду с этим, сигналы управления согласовывает работу процессора (или другого хозяина магистрали, ведущего, master) с работой памяти или устройств ввода/вывода (ведомого устройства, slave).

Основные сигналы управления – стробы обмена, т.е. стробы записи (вывода) и чтения (ввода). Процессор, формируя эти сигналы, определяет моменты соответствующих пересылок данных.

Для присоединения устройств ввода/вывода (УВВ) или внешних устройств (ВУ) к системной магистрали, их сигналы должны соответствовать стандартам соответствующих интерфейсов, через которые осуществляется связь.

Выполнение процессором операций записи и чтения могут быть осуществлены в режимах программно-управляемого обмена, прерывания и прямого доступа к памяти, основной из них – первый.

3.2 Микропроцессор Intel 8085

Микропроцессор (МП) – наиболее важный блок, входящий в состав сложных цифровых систем (например, компьютеров), и осуществляющий обработку информации.

Основные структурные принципы и порядок организации работы микропроцессоров удобно рассмотреть на примере конкретного микропроцессора. В качестве такого образца рассмотрим простейший микропроцессор Intel 8085, являющийся праотцом современных микропроцессоров. Несмотря на свой солидный возраст, он до сих пор выпускается производством или служит основой при создании новых типов микропроцессоров. Разумеется, область его применения – не компьютеры, в которых сейчас применяют более мощные и производительные микропроцессоры. Микропроцессоры типа Intel 8085, в основном, используются в системах управления, где их возможностей хватает.

3.2.1 Структура микропроцессора.

Структура микропроцессора Intel 8085 представлена на рисунке 3.1. Обмен информацией между его составными блоками осуществляется через его внутреннюю восьмиразрядную шину данных. Рассмотрим составные блоки микропроцессора:

AC (Accumulator) – регистр-аккумулятор, где хранится один из операндов или результат операции;

TR (Temporary Register) – регистр временного хранения одного из операндов;

ALU (Arithmetic-Logic Unit) — арифметико-логическое устройство, выполняющее действия над двумя словами-операндами, подаваемыми на его входы. Аккумулятор служит источником и приемником данных, TR – источником слова данных, хранимым на время выполнения операции. АЛУ функционирует согласно соотношению А:= А*В, где В хранится в TR, второй операнд поступает от аккумулятора, в него же поступает результат операции. АЛУ непосредственно выполняет лишь операции сложения, вычитания, сдвига, сравнения слов, поразрядные логические операции (конъюнкцию, дизъюнкцию, сложение по модулю 2). Более сложные операции (умножение, деление и др.) выполняются по подпрограммам. В АЛУ имеется схема перевода двоичных чисел в двоично-десятичные (DA, Decimal Adjust);

Рисунок 3.1

RF (Register Rags) – регистр флагов, т. е. битов, указывающих признаки результатов арифметических или логических операций, выполненных в АЛУ. Указываются пять признаков: Z (Zero) – нулевой результат, С (Carry) – перенос, AC (Auxiliary Carry) – вспомогательный перенос, S (Sign) – знак, P (Parity) –, четность веса слова. Признак вспомогательного переноса (переноса между младшей и старшей тетрадами восьмиразрядного слова) нужен при выполнении операций в двоично-десятичном коде. Смысл остальных признаков ясен из их наименований. Признаки служат для управления ходом процесса обработки информации.

В, С, D, E, H, L – регистры общего назначения (РОН). каждый из них Эти восьмиразрядные регистры могут применяться либо по отдельности, либо в виде пар В-С, D-E, H-L, играющих роль 16-разрядных регистров. Пары регистров именуются по первым регистрам пары как пары В, D, Н. Пара H-L, как правило, используется для размещения в ней адресов при косвенной регистровой адресации.

W және Z – программно недоступные регистры, предназначенные для временного хранения данных.