ҚАЗАҚСТАН

РЕСПУБЛИКАСЫНЫҢ БІЛІМ ЖӘНЕ ҒЫЛЫМ МИНИСТРЛІГІ

“Алматы энергетика және байланыс

университеті”

коммерциялық емес

акционерлік қоғамы

О.Т. Шанаев

ЦИФРЛЫҚ ҚҰРЫЛҒЫЛАРДЫҢ СХЕМОТЕХНИКАСЫ

Оқу құралы

Алматы 2013

ӘОЖ 681.3.06

ББК 32.844Я73

Цифрлық құрылғылардың схемотехникасы;

Оқу құралы / Шанаев О.Т. Алматы: АЭжБУ, 2013. – 92 б.

ISBN 978-601-7327-90-3

Оқу құралында цифрлық құрылғылардың элементтік негіздері суреттелген, онымен қатар қиыстырма, тізбектеме құрылғылардың және жады құралымдарының базалық құрылым принциптері қарастырылған.

Цифрлық құрылғылардың құрылымын логикалық және схемотехникалық тұрғыдан құру мүмкіншілігін көрсету мақсатында нақтылы алгоритмдерді жүзеге асырушы бірнеше цифрлық құралымның тәжірибелік моделдері суреттелген.

Микропроцессорлардың құрылымы мен микропроцессорлық жүйелердің құралым принциптерін суреттеп, микропроцессорлық жүйенің жұмысын ұйымдастыруға арналған, әртүрлі командаларды қолдану арқылы құрылған бағдарламалық құрылымдарды қарастыру арқылы микропроцессорлық техника жөнінде түпнегіз қалаушы білім игеруге мүмкіндік беріледі.

Оқу құралының ақырғы тарауы микропроцессорлық жүйелердің жалпы құрылым принциптерінің іс жүзінде жүзеге асырылу мүмкіндігін суреттеу мақсатында бағдарламалы Electronics Workbench модельдеу жүйесінде құрылған микропроцессорлық жүйенің моделін суреттеуге арналған.

Без. 56, кесте 29, әдеб. көрсеткіші 12 атау.

ББК 32.844Я73

ПІКІР БЕРУШІЛЕР: ҚазҰТУ, физ-мат. ғыл. д-р., профессор Т. Тусеев,

Абай ат. ҚазҰПУ, тех. ғыл. канд., профессор Ш.И.Хамраев,

АЭжБУ, физ-мат. ғыл. д-р., профессор С.Б. Бимурзаев

Алматы энергетика және байланыс университетінің Ғылыми кеңесі басуға ұсынды (10.01.2012 ж. № 3хаттама).

ISBN 978-601-7327-90-3

© “Алматы энергетика және байланыс университеті” КЕАҚ, 2013 ж.

Кіріспе

Цифрлық құрылғылардың нақтылы алгоритмге сәйкесті жұмыс істеуі объектінің (немесе технологиялық процестің) параметрлерін өлшеп, сосын алынған деректерді сәйкесті тәртіппен өңдеу нәтижесінде объектінің жағдайын қажетті бағытта өзгертуге арналған басқару сигналдарын қалыптастыру арқылы жүзеге асырылады.

Жұмыс принциптеріне байланысты цифрлық құрылғыларды екі түрге бөлуге болады. “Тастай логикалы” деп аталатын цифрлық құрылғылардың ақпарат өңдеу және сақтау алгоритмдері олардың сұлбақұралысымен ғана анықталады. Өзге алгоритмге көшу үшін, құрылғыны түгелдей қайта құруға тура келеді. Бұндай құрылғылардың басты артықшылығы, олардың құрама элементтерінің (мысалы, олардың құрамындағы микросұлбалардың) жасалу технологиясымен анықталатын тез әрекеттілігі.

“Икемді логикалы” жүйе деп аталатын цифрлық құрылғылардың құрылымы әртүрлі мәселелерді шешуге мүмкіндік беретіндей етіп құрылады, яғни олар әмбебап құрылғыларға жатады. Құрылғының жұмыс алгоритмін өзгерту оған жаңа бағдарлама орналастыру арқылы жүзеге асырылады. Осындай құрылғылардың қатарына микропроцессорлық жүйелер (МПЖ), оның ішінде компьютерлер жатады. Бұндай жүйелердің “әмбебаптылығы” аппараттық артықшылық арқылы жүзеге асырылады, ал бұл бүкіл жүйенің жұмыс жылдамдығына кері әсер етеді және оны қымбаттатады.

МПЖ сияқты күрделі цифрлық жүйелерді құру кезінде өзара байланысты және өзара тәуелді екі фактор ескеріледі, олар – сан-алуан түрлі мәселелердің іс жүзінде жүзеге асырылуын қамтамасыз етуші жүйенің аппаратық бөлігін (hardware) құру және жүйе бөліктемелерінің жеке жұмысы мен олардың өзара әрекеттесуін шешілетін мәселелерге сәйкесті бағдарлауға мүмкіндік беретін командалар жүйесін (software) анықтау. Демек, заманауи цифрлық жүйелер туралы толық білім алу үшін олардың аппаратық құрылым принциптерін де, әртүрлі бағдарламалық құрылымдардың жүзеге асырылу принциптерін де игеру керек.

Оқу құралының бірінші тарауында цифрлық құрылғылардың арифметикалық негіздері, онымен қатар автордың іс жүзінде пайдаланып жүрген, код түрлендірімдерінің ерекше тәсілдері талқыланған. Оған қоса осы тарауда цифрлық құрылғылардың негізін құрушы логикалық функциялардың жұмысы мен күрделі логикалық функцияларды құру және түрлендіру тәсілдері келтірілген.

Цифрлық жүйелердің құрамына кіретін құрылғылар екі түрге бөлінеді: олар – қиыстырма және тізбектеме құрылғылар. Қиыстырма құрылғылардың да, тізбектеме құрылғылардың да құрылым негізін, сәйкесті логикалық функцияларды жүзеге асырушы, логикалық элементтер құрады. Базалық логикалық элементтердің қызметі мен олардың негізгі сипаттамалары (мысалы, уақыттық сипаттамалары және олардың шығыс буындарының түрлері) оқу құралының екінші тарауында талқыланған.

Оқу құралының үшінші тарауында қиыстырма және тізбектеме құрылғылардың логикалық элементтер негізінде жалпылама құрылым принциптері мен жұмыс тәртібі және олардың өндірісте микросұлба түрінде шығарылатын қалыпты түрлері келтірілген. Оған қоса бұл тарауда қалыпты қиыстырма құрылғылардың ерекше пайдаланылу жолдары түсіндірілген. Бұл тәсілдер қазіргі заманғы бағдарламалы логикалық жинам сұлбалардың құрылым негізін қалайды.

Тізбектеме құрылғылардың құрылым негізін қалаушы жады элементтерінің және олардың негізінде құрылған тізбектеме құрылғылардың қалыпты түрлерінің (регистрлер мен санауыштардың) құрылым принциптері мен жұмысы оқу құралының төртінші тарауында қарастырылды.

Жады құрылымдарының өндірісте шығарылатын сәйкесті микросұлбаларының әртүрлі құрылым принциптері мен олардың құрама элементтерінің құрылымы оқу құралының бесінші тарауында қарастырылған.

Цифрлық құрылғылардың логикалық және құрылым принциптерін жүзеге асыру мүмңкіндіктерін суреттеу мақсатында оқу құралының алтыншы тарауында сұлбақұрылымдық моделдеу жұмысын жүзеге асыруға арналған, бұдан бұрын қарастырылған қалыпты қиыстырма және тізбектеме құрылғылар негізінде Electronics Workbench бағдарламалық ортасында құрылған, нақтылы алгоритмдерді жүзеге асыруға арналған бірнеше құралым келтірілген.

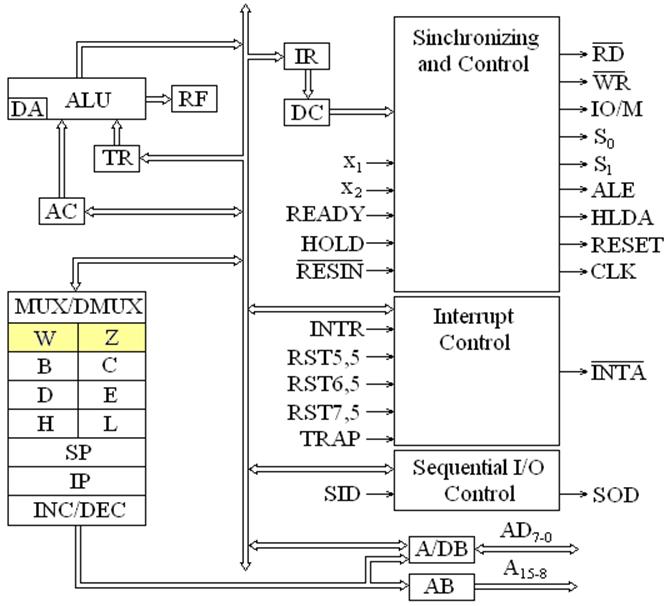

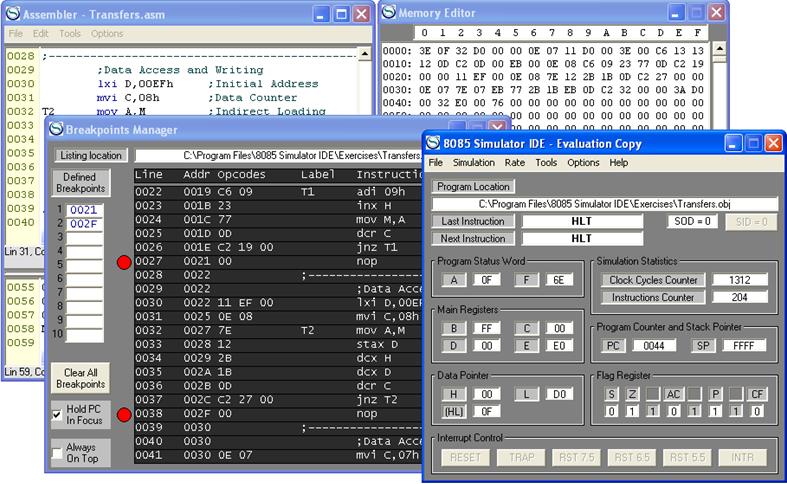

Жетінші тарауда микропроцессорлардың құрылымы мен микропроцессорлық жүйелердің негізгі құрылым принциптері Intel 8085 микропроцессорының құрамы мен оның ішкі құрама буындары, басқару сигналдары, командалар жүйесі және Intel 8085 микропроцессорының негізінде құрылған сәйкесті микропроцессорлық жүйенің жұмысының жалпы ұйымдастырылу тәртібі қарастырылды.

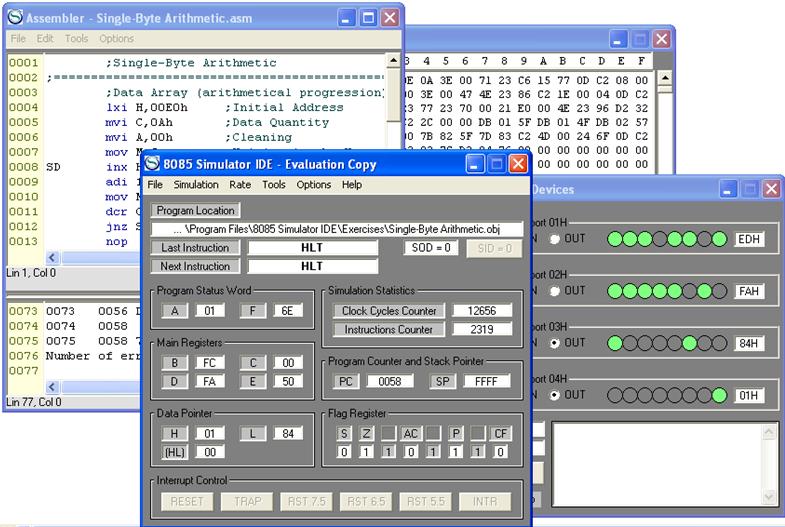

Оқу құралының сегізінші тарауында Intel 8085 микропроцессорының негізіндегі микропроцессорлық жүйеге арналған, жан-жақты (мөлшері және сілтеу тәсіліне қарай) командалар арқылы құрылған әртүрлі бағдарламалық құрылымдар суреттеледі. Келтірілген бағдарламалық құрылымдардың жүйе жұмысына іс жүзінде жарамдылығын бағдарламалы симулятордың (8085 Simulator IDE) және оның құрамындағы аспап-құралдардың қолданылым мүмкіндіктерін пайдалану арқылы тексеру ұсынылды.

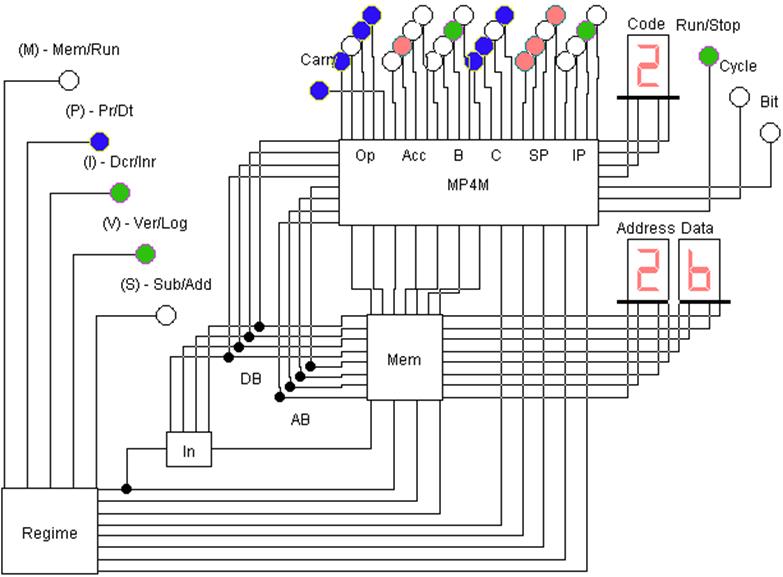

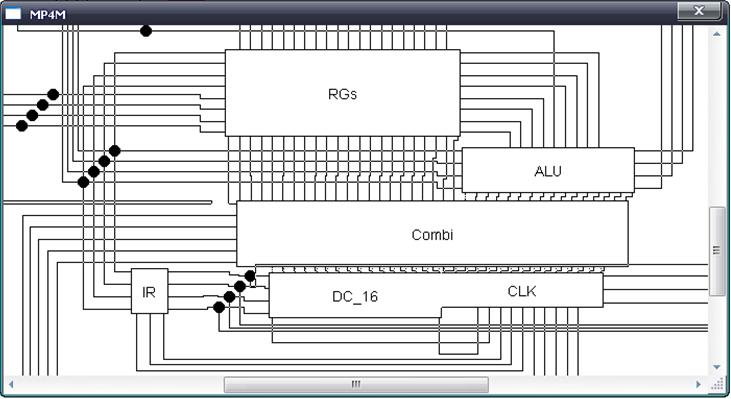

Оқу құралының тоғызыншы тарауы микропроцессорлық жүйелердің жалпы құрылым принциптерінің іс жүзінде жүзеге асырылу мүмкіндігін суреттеу мақсатында бағдарламалы Electronics Workbench модельдеу жүйесінде құрылған микропроцессорлық жүйенің моделі, оның құрама буындары мен ерекше командалар жүйесі және сәйкесті бағдарламалы құрылымдарының жүзеге асырылу жолдары қарастырылады.

Оқу құралында келтірілген сұлбалар, оның ішінде алтыншы және тоғызыншы қарастырылған құрылғылар студенттердің белсенді қатысуымен (курстық және дипломдық жұмыстарды орындау барысында) құрылды. Айтылғанды дәлел ретінде қарастырып, автор оқу құралын оқумен қатар онда келтірілген сұлбаларды Electronics Workbench модельдеу жүйесінде құрып, олардың жұмысын іс жүзінде тексергені дұрыс болады және бұл олардың цифрлық электроника бағытындағы шығармашылық мүмкіндігін дамытуға жол ашады деп санайды.

Берілген оқу құралы автордың көпжылдық педагогикалық қызметінің негізінде құрастырылды және ол 5В070400 – Есептеу техникасы және бағдарламалық қамтамасыз ету мамандығында оқитын студенттерге арналған.

1 Цифрлық техниканың арифметикалық және логикалық негіздері

1.1 Екілік кодтар

Атқарар қызметі мен күрделілігі жағынан әртүрлі цифрлық құрылғылардың (логикалық элементтерден бастап есептеу машиналарына дейін) жұмысы екілік санау жүйесінде жүзеге асырылады, яғни олардың кірістеріне түсетін және оның шығыстарынан алынатын ақпарат екілік сан түрінде көрсетіледі.

Цифрлық құрылғыларда пайдаланылатын екілік санау жүйесі позициялық санау жүйесіне жатады. Демек сандарды екілік санау жүйесінде көрсету үшін және оларға арифметикалық операциялар жүргізу үшін, өзімізге таныс, күнделікті пайдаланылатын ондық санау жүйесінің қағидалары пайдаланылады. Сондықтан алда келтірілетін, екілік санау жүйесіне байланысты түсіндірмелер ондық санау жүйесіндегі сәйкесті мәселелерді еске түсіріп, салыстырма қарастырылым арқылы жүргізіледі.

Ондық санау жүйесінде сан жазуға он символ (0 … 9) пайдаланылады (бұл жүйенің ондық санау жүйесі деп аталуы да осыған байланысты). Бұл символдардың сандағы тұрған орнына байланысты құны (салмағы) белгіленеді: ол санау жүйесі негізінің сәйкесті разряд нөмірінің мәніндегі дәрежесі арқылы анықталады. Сонымен, санның ең кіші разрядындағы (нөлінші разрядтағы) символдың құны бір (100), келесі разрядтың (бірінші разрядтың) құны он (101), одан әрі жүз (102), мың (103) және с.с. өзгере береді. Разряд құны, мәніне сәйкесті, бірлік, ондық, жүздік, мыңдық деп және с.с. аталады, ал сан разрядында тұрған символ сәйкесті разряд құнының сан құрамына қанша рет кіретіндігін көрсетеді. Келесі мысал арқылы айтылғанды түсіндірейік:

![]() .

.

Сонымен, келтірілген санның құрамында 7 бірлік, 5 жүздік, 3 мыңдық бар, ал ондық жоқ (0).

Екілік санау жүйесінде сан жазуға екі символ (0 және 1) пайдаланылады. Разряд құны екінің (яғни санау жүйесі негізінің) сәйкесті разряд нөмірінің мәніндегі дәрежесі арқылы анықталады. Сонымен, санның ең кіші разрядындағы (нөлінші разрядтағы) символдың құны бір (20), келесі разрядтың (бірінші разрядтың) құны екі (21), одан әрі төрт (22), сегіз (23) және с.с. өзгере береді. Разряд құны бірлік, екілік, төрттік, сегіздік деп және с.с. аталады, ал екілік код разрядында тұрған символ сәйкесті разряд құнының сан құрамына қанша рет кіретіндігін, дәлірек айтқанда, бар-жоқтығын көрсетеді. Айтылғанды келесі мысал суреттейді:

![]() .

.

Код құрамындағы символдардың 0 және 1 мәнінде ғана болуына байланысты, олар разрядқа сәйкесті құндық мәннің код құрамында бар-жоқтығын көрсетеді. Мысалы, келтірілген мысалдағы кодтың құрамында бірлік, екілік және сегіздік бар (1), ал төрттік жоқ (0).

1.1.1 Ондық сандардың екілік кодтары.

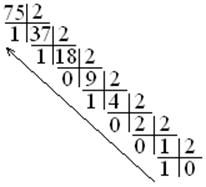

Өзімізге үйреншікті ондық сан түріндегі ақпаратты цифрлық құрылғыда өңдеу үшін ол екілік санау жүйесіндегі сәйкесті көрсетілім түріне, яғни екілік кодқа түрлендірілуі керек. Ол үшін түрлендірілетін сан және алынған кезекті бөлінділер екіге (яғни жаңа санау жүйесінің негізіне) тізбелеп бөлінеді де, бөлінді мәні нөл болған кезде бөлу операциялары тоқтатылады; жеке бөлу операцияларында анықталған қалдықтардың шығарылым бағытына қарсы тәртіппен жазылымы осы ондық санның екілік кодын береді. Мысал ретінде ондық санау жүйесіндегі 75 санына сәйкесті екілік кодтың анықталуын көрсетелік:

7510 = 10010112.

Әрине, көрсетілген тәсілмен кез келген ондық санның сәйкесті екілік кодын анықтауға болады. Бірақ автор бұл тәсілді жеңіл тәсіл деп санамайды: біріншіден, бұндағы тізбелеп жүргізілетін бөлу операциялары ұзақ уақыт алады (мысал ретінде ондық 1000 санының екілік кодын алып көріңіз); екіншіден, тізбеленген бөлу операцияларының жүргізілу ұзақтығынан, қателік жіберу ықтималдығы да ұлғая түседі.

Айтылған тәсілдің кемістіктерінен құтылу мақсатында автор ондық санның екілік кодын анықтауға іс жүзінде пайдаланып жүрген өз тәсілдерін ұсынады және оның біріншісін суреттеуге алдыңғы мысалда алынған 75 саны пайдаланылады:

- алдымен алынған ондық санның құрамына кіретін екінің ең жоғарғы дәрежесіндегі санның екілік коды жазылады (6410 = 26 = 10000002, бұл санды сөз ыңғайлылығы үшін бірінші қадам коды деп аталық);

- келесі қадамда түрлендірілетін саннан анықталған бірінші қадам коды алып тасталады да (75 – 64 = 11), қалған санның құрамына кіретін екінің ең жоғарғы дәрежесіндегі сан анықталады (810 = 23 = 10002, бұл санды екінші қадам коды деп аталық);

- осы тәртіппен жалғастыра отырып, ақырында өзімізге жатталымды кішігірім санның кодына жетеміз (11 – 8 = 3, 310 = 112);

- алынған бірнеше қадам кодтарын қосу арқылы қажетті код шығарылады:

.

.

Сонымен, қосу тәсілі деп аталатын бұл тәсілдің әр қадамында анықталатын кодтардың жазылымы да (1 және бірнеше нөл), олардың ақырында өзара қосылуы да оңай орындалатын операциялар болғандықтан бұл тәсіл арқылы ондық санның екілік кодын анықтау қиын болмайтындығы сөзсіз. Бірақ кейбір жағдайда бұл тәсілді одан әрі жеңілдету мүмкіндігі туады. Мысалы, 1000 санының кодын шығару үшін алдыңғы тәсілді пайдалану алты қадамға созылады (512 + 256 + 128 + 64 + 32 + 8). Алынған сан 512-ден гөрі 1024-ке (210) жуық, сондықтан бұл жерде қажетті кодты шығару үшін 1024 санының кодынан 24-тің кодын алу жеңіл болар еді деген ой туады. Бірақ 1024-тің 10000000000 түріндегі екілік кодынан 24 санының 11000 кодын алу тасымал арқылы жүзеге асырылатындықтан бұл оңай операция емес. 1024-тен 1 кемітілген 1023 санының коды 1111111111 болады және одан 23 санының 10111 кодын алу қиын еместігін осы мысалдың келесі суреттемесінен көреміз:

.

.

Сонымен, алу тәсілі деп аталатын, екінші тәсіл коды ізделінетін ондық санның екінің нақтылы дәрежелі санынан аздап кем болған кезінде пайдалануға ыңғайлы келеді. Ол келесі тәртіппен жүзеге асырылады:

- алдымен алынған ондық саннан аздап жоғары болатын екінің нақтылы дәрежесі арқылы сипатталатын саннан 1 кемітілген санның коды алынады (ол қатар жазылған бірнеше 1 арқылы жазылады және ондағы 1-дің саны дәреже мәніне тең болады):

- бастапқы сан мен алынған кодтың ондық мәнінің айырымы анықталып, келесі қадамда екі тәсілдің ыңғайлысын пайдалану арқылы осы санның коды анықталады;

- ақырында бірінші қадам кодынан екінші қадам коды алынып, қажетті код шығарылады.

Кейбір жағдайда ондық санға сәйкесті қажетті код айтылған екі тәсілді кезектеп пайдалану арқылы алынады.

Керісінше жағдайда, яғни берілген екілік код арқылы оған сәйкесті ондық санды анықтау код жазылымындағы 1 символдарының тұрған разрядтарына сәйкесті құндарын қосу арқылы жүзеге асырылады, оны келесі мысал суреттейді:

1101100012 = 28 + 27 + 25 + 24 + 20 = 256 + 128 + 32 + 16 + 1 = 43310.

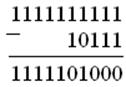

Цифрлық құрылғылардың жұмысы екілік сандарға негізделген, бірақ пайдаланушыға мұндай сандармен жұмыс істеу (мысалы, Ассемблер тілінде бағдарлама құру кезінде) оңай жұмыс емес, сондықтан бұндай жағдайда пайдаланушының жұмысын жеңілдету үшін екілік кодтар оналтылық санау жүйесінде көрсетіледі. Жүйенің аталымына сәйкесті бұл жүйеде сан жазуға (немесе көрсетуге) он алты символ пайдаланылады, олар – 1 … 9, A, B, C, D, E, F.

Ондық санның 16-лық жазылымын, әрине, дәстүрлі тәсілмен, яғни түрлендірілетін санды он алтыға бөліп, шығарылған қалдықтарды кері бағытта жазу арқылы анықтауға болады. Бірақ оны жеңілірек келетін тәсілмен анықтауға болады:

- алдымен ондық санның екілік коды анықталады;

- алынған кодтағы символдар кіші разрядынан бастап төрт-төрттен топтарға біріктіріледі;

- әрбір топтың кодына сәйкесті 16-лық символын қою арқылы түрлендірілетін ондық санның 16-лық жазылымы шығарылады.

Айтылғанды келесі мысал арқылы түсіну қиын емес:

.

.

1.1.2 Екілік сандармен арифметикалық операциялар.

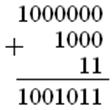

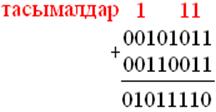

Екілік сандармен қосу операциясының жүргізілуі позициялық санау жүйесінде қабылданған тәртіппен (яғни ондық санау жүйесіндегі сияқты) жүзеге асырылады, оны келесі мысалмен суреттелік:

.

.

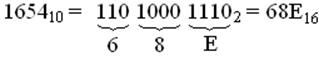

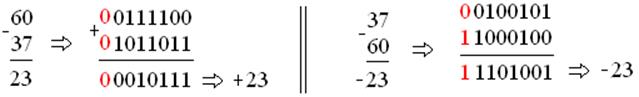

Екілік сандар арасындағы алу операциялары бұл сандардың қосымша кодта қосылуы арқылы жүзеге асырылады. Оң таңбалы екілік санның қосымша коды оның тура кодымен бірдей болады, ал теріс таңбалы екілік санның қосымша коды, оның разрядтарының мәнін терістеп, сосын оған бір қосу арқылы алынады. Қосымша кодпен көрсетілген санның ең артқы разрядының мәні оның таңбасын анықтайды: 0 – оң таңба, 1 – теріс таңба. Алу операциясының орындалымын екі мысалмен суреттелік:

.

.

Көбейту операциялары цифрлық жүйелерде бағдарламалы тәсілмен немесе арнайы құрылғы (аппаратты көбейткіш) арқылы жүзеге асырылады. Бөлу операциясы туралы да соны айтуға болады.

Цифрлық (логикалық) құрылғылардың кірістері мен шығыстарындағы кернеу мәндері логикалық 0 немесе логикалық 1 деп аталатын екі түрлі деңгейде болады. Логикалық құрылғылардың бұл ерекшелігі оларды жобалау үшін немесе осындай дайын құрылғылардың жұмысын талдау үшін логика алгебрасының (немесе Буль алгебрасының) қағидаларын пайдалануға мүмкіндік береді.

Цифрлық құрылғылардың атқарар қызметі сәйкесті логикалық функциялар арқылы сипатталады. Күрделілігі әртүрлі кез келген логикалық функцияны негізгі логикалық функциялар деп аталатын үш функция арқылы суреттеуге болады, олар – ЕМЕС, НЕМЕСЕ, ЖӘНЕ функциялары. Олардың атқарар қызметін кесте түрінде (ол ақиқаттық кестесі деп аталады) немесе сәйкесті логикалық өрнек арқылы суреттеуге болады.

ЕМЕС функциясы – аргументіне қарсы

мәнді шығаратын, бір аргументті функция (1.1 кестені қараңыз),

сондықтан бұл функция инверсия (inversion - терістеу) деп те

аталады. Оның аргументі Х деп белгіленген болса, онда бұл функция Y=![]() өрнегімен суреттеледі.

өрнегімен суреттеледі.

1.1 к е с т е

|

Х |

|

|

0 |

1 |

|

1 |

0 |

![]()

Көп аргументті НЕМЕСЕ функциясы –

аргументтерінің барлығы да 0 кезінде ғана 0 шығаратын,

ал қалған жағдайда (яғни аргументтерінің кем

дегенде біреуінің мәні 1 болғанда) 1 шығаратын, бірнеше

аргументті функция (1.2 кестені қараңыз). Бұл функция

дизъюнкция (disjunction) немесе логикалық қосу (logical addition) деп

те атала береді. Оның логикалық өрнегі Х1![]() Х0

түрінде суреттеледі.

Х0

түрінде суреттеледі.

1.2 к е с т е

|

Х1 |

Х0 |

Х1 |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

![]()

Көп аргументті ЖӘНЕ функциясы –

аргументтерінің барлығы да 1 кезінде ғана 1 шығаратын,

ал қалған жағдайда (яғни аргументтерінің кем

дегенде біреуінің мәні 0 болғанда) 0 шығаратын бірнеше

аргументті функция (1.3 кестені қараңыз). Бұл функция

конъюнкция (conjunction) немесе логикалық көбейту (logical

multiplication) деп те атала береді. Сәйкесті логикалық өрнек

Х1![]() Х0 (немесе Х1Х0) түрінде суреттеледі.

Х0 (немесе Х1Х0) түрінде суреттеледі.

1.3 к е с т е

|

Х1 |

Х0 |

Х1Х0 |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

Суреттелген ЕМЕС, НЕМЕСЕ, ЖӘНЕ функциялары арқылы кез келген күрделі функцияны суреттеуге болады, сондықтан олар логикалық функциялардың түпнегіздік жинағын (core set) құрады.

Қарастырылған үш функциядан

басқа әмбебап функциялар деп аталатын екі функция бар, олар: НЕМЕСЕ-ЕМЕС

және ЖӘНЕ-ЕМЕС функциялары. НЕМЕСЕ-ЕМЕС функциясы Пирс функциясы

деп, ал ЖӘНЕ-ЕМЕС фукциясы Шеффер функциясы деп те атала береді.

Олардың сәйкесті логикалық өрнектері ![]() және

және ![]() түрінде

суреттеледі, ал атқарар қызметі 1.4-кестеде келтірілген.

түрінде

суреттеледі, ал атқарар қызметі 1.4-кестеде келтірілген.

1.4 к е с т е

|

Х1 |

Х0 |

|

|

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

0 |

Соңғы қарастырылған екі функцияның әрбіреуінің жеке өзі-ақ түпнегіздік жинақ құрады, яғни олардың негізінде кез келген күрделі логикалық функция құруға болады.

1.2.3 Теңдік және теңсіздік функциялары.

Ерекше қызметтерге пайдаланылатын

тағы екі функцияны қарастыра кетелік, олар: теңдік (немесе

арифметикалық қосу) функциясы мен теңсіздік функциясы. Олардың

сәйкесті логикалық өрнектері ![]() және

және

![]() түрінде суреттеледі, ал

атқарар қызметі 1.5-кестеде келтірілген.

түрінде суреттеледі, ал

атқарар қызметі 1.5-кестеде келтірілген.

1.5 к е с т е

|

Х1 |

Х0 |

|

|

|

0 |

0 |

0 |

1 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

1.3 Логика алгебрасының заңдары мен заңдылықтары

Цифрлық құрылғылардың сұлбаларын құру барысында оларды суреттеуші логикалық фунцияларды әртүрлі мақсатқа сай (мысалы, оларды қарапайым түрге келтіру үшін) түрлендіру қажет болады. Бұндай түрлендірімдер логика алгебрасының заңдары мен заңдылықтарының негізінде жүргізіледі (1.6 кестені қараңыз).

1.6 к е с т е

|

Заңдар |

|

|

Коммутативтік (commutativity) немесе алмастырылым заңы |

|

|

Х1˅Х0 = Х0˅Х1 |

Х1Х0 = Х0Х1 |

|

Ассоциативтік (associativity) немесе біріктірілім заңы |

|

|

Х2˅ (Х1˅Х0) = (Х2˅Х1) ˅Х0 |

Х2 (Х1Х0) = (Х2Х1)Х0 |

|

Дистрибутивтік (distributivity) немесе таратылым заңы |

|

|

Х2Х1˅Х1Х0 = Х1(Х2˅Х0) |

(Х2˅Х1)(Х1˅Х0) = Х1˅(Х2Х0) |

|

Закон де Моргана |

|

|

|

|

|

Заңдылықтар |

|

|

X˅0 = X |

X˄0 = 0 |

|

X˅1 = 1 |

X˄1 = X |

|

X˅X = X |

X˄X = X |

|

X˅ |

X˄ |

|

X1˅X1X0 = X1 |

X1(X1˅X0) = X1 |

|

X1˅ |

X1( |

|

|

|

Бұл заңдар мен заңдылықтар – симметриялы, яғни олардың дизъюнкциялық және конъюнкциялық түрлері болады. Бұл заңдардың кейбірі дәстүрлі алгебрада қалыптасқан заңдар, сондықтан олардың дұрыстығы күмән тудырмайды, ал дәстүрлі алгебраға тән емес, жаңа заңдар мен заңдылықтардың дұрыстығына көз жеткізу (яғни оларды дәлелдеу) аргументтерінің орындарына олардың сәйкесті мәндерін (0 мен 1) қойып тексеру арқылы жүзеге асырылады.

1.4.1 Күрделі функциялардың көрсетілім түрлері.

Цифрлық құрылғының жұмысы көптеген жағдайда кесте түрінде беріледі. Әрине, оның мәтін түріндегі түсіндірме арқылы да берілуі мүмкін, бұндай жағдайда берілген түсіндірмені кесте түріндегі суреттемеге айналдыру керек болады.

Кесте түрінде сүреттелген функцияның (1.7 кестені қараңыз) логикалық өрнегін жазудың екі түрлі жолы (тәсілі) бар:

- көбейтінділердің қосылымы түрінде, яғни алдымен ЖӘНЕ функцияларын пайдаланып, сосын олардың нәтижесін НЕМЕСЕ функциясымен біріктіру арқылы жазу;

- қосындылардың көбейтілімі түрінде, яғни алдымен НЕМЕСЕ функцияларын пайдаланып, сосын олардың нәтижесін ЖӘНЕ функциясымен біріктіру арқылы жазу.

1.7 к е с т е

|

X2 |

X1 |

X0 |

Y |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

Бірінші тәсіл келесі тәртіппен жүзеге асырылады:

- функцияның (Y) 1 мәнін қабылдайтын аргумент жинақтарының логикалық көбейтінділері жазылады;

- алдыңғы айтылған логикалық көбейтінділерді жазу кезінде 1 мәніндегі аргументтер тура түрінде алынады да, 0 мәніндегі аргументтер теріс түрінде алынады (бұндай жазылымдар конъюнктивті термдер деп аталады);

- жазылған конъюнктивті термдер логикалық қосу функциясы арқылы біріктіріледі.

Кесте түрінде берілген үш аргументті функцияның айтылған тәсілмен жазылған логикалық өрнегі:

|

|

(1.1) |

Енді логикалық өрнектің жазылымының екінші тәсілін қарастыралық, ол келесі тәртіппен жүзеге асырылады:

- функцияның 0 мәнін қабылдайтын аргумент жинақтарының логикалық қосындылары жазылады;

- логикалық қосындыларды жазу кезінде 0 мәніндегі аргументтер тура түрінде алынады да, 1 мәніндегі аргументтер теріс түрінде алынады (бұндай жазылымдар диъюнктивті термдер деп аталады);

- жазылған диъюнктивті термдер логикалық көбейту функциясы арқылы біріктіріледі.

Кесте түрінде берілген үш аргументті функцияның екінші тәсілмен жазылған логикалық өрнегі:

|

|

(1.2) |

1.4.2 Логикалық функцияларды қарапайым түрге келтіру.

Құрылғының жұмысын сипаттаушы логикалық өрнектердің кез келгені арқылы оның сұлбасын құруға болады. Бірақ функция жазылымы күрделі болған сайын, оның сұлбасы да күрделі болатындығын ескеру керек. Демек оларды мүмкіндігінше қарапайым түрге келтіруге тырысу керек болады.

Логикалық функцияларды қарапайым түрге келтіруді (минимизациялауды) тікелей түрлендіру тәсілімен немесе Карна картасы арқылы жүзеге асыруға болады. Логикалық функцияларды тікелей түрлендіру, функция құрамындағы көрші термдерді тауып, оларға логика алгебрасының жоғарыда келтірілген заңдары мен заңдылықтарын тікелей пайдаланып біріктіру арқылы жүргізіледі. Көрші термдерге бір аргументінің ғана айырмашылығы бар термдер жатады. Осы тәсілдің жүзеге асырылымын (1.1) және (1.2) өрнектерінің түрлендірілуін қарастыру арқылы түсінуге болады.

(1.1) өрнегінің түрлендірілімі:

![]()

![]()

![]()

![]()

(1.2) өрнегінің түрлендірілімі:

![]()

![]()

![]()

Логикалық функцияны Карно картасы арқылы минимизациялауды суреттелік. Карно картасы – логикалық өрнектерді минимизациялауға ыңғайландырылған, функцияның кестелі суреттелімінің ерекше түрі. Жоғарыда алынған мысалдағы функцияға құрылған Карно картасы 1.1-суретте келтірілген.

|

|

X1 |

|

||

|

X2 |

0 6 |

1 7 |

1 5 |

1 4 |

|

|

0 2 |

1 3 |

1 1 |

0 0 |

|

|

|

X0 |

|

|

1.1 сурет

Карно картасында көрші термдер бірден көзге түседі: келтірілген картаның 1-, 3-, 5-, 7-ұяшықтарындағы бірліктердің өзара бірігіп, нәтижесінде одан X0 ғана қалатындығы және 4-ұяшықтағы бірліктің тек қана 5-ұяшықтағы бірлікпен бірігетіндігі көрініп тұр.

Төрт аргументті функцияға арналған Карно картасының түрі 1.2-суретте келтірілген.

|

|

X2 |

|

|

||

|

X3 |

12 |

13 |

9 |

8 |

|

|

14 |

15 |

11 |

10 |

X1

|

|

|

|

6 |

7 |

3 |

2 |

|

|

4 |

5 |

1 |

0 |

|

|

|

|

|

X0 |

|

|

|

1.2 сурет

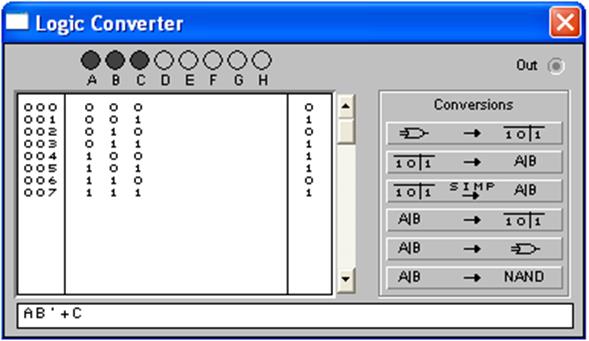

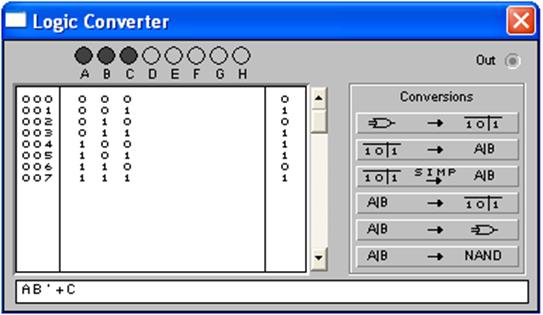

Кесте түрінде берілген функцияны минимизациялауды жүзеге асыруға арналған тағы бір тәсілді (дәлірек айтқанда, аспапты) суреттелік. Цифрлық құрылғыларды модельдеуге арналған бағдарламаларда (мысалы, Electronics Workbench модельдеу жүйесінде) кесте түрінде берілген функцияның толық және минимизацияланған түріндегі өрнектерін (оларға қоса сәйкесті құрылғының сұлбасын да) шығарып бере алатын арнайы түрлендіргіш (Logic Converter) орналастырылған. 1.3-суретте осы аспаптың сыртқы түрі және кесте түрінде берілген функцияның осы аспап арқылы минимизациялануы келтірілген.

1.3 сурет

2 Цифрлық жүйелердің құрылым негіздері

Цифрлық жүйелердің құрамындағы құрылғылар екі түрге бөлінеді, олар: қиыстырма құрылғылар және тізбектеме құрылғылар. Қиыстырма құрылғыларға шығыс сигналы (немесе шығыс сигналдары) құрылғының кіріс сигналдарымен ғана анықталатын құрылғылар жатады, ал тізбектеме құрылғылардың шығыс сигналы (шығыс сигналдары) құрылғының кіріс сигналдарымен қатар, оның алдыңғы жағдайына байланысты анықталады, яғни олардың жадылық қасиеті болады.

Қиыстырма құрылғылардың (іс жүзінде тізбектеме құрылғылардың да) негізін логикалық элементтер құрады.

Логикалық элементтер – логикалық функцияларды жүзеге асыруға арналған құрылғылар. 2.1-суретте бұрын қарастырылған қарапайым функцияларды жүзеге асырушы сәйкесті логикалық элементтердің шартты сызба белгілемелері келтірілген.

|

X1 |

X0 |

NOT |

OR |

AND |

NOR |

NAND |

XOR |

XNOR |

|

|

|

|

|

|

|

|

||

|

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

|

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

2.1 сурет

Цифрлық құрылғыларды құру кезінде олардың нақтылы алгоритмді жүзеге асырушы логикалық құрылымын анықтау мәселелерімен қатар, жалпы сипатты сұлбақұралым мәселелерін шешу қажет болады. Бұндай мәселелердің қатарына, мысалы, құрастырылушы құрылғының жұмыс логикасына сұлбада пайдаланылатын элементтердің уақыттық параметрлерінің ескеру қажеттігі жатады.

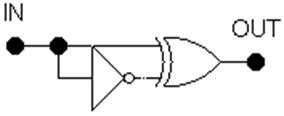

Логикалық элементтер, олардың жағдайының өзгеріс жылдамдығын сипаттаушы, нақтылы тезәрекеттілігімен сипатталады. 2.2-суретте ЕМЕС (NOT) элементі арқылы өзгермелі сигналдардың өту нәтижесі көрсетілген. Бұнда шығыс сигналының өзгерісінің кіріс сигналының өзгерісінен нақтылы уақытқа кідіретіндігі айқын көрініп тұр. Біздің Electronics Workbench модельдеу жүйесінде жүргізген өлшеміміз бойынша ондағы ЕМЕС элементіндегі сигнал кідірісі 10 ns шамасында болады. Әрине, статикалық (яғни белгілі уақыт аралығында тиянақты мәнін сақтайтын) сигналдармен істейтін құрылғылардың жұмысына бұндай кідірістің байқарлықтай әсері болмайды. Бірақ кейбір жағдайларда (мысалы, тізбектеме құрылғыларда) бұндай кідірістің құрылғының жұмысына байқарлықтай әсер етуі мүмкін, демек оны ескеру керек.

2.2 сурет

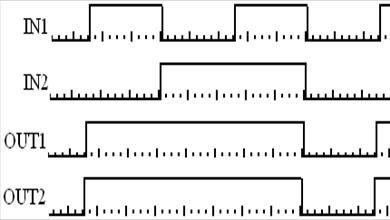

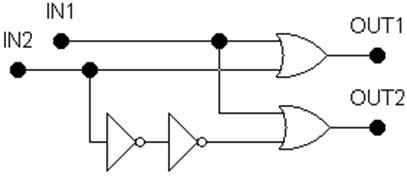

Кідіріс әрекетін суреттеу мақсатында екі ЕМЕС элементінің кірістеріне қатар берілген екі сигналдың осы элементтер арқылы алынған логикалық қосындысын қарастыралық (2.3 суретті қараңыз). Сұлбада көрсетілгендей, бір сигнал екінші элементтің кірісіне екі ЕМЕС элементі арқылы берілген.

2.3 сурет

Идеалды жағдайда (яғни ЕМЕС элементтерінде ешқандай кідірістің болмауы кезінде) екі элементтің шығыстарындағы сигнал (OUT1 және OUT2) бірдей болар еді (2.4, a суретті қараңыз). Бұл диаграмма статикалық сигналдарды бақылауға арналған Electronics Workbench модельдеу жүйесіндегі Logic Analyzer аталымды арнайы аспап арқылы алынған.

|

|

|

|

a |

b |

2.4 сурет

Сезімтал осциллограф арқылы алынған диаграммада (2.4, b суретін қараңыз) екінші элементтің бір кірісіне сигналдың екі ЕМЕС элементінен өтуге кеткен 20 ns кідірісінің әсерінен осы элементтің шығысындағы сигнал құрамына бөгде теріс импульстің қосылғанын көреміз. Сигнал құрамындағы бұндай бөгде импульс осы сигналдың түсетін құрылғысының бағдарланған жұмысын бүлдіруі мүмкін, сондықтан бұндай жағдайдың болмауын қамтамасыз ету керек.

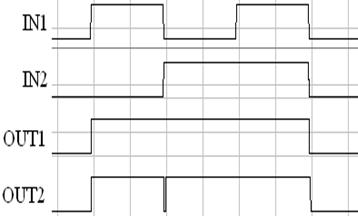

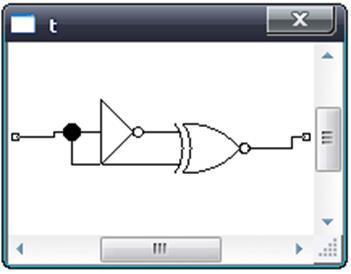

Элементтегі сигнал кідірісін ұтымды пайдалануға да болады. Мысалы, түймежинамның жеке түймесі арқылы өте қысқа (ұзақтығы 10 ns шамасындағы) жазу сигналын алу үшін 2.5-суретте көрсетілген екі элемент арқылы құрылған сұлбаны пайдалануға болады.

|

|

|

|

a |

b |

2.5 сурет

2.2 Цифрлық құрылғылардың шығыс буындары

Логикалық элементтерінің (логикалық элементтер негізінде құрылған күрделі құрылғылардың да) әртүрлі шығыс буындары логикалық шығысты, ашық коллекторлы (құйысты) және үш жағдайлы түрде құрылуы мүмкін. Шығыс буындары әртүрлі логикалық элементтердің қолданылым мүмкіндігі мен қажеттілігін қалыпты логикалық тізбектердегі, магистралды-модулді микропроцессорлық жүйелердегі және т.б. құралымдардағы элементтердің жұмыс шарттарының әртүрлілігімен түсінуге болады.

Логикалық шығысты элементтердің шығыс буындарының сұлбасы екітактілі сұлба бойынша құрылған, бұл, шығыс сигналының алды-артқы ауытқымасын жандандырылған транзисторлар арқылы, яғни олардың шығыс кедергісі шамалы болатын жағдайда, қалыптастыруға мүмкіндік береді.

Логикалық шығысты элементтердің қолданылу кезінде олардың шығыстарын параллель қосуға (әртүрлі жағдайдағы шығыстар арасында “қарама-қайшылық” туу мүмкіндігінен) болмайтындығын ескеру керек.

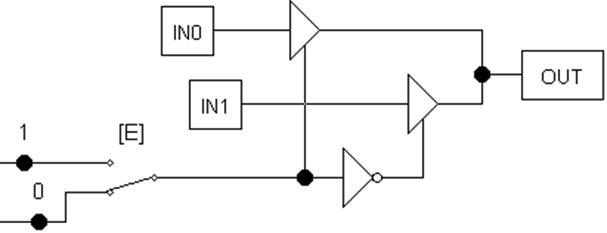

Үш жағдайлы элементтердің (3S) шығысын логикалық 0 және 1 жағдайына қоса, оның шығыс буынының шығыс транзисторларының жабық жағдайын қамтамасыз етуші арнайы басқару сигналымен (ОЕ, Output Enable) үшінші (жоғарыкедергілі) жағдайға қоюға болады. Цифрлық құрылғыларда үш жағдайлы буферлік элементтер арқылы сигналдардың әртүрлі бағытта таралуын қамтамасыз етуге пайдаланылады (2.6 суретті қараңыз). Үш жағдайлы элементтердің шығыстарын параллель қосу үшін кез келген мезетте олардың біреуі ғана жандандырылған жағдайда болуын қамтамасыз ету керек. Осындай үш жағдайлы элементтерді қолдану арқылы магистралды-модулді микропроцессорлық және с.с. жүйелер құруға мүмкіндік туады.

2.6 сурет

Ашық коллекторлы элементтердің (OC) шығыс буынында жүктемелік резистор болмайды. Сондықтан бұндай элементтердің шығыс буынындағы транзистордың жабылуы кезінде жоғарғы деңгейлі кернеу қалыптастыру үшін қорек көзіне жалғанған сыртқы резистор (немесе өзге жүктеме) қосу керек болады.

Осындай бірнеше элементтің шығыстарын, оларды ортақ Ucc - R тізбегіне жалғау арқылы, параллель қосуға болады. Бұл кезде элементтердің (3S элементтеріндегі сияқты олардың біреуі ғана жандандырылған жағдайда, ал қалғандары жабық жағдайда болуын қамтамасыз ету арқылы) ортақ жолға кезек-кезек жұмыс істеуіне мүмкіндік туады. Шығыстары қосылған элементтердің барлығының да жандандырылған жағдайда болуына рұқсат беру арқылы, құрылымды логика деп аталатын, қосымша логикалық операция орындалуына мүмкіндік туады.

3.1 Қиыстырма құрылғыларды құру тәртібі

Қиыстырма құрылғыларды құру келесі тәртіппен жүргізіледі:

- құрылғының сөз-сөйлем түріндегі түсіндірмесінің негізінде оның ақиқаттық кестесі құрылады;

- құрылған кестедегі деректер негізінде құрылғының жұмысын суреттеуші логикалық өрнек жазылады;

- қажетті жағдайда алынған логикалық өрнек минимизацияланады;

- алынған өрнек құрылғыны құруға бағдарланған түпнегіздік жинаққа (core set) сай түрлендіріледі;

- ақырғы алынған өрнек негізінде түпнегіздік жинақтың элементтері арқылы құрылғының сұлбасы құрылады.

Құрылғының қызметі, көптеген жағдайда, кесте түрінде беріледі. Әрине, оны құрылғының жұмыс логикасын сәйкесті сөз-сөйлем түріндегі түсіндірмесі арқылы беріп, оның негізінде сәйкесті кесте құру қиын емес. Сонымен, құрылғының жұмыс логикасы кесте түрінде берілген деп санаймыз (3.1 кестені қараңыз).

3.1 к е с т е

|

X2 |

X1 |

X0 |

Y |

|

X2 |

X1 |

X0 |

Y |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

|

1 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

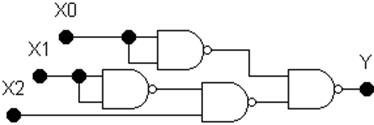

Жоғарыда суреттелген іс-әрекеттерді кезектеп орындау нәтижесінде келесі логикалық өрнектер аламыз (біріншісі – ЕМЕС, ЖӘНЕ, НЕМЕСЕ функцияларының негізінде, екіншісі – ЖӘНЕ-ЕМЕС функцияларының негізінде):

![]()

Берілген құрылғының ЕМЕС, ЖӘНЕ, НЕМЕСЕ элементтерінің негізінде құрылған сұлбасы 3.1, a суретте, ал ЖӘНЕ-ЕМЕС элементтерінің негізінде құрылған сұлбасы 3.1, b суретте көрсетілген.

|

|

|

|

a |

b |

3.1 сурет

Electronics Workbench бағдарламасының құрамындағы арнайы түрлендіргіш (Logic Converter) қиыстырма құрылғының сұлбасын құру кезеңдерін жүзеге асыруға мүмкіндік береді (3.2 суретті қараңыз).

3.2 сурет

3.2 Қалыпты қиыстырма құрылғылар

Күрделі цифрлық құрылғылар, әдетте, қалыпты қызмет атқарушы жеке түрде құрылған қалыпты қызмет түйіндері арқылы құрылады. Цифрлық құрылғылардың қызмет буындары жалпы түрде: қиыстырма және тізбектеме түрлеріне бөлінеді. Осы тарауда қиыстырма түріндегі қалыпты қызмет буындарының (шифратор, дешифратор, мультиплексор, демультиплексор, қосуыш) құрылым принциптері мен жұмыс тәртібі қарастырылады.

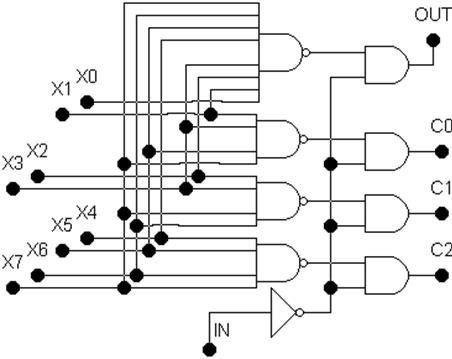

Шифратор (Coder) – сигналға сәйкесті код қалыптастырушы құрылғы. Мысал ретінде сегіз кірісті (X7 … X0) шифратордың сұлбасын құру жолын қарастыралық. Кіріс саны сегіз болғандықтан, ол үшразрядты код (C2 … C0, CODE) қалыптастыру керек және кодтың қалыптасқанын жеке сигнал (O, OUT) арқылы құптауы керек (бұл сигнал қалыптасқан кодты қажетті жады буферіне жазып алуға пайдаланылады). Үлкен құрылымның құрамындағы жеке қызмет буындары, әдетте, кезекпен істейді, бұл олардың іске қосу кірісіне сәйкесті деңгейлі сигнал жіберілуі арқылы жүзеге асырылады. Осындай іске қосу кірісі (I, IN) біздің құрастыратын шифраторда да ескерілгені дұрыс. Тағы бір ескеретін мәселе: қалыпты қызмет буындарының іске қосу кірісі мен құптау шығысындағы сигналдың жандандыру деңгейі төменгі (0) мәнінде алынады. Шифратордың ақпараттық кірістеріне түсетін сигналдардың да жандандыру деңгейі төменгі (0) мәнінде болғаны бұндай құрылғыны іс жүзінде құруға ыңғайлы болады.

Шифратордың келтірілген түсіндірме суреттемесі оның ақиқаттық кестесін құруға толық мәлімет береді, келтірілген түсіндірме мәліметтерінің негізінде сол кестені құрамыз (3.2 кестені қараңыз).

2.1 к е с т е

|

I |

Xi |

C2 |

C1 |

C0 |

O |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

|

2 |

0 |

1 |

0 |

0 |

|

|

3 |

0 |

1 |

1 |

0 |

|

|

4 |

1 |

0 |

0 |

0 |

|

|

5 |

1 |

0 |

1 |

0 |

|

|

6 |

1 |

1 |

0 |

0 |

|

|

7 |

1 |

1 |

1 |

0 |

|

|

1 |

* |

0 |

0 |

0 |

1 |

Кесте деректерінің негізінде жазылған шифратор шығыстарының логикалық өрнектері:

![]() ;

;

![]() ;

;

![]() ;

;

![]()

![]() .

.

Бұл өрнектер, алдымен, НЕМЕСЕ функциялары арқылы жазылып, сосын де Морган заңын пайдалану арқылы ЖӘНЕ-ЕМЕС функциясымен суреттелген түріне түрлендірілді; оған тағы бір себеп – ЖӘНЕ-ЕМЕС элементтерінің олардың ішкі құрылымына байланысты тезәрекеттілігі басқа элементтермен салыстырғанда жоғары болады. 3.3, a-суретте шифратордың жазылған өрнектер негізінде құрылған сұлбасы келтірілген.

Шифратор сұлбада шартты сызба белгілемесімен (3.3, b-суретті қараңыз) көрсетіледі, ал 3.3, с-суретте Electronics Workbench бағдарламасының мүмкіндігін пайдалану арқылы жүзеге асырылған алдыңғы жиналған сұлбаның біріктірілген жеке блок (Subcircuit) түріндегі суреттемесі келтірілген (оның сәйкесті шықпалары олардың келтірілген құрылым сұлбасындағы орналастырылым бағытына сай шығарылған).

|

a |

b |

c |

3.3 сурет

Құрылған шифратордың айта кететін бір кемшілігі бар, оған екі сигнал қатар жіберілген жағдайда оның шығарған коды шым-шытырық бірдеңеге айналып кетеді. Осындай жағдайды болдырмас үшін шифратордың өндірісте шығарылатын микросұлбалары (мысалы, 74148 микросұлбасы), әдетте, мәртебелі түрде құрылады. Яғни олар түскен бірнеше сигналдың белгіленген мәртебесі жоғарғысының кодын шығарады да, қалғандарына көңіл бөлмейді.

3.4 сурет

Көптеген жағдайда таңдап алынған шифратор микросұлбасының өлшемі (кіріс саны) қойылған талапқа сай келмей, оны ұлғайту қажет болады. Мысалы, 74148 микросұлбасы сегіз кірісті мәртебелі шифратор қызметін атқарады. Осындай миросұлбалар негізінде (немесе алдыңғы құрылған сұлбаның жабық түріндегі блогы арқылы) кіріс саны екі есе ұлғайтылған шифратор құруға болады (3.4 суретті қараңыз).

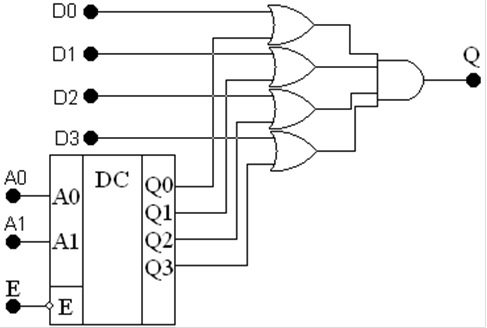

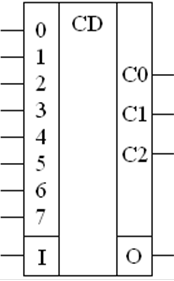

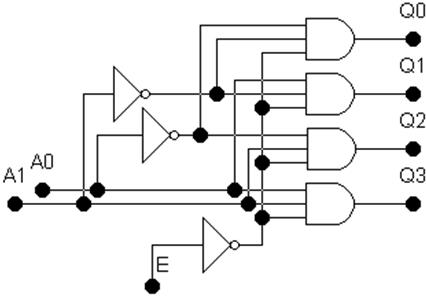

Дешифратор (Decoder) – кірістеріне түскен екілік кодқа сәйкесті шығысында сигнал қалыптастырушы құрылғы. Мысал ретінде төрт теріс шығысты (Q3 … Q0) дешифратордың сұлбасын құру жолын қарастыралық. Шығыс саны төртеу болғандықтан, оның кірісіне түсетін код екіразрядты (A1A0) болады. Дешифратордың іске қосу кірісіндегі (E, Enable) сигналдың жандандыру деңгейін төменгі (0) мәнінде алалық.

Дешифратордың келтірілген түсіндірме суреттемесінің негізінде оның ақиқаттық кестесін (3.3 кестені қараңыз) құрамыз.

3.3 к е с т е

|

E |

A1 |

A0 |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

1 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

1 |

|

|

1 |

0 |

1 |

0 |

1 |

1 |

|

|

1 |

1 |

0 |

1 |

1 |

1 |

|

|

1 |

* |

* |

1 |

1 |

1 |

1 |

Кесте деректерінің негізінде жазылған дешифратор шығыстарының логикалық өрнектері:

![]() ;

;

![]() ;

;

![]()

![]() .

.

3.5, a-суретте дешифратордың жазылған өрнектер негізінде құрылған сұлбасы келтірілген.

Дешифратор сұлбада шартты сызба белгілемесімен (3.5, b-суретті қараңыз) көрсетіледі, ал 3.5, c-суретте оның Electronics Workbench бағдарламасында жиналған сұлбасының біріктірілген жеке блок түріндегі суреттемесі келтірілген.

|

a |

b |

c |

3.5 сурет

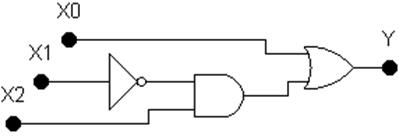

Күрделі логикалық функцияның өрнегінің жазылу тәртібін қарастыру кезінде функцияның алынған логикалық өрнегіне көз салсақ, ондағы әрбір термнің тура сегіз шығысты дешифратордың сәйкесті шығыстарының адресі екендігін көреміз. Демек осындай дешифратордың сәйкесті шығыстарын бескірісті НЕМЕСЕ элементінің кірістеріне жалғау арқылы берілген функцияны жүзеге асыруға болады. Егер дешифратор теріс шығысты болса, онда бұл өрнекті Морган заңы арқылы түрлендіреміз:

![]() .

.

Алынған өрнектен берілген құрылғының қызметін теріс шығысты дешифратор негізінде жүзеге асыру үшін оның сәйкесті шығыстарына бескірісті ЖӘНЕ-ЕМЕС элементін жалғау жеткілікті екендігі көрініп тұр (3.6 суретті қараңыз).

3.6 сурет

Қиыстырма құрылғының сұлбасын дешифратор арқылы құру – аса ыңғайлы тәсіл: біріншіден, логикалық өрнекті минимизациялаудың қажеті жоқ (дәлірек айтқанда, өрнектің өзінің де қажеті жоқ, себебі дешифратор қай шығыстарының біріктірілетінін кестеден-ақ түсінікті), екіншіден, жалғыз дешифратор негізінде қатарынан бірнеше функцияны жүзеге асыруға болады.

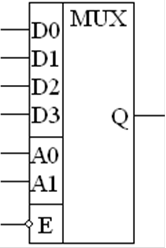

Мультиплексор (Multiplexer) – ақпараттық сигналдардың түскен адрестік кодқа сәйкесті біреуін шығысына қосылған құрылғыға бағыттаушы құрылғы. Бұл анықтамаға сәйкесті мультиплексордың екі кірістер тобы ажыратылады, олар: ақпараттық және адрестік кірістері, әрине, оның іске қосылу кірісі де болу керек.

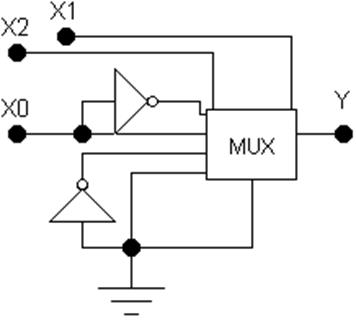

Мультиплексордың дешифратор арқылы жүзеге асырылған сұлбасы мен шартты сызба белгілемесі 3.7-суретте келтірілген.

|

|

|

|

a |

b |

3.7 сурет

Бірнеше мультиплексорды қатар қосу арқылы бірнешеразрядты (мысалы, сегізразрядты) сөздердің біреуін бір арнаға жіберу жұмысын атқаратын мультиплексорлық құрылым құру қиын емес, бұндай құрылым арналы мультиплексор деп аталады.

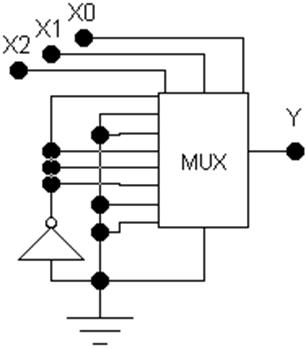

Мультиплексор негізінде де қиыстырма құрылғының жұмысын жүзеге асыруға болады, оның екі жолын (тәсілін) қарастырамыз.

Бірінші тәсіл мультиплексордың адрестік кірістерінің саны жүзеге асырылатын функцияның аргументтерінің санымен бірдей болған жағдайда қолданылады. Бұл жағдайда мультиплексордың ақпараттық кірістері функцияның сәйкесті аргументтер жинағындағы мәндеріне сәйкесті қойылады да, оның адрестік кірістеріне аргумент мәндеріне сәйкесті сигналдар беріледі. 3.4-кестеде берілген функцияның осы тәсілмен сегіз кірісті мультиплексор негізінде құрылуы 3.8, a-суретте көрсетілген. Бұнда пайдаланылған сәйкесті қосалқы сұлбаның ақпараттық кірістері – оның сол жағына, ал адрестік кірістері оң жағына шығарылған.

3.4 к е с т е

|

X2 |

X1 |

X0 |

Y |

|

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

0 |

|

|

|

|

a |

b |

3.8 сурет

Екінші тәсіл функцияны адрестік кірістерінің саны аргументтер санынан кем болатын мультиплексор арқылы құру қажеттігінде қолданылады. Бұл жағдайда мультиплексордың адрестік кірістеріне аргументтердің бір бөлігіне сәйкесті сигналдар беріледі де, ал қалғаны мультиплексордың ақпараттық кірістерін баптауға пайдаланылады. Келтірілген функцияның осы тәсілмен төрт кірісті мультиплексор негізінде құрылуы 3.8, b-суретте көрсетілген.

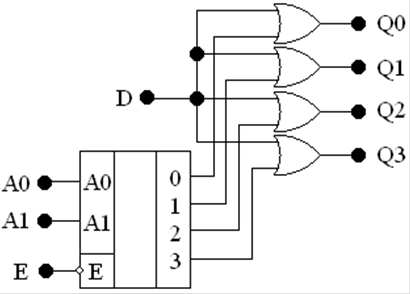

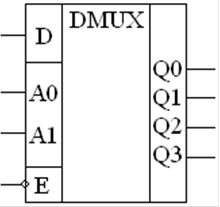

Демультиплексор (Demultiplexer) – дерек кірісіндегі сигналды сілтеу коды арқылы анықталған шығысына жіберетін құрылғы. Демультиплексордың дешифратор арқылы құрылған сұлбасы мен оның сәйкесті шартты сызба белгілемесі 3.5-суретте келтірілген.

|

|

|

|

a |

b |

3.5 сурет

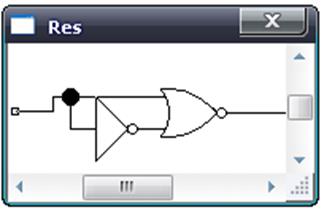

3.2.5 Қосу құрылғылары.

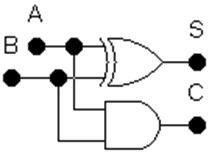

Қосуыштар – сандарды арифметикалық қосуға арналған құрылғылар. Көпразрядты сандарды қосу бірнеше бірразрядты қосуыштар арқылы жүзеге асырылады. Сондықтан, алдымен, сол бірразрядты қосуыштартардың құрылым принциптерін қарастырамыз.

Екі бірразрядты санды қосу кезінде олардың қосынды нәтижесі (S, Sum) мен келесі разрядқа жіберілетін тасымал (C, Carry) шығарылу керек, демек оның жұмысын 3.5-кестемен суреттеуге болады.

3.5 к е с т е

|

A |

B |

S |

C |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

Кесте деректері негізінде жазылған құрылғы шығыстарының логикалық өрнектері:

![]() ;

; ![]() .

.

Осы өрнектердің негізінде құрылған қосуыштың сұлбасы мен оның сәйкесті біріктірмесі 3.10, a-суретте келтірілген.

|

|

|

|

|

|

a |

b |

||

3.10 сурет

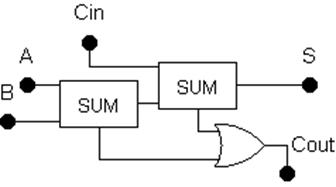

Бұл қосуыш көпразрядты сандардың бірінші разрядтарын қосуға ғана жарайды (сондықтан ол жартылай қосуыш деп аталады), ал оның қалған разрядтарға жарауы үшін оның алдыңғы разрядтан түскен тасымалды да қосатын мүмкіндігі болу керек. Толық қосуыштың жартылай қосуыштар арқылы құрылған сұлбасы мен оның сәйкесті біріктірмесі 3.10, b-суретте келтірілген.

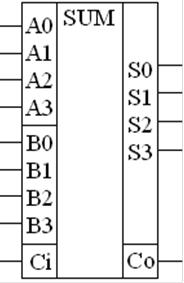

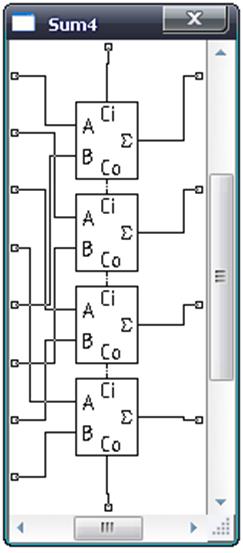

Көпразрядты қосуыштарды суреттелген толық қосуыштар арқылы құру қиын емес. 3.11-суретте төртразрядты қосуыштың сұлбасы, біріктірме блогы және шартты сызба белгілемесі келтірілген.

|

|

|

|

|

a |

b |

c |

3.11 сурет

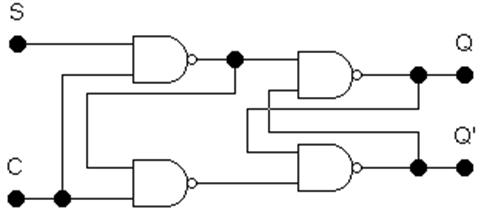

Шығыс сигналы (немесе сигналдары) кіріс сигналдарының кезекті мәндеріне және өзінің алдыңғы (кейде одан бұрынғы да) жағдайына байланысты анықталатын құрылғылар тізбектеме құрылғылар деп аталады. Демек бұндай құрылғылардың бұрынғы жағдайын есте сақтайтын мүмкіндігі, яғни оның құрамында жады элементтері болу керек. Сондықтан, алдымен, жады элементтерінің (триггерлердің) түрлерімен және олардың құрылымы мен жұмыс принциптерімен танысамыз.

Триггерлер – екі тиянақты жағдайы бар бірразрядты екілік сан сақтауға арналған құрылғылар. Оның тиянақты жағдайларының біреуі лог.1-ге, екіншісі лог.0-ге сәйкес келеді. Әдетте, триггерлік құрылымның қарама-қарсы деңгейлі (тура және теріс деп аталатын) екі шығысы болады, триггердің жағдайы оның тура шығысындағы сигнал деңгейімен анықталады.

Ақпараттың енгізілу (жазылу) тәртібіне байланысты триггерлер асинхронды және синхронды болып бөлінеді.

4.1.1 Асинхронды RS-триггерлер.

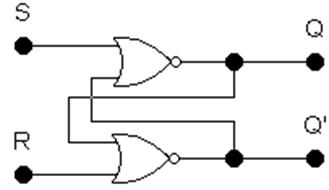

Асинхронды триггерлердің жаңа жағдайға ауысуы тікелей олардың кірісіне берілетін ақпараттық сигналдардың өзгерісімен ғана анықталады. Оларды НЕМЕСЕ-ЕМЕС немесе ЖӘНЕ-ЕМЕС элементтерінің негізінде құруға болады. Асинхронды триггердің НЕМЕСЕ-ЕМЕС элементтерінің негізінде құрылған сұлбасы 4.1, a-суретте келтірілген.

|

|

|

|

a |

b |

4.1 сурет

Бұл құрылымның жұмысын 4.1-кестедегі жазылым ретімен талқылау арқылы қарастырамыз.

4.1 к е с т е

|

|

R |

S |

Q |

Q’ |

|

1 |

0 |

0 |

? |

? |

|

2 |

1 |

0 |

1 |

|

|

3 |

0 |

1 |

1 |

|

|

4 |

1 |

1 |

0 |

|

|

5 |

0 |

1 |

0 |

|

|

6 |

1 |

1 |

0 |

0 |

|

7 |

0 |

0 |

??? |

??? |

Кестенің бірінші жолында – R = 0, S = 0; екі элементтің де бір кірісінде 0 тұр, ал олардың кері байланыстық кірістерінде қарастырылым басында қандай сигнал тұрғаны белгісіз, демек құрылым шығыстарындағы (Q және Q’) сигнал деңгейлері де белгісіз.

Кестенің екінші жолында – R = 1, S = 0; жоғарғы элементтің бір кірісінде лог.1 тұрғандықтан, бұл элементтің жұмыс логикасына сәйкесті, оның шығысында (Q) лог.0 деңгейлі сигнал туады да, ол кері байланыс жолы арқылы төменгі элементтің екінші кірісіне түседі, нәтижесінде оның шығысында (Q’) лог.1 деңгейлі сигнал туады; сонымен, бұл жағдайда триггер лог.0 жағдайына келтіріледі (яғни оған 0 жазылады).

Кестенің үшінші жолында – R = 0, S = 0; жоғарғы элементтің R кірісіндегі сигнал деңгейі өзгергенмен, оның екінші кірісінде (құрылымның Q’ шығысына жалғанған) лог.1 деңгейі тұрғандықтан, бұл элементтің шығысындағы сигнал деңгейі алдыңғы лог.0 деңгейінде қалады, демек триггердің жағдайы өзгермейді.

Кестенің төртінші жолында – R = 0, S = 1; төменгі элементтің бір кірісінде лог.1 тұрғандықтан, оның шығысында (Q’) лог.0 деңгейлі сигнал туады да, ол кері байланыс жолы арқылы жоғарғы элементтің екінші кірісіне түседі, нәтижесінде оның шығысында (Q) лог.1 деңгейлі сигнал туады; сонымен, бұл жағдайда триггер лог.1 жағдайына келтіріледі (яғни, оған 1 жазылады).

Кестенің бесінші жолында – R = 0, S = 0; төменгі элементтің S кірісіндегі сигнал деңгейі өзгергенмен, оның құрылымның Q шығысына жалғанған кірісінде лог.1 деңгейі тұрғандықтан, бұл элементтің шығысындағы сигнал деңгейі алдыңғы лог.1 деңгейінде қалады, демек триггердің алдыңғы жағдайы сақталады.

Құрылымның қарастырылған жағдайларынан келесі қорытынды шығаруға болады: R = 1, S = 0 берілу жағдайы триггердің 0 жазу режиміне, R = 0, S = 1 жағдайы триггердің 1 жазу режиміне, ал R = 0, S = 0 жағдайы триггердің жазылған санды сақтау режиміне сәйкес келеді.

Триггердің кірістеріне R = 1, S = 1 берілген кезде (алтыншы жол) екі элементтің де шығыстарында лог.0 деңгейлі сигнал туады да, триггер сақтау режиміне ауыстырылғанда (жетінші жол), триггердің қай жағдайға тиянақталатындығы – кездейсоқ оқиға. Демек бұндай жағдайды тудырмас үшін, қарастырылған триггердің кірістеріне R = 1, S = 1 берілмеуі керек, сондықтан бұл жағдай триггердің тыйым салынған режимі деп аталады.

Сонымен, қарастырылған триггердің жұмыс режимдерін 4.2-кесте түрінде суреттеуге болады.

4.2 к е с т е

|

R |

S |

Q |

Q’ |

Жұмыс режимдері |

|

0 |

0 |

Q0 |

Q0’ |

Сақтау режимі |

|

0 |

1 |

1 |

0 |

‘1’ жазу режимі |

|

1 |

0 |

0 |

1 |

‘0’ жазу режимі |

|

1 |

1 |

– |

– |

Тыйым салынған режим |

Қарастырылған триггердің жазу режимдері сәйкесті ақпараттық сигналдардың (S – Set, R – Reset) бірлік деңгейімен жүзеге асырылатын-дығына байланысты бұндай триггер тура кірісті триггер деп аталады. Оның шартты сызба белгілемесі 4.1, b-суретте келтірілген.

ЖӘНЕ-ЕМЕС элементтерінің негізінде құрылған асинхронды триггердің сұлбасы 4.2, a-суретте келтірілген.

|

|

|

|

a |

b |

4.2 сурет

Бұл құрылымның жұмысын 4.3-кестедегі жазылым ретімен қарастырамыз.

4.3 к е с т е

|

|

R |

S |

Q |

Q’ |

|

1 |

1 |

1 |

? |

? |

|

2 |

0 |

0 |

1 |

|

|

3 |

1 |

0 |

1 |

|

|

4 |

0 |

1 |

0 |

|

|

5 |

1 |

1 |

0 |

|

|

6 |

0 |

0 |

1 |

1 |

|

7 |

1 |

1 |

??? |

??? |

Кестенің бірінші жолында – R = 1, S = 1; екі элементтің де бір кірісінде 1 тұр, ал олардың кері байланыстық кірістерінде қарастырылым басында қандай сигнал тұрғаны белгісіз, демек құрылым шығыстарындағы (Q және Q’) сигнал деңгейлері де белгісіз.

Кестенің екінші жолында – R = 0, S = 1; төменгі элементтің бір кірісінде лог.0 тұрғандықтан, бұл элементтің жұмыс логикасына сәйкесті, оның шығысында (Q’) лог.1 деңгейлі сигнал туады да, ол кері байланыс жолы арқылы жоғарғы элементтің екінші кірісіне түседі, нәтижесінде оның шығысында (Q) лог.0 деңгейлі сигнал туады; сонымен, бұл жағдайда триггер лог.0 жағдайына келтіріледі (яғни оған 0 жазылады).

Кестенің үшінші жолында – R = 1, S = 1; төменгі элементтің R кірісіндегі сигнал деңгейі өзгергенмен, оның құрылымның Q шығысына жалғанған кірісінде лог.0 деңгейі тұрғандықтан, бұл элементтің шығысындағы сигнал деңгейі алдыңғы лог.1 деңгейінде қалады, демек триггердің жағдайы өзгермейді.

Кестенің төртінші жолында – R = 1, S = 0; жоғарғы элементтің бір кірісінде лог.0 тұрғандықтан, оның шығысында (Q) лог.1 деңгейлі сигнал туады да, ол кері байланыс жолы арқылы төменгі элементтің екінші кірісіне түседі, нәтижесінде оның шығысында (Q’) лог.0 деңгейлі сигнал туады; сонымен, бұл жағдайда триггер лог.1 жағдайына келтіріледі (яғни, оған 1 жазылады).

Кестенің бесінші жолында – R = 1, S = 1; жоғарғы элементтің S кірісіндегі сигнал деңгейі өзгергенмен, оның құрылымның Q’ шығысына жалғанған кірісінде лог.0 деңгейі тұрғандықтан, бұл элементтің шығысындағы сигнал деңгейі алдыңғы лог.1 деңгейінде қалады, демек триггердің алдыңғы жағдайы сақталады.

Құрылымның қарастырылған жағдайларынан келесі қорытынды шығаруға болады: R = 0, S = 1 берілу жағдайы триггердің 0 жазу режиміне, R = 1, S = 0 жағдайы триггердің 1 жазу режиміне, ал R = 1, S = 1 жағдайы триггердің жазылған санды сақтау режиміне сәйкес келеді.

Триггердің кірістеріне R = 0, S = 0 берілген кезде (кестенің алтыншы жолы) екі элементтің де шығыстарында лог.1 деңгейлі сигнал туады да, триггер сақтау режиміне ауыстырылғанда (кестенің жетінші жолы), триггердің қай жағдайға тиянақталатындығы кездейсоқ оқиға. Демек бұндай жағдайды тудырмас үшін, қарастырылған триггердің кірістеріне R = 0, S = 0 берілмеуі керек, сондықтан бұл жағдай триггердің тыйым салынған режимі болады.

Сонымен, қарастырылған триггердің жұмыс режимдерін 4.4-кесте түрінде суреттеуге болады.

4.4 к е с т е

|

R |

S |

Q |

Q’ |

Жұмыс режимдері |

|

0 |

0 |

– |

– |

Тыйым салынған режим |

|

0 |

1 |

1 |

0 |

‘0’ жазу режимі |

|

1 |

0 |

0 |

1 |

‘1’ жазу режимі |

|

1 |

1 |

Q0 |

Q0’ |

Сақтау режимі |

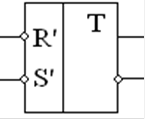

Қарастырылған триггердің жазу режимдері сәйкесті ақпараттық сигналдардың (S – Set, R – Reset) нөлдік деңгейімен жүзеге асырылатын-дығына байланысты бұндай триггер теріс кірісті триггер деп аталады. Оның шартты сызба белгілемесі 4.2, b-суретте келтірілген.

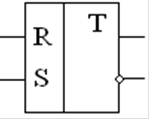

Енді синхронды триггерлерді қарастыралық. Синхронды триггерлердің жаңа жағдайға ауысуы арнайы басқару сигналымен жүзеге асырылады, әрине, оның қай жағдайға ауысатындығы ақпараттық сигналдарға байланысты анықталады. Басқару сигналын қабылдау тәсіліне байланысты синхронды триггерлер статикалы басқарылымды және динамикалы басқарылымды түрлеріне ажыратылады.

Статикалы басқарылымды (яғни деңгей арқылы басқарылатын) RS-триггердің сұлбасын теріс кірісті асинхронды RS-триггерге екі ЖӘНЕ-ЕМЕС элементінен тұратын басқару сұлбасын қосу арқылы жүзеге асыруға болады (4.3, a-суретті қара).

|

|

|

|

a |

b |

4.3 сурет

Бұл триггердің жұмыс режимдері 4.5-кестеде суреттелген.

4.5 к е с т е

|

С |

R |

S |

Q |

Q’ |

Жұмыс режимдері |

|

0 |

x |

x |

Q0 |

Q0’ |

Сақтау режимі |

|

1 |

0 |

0 |

– |

– |

Сақтау режимі |

|

0 |

1 |

1 |

0 |

‘1’ жазу режимі |

|

|

1 |

0 |

0 |

1 |

‘0’ жазу режимі |

|

|

1 |

1 |

Q0 |

Q0’ |

Тыйым салынған режим |

C = 0 кезінде триггер сақтау режимінде болады. Триггердің R мен S кірістеріндегі сигнал деңгейлеріне сәйкесті жағдайға ауысуы С = 1 кезінде жүзеге асырылады. Синхронды RS-триггердің шартты сызба белгілемесі 4.3, b-суретте келтірілген.

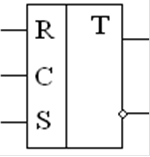

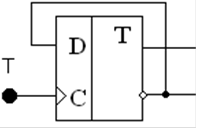

Статикалы басқарылымды D-триггердің (Delay – кідіріс) сұлбасы мен шартты сызба белгілемесі 4.4-суретте келтірілген, ал оның жұмыс режимдері 4.6-кестеде суреттелген.

|

|

|

|

a |

b |

4.4 сурет

4.6 к е с т е

|

С |

D |

Q |

Q’ |

Жұмыс режимдері |

|

0 |

x |

Q0 |

Q0’ |

Сақтау режимі |

|

1 |

0 |

0 |

1 |

‘0’ жазу режимі |

|

1 |

1 |

0 |

‘1’ жазу режимі |

Бұдан әрі динамикалы басқарылатын триггерлердің үш түрін қарастырамыз, олар – D-триггер, JK-триггер және T-триггер.

Динамикалы басқарылатын триггерлердің жағдайының ауыстырылуы басқару сигналының сәйкесті (тура немесе теріс) ауытқымасымен жүзеге асырылады. Динамикалы басқарылатын триггерлер, әдетте, үштриггерлі құрылым негізінде құрылады. Олардың сұлбақұралымына көңіл аудармай-ақ, жұмыс режимдерімен ғана танысамыз.

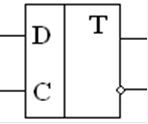

Динамикалы басқарылымды D-триггердің шартты сызба белгілемесі 4.5, a-суретте келтірілген, ал оның жұмыс режимдері 4.7-кестеде суреттелген.

|

|

|

|

a |

b |

4.5 сурет

4.7 к е с т е

|

С |

D |

Q |

Q’ |

Жұмыс режимдері |

|

|

0 |

0 |

1 |

Сақтау режимі |

|

1 |

1 |

0 |

Жазу режимі |

Бұл триггердің жағдайының ақпараттық сигналдың мәніне (D) сәйкесті ауысуы басқару сигналының тура ауытқу (0-ден 1-ге) мезетінде жүзеге асырылады. Оның шартты сызба белгілемесінде басқару сигналының ауытқу бағыты сәйкесті бағыттама түрінде бейнеленеді.

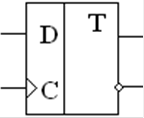

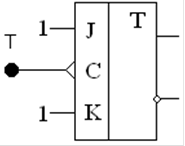

JK-триггердің төрт түрлі жұмыс режимі бар (4.8-кестені қараңыз): оның үш режимі (‘0’ жазу, ‘1’ жазу, сақтау) RS-триггердегі сияқты, ал төртінші режим санау режимі деп аталады, бұл режимде триггер кезекті жағдайынан қарсы жағдайға ауысады. JK-триггердің келтірілген жұмыс кестесінде және оның шартты сызба белгілемесінде (4.5, b-суретті қараңыз) оның жағдайын ауыстыруы басқару сигналының теріс ауытқу (1-ден 0-ге) мезетінде жүзеге асырылатындығы сәйкесті бағыттау белгілерімен суреттеледі.

4.8 к е с т е

|

С |

J |

K |

Q |

Q’ |

Жұмыс режимдері |

|

|

0 |

0 |

Q0 |

Q0’ |

Сақтау режимі |

|

0 |

1 |

0 |

1 |

‘0’ жазу режимі |

|

|

1 |

0 |

1 |

0 |

‘1’ жазу режимі |

|

|

1 |

1 |

Q0’ |

Q0 |

Санау режимі |

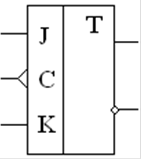

T-триггер – санау режимінде істейтін триггер. T-триггердің қызметін жүзеге асыру үшін D-триггер мен JK-триггердің қосылым тәртібі 4..6-суретте келтірілген.

|

|

|

|

a |

b |

4.6 сурет

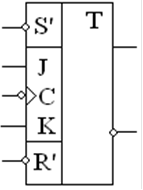

Микросұлба түрінде D-триггерлер мен JK-триггерлер шығарылады. Бұл микросұлбаларда ақпараттық және басқару сигналдарын енгізу шықпаларымен қатар, бастапқы қойылым сигналдарының (R, S) шықпалары орналастырылады (4..7 суретті қараңыз). Бұл кірістерге берілетін асинхронды сигналдардың мәртебесі басқа сигналдарға қарағанда жоғары болады.

|

|

|

|

a |

b |

4.7 сурет

4.2 Регистрлер

Регистр – көпразрядты екілік сан сақтауға арналған құрылғы. Олар триггерлердің (мысалы D-триггерлердің) негізінде құрылады. Әрине, регистр құрамындағы триггерлердің саны регистрдің разряд санымен анықталады. Регистрге санның енгізілу тәртібіне байланысты олардың тізбекті және параллель регистр деп аталатын түрлері болады.

Тізбекті регистрде әрбір триггердің шығысы келесі триггердің ақпараттық кірісіне жалғанады. Бірнешеразрядты екілік сан түріндегі сөздің разряд мәндері бір-бірлеп бірінші триггерге тактілік сигналдың сәйкесті ауытқуында енгізіледі де, осы мезетте триггерлердегі бұрынғы енгізілген разряд мәндері бір триггерден келесі триггерге ығысып отырады. Әрине, бүкіл сөзді енгізу үшін, оның қанша разряды болса, сонша тактілік сигнал қажет болады.

Параллель регистрдің триггерлерінің ақпараттық кірістеріне сөз разрядтарының мәндері қатар беріліп, олар регистрге жалғыз тактілік сигнал арқылы енгізіледі.

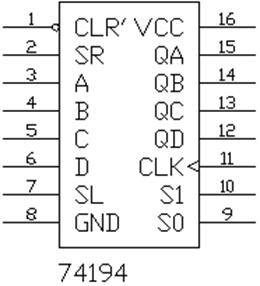

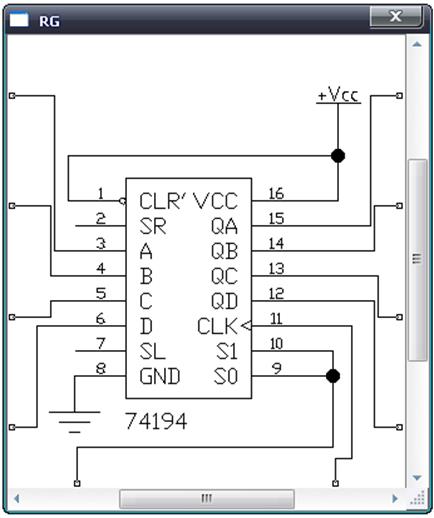

Екі түрлі енгізу тәсілі қамтылған әмбебап регистрлер де болады. Осындай әмбебап регистрдің мысалы ретінде 74194 аталымды төртразрядты регистрдің сызба белгілемесі келтірілген (4.8 суретті қараңыз).

Оның шықпаларының (яғни, оларға берілетін сигналдардың) қызметі:

- VCC, GND – қорек көзі мен жердің қосылатын шықпалары;

- A, B, C, D – ақпаратты параллель енгізу шықпалары;

- QA, QB, QC, QD – регистрдің шығыстары;

- SR – солға ығыстыру кезіндегі ақпарат енгізу шықпасы;

- SL – оңға ығыстыру кезіндегі ақпарат енгізу шықпасы;

- S1, S0 – регистрдің жұмыс режимдерін анықтаушы сигналдардың шықпалары: S1 = 0, S0 = 0 – сақтау режимі; S1 = 0, S0 = 1 – солға ығыстыру режимі; S1 = 1, S0 = 0 – оңға ығыстыру режимі; S1 = 1, S0 = 1 – параллель енгізу режимі;

- CLK – тактілік сигналдың шықпасы;

- CLR’ – тазарту сигналының шықпасы.

4.8 сурет

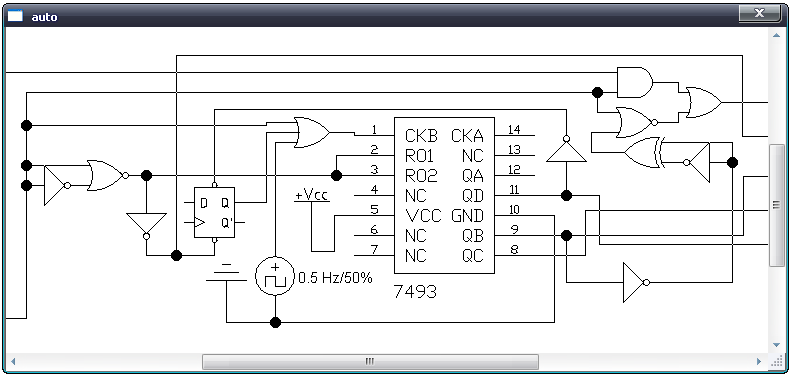

Санауыш – импульстердің әрбір сәйкесті ауытқымасында құрамындағы санды бірге өзгертіп отыратын құрылғы. Құрамындағы санның өзертілу бағытына байланысты тура теріс және әмбебап санауыштар болады. Санауыштар T-триггерлердің негізінде құрылады.

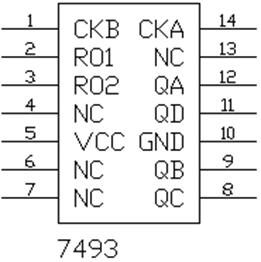

Қарапайым санауыштың мысалы ретінде Electronics Workbench бағдарламасының элементтер қорындағы 7493 аталымды төртразрядты санауыш микросұлбасының белгілемесі көрсетілген (4.9, a-суретті қараңыз).

|

|

|

|

a |

b |

4.9 сурет

Оның құрамында бірразрядты және үшразрядты санауыштар орналастырылған. Бұл микросұлбаның шықпаларының қызметі:

- VCC, GND – қорек көзі мен жердің қосылатын шықпалары;

- CKA, QA – бірразрядты санауыштың кірісі мен шығысы;

- CKB, QB, QC, QD – үшразрядты санауыштың кірісі мен шығыстары;

- R01, R02 – санауыштарды тазарту сигналының шықпасы.

Бұл микросұлбаның құрамындағы санауыштарды жеке түрінде де, оларды бір-біріне жалғап, төртразрядты санауыш ретінде де пайдалануға болады.

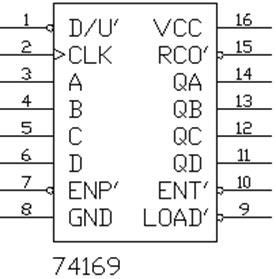

Әмбебап санауыштың мысалы ретінде Electronics Workbench бағдарламасының элементтер қорындағы 74169 аталымды төртразрядты санауыштың сызба белгілемесі көрсетілген (4.9, b-суретті қараңыз).

Бұл микросұлбаның шықпаларының қызметі:

- VCC, GND – қорек көзі мен жердің қосылатын шықпалары;

- A, B, C, D – ақпараттың параллель енгізілу кірістері;

- LOAD’ – ақпаратты параллель енгізу сигналының кірісі;

- QA, QB, QC, QD – санауыштың шығыстары;

- D/U’ – санау бағытын анықтаушы сигнал шықпасы;

- ENP’, ENT’ – санауышты іске қосу сигналдарының кірістері;

- CLK – тактілік сигналдың кірісі;

- RCO’ – санау шегіне жету сигналы.

Жады құрылғылары (өзгеше айтқанда, жадылық құрылғылар), олардың орналастырылған цифрлық жүйелерінде, ақпарат сақтау қызметін атқарады. Цифрлық жүйелердің құрамына, олардың атқаратын қызметіне байланысты жады құрылғыларының бірнеше түрі енгізілуі мүмкін, олар: микропроцессорлардың құрама бөлігі ретіндегі регистрлік жады; цифрлық жүйенің тезәрекеттілігін көтеруге мүмкіндік беретін кэш-жады; процессормен тікелей дерек алмастыру режимінде жұмыс атқарушы және онымен тезәрекеттілігі жағынан келістірілген негізгі жады (қызмет жадысы, тұрақты жады); үлкен көлемді ақпарат сақтауға арналған сыртқы жады және т.б.

5.1 Жады құрылғыларының сипаттамалары

Жады құрылымдарының жұмыс мүмкіндігін сипаттаушы негізгі параметрлері:

- ақпараттық сыйымдылығы – сақталатын ақпараттың ең жоғарғы көлемі. Ол бит, байт немесе бірнеше байттан тұратын, сөз санымен сипатталады. Бұл параметр, көбінесе сақталатын сөз санының олардың разряд санына көбейтіндісі түрінде сипатталады;

- тезәрекеттілігі – оқу, жазу операцияларының және оқу/жазу циклінің ұзақтығымен бағаланады. Оқу (немесе жазу) уақыты – басқару (оқу/жазу) сигналының берілген мезетінен сәйкесті операцияның орындалып біткеніне дейінгі уақыт аралығы. Оқу/жазу циклінің ұзақтығы – тізбелі жүргізілетін операциялардың минималды уақыт аралығы.

Қазіргі заманғы сөз тобымен (бумасымен) жұмыс істейтін жады құрылымдарында айтылған дәстүрлі параметрлермен қатар бастапқы байланыс уақыты (Latency) және буманың келесі сөздерінің жіберілім қарқыны (Bandwidth) аталымды жаңа параметрлер енгізілген.

Келтірілген динамикалық параметрлермен қатар, бірнеше басқару сигналының өзара орналасымы мен олардың ұзақтығын анықтаушы режимдік параметрлер де бар.

Жадылық құрылғылардың жұмысы келесі сигналдармен басқарылады:

- A (Address) – адрес, оның разрядтылығы (n) жады құрылымының ұяшық санымен (N) анықталады. Жады құрылымының ұяшық саны, әдетте, екінің тұтас мәнді дәрежесімен сипатталады. Адрес разрядтылығы жадының ұяшық санына n =log2N қатынасымен байланысты;

- CS (Chip Select) немесе CE (Chip Enable) – микросұлбаны таңдау немесе іске қосу сигналы;

- R/W (Read/Write) – сәйкесті операцияны орындату сигналы;

- DI (Data Input) және DO (Data Output) – кіріс және шығыс деректерінің сигналдары жүретін желілер. Кейбір жады құрылымдарында олар біріктірілген түрінде пайдаланылады.

Деректерге шығу тәсіліне қарай жады құрылғыларының сілтеу арқылы шығарылымды, тізбекті шығарылымды және танымалды шығарылымды түрлері ажыратылады.

Сілтеу арқылы шығарылым кезінде жады құрылғысының адрестік кірістеріндегі код дерек адмастырылуы жүргізілетін ұяшықты көрсетеді. Бұндай жады құрылғылары аса дамығандығына байланысты жадының өзге түрлері осылардың негізінде құрылады.

Сілтеу арқылы шығарылымды жады құрылғылары өз кезегінде RAM (Random Access Memory) және ROM (Read Only Memory) түрлеріне бөлінеді. RAM түрлі жады құрылғыларда кезекті бағдарламаның орындалуы кезіндегі алмасуға қатысты кез келген уақытта өзгеретін деректер сақталады. Олардың құрамындағы жады элементтері қорек көзіне тәуелді болады.

RAM түрлі ЖҚ-лар құрамындағы жады элементтерінің түріне қарай статикалық (SRAM) және динамикалық (DRAM) болып бөлінеді. Оның біріншісінде жады элементтері ретінде триггерлер пайдаланылады, сондықтан олардың тезәрекеттілігі жоғары болады, ал екіншісінде деректер МТШ-құрылымның элементтері арқылы құрылған конденсаторлардың зарядтары түрінде сақталады. Конденсаторлардың өздігінен зарядсыздануы деректерді жояды, сондықтан олардың қайта-қайта (әрбір миллисекунд сайын) қалпына келтіріліп отырылуы керек. Бірақ динамикалық жады элементтерінің орналастырылым тығыздығы статикалық құрылыммен салыстырғанда бірнеше есе асып түседі.

Динамикалы RAM түріндегі жады құрылымдарының ақпараттық сыйымдылығы жоғары болады және арзанға түседі, сондықтан есептеу машиналарының негізгі жадысы ретінде пайдаланылады. Статикалы RAM түріндегі жады құрылымдары динамикалы құрылымдармен салыстырғанда бірнеше есе қымбатқа түседі (жады элементтерінің күрделілігінен) және олардың ақпараттық сыйымдылығы да сонша есе кем болады. Олардың артықшылығы тезәрекеттілігінде, осыған байланысты қолданылым аймағы – кэш-жадысының сұлбалары.

ROM түрлі жады құрылымдарының кейбір түрінде ақпарат ешқашан өзгертілмейді, ал кейбірінде өзгертуге болады, бірақ ол құрылғының жұмыс режимінде емес, арнайы режимде ғана жүзеге асырылады.

ROM түрлі ЖҚ-лар бағдарлану тәсіліне (және орнына) байланысты бірнеше түрде шығарылады, олар: ROM(M), PROM, EPROM және EEPROM.

ROM(M) түріндегі құрылымдар жинам технологиясымен өндірісте шығарылу кезінде арнайы маскалар арқылы бағдарланады да, одан кейін ондағы ақпарат ешқашан өзгертілмейді.

PROM (Programmable ROM) түріндегі құрылымдарды пайдаланушының өзі бағдарлайды (яғни оған қажетті ақпаратты енгізеді), одан кейін бұл құрылым ROM(M) сияқты тұрақты жады ретінде пайдаланылады.

EPROM (Electrically Programmable ROM) және EEPROM (Electrically Erasable Programmable ROM) түріндегі құрылымдардағы ақпаратты өшіріп, одан кейін оларды қайтадан бағдарлауға болады. EPROM құрылымдарындағы ақпарат ультракүлгін сәулесімен, ал EEPROM құрылымдарындағы ақпарат электр сигналдарымен өшіріледі. Оларды бағдарлау зертханалық жағдайда арнайы бағдарлаушы құрылғылар арқылы жүзеге асырылады.

Тізбекті шығарылымды жады құрылымдарында жазылған деректер кезек құрады. Кезектегі сөздердің оқылуы олардың жазылым тәртібімен немесе керісінше тәртіппен жүзеге асырылады. Сөздердің тура шығарылым тәртібі FIFO (First In – First Out) буферлері мен файлды және циклді ЖҚ-ларда қолданылады. Сөздердің кері тәртіппен оқылуы LIFO (Last In – First Out) буферлері ретінде істейтін стек түріндегі ЖҚ-ларда қолданылады.

Танымалды шығарылымды ЖҚ-лардағы ақпаратты іздеу оның жадыдағы орналасымы арқылы емес, cөз құрамына енгізілген арнайы танымал белгісі (tag) арқылы жүзеге асырылады. Олар, негізінде, үлкен цифрлық жүйелердің (мысалы, есептеу машиналарының) құрамындағы, кэш-жадыларда пайдаланылады.

5.2 RAM түріндегі жады құрылғыларының құрылымдары

Статикалы RAM түрлі жады құрылғылары 2D, 3D және 2DM құрылымымен құрылады.

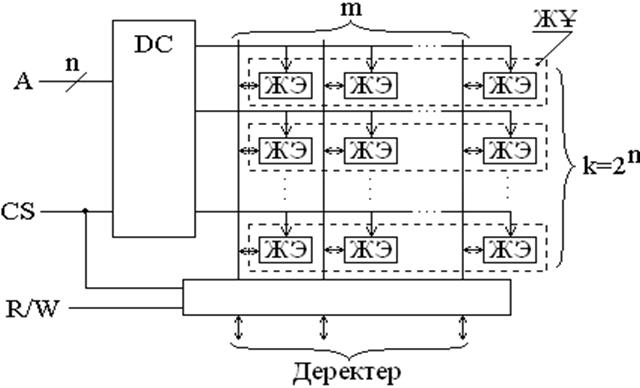

2D құрылымында n-разрядты m-разрядты жады ұяшықтары (ЖҰ) дешифратордың сәйкесті шығыстарына қосылады, яғни олар бір жол бойында орналастырылады (суретте – вертикаль бойында), сондықтан бұндай құрылым, көбіне, сызықты құрылым деп аталады (5.1 суретті қараңыз).

5.1 сурет

Адрес кодының дешифраторы (DC), рұқсат сигналы CS (Chip Select) берілген кезде, шығыс жолдарының біреуін жандандырып, таңдалған жолдағы ұяшыққа, демек онда сақтаулы сөзге қол жеткізеді. Матрица бағаналарының сәйкесті элементтері вертикаль жолға, яғни ішкі дерек жолына (разряд жолына, оқу/жазу жолына) жалғанған. Бағана элементтерінде сөздердің аттас биттері сақталған. Сөздің жіберілім бағыты R/W (Read/Write) сигналының әрекетіне байланысты оқу/жазу күшейткіштерімен анықталады.

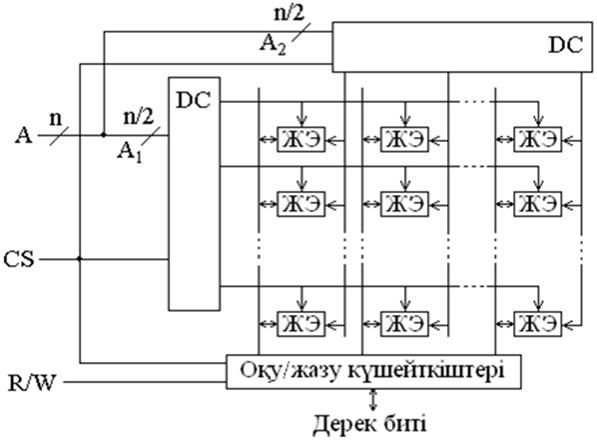

3D құрылымы (матрицалы құрылым) қоскоординаталы талғам арқылы адрес дешифраторын жеңілдетуге мүмкіндік береді (5.2 суретті қараңыз).

Бұнда n разрядты адрес коды екіге бөлінеді де, олардың әрбіреуі жеке ажыратылады. Жандандырылған жолдардың қиылысындағы жады элементі (немесе ұяшығы) таңдалады. Бұндай қиылыстар саны 2n/2 х 2n/2 = 2n. Екі дешифратордың шығыстарының толық саны 2n/2 + 2n/2 = 2n/2+1 болады, ал бұл 2D құрылымдағы дешифратордың шығыс санынан (2n) санынан едәуір кем.

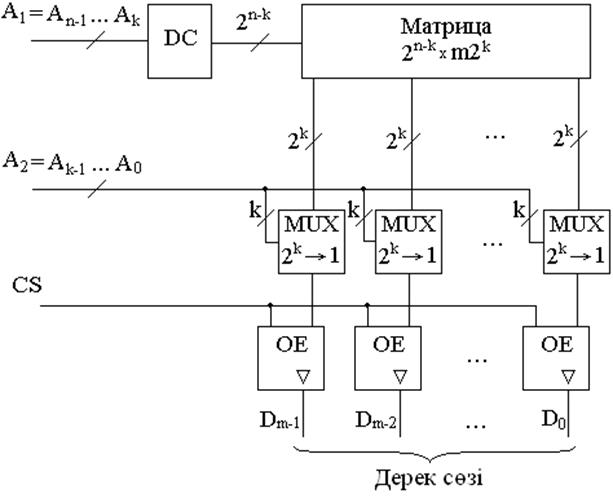

Үлкен құрылымдардың (мысалы, компьютерлердің) жады жүйелерін ұйымдастыруға арналған 2DM (модификацияланған 2D) құрылымында 2D және 3D құрылымдарының екеуінің де артықшылық жақтары қамтылған – адрес ажыратылуы жеңілдетілген және екікоординаталы талғанымды жады элементтерінің қажеттігі жоқ.

5.2 сурет

2DM құрылымының жады элементтерінің матрицасы (5.3 суретті қараңыз) 2D құрылымының сипатындай: дешифратордың жандандырылған шығысы толық бір жолды таңдайды. Бірақ 2D құрылымынан ерекше, бұнда жол ұзындығы сақталушы сөздердің разряд санындай емес, одан бірнеше есе асып түседі. Жолдардың біреуін таңдауға адрес кодының An–1... Ak бөлігі пайдаланылады. Адрестің қалған разрядтары (от Ak–1... A0) таңдалған жолдағы көптеген сөздердің қажеттісін мультиплексор арқылы бөліп шығаруға пайдаланылады. Жол ұзындығы – m2k, бұндағы m – сақталушы сөздердің разряд саны. Ұзақтығы 2k жолдың әрбір “кесіндісінен” 2k мультиплексор бір бит таңдайды. Мультиплексорлардың шығыстарында шығыс сөзі қалыптасады. Үш жағдайлы басқарылымды буферлердің ОЕ кірістеріне түсетін CS сигналының рұқсатымен шығыс сөзі сыртқы желіге жіберіледі.

5.3 сурет

5.3 ROM түріндегі жады құрылғыларының элементтері

ROM (Read Only Memory) түрлі жадылық құрылғылардың кейбіреуіндегі ақпарат (ROM(M) және PROM түрлі ЖҚ-да) ешқашан өзгермейді, ал кейбіреуінде (EPROM және EEPROM түрлі ЖҚ-да) өзгертіледі, бірақ ол құрылғының жұмыс режимінде емес, арнайы режимде жүзеге асырылады.

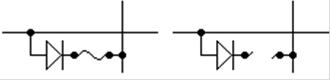

ROM(M) түріндегі құрылымдар жинамды технологиямен олардың өндірісте шығарылу кезінде арнайы маскалар арқылы бағдарланады да, одан кейін ақпарат ешқашан өзгертілмейді. Оларды бағдарлау жады элементтерінің матрицасының горизонталь және вертикаль жолдарының арасында байланыс элементтерінің орналастырылуы арқылы жүзеге асырылады. Байланыс элементтері ретінде диодтардың, биполярлы транзисторлардың, МОШ-транзисторлардың және т.б. пайдаланылуы мүмкін.

Диодты ROM(M) матрицасында (5.4 суретті қараңыз) горизонталь жолдар – сөз талғам жолдары, ал вертикаль жолдар – оқылым жолдары. Оқылатын сөз диодтардың координат торының түйіндеріндегі орналасысымымен анықталады. Диодтың тұрған кезінде таңдалған горизонталь жолдың жоғары мәнді потенциалы сәйкесті вертикаль жолға жіберіледі де сөздің осы разрядында логикалық бір сигналы шығады. Диодтың жоқ кезінде, вертикаль жол резистор арқылы жерге жалғанғандықтан, осы жолдың потенциалы нөлге жуық болады. Көрсетілген матрицадағы талғам жолы Т0 жандандырылғанда 11010001 сөзі оқылады (нөмірі нөл ұяшықта осы сөз сақталған). Т1 жолы жандандырылғанда 10101011 сөзі оқылады (ол нөмірі 1 ұяшықта сақталған). Талғам жолдары – адрес дешифраторының шығыстары, әрбір адрес қиыстырымы дешифратордың сәйкесті шығысын жандандырады да, сілтенген ұяшықтағы сөз оқылады.

5.4 сурет

МТШ-технологиясымен құрылған ROM(M) құрылымының матрицасының сәйкесті қиылысындағы нөл сақтаушы МТШ-транзисторларының арнасы мен жапқышының арасындағы тотық қабатының қалыңдығы ұлғайтылады да, ол транзистордың шекті ашылым кернеуін өсіреді, яғни ол ашылмайтын жағдайға келтіріледі, ал бір сақтаушы транзисторлардың тотық қабатының қалыңдығы оның дешифратордан түсетін талғам сигналымен ашылатындай мөлшерге қойылады (5.5 суретті қараңыз).

5.5 сурет

ROM(M) түрлі ЖҚ-лардың жады элементтері өте аз орын алады, демек сәйкесті микросұлбалардың жиналым деңгейі жоғары болады. Бірақ жиналымды технологиялық тәсілмен бағдарлауға арналған маскаларды жобалау мен жасауға кететін қаражат аса жоғары болады. Бұндай қаражат олардың кең қолданылатын жағдайында ғана ақталады. Бұдан олардың қолданылым аймағы да анықталады, олар – тұтынушылардың көпшілігіне қажетті, стандартты ақпарат сақтау. Мысалы, маскалы бағдарламалы жады құрылғыларында алфавит (орысша және латынша) символдарының, қалыпты функциялардың (синустың, квадраттық функциялардың және т.б.) кестелері, стандартты бағдарламалар және с.с. кең қолданылымды ақпараттың “тігілімдері[1]” болады.

PROM (Programmable ROM) түрлі жадылық құрылғылардың микросұлбалары арнайы жалғамаларды жою немесе оларды құру арқылы бағдарланады. Микросұлбаның бастапқы дайындалымында барлық жалғамалар болады (немесе ешқандай жалғама болмайды). Бағдарлаудан кейін олардың қажеттілері ғана қалады (немесе құрылады).

Жойылымды жалғамалы ЖҚ-лардың бастапқы микросұлбасында барлық жалғама орналастырылған (яғни жады матрицасының барлық қиылысында лог.1 тұрады). Бағдарлау кезінде олардың кейбірі амплитудасы мен ұзақтығы жеткілікті мөлшердегі ток импульстарымен еріту арқылы жойылады (яғни жады матрицасының сәйкесті қиылыстарына лог.0 жазылады). Ерітілме жалғамалар диодтардың немесе транзисторлардың электродтарына қосылады (5.6, a-суретті қараңыз).

|

|

|

|

a |

b |

5.6 сурет

Құрылымды жалғамалы ЖҚ-лардың бастапқы микросұлбасының құрамындағы жады матрицасының барлық қиылысында қарсы қосылымды диод түріндегі құрылым орналастырылған (5.6, b-суретті қараңыз). Қосдиодты құрылымның бастапқы жағдайдағы кедергісі жоғары болады да, бұл қиылыстардың ажыратылған жағдайына, яғни онда лог.0 сақталған элемент тұрғанына сәйкес келеді. Нақтылы қиылыстарды лог.1 жағдайына келтіру үшін, яғни онда бір жазу үшін, бұндағы диодтарға жоғары мәнді кернеу беру арқылы кері бағытта қосылған диод тесіліп, бұл қиылыс тұйықталады да, онда ток жүргізуші жалғама туады.

Қайта бағдарламалы EPROM және EEPROM түрлі ЖҚ-ларда ескі информацияны өшіріп, оның орнына жаңа ақпарат жазу мүмкіндігі қамтылған. Бұл операциялар (өшіру және жазу) олардың жұмыс режимінен шығарылған арнайы жағдайда жүргізіледі. Ақпараттың өшірілуі EPROM құрылымында ультракүлгін сәулесімен, ал EEPROM құрылымында электрлік тәсілмен жүзеге асырылады.

Қазіргі заманғы қайта бағдарламалы ЖҚ-лардың жады элементтері ретінде жұмысы қалқыма жаппаның тудырылуына негізделген МНТШ-транзисторлар (Металл, Нитрид, Тотық, Шалаөткізгіш) мен ЗТИМТШ-транзисторлар (Зарядтардың Тасқынды Инжекциясына МТШ-транзистор) қолданылады [1].

6 Цифрлық құрылғылардың моделдері

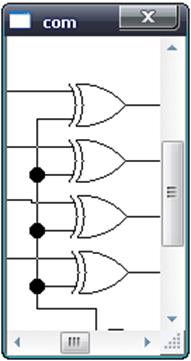

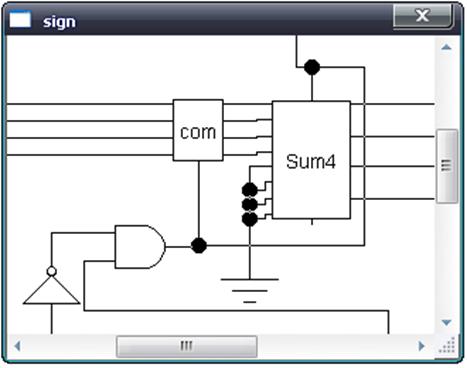

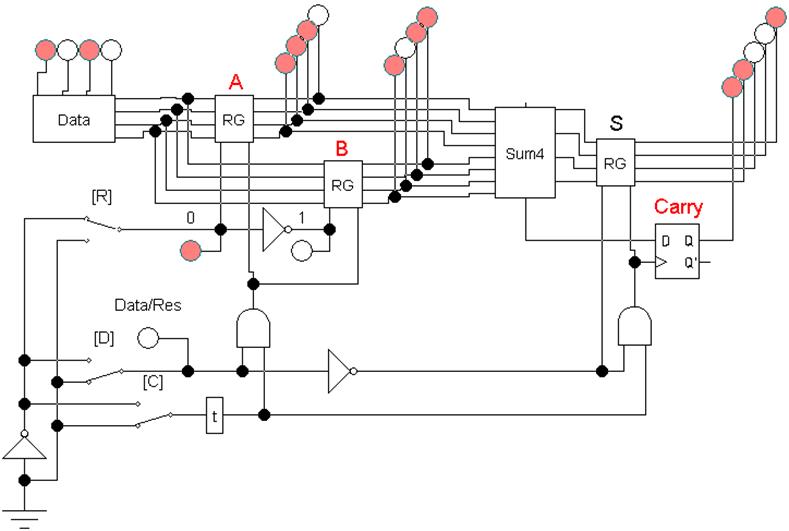

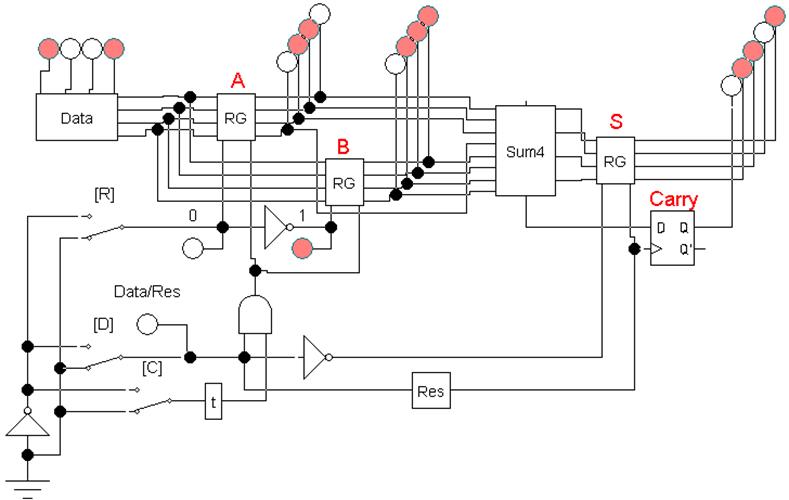

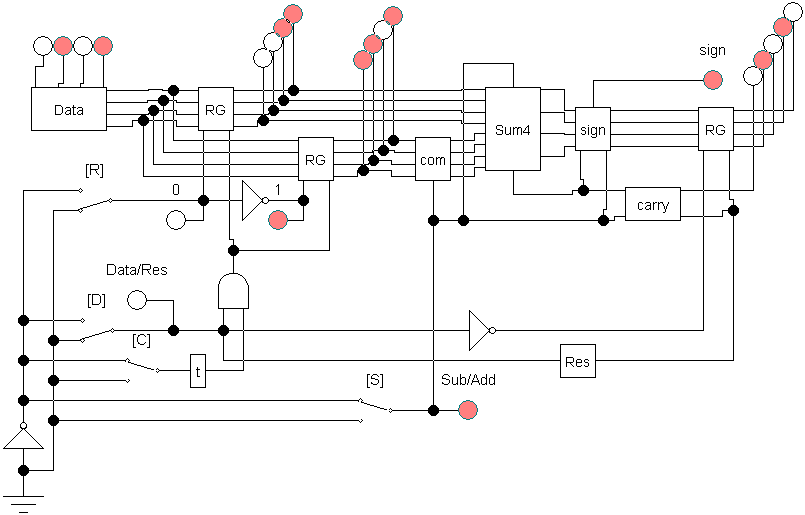

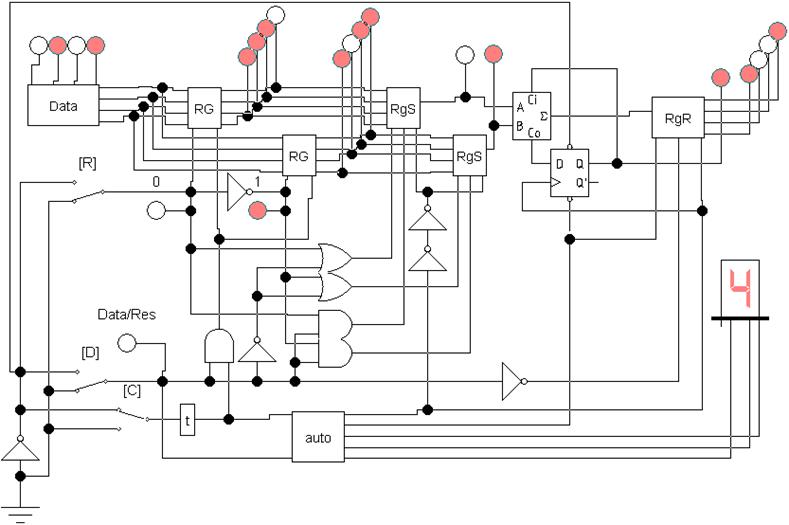

Цифрлық құрылғылардың құрылымын логикалық және схемотехникалық тұрғыдан құру мүмкіншілігін көрсету мақсатында схемотехникалық моделдеу жұмысын жүргізуге арналған Electronics Workbench бағдарламалы ортасында алдында қарастырылған қалыпты қиыстырма және тізбектеме арқылы құрылған, нақтылы алгоритмдерді жүзеге асырушы бірнеше цифрлық құралымның тәжірибелік моделдерін суреттелік.

Бұдан әрі келтірілген және суреттелетін моделдер төртразрядты деректермен жұмыс істейтіндей етіп құрылған. Қажетті жағдайда оларды разряд саны жоғарырақ деректермен (мысалы, сегізразрядты деректермен) істейтіндей етіп жаңарту қиын емес.

Әртүрлі цифрлық құрылғылардың тәжірибелік моделін құру кезінде құрылғының нақтылы қызмет буындарына бастапқы сандарды (екілік код түріндегі) енгізу қажеттігі туады (6.1 суретті қараңыз). Ол үшін шифраторлар негізіндегі немесе мультиплексор негізіндегі (кезектеп тексермелі деп аталатын) дерек енгізу құрылғысын құруға болар еді. Бүндай құрылғыларда қажетті екілік код түймежинамдағы сәйкесті түймені басу арқылы қалыптастырылады.

6.1 сурет

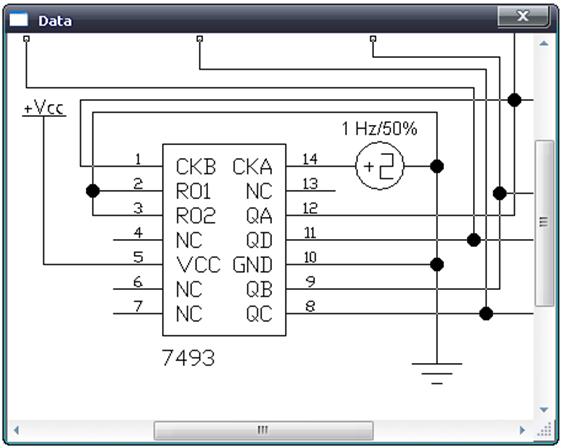

Дерек көзінің ең қарапайым (жеңіл және тезірек құрылатын) түрін санауыш негізінде құруға болады, бұндай құрылғыны динамикалық дерек көзі деп атадық. 6.2 суретте келтірілген сұлбадағы дерек көзі Data, жиілігі 1 Гц генератордан істеуші төртразрядты санауыштың 7493 микросұлбасының негізнде құрылған. Оның индикаторларында 0 – 15 арасындағы сандардың коды 1 секунд сайын (генератордың қойылған жиілігіне сәйкесті) тізбелі түрде шығарылып тұрады. Қажетті санның коды шығуын күтіп, оны кіріс деректерінің қабылдағышына жазып алу ғана қалады.

6.2 сурет