Некоммерческое акционерное общество

АЛМАТИНСКИЙ УНИВЕРСИТЕТ ЭНЕРГЕТИКИ И СВЯЗИ

Кафедра «Электроника»

СХЕМОТЕХНИКА 1

Методические указания и задания к выполнению расчетно-графической работы (для студентов всех форм обучения специальности 5В070400 – Вычислительная техника и программное обеспечение, 5В070300- Информационные системы)

Алматы 2011

СОСТАВИТЕЛЬ: У.К.Дегембаева. Схемотехника 1. Методические указания и задания к выполнению расчетно-графической работы (для студентов всех форм обучения специальности 5В070400 – Вычислительная техника и программное обеспечение, 5В070300- Информационные системы). - Алматы: АУЭС, 2011. –25 с.

Рассмотрены узловые вопросы схемотехники - элементной базы цифровых и аналоговых микросхем. Немаловажное значение имеют также сведения о структуре конструкции интегральных микросхем, а также технологических процессах, применяемых в микроэлектронике.

Ил. 8, табл. 8, библиогр. – 19 назв.

Рецензент: канд. техн. наук, доцент Б.С. Байкенов

Печатается по плану издания некоммерческого акционерного общества «Алматинский университет энергетики и связи» на 2011 г.

© НАО «Алматинский университет энергетики и связи», 2011 г.

Содержание

|

Введение |

3 |

|

1 Рекомендации к выполнению расчетно-графических работ 1 и 2 |

4 |

|

2 Требования по оформлению работы |

4 |

|

3 Задания к выполнению расчетно-графических работ 1 и 2 Расчетно-графическая работа №1.Задание 1 |

4 |

|

3.1 Контрольные вопросы 1 раздела |

6 |

|

3.2 Контрольные вопросы 2 раздела |

6 |

|

4 Расчетно-графическая работа 2 |

9 |

|

4.1 Задание 1 - электрический расчет цифровой схемы |

9 |

|

4.2 Задание 2 - разработка топологии ИМС для выше приведенной схемы |

8 |

|

5 Методические указания выполнения задания №1- анализ схемы логического элемента |

13 |

|

5.1 Методические указания к выполнению второго задания расчетно –графической работы №2 |

18 |

|

5.2 Пример выполнения методического задания №2- пример выполнения топологии ГИМС |

19 |

|

Список литературы |

24 |

1 Рекомендации к выполнению расчетно-графических работ 1,2

Целью расчетно-графических работ является закрепление теоретического материала по второму разделу курса «Схемотехнка 1» и приобретению навыков анализа ЦИМС и составления топологии гибридных ИМС.

Выбор варианта

Номер варианта принципиальной схемы для её анализа и электрического расчета определяется последней цифрой номера студенческого билета. А номер варианта технологической части предпоследней цифрой.

2 Требования по оформлению работы

1) Работа выполняется на листах писчей бумаги формата А4. Она

должна быть аккуратно оформлена, страницы должны быть пронумерованы.

2) На титульном листе должен быть указан номер варианта.

3) Графики и чертежи выполняются с соблюдением правил черчения и ГОСТ. Все графики, чертежи, рисунки и таблицы должны быть пронумерованы.

4) Расчетные формулы должны приводиться в тексте работы в

общем виде с объяснением буквенных обозначений. Все числовые значения необходимо подставлять в формулы в основных единицах (Вольт, Ампер, Ом, сек. и т. д.), либо указывать единицы измерения. Результаты расчета должны приводиться с указанием единицы измерения полученной величины.

5) Пояснения должны быть достаточно полными для описания выполняемых действий.

6) В конце работы должна быть перечислена литература, использованная при проектировании.

7) Работа должна быть подписана с указанием даты.

3 Задания к выполнению расчетно-графической работы 1и 2

Расчетно-графическая работа №1. Задание 1

Первая расчетно-графическая работа направлена на закрепление теоретического материала по лекционному курсу «Схемотехника1» для студентов специальности факультета Информационные технологии.

Вариант индивидуального задания определяется в таблице 1.1 по предпоследней (вопрос из первого раздела) и последней (вопрос из второго раздела) цифрам номера зачетной книжки и по первой букве фамилии студента.

Т а б л и ц а 1.1

|

|

Первая буква фамилии студента |

|||||||||

|

Вопросы из 1 раздела |

А,Д |

Б,Е |

В,Г,Я |

Ж,ЗИ |

Л,К |

М,О |

Н,П |

С,Ч,Ф |

Р,Т,У |

Х,Ц,Ш, |

|

1,11 |

2,11 |

3,13 |

4,14 |

5,15 |

6,16 |

7,17 |

8,18 |

9,19 |

10,20 |

|

|

Вопросы из 2 раздела |

40,29 |

39,28 |

38,27 |

37,26 |

36,25 |

35,24 |

34,23 |

32,22 |

31,21 |

30,20 |

3.1 Контрольные вопросы 1 раздела

1) В чем состоит различие аналоговых и цифровых электронных

устройств?

2) Почему в ключевой схеме на кремниевом n-p-n-транзисторе можно не использовать специального источника запирающего напряжения на входе?

3) От чего зависит остаточное напряжение на открытом ключевом транзисторе (биполярном или МДП)? Дайте его оценку.

4) Какие параметры определяют быстродействие (время задержки) ключа на биполярном транзисторе и ключа на МДП-транзисторе?

5) Почему ключ на биполярном транзисторе с диодом Шоттки имеет более высокое быстродействие по сравнению с ключом без диода Шоттки?

6) Начертите принципиальные схемы и поясните принцип действия базовых логических элементов ТТЛ, ТТЛШ, pМДП, nМДП, КМДП.

7) Какими причинами вызван переход от ИМС малой и средней степени интеграции к БИС и СБИС?

8) Какие ограничения существуют для повышения степени интеграции БИС?

9) Приведите характеристики и перечислите параметры ОУ.

10) Из каких основных каскадов состоят интегральные ОУ?

Приведите схемы этих каскадов и поясните принцип их работы.

11) Начертите схему дифференциального усилительного каскада и поясните, какие точки являются входом схемы, а какие выходом; как влияет на величину выходного сигнала синфазный входной сигнал и дифференциальный входной сигнал; от каких факторов зависит коэффициент усиления?

12) Приведите схемы каскадов сдвига уровня напряжения и эмиттернного повторителя, поясните принцип работы и параметры.

13) Какие устройства обработки сигналов можно построить на основе ОУ?

14) В чем отличие аналоговых электронных ключей от ключей, применяемых в составе логических элементов?

15) Дайте определение понятия комплексная миниатюризация, поясните цель комплексной миниатюризации РЭА.

16) Как классифицируются все изделия микроэлектроники?

17) Поясните отличие функциональных компонентов (приборов) от ИМС.

18) Поясните устройство гибридной ИМС.

19) Перечислите преимущества и недостатки толстоплёночных и тонкоплёночных гибридных ИМС.

3.2 Контрольные вопросы 2 раздела

1) Изобразите и поясните возможные варианты конструкции плёночных резисторов, конденсаторов и индуктивностей.

2) Какими причинами ограничено применение тонкоплёночных индуктивных элементов?

3) Перечислите основные методы нанесения тонких плёнок, поясните основные преимущества и недостатки каждого из методов.

4) Перечислите основные методы получения заданной конфигурации пассивных элементов и назовите их недостатки и преимущества.

5) Перечислите и поясните базовые физико-химические процессы создания полупроводниковых микроэлектронных структур.

6) Приведите последовательность технологических операций по изготовлению полупроводниковых биполярных ИМС.

7) Приведите последовательность технологических операций по изготовлению МДП ИМС.

8) Каким образом осуществляется сборка и герметизация полупроводниковых ИМС, какие типы корпусов Вы знаете?

9) Какие виды изоляции между элементами полупроводниковой ИМС Вы знаете? Объясните преимущества и недостатки каждого из них.

10) Изобразите устройство интегрального n-p-n транзистора, поясните основные отличия от аналогичного дискретного транзистора.

11) Изобразите устройство многоэмиттерного и многоколлекторного транзисторов, поясните их основные особенности.

12) Изобразите устройство горизонтального и вертикального `p-n-p транзисторов, поясните их основные особенности.

13) Изобразите схемы включения транзисторов в качестве диода, приведите основные параметры для каждой из схем включения.

14) Изобразите устройство МДП полупроводниковой ИМС.

15) Изобразите устройство КМДП структуры, поясните основные особенности и преимущества .

16) Перечислите и объясните основные преимущества и недостатки МДП ИМС по сравнению с биполярными ИМС.

17) Изобразите устройство диффузионного резистора, приведите его основные параметры.

18) Изобразите модель (эквивалентную схему) диффузионного резистора, учитывающую паразитные эффекты.

19) Изобразите устройство диффузионного конденсатора на основе обратно смещенного p-n перехода и МДП конденсатора. Назовите их параметры .

20) Приведите модели (эквивалентные схемы) конденсаторов полупроводниковых ИМС. Дайте их сравнительную оценку.

21) Дайте определение понятию большая интегральная схема (БИС).

22) В чем заключаются принципиальные преимущества БИС?

23) Перечислите основные проблемы, возникающие при повышении степени интеграции БИС.

24) Какие базовые интегральные элементы используются в БИС и почему?

25) Перечислите основные виды универсальных БИС.

26) Дайте определение понятия микропроцессор, поясните, из каких основных узлов он состоит?

27) Поясните назначение БИС АЦП и ЦАП.

28) Приведите характеристики и перечислите параметры ОУ.

29) Из каких основных каскадов состоят интегральные ОУ? Приведите схемы этих каскадов и поясните принцип их работы.

30) Начертите схему дифференциального усилительного каскада и поясните, какие точки являются входом схемы, а какие выходом; как влияет на величину выходного сигнала синфазный входной сигнал и дифференциальный входной сигнал; от каких факторов зависит коэффициент усиления?

31) Какие устройства обработки сигналов можно построить на основе ОУ?

32) В чем состоит основное отличие приборов функциональной электроники от обычных интегральных микросхем?

33) Каким образом происходит формирование, хранение перенос зарядовых пакетов в приборах с зарядовой связью?

34) Назовите область применения приборов с зарядовой связью.

35) На каких принципах основана запись и хранение информации в магнитоэлектронных приборах?

36) Какие функции преобразования и обработки сигналов можно реализовать с помощью акустоэлектронных приборов?

37) Пояснить работу биполярных и полевых транзисторов с нагрузкой.

38) Охарактеризовать шумовые свойства биполярных и полевых транзисторов.

39) Объяснить устройство цифровых ключей на биполярных и полевых транзисторах.

40) Объяснить устройство аналоговых ключей на транзисторах.

4 Расчетно-графическая работа 2

4.1 Задание 1 - электрический расчет цифровой схемы

Для трех комбинаций входных сигналов составить таблицу состояний всех активных элементов и провести электрический расчет, а именно:

- оценить потенциалы в точках, указанных на схеме (А, В, С и т. д.);

- рассчитать все токи схемы и указать их направления;

- рассчитать мощности, которые рассеиваются на резисторах, и мощности потребляемой всей схемой.

Результаты расчетов свести в таблицы. Примеры расчетов и таблиц будут даны в соответствующих разделах.

4.2 Задание 2 - разработка топологии ИМС для выше приведенной схемы

Разработка топологии включает в себя следующие операции:

- выбор материала для пленочных резисторов согласно заданного варианта;

- расчет размеров всех резисторов;

- выбор материала для проводников и контактных площадок;

- расчет площади, занимаемой активными и пассивными элементами схемы;

- определение и выбор размеров подложки;

- составление топологического чертежа.

Топологический чертеж должен быть выполнен в масштабе 10:1 или 20:1.

Задания к выполнению первой задачи

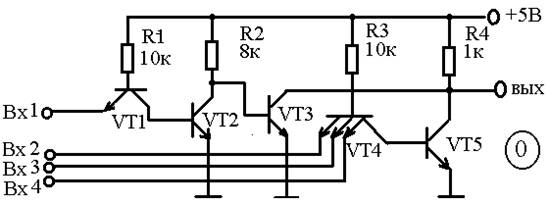

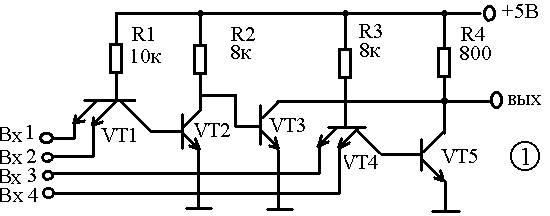

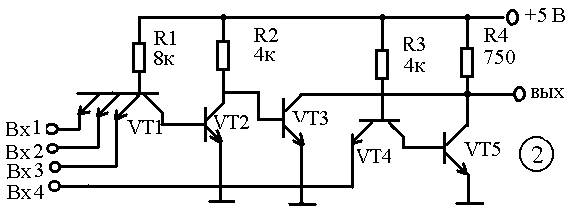

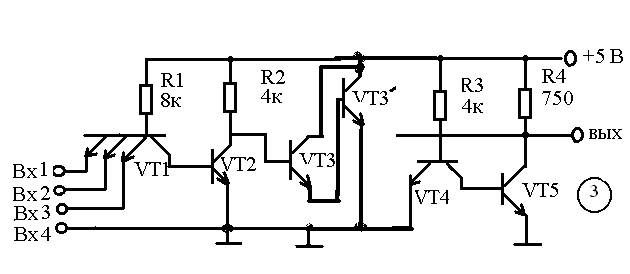

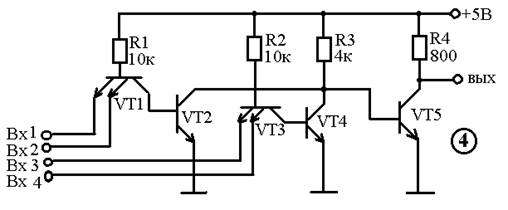

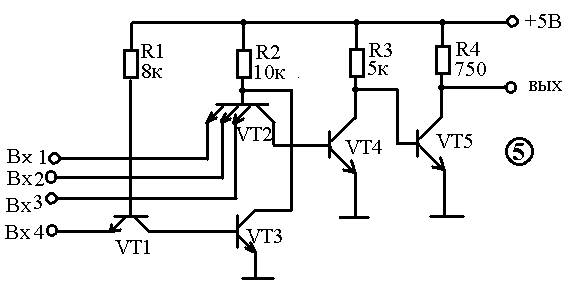

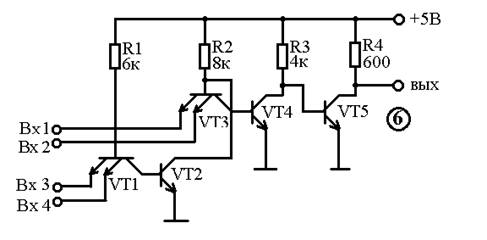

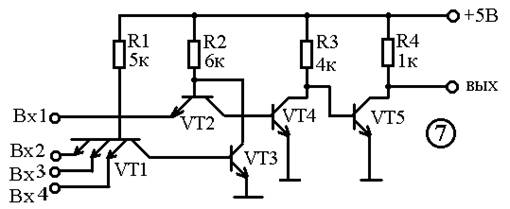

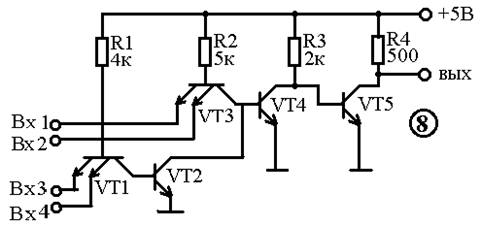

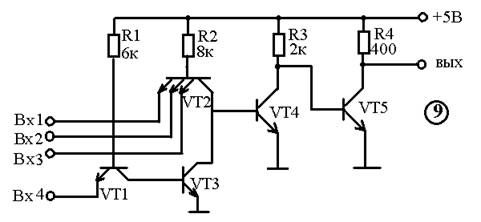

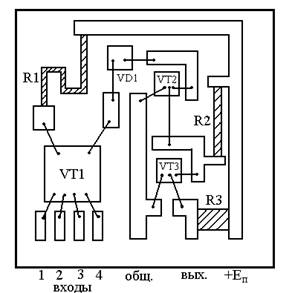

Варианты принципиальных схем приведены на рисунке 1, а комбинации входных сигналов, для которых необходимо провести анализ, даны в таблице 2.

Рисунок 1- Варианты схем к расчетно-графической работе

Цифра в кружочке означает последнюю цифру номера студенческого билета. Для успешного решения задачи необходимо сначала изучить принципы работы транзисторных ключей и логических элементов на биполярных транзисторах. При решении задачи нужно учесть, что интегральные схемы ТТЛ изготавливаются из кремния. Транзисторы работают в режиме ключа. Эти обстоятельства позволяют использовать упрощенные модели вольт - амперных характеристик (ВАХ) диодов и транзисторов для расчетов токов и напряжений.

Т а б л и ц а 2 - Комбинации входных сигналов

|

Последняя цифра номера студенческого |

Значения входных сигналов |

Последняя цифра номера студенческого |

Значения входных сигналов |

||||||

|

билета |

Входы |

билета |

Входы |

||||||

|

|

1 |

2 |

3 |

4 |

|

1 |

2 |

3 |

4 |

|

|

0 |

1 |

1 |

1 |

|

1 |

1 |

1 |

0 |

|

0 |

0 |

0 |

1 |

0 |

5 |

1 |

0 |

1 |

0 |

|

|

1 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

|

0 |

1 |

1 |

1 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

6 |

0 |

1 |

0 |

1 |

|

|

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

|

|

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

|

2 |

0 |

1 |

0 |

0 |

7 |

0 |

0 |

0 |

1 |

|

|

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

1 |

|

|

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

|

3 |

0 |

1 |

1 |

1 |

8 |

1 |

0 |

0 |

1 |

|

|

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

|

1 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

|

4 |

1 |

0 |

0 |

1 |

9 |

0 |

0 |

1 |

1 |

|

|

0 |

0 |

1 |

1 |

|

1 |

1 |

1 |

0 |

Приведем словесные формулировки этих моделей.

Упрощенная модель ВАХ кремниевого p-n перехода (диода):

- если напряжение на p-n обратное или прямое, но не превышает значения U*, то ток через p-n переход считается равным нулю;

- если через p-n переход протекает прямой ток, то напряжение на диоде принимаем равным U*=0,7 В.

Упрощенная модель кремниевого биполярного транзистора:

- если на каждом из двух p-n переходов транзистора действуют прямые напряжения, не превышающие значения U*, либо обратные напряжения, то транзистор закрыт и все токи считаются равными нулю;

- если через эмиттерный переход протекает прямой ток, то напряжение база-эмиттер равно U*=0,7 B, транзистор открыт и может находиться в одном из двух режимов: активном или насыщения; для уточнения режима вычисляют ток базы IБ , произведение В×IБ и максимально возможное значение тока коллектора насыщенного транзистора IКН, затем проводят сравнение:

- если В×IБ <IKH , то режим активный, если В×IБ>IКН, то режим насыщения;

- ток коллектора в активном режиме не зависит от напряжения на переходе коллектор-база и равен IК =B×IБ;

- напряжение на переходе коллектор-база в режиме насыщения равно 0,6 В, тогда напряжение коллектор-эмиттер равно 0,1 В.

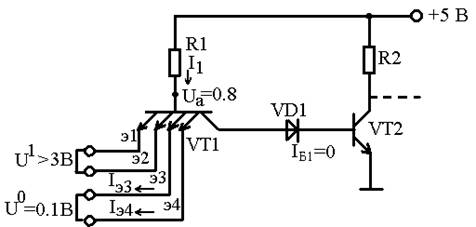

Следовательно, при выполнении расчетов принимаем:

U0=0,1 B, U1>3 В, падение напряжения на диоде и эмиттерном переходе при прямом включении равно 0,7 В, коэффициент передачи тока базы В=50, инверсный коэффициент передачи тока базы ВI=0,05.

5 Методические указания выполнения задания №1 - анализ схемы логического элемента

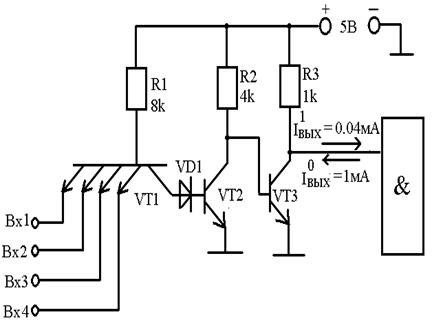

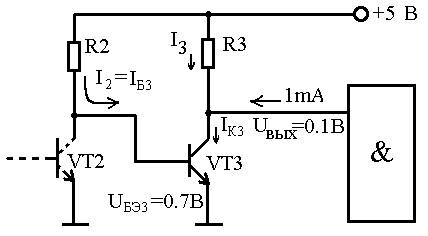

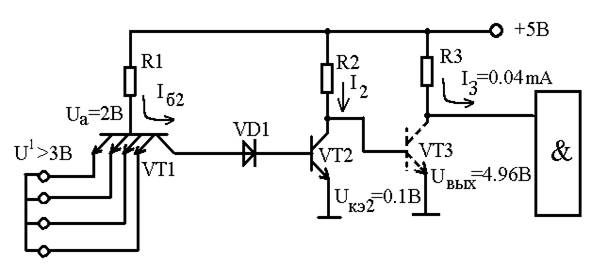

Принципиальная схема логического элемента, показана на рисунке 2.

Значения сопротивлений и напряжение питания указаны на схеме. В виде прямоугольника показан следующий логический элемент, вход которого является нагрузкой для нашего логического элемента. Требуется провести расчет токов через резисторы и выходного напряжения для двух комбинаций входных сигналов ²1100² и ²1111², а также описать принцип действия и составить таблицу истинности.

Проведем расчет для комбинации входных сигналов ²1100², т.е. согласно принятым значениям UВХ1=UВХ2=U1>3 В, а UВХ3=UВХ4=U0=0,1 В. Определим величину тока через резистор R1. Рассмотрим все возможные пути, по которым может протекать этот ток. В схеме только один источник напряжения - источник питания +5 В. Поэтому все постоянные токи в схеме могут протекать только в одном направлении от шины +5 В к общей шине.

Рисунок 2 - Принципиальная схема логического элемента

На рисунке 3 выделена часть схемы, по которой может протекать ток, идущий через R1 (ток I1). Ток I1 протекает от шины +5 В через R1 и далее может течь от базы транзистора VT1 налево через эмиттерные переходы, источники сигнала на общую шину или направо через коллекторный переход, диод и эмиттерный переход транзистора VT2 к общей шине.

Предположим, что ток протекает через переходы Б-Э3 и Б-Э4 транзистора VT1, то напряжения на этих переходах одинаковы и, согласно предложенной выше модели, равны 0,7 В. Следовательно потенциал базы транзистора VT1 (точка А) равен 0,8 В.

Рисунок 3 - Частичная схема для расчета тока I1 при комбинации входных сигналов ²1100²

Предположим, что ток протекает через переходы Б-Э3 и Б-Э4 транзистора VT1, то напряжения на этих переходах одинаковы и, согласно предложенной выше модели равны 0,7 В. Следовательно потенциал базы транзистора VT1 (точка А), равен UА=U0+UБЭ=0,1+0,7=0,8 В. Заметим, что переходы база-эмиттер Б-Э1 и Б-Э2 находятся под обратным напряжением, так как потенциал базы (р-область) ниже, чем потенциал эмиттеров (n-области) на величину

0,8-3=-2,2 В. Поэтому через эти переходы протекает только обратный ток.

Ток правой ветви при этом будет отсутствовать, так как для того чтобы он протекал в точке А требуется потенциал равный

UБК1+UVD1+UБЭ2=0,6+0,7+0,7 =2 В.

Следовательно транзистор VT2 будет закрыт. Находим ток I1.

I1=(E-UA)/R1=(5-0,8)/8*103=0,525 мА.

Рассчитаем величины токов I2 и I3, протекающих через резисторы R2 и R3.Выделим отдельно ту часть схемы по которой протекают указанные токи (см. рисунок 4). Закрытый транзистор VT2 показан пунктиром. Тогда через резистор R2 протекает ток базы транзистора VT3, транзистор открыт и напряжение на базе этого транзистора будет равно UБ3=0,7 В.

Находим ток I2 =IБ3. I2=(E-UБ3)/R2=(5-0,7)/4*103=1,075 мА.

Предположим, что транзистор VT3 находится в режиме насыщения.

По условию напряжение открытого транзистора UКЭ3=UВЫХ=0,1 В, тогда

I3=(E-UКЭ3)/R3=(5-0,1)/1*103=4,9 мА.

Рисунок 4 - Частичная схема для определения токов токов I2 и I3 при комбинации входных сигналов ²1100²

Низкое напряжение на коллекторе транзистора VT3 соответствует логическому ²0² на выходе схемы. Через коллектор транзистора VT3 протекает ток IК3=I3+IВЫХ=4,9+1=5,9 мА.

Сравним токи IБ3*B и IК3. IБ3*В=1,075*50=53,75 мА.

Так как IБ3*B>IК3, то действительно транзистор находится в режиме насыщения.

Проведем теперь расчет для комбинации входных сигналов ²1111², т. е. для случая, когда на все четыре входа подано высокое напряжение, соответствующее логической единице. UВХ1=UВХ2=UВХ3=UВХ4>3 B.

Покажем на схеме рисунке 5, как будут при этом распределяться токи и потенциалы.

Рисунок 5 - Схема для расчета токов I1, I2 и I3 при комбинации входных сигналов ²1111²

Прежде всего отметим, что потенциал в точке А на базе транзистора VT1 будет равен

UA=UБК1+UVD1+UБЭ2=0,6+0,7+0,7=2 B,

так как между данной точкой и общей шиной включено последовательно три p-n перехода: база-коллектор VT1, диод VD1 и база-эмиттер VT2. Так как все четыре эмиттера транзистора VT1 находятся под более высоким потенциалом, чем база, то все четыре эмиттерных перехода закрыты и ток от точки А потечет по правой ветви. Тогда ток I1 равен

I1=(E-UА)/ R1=(5-2)/8*103=0,375 мА.

Прежде всего отметим, что потенциал в точке А на базе транзистора VT1 будет равен UA=UБК1+UVD1+UБЭ2=0,6+0,7+0,7=2 B, так как между данной точкой и общей шиной включено последовательно три p-n перехода: база-коллектор VT1, диод VD1 и база-эмиттер VT2. Все четыре эмиттера транзистора VT1 находятся под более высоким потенциалом, чем база, поэтому все четыре эмиттерных перехода закрыты и ток от точки А потечет по правой ветви. Тогда ток I1 равен I1=(E-UА)/ R1=(5-2)/8*103=0,375 мА.

Через входные эмиттерные переходы протекают обратные токи . Вычислим эти токи, умножая ток базы VT1 ( I1 ) на инверсный коэффициент передачи тока В1:IЭ1=IЭ2=IЭ3=IЭ4=I1*BI=0,375*0,05=0,01775 мА.

В транзистор VT1 втекают пять токов IЭ1,IЭ2,IЭ3,IЭ4 и I1 , а вытекает через коллекторный переход и попадает в базу транзистора VT2 только один ток IБ2.

Исходя из этих соображений, вычисляем ток базы VT2:

IБ2=IЭ1+IЭ2+IЭ3+IЭ4+I1=0,446 мA.

Предполагая, что транзистор VT2 находится в режиме насыщения и, проделав выше приведенные выкладки, получаем, что это действительно так. Тогда напряжение UКЭ2=UБЭ3=0,1 В. Следовательно, транзистор VT3 закрыт и ток его коллектора равен нулю.

При этом через резистор R3 протекает только входной ток логического элемента нагрузки, равный по условию I3=0,04 мА. Тогда напряжение на выходе будет равно UВЫХ=E – I3 ×R3=5 - 0,04×10-3 ×103=4,96 B.

Полученное напряжение UВЫХ близко к напряжению питания и соответствует уровню логической единицы.

Рассчитаем мощности, потребляемые микросхемой для каждой

комбинации. Расчет произведем по формуле P=E*(I1+I2+I3).

Для первой комбинации Р=5×(0,525+1,075+4,9)10-3=32,5 мВт.

Для второй комбинации Р=5×(0,375+1,225+0,04)10-3=8,2 мВт.

Результаты расчетов занесем в таблицу 3.

Т а б л и ц а 3-Значения токов и мощностей, полученных в результате расчетов

|

Входная комбинация |

Токи, мА |

Потребляемая |

|||||

|

Вх 1 |

Вх 2 |

Вх 3 |

Вх 4 |

I1 |

I2 |

I3 |

мощность, мВт |

|

1 |

1 |

0 |

0 |

0,525 |

1,075 |

4,9 |

32,5 |

|

1 |

1 |

1 |

1 |

0,375 |

1,225 |

0,04 |

8,2 |

Для расчета размеров резисторов, которые будем определять ниже, выделим каждый из токов, имеющих максимальное значение, и запишем в таблицу 4. Затем вычислим мощности, рассеиваемые на резисторах, по формуле

PRi=I2i ×Ri и результаты также занесем в таблицу 4.

Т а б л и ц а 4 - Максимальные мощности резисторов

|

Максимальный ток, мА |

Мощность резистора, мВт |

||||

|

I1 |

I2 |

I3 |

PR1 |

PR2 |

PR3 |

|

0,525 |

1,225 |

4,9 |

2,2 |

6 |

24 |

Составим таблицу истинности. В схеме 4 входа, поэтому возможны всего 24=16 комбинаций входных сигналов. Пронумеруем эти комбинации числами от 0 до15 и запишем в таблицу 5.

Помня о том, что логической единице на входе соответствует уровень не менее 3 В, а логическому нулю 0,1 В, проанализируем работу схемы. С разу же поставим символ ² 0 ² в строке для комбинации ²1100² и ²1² для комбинации ²1111², так как анализ для этих случаев уже проведен.

Заметим, что выходное напряжение будет иметь низкий уровень (логический нуль) во всех случаях, когда транзистор VT3 открыт, т. е. находится в режиме насыщения. Это имеет место, если транзистор VT2 закрыт, а это, в свою очередь, произойдет только тогда, когда ток I1 будет протекать влево через один или несколько эмиттеров транзистора VT1. Таким образом, всем входным комбинациям, имеющим хотя бы один нуль, выходной сигнал соответствует логическому нулю.

Т а б л и ц а 5 - Таблица истинности для схемы, изображенной на рисунке 2

|

Номер |

Входн. комбин. |

|

Номер |

Входн. комбин. |

|

||||||

|

комбинации |

Входы |

Вых |

комбинац |

Входы |

Вых. |

||||||

|

|

1 |

2 |

3 |

4 |

|

|

1 |

2 |

3 |

4 |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

8 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

9 |

1 |

0 |

0 |

1 |

0 |

|

2 |

0 |

0 |

1 |

0 |

0 |

10 |

1 |

0 |

1 |

0 |

0 |

|

3 |

0 |

0 |

1 |

1 |

0 |

11 |

1 |

0 |

1 |

1 |

0 |

|

4 |

0 |

1 |

0 |

0 |

0 |

12 |

1 |

1 |

0 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

0 |

13 |

1 |

1 |

0 |

1 |

0 |

|

6 |

0 |

1 |

1 |

0 |

0 |

14 |

1 |

1 |

1 |

0 |

0 |

|

7 |

0 |

1 |

1 |

1 |

0 |

15 |

1 |

1 |

1 |

1 |

1 |

Таким образом, всем входным комбинациям, имеющим хотя бы один нуль, выходной сигнал соответствует логическому нулю.

5.1 Указания к выполнению второго задания расчетно –графической работы №2

Для выполнения этой задачи следует изучить материал по гибридным ИМС [2, стр.148-204] и [3,стр. 186-191 и 239-244].

Первым этапом является расчет размеров пассивных элементов, т. е. резисторов.

Второй этап - расчет площади, занимаемой пассивными и активными элементами, и выбор подложки.

На третьем этапе решения задачи заданную электрическую схему необходимо преобразовать таким образом, чтобы все внешние выводы находились на краю длинной стороны подложки и были исключены все пересечения пленочных проводников. Последнее условие выполняют, заменяя взаимные пересечения пленочных проводников пересечением пленки и выводов навесных бескорпусных диодов и транзисторов.

Общими принципами составления топологического чертежа являются минимизация длины межэлементных соединений; минимизация площади, занимаемой элементами; равномерное расположение элементов по площади подложки.

Эскиз топологии должен быть выполнен на миллиметровой бумаге в масштабе 10:1 или 20:1.

При составлении топологического чертежа необходимо учитывать следующие основные ограничения, накладываемые тонкопленочной технологией:

- пассивные и активные элементы располагаются на расстоянии не менее 1 мм от края подложки;

- входные и выходные контакты располагаются вдоль длинных сторон подложки на расстоянии не менее 1 мм от края;

- навесные элементы (компоненты) устанавливаются в специально отведенные места на расстоянии не менее 0,5 мм от пленочных элементов и не менее 0,6 мм от контактных площадок; минимальное расстояние между навесными компонентами 0,3 мм;

- длина проволочных выводов навесных компонентов должна находиться в пределах от 1 до 5 мм;

минимально допустимое расстояние между пленочными элементами (в том числе и контактными площадками) 0,2 мм;

- размеры пленочных резисторов должны быть кратными 0,05 мм;

- минимальная длина резистора lmin не менее 0,5 мм;

- минимальная ширина резистора bmin не менее 0,2 мм;

- минимально допустимая ширина проводников 0,1 мм;

- минимально допустимые размеры контактных площадок для припайки внешних выводов 0,4х0,4 мм, а для приварки навесных элементов - 0,2х0,25 мм.

5.2 Пример выполнения методического задания №2- пример выполнения топологии ГИМС

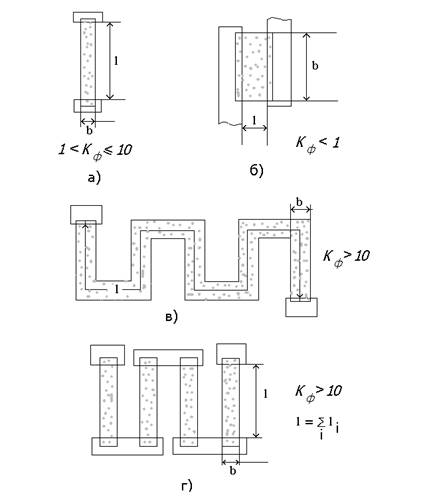

Размер и конфигурация пленочных резисторов находится по заданным номиналам резисторов Ri, удельному поверхностному сопротивлению пленки Rs, выбранному из таблицы 6, и мощности, рассеиваемой на резисторе (см. таблица 6).

Для определения размеров резисторов находим их коэффициент формы

Кфi= Ri/Rs.

Для примера возьмем материал нихром с удельным поверхностным сопротивлением RS=400 Ом/квадрат. Результаты заносим в таблицу 7.

Расчет длины резистора проводим по формуле.

Т а б л и ц а 6 - Характеристика материалов пленочных резисторов

|

Предпоследняя цифра номера студенческого билета |

Материал |

RS, Ом/квадр. |

Р0, мВт/мм2 |

|

0 |

Нихром |

400 |

20 |

|

1 |

Сплав МЛТ-3 |

500 |

20 |

|

2 |

Нитрид тантала |

400 |

30 |

|

3 |

Сплав РС-3001 |

800 |

20 |

|

4 |

Сплав РС-3710 |

2000 |

20 |

|

5 |

Нихром |

500 |

20 |

|

6 |

Сплав МЛТ-3 |

500 |

20 |

|

7 |

Нитрид тантала |

500 |

30 |

|

8 |

Сплав РС-3001 |

1000 |

20 |

|

9 |

Сплав РС-3710 |

2500 |

20 |

Ширина резистора определяется как bi=li/KФi.

Результаты расчетов заносим в первую строку таблицы 7.

Т а б л и ц а 7 - Размеры пленочных резисторов

|

|

R1 |

R2 |

R3 |

||||||

|

|

KФ1 |

l1, мм |

b1, мм |

KФ2 |

l2, мм |

b2, мм |

KФ3 |

l3, мм |

b3, мм |

|

Рассчетн. значение |

20 |

1,48 |

0,07 |

10 |

1,73 |

0,17 |

2,5 |

1,73 |

0,692 |

|

Оконча-тельное значение |

20 |

4,0 |

0,2 |

10 |

2,0 |

0,2 |

2,5 |

1,75 |

0,7 |

Так как ширина резисторов b1 и b2 получилась менее 0,2 мм, то принимаем их ширину равной 0,2 мм и пересчитываем их длину. Длину резистора l3 округляем до 1,75 мм и пересчитываем его ширину. Новые результаты заносим во вторую строку таблицы 7.

Конфигурация всех типов пленочных резисторов в зависимости от их коэффициента формы приведены на рисунке 6.

Определим площадь, занимаемую резисторами,

SR=SR1+SR2+SR3=0,8+0,4+1,225=2,425 мм2.

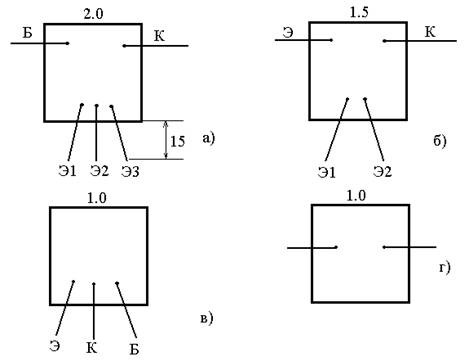

Навесные элементы с указанием их размеров приведены на рисунке 7.

Площадь, занимаемая навесными элементами схемы, равна

S=SVT1+SVT2+SVT3+SVD1=4+1+1+1=7 мм2.

Общая площадь, занимаемая пленочными резисторами и навесными элементами, равна 9,425 мм2. Учитывая площадь соединений, промежутки между элементами ИМС и расстояние от края подложки, следует увеличить суммарную площадь подложки в 4-5 раз, т. е. её площадь должна составить не менее 50 мм2. Из таблицы 8 выбираем подложку с размерами 10х10 мм.

Рисунок 6 - Конфигурации пленочных резисторов

Т а б л и ц а 8 - Рекомендуемые размеры подложек для гибридных ИМС

|

Длина, мм |

30 |

30 |

30 |

24 |

20 |

16 |

12 |

10 |

|

Ширина, мм |

24 |

16 |

12 |

20 |

16 |

10 |

10 |

10 |

Составляем топологический чертеж ИМС, размещая рассчитанные элементы на поле подложки (см. рисунок 8).

а) трехэмиттерный,

б) двухэмиттерный,

в) одноэмиттерный: биполярные транзисторы;

г) диод.

Рисунок 7 - Конструкции навесных элементов

Рисунок 8 - Чертеж топологии ГИМС

Список литературы

1. Лачин В.И., Савелов Н.С. Электроника – Ростов-на-Дону «Феникс, 2000, -448 с.

2. Алексенко А.Г., Шагурин И.И. Микросхемотехника. - М.: Радио и связь, 1990. -496 с.

3. Ефимов И.Е., Горбунов Ю.И., Козырь И.Я. Микросхемотехника. Проектирование, виды микросхем, функциональная Схемотехника. -М.: Высшая школа, 1987.-416 с.

4. Степаненко И.П. Основы микроэлектроники. -М.: Сов. Радио, 2004.-424 с.

5. Игнатов А. Н. Микроэлектронные устройства связи и радиовещания. - Томск: Радио и связь, Томское отделение, 1990.-400с.

6. Конспект лекций Схемотехника 1. Жолшараева Т.М. АИЭС. Алматы, 2010.− 81 с.

7. Угрюмов Е.П. Цифровая схемотехника.- СПб.: БХВ – Санкт-Петербург, 2000. - 528 с.

8. Гольденберг Л.М. и др. Цифровые устройства и микропроцессорные системы. Задачи и упражнения: Учебное пособие. - М.: Радио и связь, 1992 . - 256 с.

9. Бирюков С.А. Применение цифровых микросхем серий ТТЛ и КМОП.2-е изд.- М.: ДМК, 2000. - 240 с.

10. Калабеков Б.А. Цифровые устройства и микропроцессорные системы. Учебник для техникумов связи.- М.: Горячая линия –Телеком, 2000. – 336 с.

11. Новиков Ю.В., Скоробогатов П.К. Основы микропроцессорной техники. Курс лекций. – М.: ИНТУИТ.РУ. «Интернет-университет информационных технологий», 2003. – 440 с.

12. Пухальский Г.И. Проектирование микропроцессорных систем. Учебное пособие для вузов.- СПб.: Политехника, 2001.–544 с.

13. Цифровая и вычислительная техника: Учебник под ред. Э.В.Евреинова.- М.: Радио и связь, 1991. - 464 с.

14. Бойко В.И., Гуржий А.Н., Жуйков В.Я. и др. Схемотехника электронных устройств. Цифровые устройства.- СПб.: БХВ – Петербург, 2004. – 512 с.

15. Бойко В.И., Гуржий А.Н., Жуйков В.Я. и др. Схемотехника электронных устройств. Микропроцессоры и микроконтроллеры.- СПб.: БХВ – Петербург, 2004. – 464 с.

16. Сташин В.В., Урусов А.В., Мологонцева О.Ф. Проектирование цифровых устойств на однокристальных микроконтроллерах. – М.: Энергоатомиздат, 1990. – 224 с.

17. Петрищенко С.Н. Цифровые устройства и микопроцессоры. Конспект лекций для студентов специальности 050719 – Радиотехника, электроника и телекоммуникации дистанционной формы обучения. – Алматы: АИЭС, 2006. – 36 с.

18. Лебедев О.Н. и др. Изделия электронной техники. Цифровые микросхемы. Микросхемы памяти. ЦАП и АЦП: Справочник.- М.: Радио и связь, 1994. – 248 с.

19. Лебедев О.Н. Применение микросхем памяти в электронных устройствах: Справочное пособие. – М.: Радио и связь, 1994. – 216 с.

Св.план 2011 г., поз. 196