АЛМАТЫ ЭНЕРГЕТИКА ЖӘНЕ БАЙЛАНЫС УНИВЕРСИТЕТІ

Электроника және компьютерлік технологиялар кафедрасы

Т.М.Жолшараева, Ұ.Қ.Дегембаева

СХЕМОТЕХНИКА

Оқу құралы

(0В0704 – Есептеу техникасы және бағдарламалық қамту, 0В0719 – Радиотехника, электроника және телекоммуникация және 0В0702 – Автоматтандыру және басқару мамандықтары бойынша оқудың барлық түріндегі студенттер үшін)

УДК 004.31/38:621.38 (075.8)

ББК 32.844 Я73

Схемотехника:

Ж79 Оқу құралы / Т.М.Жолшараева, Ұ.Қ.Дегембаева;

АЭжБУ. Алматы, 2011. – 80 бет.

ISBN 978−601−7307-21-9

Негізгі аналогты және сандық электрондық құрылғылар қарастырылды. Құрылымдық және принципиалды схемалар, уақытша диаграммалар келтірілген және құрылғылардың жұмыс істеу принципі сипатталған.

Оқу құралы 5B070400 – Есептеу техникасы және бағдарламалық қамтамасыз ету мамандығында оқитын студенттерге арналған және оны 5B070200 – Автоматтандыру және басқару мен 5B071900 – Радиотехника, электроника және телекоммуникациялар мамандықтарында оқитын студенттер қолдана алады.

Без. 98, 13 кесте, әдеб. кор. – 15 атау.

ББК 32.844Я73

Пікір берушілер: ТЭАКТ, техн. ғыл. д.- ры, проф. Ш.Б.Биттеев

АЭжБУ, техн. ғыл. д.-ры, проф.З.С.Куралбаев

Қазақстан Республикасының Білім және Ғылым Министрлігінің 2011 ж. арналған басылым жоспары бойынша шығарылды.

ISBN 978−601−7307-21-9

© «Алматы энергетика және байланыс университеті» КЕАҚ, 2012 ж.

Білімнің қай саласына болса да, анықтама беру әрдайым қиын болып келеді, себебі бұл жағдайда негізінен бір тұтас болып келетін бұл саланы бөлуге тура келеді. Соның өзінде де әлдебір ғылым саласының нақтылы объектілерін ретке келтіреміз десек, бізге санақ нүктелері керек болып шығады. Осы мақсатымызға жетуге ғылыми түсініктер көмектесе алады. Сондықтан, тәуекел деп, алдыңыздағы кітапта қарастырылатын физикалық электроника, микроэлектроника, микроэлектрондық технология және схемотехника деген білім салаларына мағыналы анықтамаларды беріп көрейік. Қазіргі замандағы электрониканың орасан зор “ғимаратын” салғанмен, зерттеушілер өздеріне келесі сұрақтарды қойды: электрониканың жұмыс істеуі ең жақсы ма, оның шеше алмайтын міндеттері бар ма, ғылыми-техникалық революция ұсынатын жаңа түйінді мәселелерді қойғанда қиындықтар туады. Расында да, ақпаратты (информацияны) көзбен шолатындай етіп бейнелеу, оптикалық құбылыстардың қатыстыруын әрқашанда керек қылады. Міне, сондықтан, болашақ ақпараттық жүйелерді жасау тәсілдердің жаңаларының арасында «оптоэлектроника» маңызды орын алады. Оптикалық құбылыстардың ерекшеліктері электрондық құбылыстармен үйлесе (тіркесе) отырып оптоэлектрондық ақпараттық жүйелерге (ОАЖ) жаңа, зор мүмкіншіліктер істеп береді. Яғни, оптоэлектроника, оптика мен электрониканың мүмкіншіліктерінен асып түседі.

Кейбір анықтамаларға көшкенге дейін, ең алдымен, келесі бетте көрсетілген көзқарас жүйесінің кестесін (диаграммасын) қарастырайық. Бұл кесте осы курс пәндерінің арасындағы ішкі байланыстарын бақылауға мүмкіндік береді де, оқулықтың мазмұнымен таныстырады.

1 Аналогтық құрылғылардың схематехникасы

1.1 Дифференциалды күшейткіш

1.1.1 Дифференциалды күшейткіштің жұмыс жасау режимі.

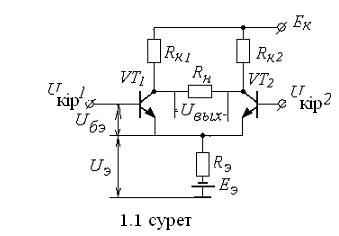

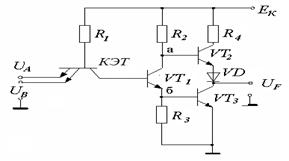

Дифференциалды күшейткіш (1.1 суретті қара) дифференциалды сигналдар

деп аталатын әр түрлі кіріс сигналдарды күшейтеді. Оны

биполярлы және униполярлы транзисторларда құруға

болады. Ол өз алдына параллелді-тең каскад немесе теңгерілген

көпірді білдіреді.

Дифференциалды күшейткіш (1.1 суретті қара) дифференциалды сигналдар

деп аталатын әр түрлі кіріс сигналдарды күшейтеді. Оны

биполярлы және униполярлы транзисторларда құруға

болады. Ол өз алдына параллелді-тең каскад немесе теңгерілген

көпірді білдіреді.

Тұрақты токтың ортақ Rэ эмиттерлі кедергісінің екі күшейткіші арқылы салынады. Rк1 = Rк2 коллекторлық жүктемелер. Ұқсас VT1 және VT2 транзисторлары Rк1 және Rк2 резисторларымен бірге көпір иығын құрайды, оның бір диагоналіне Ек қайнар көзі, екінші жағына – Rн жүктемесі кіреді.

Каскад қорегі екі Eк = Eэ

қайнар көзінен жүзеге асады, яғни қоректің

![]() сомалық күшейткіші.

сомалық күшейткіші.

![]() арқылы

ортақ нүктеге қатысты VT1 және VT2

эмиттерлер потенциалы қысқарады, сонымен қатар потенциалдар

келісуіне қажеттілік етпейді.

арқылы

ортақ нүктеге қатысты VT1 және VT2

эмиттерлер потенциалы қысқарады, сонымен қатар потенциалдар

келісуіне қажеттілік етпейді.

Дискреттік транзисторларда абсолюттік симметрияны алу қиын, сондықтан сапалы ДК интегралдық микросхемаларда құралады.

ДК жұмысының мүмкін болатын режимдерін қарастырайық:

а) тыныштық режимі. ДК-тің екі кірісі де жерленген, яғни

![]() .

.

Эмиттер-базасының кернеу тыныштығы минус Uэ

![]() тең. Өз кезегінде эмиттердегі кернеу

тең. Өз кезегінде эмиттердегі кернеу

![]() болады.

болады.

Демек, базада кернеу![]() болады.

болады.

Транзистордың екеуі де ашық,

активті режимде жұмыс жасауда. Тыныштық тогы

![]() ағуда. Олар

Rк1

және

Rк2-де бірдей

ағуда. Олар

Rк1

және

Rк2-де бірдей

кернеу түсуін қадағалайды.

Демек, ![]() . Uшығ Rн –дан

алынады.

. Uшығ Rн –дан

алынады.

![]() .

.

Эмиттерлер тогы Iэ1= Iэ2; Iэ = Iэ1+ Iэ2.

Схемалардың артықшылықтары:

- ЭҚҚ-нің орнын басатын қайнар көзі керек емес;

-

кернеу көзінің

тұрақты еместігінен және температураның

тұрақсыздығынан дрейф кішірейеді. Мысалы, Ек кернеу

қорегін үлкейткен жағдайда немесе қоршаған

ортаның коллекторларға кернеу жетілдіруі таңбасына және

көлеміне қарай бірдей болса ![]() , осыдан шығады,

, осыдан шығады,

![]() ;

;

б) кіріс сигналдарының режимі. Сигнал берудің үш әдісін қарастырайық:

1) ес>0 сигналы транзисторлар базасының арасымен беріледі (1.2 a суретті қара).

Онда

![]() ,

,

![]() .

.

Коллекторлы токтың жетілуі 0<![]() , коллекторлы кернеудің жетілуі 0>

, коллекторлы кернеудің жетілуі 0>![]() . Шығыс кернеу

. Шығыс кернеу

![]() .

.

Коллектор тогының өзгерісі эмиттер тогының өзгерісіне әкеледі

0<![]() ,

эмиттердің ортақ тогы

,

эмиттердің ортақ тогы ![]() , демек,

, демек,

![]() –эмиттердің тұрақты тогы.

–эмиттердің тұрақты тогы.

Эмиттерде кернеу жетілуі жоқ, UЭ тұрақты. Яғни тұрақты құраушысының кернеу тұрақтануы орынды, ауыспалы құраушысының кері байланысы жоқ;

2) сигнал базалардың біреуіне беріледі, ал екіншісі жерсіздендірілген (1.2 б суретті қара). Мұндай кіріс дифференциалды кіріс деп аталады.

![]()

![]()

![]() база тогы өседі.

Демек,

база тогы өседі.

Демек,

![]() коллектор тогы да және

коллектор тогы да және

![]() эмиттер тогы да өседі.

Коллектордағы

кернеу

эмиттер тогы да өседі.

Коллектордағы

кернеу ![]() азаяды.

Эмиттерлі токтың қосындысы

азаяды.

Эмиттерлі токтың қосындысы

![]() тұрақты.

Демек,

тұрақты.

Демек,

![]() ,

,

![]() ,

,

![]() .

Кіріс кернеу,

оның алдындағы жағдайдағыдай

.

Кіріс кернеу,

оның алдындағы жағдайдағыдай

![]() ;

;

3) сигналдар

![]() және

және

![]() екі кірісіне екі тәуелсіз қайнар

көзінен беріледі (1.2 суретті қара). Мұнда суперпозиция

принципі әділ.

екі кірісіне екі тәуелсіз қайнар

көзінен беріледі (1.2 суретті қара). Мұнда суперпозиция

принципі әділ.

![]() ,

,

мұндағы K – ДК-тің күшейту коэффициенті.

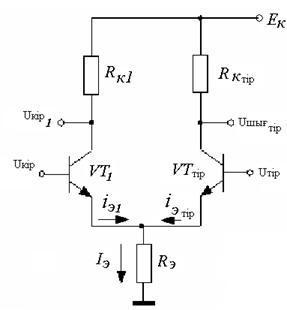

1.1.2 Тұрақты ток генераторымен дифференциалды күшейткіш.

1.3 сурет

Кіріс сигналдардың түрлілігі дифференциалды сигнал деп аталады.

Синфаздық сигнал –

бұл екі кіріске бір уақытта әсер ететін сигнал, мысалы,

кернеу қорегін, температураны және т.б. өзгерістерді сол

себептен өзгертетін сигнал, яғни бұл бөгет, ал

оның ықпалын төмендету керек. Синфаздық сигналдың

(СС) қасиетін төмендету үшін эмиттер тогын

тұрақтандыру керек. Екі кіріске коллекторлар тогын

Iк1 және

Iк2

үлкейтуге дайын синфаздық кернеу әсер етеді деп алайық.

Ал олардың қосындысы тұрақты өлшем болып

саналатын Iэ

тең. Яғни коллектор тогы

үлкеймейді және коллектор кернеуі мен кіріс өзгермейді.

Эмиттер тогын тұрақтандыру үшін эмиттер кедергісін ![]() көбейту керек,

бірақ ол кезде кернеу қорегі үлкейіп өзгереді.

Транзисторларда

көбейту керек,

бірақ ол кезде кернеу қорегі үлкейіп өзгереді.

Транзисторларда ![]() орнына ток көзін немесе тұрақты

токта аз ғана кернеуі бар, ал ауыспалы токта көп кернеуі бар

тұрақты ток генераторын (ТТГ) қойған абзал (1.3

суретті кара).

орнына ток көзін немесе тұрақты

токта аз ғана кернеуі бар, ал ауыспалы токта көп кернеуі бар

тұрақты ток генераторын (ТТГ) қойған абзал (1.3

суретті кара).

ТТГ схемасына VT3 транзисторы, VD диоды, R1, R2, R3 резисторлары және қайнар көзі – Еэ кіреді.

Iэ тогы эмиттерлер, VT1 және VT2

дифференциалды күшейткіші тогының сомасы болып табылады

және ол VT3-те тұрақты токтың

генераторымен беріледі. ТТГ схемасы – бұл жалпы базамен схема бойынша

күшейткіш. Оның шығыс кернеуі схемадағы RЭ-дан

көбірек . VT3 базасына орын ауыстыру R1,

VD, R2 бөлгіштері арқылы беріледі. VD диоды

![]() термокомпенсация үшін әділ қызмет

етеді.

термокомпенсация үшін әділ қызмет

етеді.

R1>> R2, Rэ

шарты орындалу керек. I1 тогы R1

тұрақтылығы арқылы, себебі R1 үлкен

және температураға еш тәуелді емес. Өз кезегінде

Кирхгофтың бірінші заңына байланысты

![]() .

.

Температураны жоғарылатқан кезде VT3 кіріс сипаттамасы солға ығысады, яғни эмиттер Iэ3 тогы көбейеді. Бір уақытта VD диодының кернеуі азайып, I2 тогы көбейеді. Осыдан шыға, I1 ‑ I2 тең, Iб3 тогы азаяды. Iк3 = a Iб3 тогы да азаяды. Осыған сай, дифференциалды күшейткіштің Iэ эмиттер тогы тұрақты болады.

Iэ-ды аналитикалық жолмен анықтайық.

Iб3 << Iэ болғандықтан, Iэ3 = Iк3 = Iэ есептеуге болады, онда

![]() . (1.1)

. (1.1)

Iб3 << I1 болғандықтан, I1 = I2. 1.3 суретінде көріп тұрғандай

![]() . (1.2)

. (1.2)

(1.1)

суретінен ![]() ескере отырып, Iэ табамыз.

ескере отырып, Iэ табамыз.

,

,

яғни Iэ тогы температураға тәуелді емес, ТТГ-нан да сол сұралады.

1.1.3 Дифференциалды күшейткіштердің түрлендірілген схемалары.

ДК-ның түрлендірілген схемаларында келесілер қолданылады:

а) ДК кірістеріне қосымша транзисторлары қойылады (Дарлингтон жұбы), олардың кіріс кернеулері әлдеқайда жоғары және ток тасымалдау коэффициенті екі транзисторға тең;

б) ДК кірісінің алдына эмиттерлік қайталағыштар қойылады, олардың кіріс кедергісі бірнеше килоом;

в) кірісінде өрістік транзисторларымен ДК;

г) динамикалық жүктемесімен ДК.

1.1.4 Динамикалық жүктеменің дифференциалды күшейткіші.

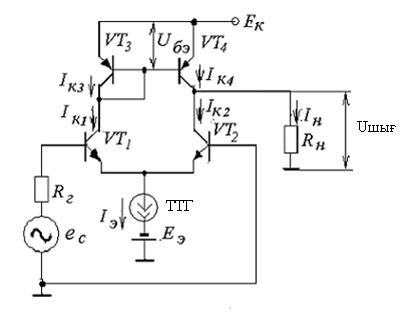

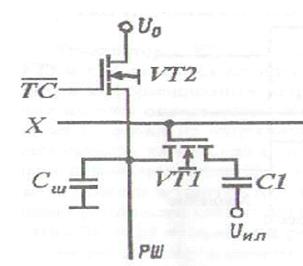

Ku күшейткішінің күшейту коэффициентін арттыру үшін Rк коллекторлық жүктемені арттыру қажет, бірақ ондай жағдайда, Ек қорек көзінің кернеуін арттыру керек болады. Интегралды схемаларда Rк үлкеюі микросхемалардың көлемі мен көлемдерінің үлкеюіне әкеледі. Сондықтан АЖ-лерде динамикалық жүктемелер қолданылады, яғни Rк1 және Rк2 резисторларының орнына VТ3 және VТ4 транзисторлары қойылады, ал олардың тұрақты токта төмен кедергілері, ауыспалы токта жоғары кедергілері болады. VТ3 және VТ4 транзисторлары негізгіге қарағанда қарама-қарсы.

VT1 және VT2 транзисторлар (n-p-n-типті) – негізгі, VТ3 және VТ4 транзисторлар (p-n-p-типті) – коллекторлық жүктеме. Бұл транзисторлар коллекторлар арқылы жалғанған. VТ3 транзисторы диодты қосылу кезінде пайдаланылады. Эмиттерлік тізбекте схемаға синфазды сигналдың ықпалын азайту үшін тұрақты ток генераторы (ТТГ) қойылады.

ДК кірісі – дифференциалды, шығысы ‑ біртактілі. VТ3 және VТ4 транзисторлары токты айна схемасы бойынша қосады да – токтың шағылдырғышы болып табылады. Iк1 тогы, VТ3-мен ағып, VТ3 және VТ4 Uбэ3=Uбэ4 транзисторының базасында бірдей ығысу тудырады. Сондықтан Iк4= Iк3, а Iк3 Iк1 тогы болып табылады.

1.4 сурет

Өз кезегінде Iк4=Iк1. VТ4 тогы VT1 тогының өзгерістерін қайталайды, яғни VТ4 тогы толығымен Iк1 қайталайды, сондықтан VТ3 және VТ4 жұбы айналы ток деп аталады.

![]() , және Кu тауып

көрейік. Кірісіне ec сигналы берілді делік.

, және Кu тауып

көрейік. Кірісіне ec сигналы берілді делік.

![]() және

және

![]() базаларының токтарын жетілдіру. Онда

коллекторлар тогы

базаларының токтарын жетілдіру. Онда

коллекторлар тогы

![]()

және

.

.

Себебі

![]() , онда

, онда

.

.

ДК шығысындағы ток

![]() тең.

тең.

ДК шығысындағы ток b есе күшейіп, екі еселенді.

![]()

ДК шығыс кернеуі, мұнда

![]() - келесі каскадтың кіріс кернеуі.

- келесі каскадтың кіріс кернеуі.

ДК күшейту коэффициенті.

![]() кезінде

кезінде

![]() кедергісі бірнеше жүздеген

килоомға дейін қамтамасыз болуы мүмкін, демек,

кернеуі бойынша ДК күшейту коэффициенті жүздеген және

мыңдаған килоомға дейін жете алады.

кедергісі бірнеше жүздеген

килоомға дейін қамтамасыз болуы мүмкін, демек,

кернеуі бойынша ДК күшейту коэффициенті жүздеген және

мыңдаған килоомға дейін жете алады.

Сондықтан, ток шағылдырғышы кернеуі бойынша күшейтудің жоғары коэффициентін алуға және біртактілік кірісінде сигналды екі еселеуге мүмкіндік береді.

1.2 Күшейткіштердің шығыс каскады

Шығыс каскадтар – бұл қуаттылық күшейткіші. Олар максималды мүмкіндікті ПӘК және минималды жолақсыз бұрмаланулардың жүктемесінде максималды қуаттылық алуға қызмет етеді.

Микроэлектроникада А класы ПӘК-тің төмендігінен сирек қолданылады. Ең жиі қолданылатыны В және АВ класты екі тактілік күшейткіштер.

1.2.1 Қарапайым екі такттілік схема.

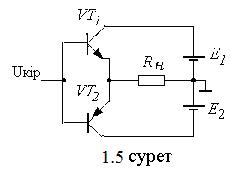

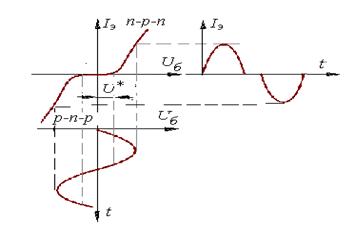

В класстық күшейткіштің қарапайым екі такттілік схемасын комплиментарлық транзисторларда қарастырайық (1.5 суретті кара).

VT1 – n-p-n, VT2 – p-n-p –типті транзистор.

VT1 – n-p-n, VT2 – p-n-p –типті транзистор.

Rн жүктемесі эмиттерлі тізбекке жалғанған, яғни транзистор схема бойынша ортақ коллекторға қосылған, сондықтан, бұл эмиттерлік қайталағыш ток күшейтудің үлкен коэффициентінің шартынан, қуаттылық жағынан үлкен күшейту береді.

Тыныштық кезінде екі транзистор да жабық күйде, себебі Uэб = 0 (класс В).

Кірісіне ауыспалы кернеудің дұрыс доғасын жібергенде VT1 – ашылады, ал VT2 – жабылады. Ток +Е1 ‑ КЭ1 ‑ Rн ‑ – Е1-дан ағындайды.

1.6 сурет

Кірісіне ауыспалы кернеудің кері доғасын

жібергенде VT1 – жабылады, VT2 – ашылады.

Ток +Е2 ‑ Rн ‑ЭК2

‑ – Е2-ден ағындайды. Осылайша, схема екі тактілі

жұмыс жасайды: бірінші тактіде VT1 ашық, екіншіде

‑ VT2, яғни күшейткіштің

шығысында екі полярлы сигнал орын алады. Қуаттылықта

күшейту коэффициенті ![]() .

.

Схеманың кемшілігі, ол жолақсыз

бұрмаланудың жоғары коэффициенті. Ал 1.6 суретте бірлескен

таралатын ![]() сипаттама

келтірілген. Шығысында дұрыс және теріс доғаның

ұзақтығы сигналдың жартыпериодынан да аз

(синусоиданың бөлігі күшеймейді). Шығыс Iэ

тогында импульстік характер бар, яғни өз спектрінде көптеген

гармоникалары бар. Ол кішкене Uшығ-да, U* ерекше

маңызды.

сипаттама

келтірілген. Шығысында дұрыс және теріс доғаның

ұзақтығы сигналдың жартыпериодынан да аз

(синусоиданың бөлігі күшеймейді). Шығыс Iэ

тогында импульстік характер бар, яғни өз спектрінде көптеген

гармоникалары бар. Ол кішкене Uшығ-да, U* ерекше

маңызды.

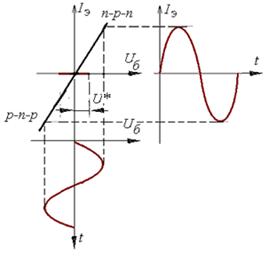

1.2.2 Екітактілі қуаттылық күшейткіш.

Кернеудің деңгейінің жылжыту

схемасынан жолақсыз бұрмалануларды болдыртпау үшін,

транзисторлар қорына бөлек ығысулар кіреді (1.7 суретті

қара). VD1 және VD2 диодтарында

U* кернеудің құлауы пайда болады, ол VТ1

координата басынан транзистордың жұмыс нүктесін солға

және VT2 – оңға бұрады (1.8 суретке

қара).

Кернеудің деңгейінің жылжыту

схемасынан жолақсыз бұрмалануларды болдыртпау үшін,

транзисторлар қорына бөлек ығысулар кіреді (1.7 суретті

қара). VD1 және VD2 диодтарында

U* кернеудің құлауы пайда болады, ол VТ1

координата басынан транзистордың жұмыс нүктесін солға

және VT2 – оңға бұрады (1.8 суретке

қара).

Тасымалдау сипаттамасы түзу жолақты

білдіреді. Осыдан келіп, жолақсыз бұрмаланулар азаяды. Бұл

диодтар әр кезде ашық, себебі ![]() қорек көзінің

сомалық

қорек көзінің

сомалық

кернеуі кіріс сигналынан әрқашан көбірек.

1.8 сурет

Базалық тізбекте трансформаторсыздық күшейткіштің қуаттылығын кернеуді бөлгішімен түрлерін қарастырайық (1.9 суретті қара). Мұндай схема басқаша қосымша симметриясы бар схема деп аталады. Мұнда R1, R2, R3 – АВ класында ығысуды тудыру үшін кернеуді бөлгіш.

![]() шарты

орындалуы керек.

шарты

орындалуы керек.

Ортаңғы R2 нүктесі нөлдік потенциалға ие екені айқын. Екі транзистордың базасы ауыспалы токпен жерленген деп есептеп, кіріс кернеуін базалардың біреуіне жіберу керек. Сигнал бір фазадан екі транзисторға берілетіндіктен, олар кезекпен жұмыс жасайды. Әдетте R2 орнына диодтар қояды. Әр диодта U*= 0,7 В құлайды, ол АВ класты тәртіпті қамтамасыз ететін ығысуды тудырады.

1.9 сурет - Ортақ коллектормен транзисторларды қосу схемасы

1.3 Операциялық күшейткіштер

1.3.1 Операциялық күшейткіштердің негізгі параметрлері және белгілеуі

Операциялық күшейткіш – ол тұрақты токтың дифференциалды кірісі мен бір тактілі шығысымен универсалды күшейткіші болады.

Идеалды ОК келесі параметрлерге ие:

-

![]() кернеуімен

күшейту коэффициенті;

кернеуімен

күшейту коэффициенті;

- Rкір Þ¥ кіріс кедергісі;

- Rшығ Þ0 шығыс кедергісі.

Мұндай сипаттамалар терең кері

байланысты (КБ) қолдануға мүмкіндік береді,

және ОК қасиеттері тек ОК тізбегінің элементтерінің

параметрлерімен анықталады. Түрлі ОК-терді пайдалана отырып,

түрлі математикалық операцияларды жүзеге асыруға

болады. Сондықтан бұл күшейткіштер

Мұндай сипаттамалар терең кері

байланысты (КБ) қолдануға мүмкіндік береді,

және ОК қасиеттері тек ОК тізбегінің элементтерінің

параметрлерімен анықталады. Түрлі ОК-терді пайдалана отырып,

түрлі математикалық операцияларды жүзеге асыруға

болады. Сондықтан бұл күшейткіштер

Операциялық деп аталды.

ОК-тің шартты белгісі 1.10 суретте келтірілген.

Мұнда:

кіріс 1 –инверторламаушы кіріс, яғни шығыс сигналы фаза бойынша кіріс сигналымен сәйкес;

кіріс 2 – инверторлаушы кіріс, яғни шығыс сигналы фаза бойынша кіріс сигналымен қарама-қарсы;

шығыс – бір тактілі;

+Еп және ‑Еп –‑ екі қорек көзінің қорытындысы Еп немесе екі полярлық кайнар көзі.

ОК жиілік коррекциясының сыртқы тізбегіне қосылуға, әдетте, көптеген қорыту санына ие болады. Ал олар күшейткіштің амплитудалық-жиілік сипаттамасының (АЖС) керек күйін тудырады.

ОК-тің сипаттамасы идеалдыдан кішкене ғана айырмашылығы бар.

ОК-тің негізгі параметрлері:

![]() а) дифференциалды сигналдың күшейту

коэффициенті

а) дифференциалды сигналдың күшейту

коэффициенті

б) Синфазды сигналдың күшейту коэффициенті

в) ОК синфазды сигналының әлсіреу коэффициенті (децибелда):

г) Rкір кіріс кедергі, әдетте 400 кОм (ондаған кОм-нан ондаған Мом дейін жетеді);

д) шығыс кедергі Rшығ = 20 ¸2000 Ом;

е)

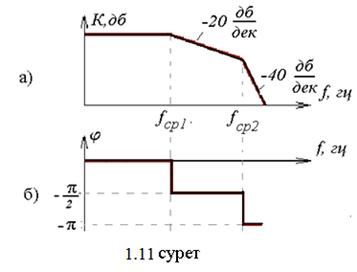

амплитудалы-жиілік сипаттама (АЖС) – ![]() – күшейту коэффициентінің жиіліктен тәуелділігі

(логарифмдік

масштабта линияланған сипаттама – Боде диаграммасы)

– күшейту коэффициентінің жиіліктен тәуелділігі

(логарифмдік

масштабта линияланған сипаттама – Боде диаграммасы)

![]()

![]() 1.11,а

суретте келтірілген. ОК АЖС-ы бөлек каскадтардың сомалық

АЖС-сын білдіреді. Он есе жиіліктің өзгеруі (декадаға) кернеу

бойынша күшейту коэффициентінің он есе азаюына әкеледі

(яғни минус 20 дБ).

1.11,а

суретте келтірілген. ОК АЖС-ы бөлек каскадтардың сомалық

АЖС-сын білдіреді. Он есе жиіліктің өзгеруі (декадаға) кернеу

бойынша күшейту коэффициентінің он есе азаюына әкеледі

(яғни минус 20 дБ).

Екі каскадты ОК-те АЖС-ның екі сынығы бар (әр каскад бір сынық әкеледі);

ж) ОК фазажиілікті сипаттама (ФЖС) – сигнал

фазасының жиіліктен тәуелділігі

ж) ОК фазажиілікті сипаттама (ФЖС) – сигнал

фазасының жиіліктен тәуелділігі ![]() (1.11,б суретке қара). Жоғары

жиіліктерде әр каскад минус

(1.11,б суретке қара). Жоғары

жиіліктерде әр каскад минус

![]() -ге тең фазалық ығысу

тудырады. ФЖС

-ге тең фазалық ығысу

тудырады. ФЖС

![]() -ге кешігеді, мұнда n – ОК

каскадтарының саны.

-ге кешігеді, мұнда n – ОК

каскадтарының саны.

ОК жұмысының тұрақтануы үшін АЖС және ФЖС түзетуді керек етеді;

и) ![]() ‑

күшейтудің жалғыз жиілігі, яғни күшейту

коэффициенті бірге тең жиілігі;

‑

күшейтудің жалғыз жиілігі, яғни күшейту

коэффициенті бірге тең жиілігі;

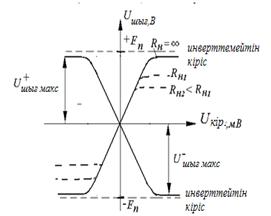

к) амплитудалы сипаттама немесе тасымалдау сигналының сипаттамасы – шығыс кернеуінің кіріс кернеуіне тәуелділігі Uшығ=f(Uкір) 1.12 суретте келтірілген.

Әдетте Uшығ.макс=Еп-1 В.

л) егер Uшығ = 0 жағдайда, және тағы да = 0 жағдай болса, онда ОК теңдігі орын алады.

1.12 сурет 1.13 сурет

Шын ОК-те схема ішінде баланс айырғышы орын алады, соның салдарынан Uшығ = 0 кезінде Uшығ.сдв¹0 пайда болады (1.13 суретті кара);

м) U нолдік кір. ығ. немесе бастапқы ығысу – бұл шығыс кернеуі нөльге тең болуы үшін кірістерінің біріне берілетін тұрақты кернеу. Ол шамамен 1...3 мВ тең;

н) кіріс токтардың түрлілігі Iкір сдв=Iб1- Iб2‑ 5…50 нА;

п) мүмкін болатын синфаздық кернеулердің диапазоны – бұл ОК-дің көп немесе аз – 3…13 В қалыпқа кірмеуі үшін екі кірісте де максималды бірдей кернеу беріледі.

1.3.2 Екі каскадты операциялық күшейткіш.

1.14 сурет

Екі каскадты Операциялық күшейткіштің схема-үлгісі 1.14 суретте көрсетілген. Дифференциалды кіріс күшейткіш VT1 ¸ VT4 транзисторларында құрастырылған. Негізгі транзисторлар VT1 және VT2 – p-n-p-типті.

Динамикалық жүктеме (VT3 және VT4 ‑ n-p-n-типті транзисторлар) өз кезегінде токты айна немесе ток шағылдырғышын ұсынады. ДК ток айнасымен дифференциалды кіріс пен бір тактілі шығысты білдіреді. ТТГ1 эмиттер тізбегінде эмиттер тогын тұрақтандыру үшін және дрейф кернеуін төмендету үшін керек. Каскад ОК-тің кіріс параметрлерінің қажетін қамтамасыз етеді.

Жалпы эмиттер схемасымен құрама VT5 және VT6 транзисторларда құралған екінші каскад, амплитуда күшейткіші болып табылады. ОК кернеуіндегі керек ететін күшейту коэффициентін қамтамасыз етеді. Жүктемелік карсылас каскадының орнына ТТГ2 ток көзі қолданылады. СК »30 пФ сыйымдылығы – жиілік сипаттамасын түзету үшін керек. VD1 және VD2 кіріс каскадында бастапқы жұмыс нүктесінде ығысуы пайда болу үшін диодтары керек.

Кіріс каскадына: VT7 (n-p-n-типті)

және VT8 (p-n-p-типті)

транзисторлардың комплементарлы жұбы, VD1

және VD2 диодтары, ГСТ2

тұрақты ток генераторы, VT6 транзисторы кіреді.

Шығыс каскады АВ класының екі тактілі қуат күшейткіші

болып табылады. ГСТ2, VD1, VD2

және VT6–нен тұратын кернеу бөлгіші VT7

және VT8 транзисторларының жұмыс нүктесінің

ығысуын тудырады және де ![]() .

Кажетті бастапқы ығысу, айтылып кеткендей, VD1

және VD2 диодтарымен беріледі. Бұл диодтар кіріс

күшейткішінің тыныштық режимінде температураның

тұрақтандыруын қамтамасыздандырады.

.

Кажетті бастапқы ығысу, айтылып кеткендей, VD1

және VD2 диодтарымен беріледі. Бұл диодтар кіріс

күшейткішінің тыныштық режимінде температураның

тұрақтандыруын қамтамасыздандырады.

Сигнал болмаған кезде ОК кірісінде Uшығ = 0 тогы Iж = 0 жүктемесі арқылы болады. VT7 және VT8 транзисторлары арқылы аз ғана бастапқы ток ағады, ал ол VT7 транзисторында плюс UVD1 және VT8 транзисторында минус UVD2 ығысуымен келісілген. Диодтар тура бағытта қосулы және әр уақытта ашық, себебі кернеудің дұрыс орналасқан кезінде VT6 қорек көзінің кернеуінің арқасында + Еп1 и ‑ Еп2 диодтардың анодына катодына қарағанда дұрыс кернеу берілді. Екі транзитордың базасы да ауыспалы токпен жерсізденген деп есептеуге болады, себебі диодтардың кедергілері ауыспалы құраушыда нөлге жақын. VT7 және VT8 транзисторлары кезекпен ашық. Кернеудің дұрыс орналасқан кезінде VT6 коллектордан берген кезінде транзистор VT8 жабылады, ал VT7 ашылады. Ток мына тізбекпен ағады: + Еп1, кэVT7, Rн, ‑ Еп1. Кернеудің кері орналасқан кезінде VT6 коллектордан берген кезінде транзистор VT7 жабылады, ал VT8 ашылады. Ток мына тізбекпен ағады: + Еп2, Rн, кэVT8, ‑ Еп2.

1.3.3 Сыртқы тізбектер.

Операциялық күшейткіштерде сыртқы тізбектер қолданылады:

а) жиілік сипаттаманың коррекциялау тізбектері – жиілікті-тәуелді RC-тізбектері;

б) нөлдік кірісін ескере, шығысында нөлдік кернеуді орнату үшін теңестіру тізбектері;

в) қорғаныш тізбектері:

1) жоғары кіріс кернеуінде кірісіндегі тесіктен;

2) шығысындағы қысқа тұйықталудан шамамен 400 ом резистор жүйелі қосылады;

3) қосылудың дұрыс емес қарама-қарсылығынан қоректену қайнарының кері полюстенуінен;

4) қорек көзінің қатты қызып кетуінен;

г) кері байланыс тізбектері.

Әдетте, ОК-да жағымсыз кері байланыс

қолданылады, себебі онсыз ![]() кезінде

де күшейту коэффициенті шексіздікке ұмтылады және

кезінде

де күшейту коэффициенті шексіздікке ұмтылады және

![]() шекті

мәнге жете алады.

шекті

мәнге жете алады.

Жағымсыз кері байланыс рұқсат етеді:

берілген функциялармен схема құру;

күшейту коэффициентінің керегіне қол жеткізу;

схеманың тұрақтылығын арттыру;

керекті ![]() және

және

![]() қол жеткізу;

қол жеткізу;

сызықты және сызықсыз бұрмалануларды азайту.

Сигналдардың күшейткіші мен шешуші күшейткіштерді қарастырайық.

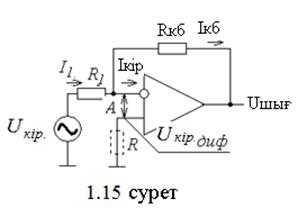

1.3.4 Инверторлаушы күшейткіш.

Мына схемада (1.15 суретті қара) жорамалдарды қабыл аламыз:

![]() ;

;![]() .

(1.1)

.

(1.1)

![]() және

және  болған соң, онда

болған соң, онда![]() .

.

Осыдан келе А нүктесін жерсіздендірген деп санауға болады.

Кирхгофтың бірінші заңымен

![]() , ал

, ал ![]() болғандықтан, онда Iкір=0

және осыдан шығатыны

болғандықтан, онда Iкір=0

және осыдан шығатыны

![]() .

.

Инверторлаушы күшейткіштің күшейту коэффициентін анықтайық

(1.2)

(1.2)

1.2 суретте көрсетілгендей, инверторлаушы күшейткіштің күшейту коэффициенті ОК параметрлеріне тәуелді емес, кері байланыс элементтерімен анықталады. Мұнда кернеу бойынша параллелді кері байланыс орын алады.

Егер ![]() ,

онда (1.15 суретті кара) күшейткіш инвертор болып табылады.

,

онда (1.15 суретті кара) күшейткіш инвертор болып табылады.

Кіріс токтарды симметрлеу үшін (теңестіру)

R резисторы қойылады, ал ол параллелді жалғанған Rкб

және R1 сияқты анықталады

![]() .

.

1.3.5 Терістемейтін күшейткіш.

1.16 а суретте терістемейтін күшейткішің схемасы көрсетілген.

Rкб–R1 тізбегі кернеу бойынша жүйелі

жағымсыз кері байланыс (ЖКБ) тудырады. Кіріс сигналы терістемейтін

кіріске беріледі. Мысалға, (1.1) шарттары орындалады делік. Мұнда

![]() және

және![]() . 1.16,а суреттен Uшығ

= I1R1,=I1 (R1+Rкб) табамыз,

осыдан шыға, терістемейтін күшейткіштің күшейту коэффициенті

. 1.16,а суреттен Uшығ

= I1R1,=I1 (R1+Rкб) табамыз,

осыдан шыға, терістемейтін күшейткіштің күшейту коэффициенті

![]() тең.

тең.

Егер ![]() және

және ![]() (1.16,б

суретті кара), онда ол кернеудің қайталағышы. Кернеу бойынша

(ЖКБ) 100% орын алады.

(1.16,б

суретті кара), онда ол кернеудің қайталағышы. Кернеу бойынша

(ЖКБ) 100% орын алады.

Шығысында сигнал кіріс сигналын қайталайды.

1.3.6 Шешуші күшейткіштер.

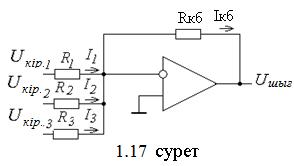

1.3.6.1 Терістейтін сумматор (1.17 суретті кара).

1.17

суреттен ![]()

шығады,себебі

![]() ,

,

![]()

Егер

![]() ,

онда

,

онда

![]() .

.

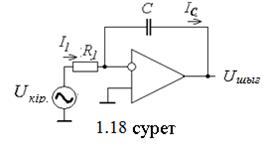

1.3.6.2 Терістейтін интегратор (1.18 суретті кара).

(1.1)

шартынан ![]() шығады.

Конденсатор

арқылы ток

шығады.

Конденсатор

арқылы ток  тең,

тең,

ал кіріс тогы  .

.

(1.1) шарты орындалғаны үшін,

![]() және

және ![]() .

.

Осыдан шығатыны, ;

;

![]() .

.

Мұнан интегралдап,

![]() аламыз.

аламыз.

Ukip, Uшыг-тан сызықты тәуелді, яғни интегратор схемасы кернеудің сызықты өзгеретін генераторының қарапайым схемасы болып табылады.

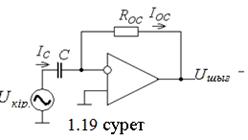

1.3.6.3 Терістейтін дифференциатор (1.19 суретті кара)

ТокRкб

-ге тең,

-ге тең,

С сыйымдылығы арқылы ток

тең.

тең.

Кіріс ток нөлге тең

болғандықтан, ![]()

және

.

Мұнан

.

.

1.3.6.4 Логарифмдік күшейткіш (1.20 суретті қара).

Мұнан ![]() ,

,

Мұнда

![]() ,

,  .

.

Осыдан шығатыны,![]()

.

.

Логарифмдеп

аламыз.

аламыз.

1.3.7 ОК-тың сызықсыз жұмыс режимі.

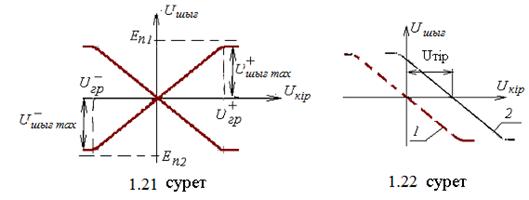

Егер ![]() (1.21 суретті қара),

онда ОК сызықты режимде жұмыс жасайды,

(1.21 суретті қара),

онда ОК сызықты режимде жұмыс жасайды, ![]() кезінде – сызықсыз кілтті

немесе импульсті режим.

кезінде – сызықсыз кілтті

немесе импульсті режим.

ОК кірістерінің біріне кернеу берген кезде екінші сипаттамадағы жібергіш функция осы мәнге жылжиды. Мысалы, ОК инвенторлаушы кіріске (1.22 суретті кара) Uоп кернеуі беріледі, сонда инвенторлаушы кірістің сипаттамасы (қисық 1) оңға қарай Uоп мәніне ығысады (қисық 2).

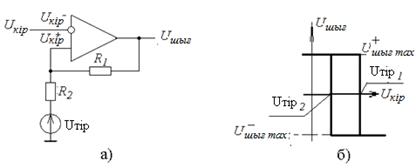

1.3.8 Аналогты компаратор.

Аналогты компаратор (1.23, а суретті кара) тіреуіш кернеумен аналогты сигналды салыстыру үшін қолданылады.

1.23, а суретте инверторламайтын кіріске Uтір. тіреуіш кернеуі, ал инверторлаушы кіріске ‑ аналогты сигнал Uкір. беріледі.

1.23 сурет

Сонымен қатар мына шарттар орындалады (1.23,б суретте – ОК жібергіш функция сипаттамасы):

егер:

Uкір< Uтір.,

онда ![]() ,

,

егер:

Uкір> Uтір,

онда ![]() .

.

1.24 сурет

Uкір = Uтір, теңдігі кезінде Uшығ = 0. ОК компараторының күшейту коэффициенті жүз мыңдаған болғандықтан, онда компаратор шығысы қарама-қарсы мәнге ауысады.

1.24 суретте компаратор кернеуінің кірісі мен шығысының уақытша диаграммалары келтірілген.

1.3.9 Шмидт триггері.

Шмидт триггері тұрақты тепе-теңдіктің екі жағдайына ие және аналогты сигналды импульсті сигналға түрлендіреді.

Өткен жолы көорсетілген 1.25, а суретте триггердің принципиалды схемасы, ал 1.25, б суретте – оның жібергіш функция сипаттамасы келтірілген.

![]() және

және

![]() резисторлары

дұрыс кері байланыс тудырады, ал ол триггер шығысын дұрыстан

бұрысқа және керісінше жағдайға көшу

тәріздес ауысуды қамтамасыз етеді.

резисторлары

дұрыс кері байланыс тудырады, ал ол триггер шығысын дұрыстан

бұрысқа және керісінше жағдайға көшу

тәріздес ауысуды қамтамасыз етеді.

Триггер ауысулары болатын босағалық кернеу (1.25, б суретті қара) былай анықталады:

1.25 сурет

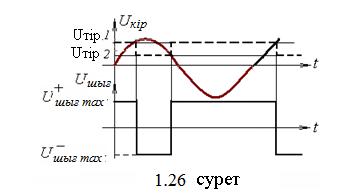

![]() 1.26 суреттен,

Uкір = 0 кезінде,

шығысында

1.26 суреттен,

Uкір = 0 кезінде,

шығысында

![]() екені көрінеді, себебі инвенторламайтын

кірісте Uкір+

Uтір>0.

Uкір

екені көрінеді, себебі инвенторламайтын

кірісте Uкір+

Uтір>0.

Uкір

![]() дейін үлкейген кезде,

ығысуға

тең Uкір+ триггері

дейін үлкейген кезде,

ығысуға

тең Uкір+ триггері

![]() -ға ауысады.

-ға ауысады.

![]() ,

,

![]() дұрыс кері байланыстың арқасында

ендігі Uкір+

ығысуы

дұрыс кері байланыстың арқасында

ендігі Uкір+

ығысуы ![]() -ге тең болады.

Uкір

-ге тең болады.

Uкір

![]() -ге дейін азайған кезде,

триггердің

-ге дейін азайған кезде,

триггердің ![]() -ге кері ауысуы пайда болады және т.с.с.

-ге кері ауысуы пайда болады және т.с.с.

Босағалық кернеу біреуінен екіншісіне секіріп ауысқандықтан, триггер басқарушы компаратор болып табылады.

1.4 Электрлік сигналдардың генераторы

1.4.1 Синусоидалы тербелістердің RC-генераторы.

ОК-ге RC-генераторының синусоидалы тербелісінің артықшылықтары деп – қарапайымдылығы, арзандығы, ал кемшіліктері деп – генерация жиілігінің болғандығы аз ғана тұрақтылығы.

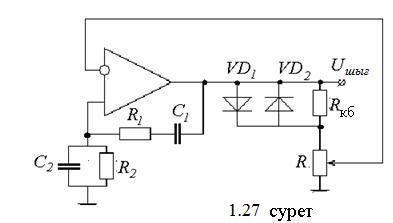

Вин көпірімен генератор схемасын қарастырайық (1.27 суретті қара).

![]() Вин көпірі (R1, R2,

C1, C2 элементтері) дұрыс кері байланыс

тудырады. Кері байланыстың

буынының жіберу коэффициенті квазирезонансты

Вин көпірі (R1, R2,

C1, C2 элементтері) дұрыс кері байланыс

тудырады. Кері байланыстың

буынының жіберу коэффициенті квазирезонансты

жиілікте,

жиілікте,

тең.

тең.

Егер ![]() және

және ![]() болса, онда

болса, онда ![]() ,

, ![]() .

.

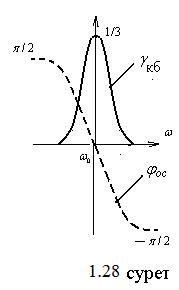

1.28 суретте Вин көпірінің АЖС және

ФЖС келтірілген, бұдан ![]() квазирезонансты жиілікте

квазирезонансты жиілікте ![]() фаза ығысуы

нөлге тең, ал

фаза ығысуы

нөлге тең, ал ![]() кері байланыс буынының жіберу

коэффициенті 1/3-ке тең. Сол себептен

кері байланыс буынының жіберу

коэффициенті 1/3-ке тең. Сол себептен ![]() фаза балансының шарттары

орындалады, сондықтан

фаза балансының шарттары

орындалады, сондықтан ![]() күшейткішінің фазалық

ығысуы да нөлге тең, себебі кері байланыс сигналы

инвертерлемейтін кіріске беріледі.

күшейткішінің фазалық

ығысуы да нөлге тең, себебі кері байланыс сигналы

инвертерлемейтін кіріске беріледі.

(1.27 суретті қара) схемасында R кедергісі

бұрыс кері байланыс тереңдігін жанастыру үшін

қосылған, ал ол ![]() амплитуда балансының шартын

орындауға өте қажет. VD1 және VD2 қарсы-параллелді

диодтар шығыс сигналдың амлитудасын тұрақтандыру

үшін қосылған. Тым үлкен Uшығ үшін

диодтар кезектесіп, тура өткізгіштік қалыпқа кіреді

және күшейту коэффициентін азайта отырып, бұрыс кері байланыс

сигналдың амплитудасын үлкейтеді.

амплитуда балансының шартын

орындауға өте қажет. VD1 және VD2 қарсы-параллелді

диодтар шығыс сигналдың амлитудасын тұрақтандыру

үшін қосылған. Тым үлкен Uшығ үшін

диодтар кезектесіп, тура өткізгіштік қалыпқа кіреді

және күшейту коэффициентін азайта отырып, бұрыс кері байланыс

сигналдың амплитудасын үлкейтеді.

1.4.2 Релаксациялық тербелістердің генераторы.

1.4.2.1 Автотербелісті мультивибратор.

Импульсті генераторлардың

құрылуы кезінде қолданылатын интегралды операциялық күшейткіштердің

(ОК) негізгі қасиеттері болып, үлкен кіріс (жүздеген килоом)

және кіші (ондаған ом) шығыс кедергі, үлкен (жүз

мыңдаған) күшейту коэффициенті және екі фазалық

кірістің бары табылады. ОК-тің шығыс кернеуінің

полярлығы ![]() және

және

![]() кернеулерінің үлкенімен және

сәйкес келетін инверттелген кірістермен анықталады.

кернеулерінің үлкенімен және

сәйкес келетін инверттелген кірістермен анықталады.

ОК-дағы тікбұрыштық импульстердің генераторларының құрылу принципі ОК шығысының оның инвертті кірісімен қосылу кезіндегі тұйықталған резисторлы немесе резисторлы-сыйымдылықты дұрыс кері байланыс (ДКБ) тізбегін алуға негізделген. ДКБ тасқын (лавина) тәріздес процестердің пайда болуын қамтамасыз етеді.

ОК-тегі автотербелістік

мультивибратордың жұмысын қарастырайық, онда ДКБ R1,

R2 кернеу бөлгішімен шығысынан инвертті кірісіне

қамтамасыз етіледі (1.29, а суретті қара). Бір

квазитұрақты тепе-теңдіктен екіншісіне мультивибраторды

ауыстыру ![]() кір релаксациялық өзгерістердің арқасында болады.

кір релаксациялық өзгерістердің арқасында болады.

Егер t=0 кезінде ОК қорек

көзін қосса, онда шығыс кернеу өседі, R1,

R2 бөлгіштердің арқасында кернеу U+кір

инвенторламайтын кірісте өседі, ал олардің одан сайын өсуіне

әкеледі. Тасқын тәріздес процесс нәтижесінде

шығыс кернеу секірмелі түрде Е+ дейін

өседі, ал кіріс U+кірgE+-ге дейін, мұнда

g-= R2/(R1 +R2), Е – интегралды операциялы

күшейткіштің қорек көзінің кернеуі. Сол кезде

![]() вх өзгеріп үлгермей нөлге тең болады. С

конденсаторының R арқылы заряды басталады. Ол Е+-ге

tзар =RC

тұрақты уақытымен талпынатын

вх өзгеріп үлгермей нөлге тең болады. С

конденсаторының R арқылы заряды басталады. Ол Е+-ге

tзар =RC

тұрақты уақытымен талпынатын

![]() кір–нің өсуіне әкеледі. t1 моментінде,

кір–нің өсуіне әкеледі. t1 моментінде,

![]() кір = U+кір =gE+

секірмелі түрде режим өзгереді және

кір = U+кір =gE+

секірмелі түрде режим өзгереді және

![]() -ге

дейін өзгереді, ал U+кір =g

-ге

дейін өзгереді, ал U+кір =g![]() тең. Бұл процесс тасқын тәріздес өтеді.

тең. Бұл процесс тасқын тәріздес өтеді.

![]() -ге дұрыс қоршаумен қосылған, ал корпусқа

бұрыс қосылған С конденсаторы,

-ге дұрыс қоршаумен қосылған, ал корпусқа

бұрыс қосылған С конденсаторы,

![]() -ға дейін +С, R тізбегі бойынша зарядталуға

тырысады, ОК шығысы –С. t2 моментінде,

-ға дейін +С, R тізбегі бойынша зарядталуға

тырысады, ОК шығысы –С. t2 моментінде,

![]() кір =–g

кір =–g![]() , қайтадан лақтыру кездеседі.

, қайтадан лақтыру кездеседі.

Бұл процестер периодты түрде қайталанады. Импульс ұзақтығы мынаған тең:

.

.

Импульстерді қайталау периоды

.

.

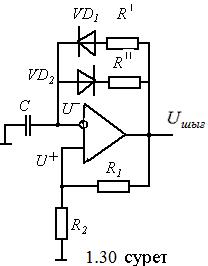

Құбырлылық Q=T/tu =2.

Q>2 құбырлылығымен мультивибратор құру үшін, заряд тізбегінің дәреже тізбегінен айырмашылығы болуы қажет (1.30 суретті қара). Қуат: Uшығ, R’, VD1, С корпус тізбегімен, ал дәреже: +С, VD2, R’’, корпус, –С тізбегімен жүреді.

Дұрыс импульс ұзақтығы

![]() .

.

Бұрыс импульс ұзақтығы

![]()

![]() .

.

![]() Құбырлылық

Құбырлылық

1.4.2.2 Операциялық күшейткіште сызықты өзгеретін кернеудің генераторы (СӨКГ).

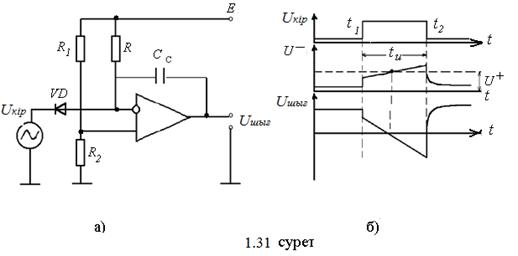

1.31,а суретінде СӨКГ схемасында RC интеграцияланушысы – ОК бұрыс кері байланыс тізбегіне қосылған тізбекше. СӨКГ ұзақтығы tи дұрыс Uкір қарама-қарсылық импульстармен басқарылады. Кіріс импульстер VD диод базасына беріледі, оның эмиттері ОК-тің инвенторлаушы кірісіне жалғанған.

Генератордың бастапқы жағдайы (t < t1), Uкір = 0 кезінде VD диоды ашық, ток R, диод VD қорек көзінен ағады, Uкір сигнал көзі, корпус.

![]() .

.

Инвентерлалмайтін кірісте кернеу

мұнда

мұнда  .

.

![]() кезінде ОК-ті шектік режиміне

ауыстыру үшін,

кезінде ОК-ті шектік режиміне

ауыстыру үшін, ![]() кернеу

кернеу ![]() -ды

соншалықты асады. Бұл жағдайда С конденсаторы UC

(0) = E кернеуіне дейін зарядталған. Конденсатор заряды Е+

тізбегі бойынша жүреді, ОК шығысы, С, VD, сигнал

көзі Uкір, корпус

-ды

соншалықты асады. Бұл жағдайда С конденсаторы UC

(0) = E кернеуіне дейін зарядталған. Конденсатор заряды Е+

тізбегі бойынша жүреді, ОК шығысы, С, VD, сигнал

көзі Uкір, корпус ![]() .

.

Tтура арасының жұмыс жүрісінің құрылуы.

t1 моментінде tu ұзақтығымен кіріс

импульсін беру кезінде (1.31, б суретті қара.) диод VD жабылады. Е

көзінің дұрыс ![]() кернеу секірісі ОК-ті

сызықты күшейту режиміне ауыстырады және ОК оған кіріс

болып есептелетін Е тұрақты кернеуін интегралдайды.

кернеу секірісі ОК-ті

сызықты күшейту режиміне ауыстырады және ОК оған кіріс

болып есептелетін Е тұрақты кернеуін интегралдайды. ![]() кірісінде

дұрыс секіріс t1 моментте шығысында бұрыс

секіріс береді.

кірісінде

дұрыс секіріс t1 моментте шығысында бұрыс

секіріс береді.

![]() кернеуінің

үлкеюін тудырып қуаттанған С конденсаторы баяу қуатсызданады,

ал ол шығыс кернеуінің азаюын ескертеді.

кернеуінің

үлкеюін тудырып қуаттанған С конденсаторы баяу қуатсызданады,

ал ол шығыс кернеуінің азаюын ескертеді.

Tтура = tи жұмыс барысының ұзақтылығы және RC

тізбегі уақытының тұрақтылығы tи

интервал соңында конденсатор нөлге дейін қуатсызданып, ![]() дейін қайта

қуатталатындай етіп есептелініп қоюы керек.

дейін қайта

қуатталатындай етіп есептелініп қоюы керек.

Tкері араның кері жүріс құрылуы.

t2 моментінде кіріс импулсінің соңында VD диоды

ашылады. ![]() секірмелі түрде

секірмелі түрде ![]() дейін азаяды, сол кезде ОК

күшейту режимінен шығады.

дейін азаяды, сол кезде ОК

күшейту режимінен шығады. ![]() Е+-ге дейін көбейеді, ал үлкен жылдамдықпен

Е+-ге дейін көбейеді, ал үлкен жылдамдықпен ![]() -ге дейін

қуатталған конденсатор, ашық VD диодының

кедергісімен анықталып, нөлге дейін қуатсызданады және

бастапқы UС (t) =

-ге дейін

қуатталған конденсатор, ашық VD диодының

кедергісімен анықталып, нөлге дейін қуатсызданады және

бастапқы UС (t) = ![]() кернеуіне дейін қуатталады.

кернеуіне дейін қуатталады.

Берілген Tпр кезіндегі RC уақытының қажетті тұрақтысын анықтаймыз.

![]() қуаттанып

кеткен конденсаторының тогы тұрақталуға және

қуаттанып

кеткен конденсаторының тогы тұрақталуға және  тең болуға

жақын болғандықтан, Tтура арасының

тура жол жүру кезінде, конденсатордағы кернеу шамамен 2Е тең

мөлшерге дейін өзгереді. Сондықтан

тең болуға

жақын болғандықтан, Tтура арасының

тура жол жүру кезінде, конденсатордағы кернеу шамамен 2Е тең

мөлшерге дейін өзгереді. Сондықтан

![]() , осыдан

, осыдан ![]() , немесе

, немесе ![]() үшін

үшін![]()

Осылайша белгілі Tпр кезінде, С бере отырып, R мағынасын анықтауға немесе керісінше болады.

Генератор жұмысы режимінің қайта қалпына келу уақыты немесе Tкерi араның кері жүрісі

![]()

![]() .

.

Мұндағы ![]() - ашық

диодтың кедергісі.

- ашық

диодтың кедергісі.

Сызықсыздық

коэффициенті ![]() .

.

1.5 Гиратор

Гиратор – бұл электрлік схема, онда ОК-тің кері байланысына индуктивтілік катушкасын еліктеу үшін RC, тізбегі қосылған. Кейде гираторларды синтездеуші индуктивтіліктер деп атайды. Мұндай «активті индуктивтілік катушкалар» кішкене ғана жеңіл, қымбат емес корпустарда үлкен индуктивтілікті жүзеге асыруға мүмкіндік береді, яғни бұл схеманы әдеттегі катушканың орнына қолдануға болады. Негізгі кемшілігі – fжұм. жұмыс жиілігі бірнеше килогерцтен аспайды.

Гиратор жұмысының ойы – Uс

конденсаторында кернеуді қолданып, Uкір

Гиратор жұмысының ойы – Uс

конденсаторында кернеуді қолданып, Uкір ![]() кіріс кернеуі мен Iкір

кіріс тогын индуктивтілік катушкасында кернеу немесе ток тәріздес

өзін-өзі ұстасын деген мақсат болған (1.32

суретті қара).

кіріс кернеуі мен Iкір

кіріс тогын индуктивтілік катушкасында кернеу немесе ток тәріздес

өзін-өзі ұстасын деген мақсат болған (1.32

суретті қара).

Жиілікті үлкейткен кезде ![]() индуктивті кедергі өседі

және индуктивтілік катушкасында кернеу өседі. Кернеу

қайталағышы

индуктивті кедергі өседі

және индуктивтілік катушкасында кернеу өседі. Кернеу

қайталағышы ![]() шығыс кернеуінде гиратор схемасы

шығыс кернеуінде гиратор схемасы ![]() кедергісінде ОК

кірісінде қолданылады.

w жиілігінің үлкейген кезінде Uс

конденсаторының кернеуі

кедергісінде ОК

кірісінде қолданылады.

w жиілігінің үлкейген кезінде Uс

конденсаторының кернеуі ![]() = (1 /

w С)-мен

бірге азаяды. Сонымен, UR1 кіріс кернеуі, ал онымен

қатар

= (1 /

w С)-мен

бірге азаяды. Сонымен, UR1 кіріс кернеуі, ал онымен

қатар ![]() қайталағышы

да көбейеді. R2 кедергісі

қайталағышы

да көбейеді. R2 кедергісі

![]() арқылы

қайталағышының шығыс кернеуі қайтадан кірісіне

беріледі және кірісіндегі кернеу жиіліктің өсуімен бірге

өседі, яғни катушка индуктивтілігінде кернеуге тең болады.

арқылы

қайталағышының шығыс кернеуі қайтадан кірісіне

беріледі және кірісіндегі кернеу жиіліктің өсуімен бірге

өседі, яғни катушка индуктивтілігінде кернеуге тең болады. ![]() кедергісін мүмкін

болғанша аз етіп таңдаған жөн. Ол әдетте берілген

операциялық күшейткіштің жүктемесінің минималды

кедергісіне тең етіп алынады (шамамен 1 кОм).

кедергісін мүмкін

болғанша аз етіп таңдаған жөн. Ол әдетте берілген

операциялық күшейткіштің жүктемесінің минималды

кедергісіне тең етіп алынады (шамамен 1 кОм). ![]() кедергісі

кедергісі ![]() -мен салыстырғанда

көбірек болу керек, бірақ операциялық

күшейткіштің

-мен салыстырғанда

көбірек болу керек, бірақ операциялық

күшейткіштің ![]() және

және ![]() -нен 200-ден көп болмауы керек. L индуктивтілігінің

берілген мөлшерімен

-нен 200-ден көп болмауы керек. L индуктивтілігінің

берілген мөлшерімен ![]() пайдалана отырып,

пайдалана отырып,

![]() табуға болады.

табуға болады.

Гиратордың төзімділігі мына формуламен

анықталады ![]() .

.

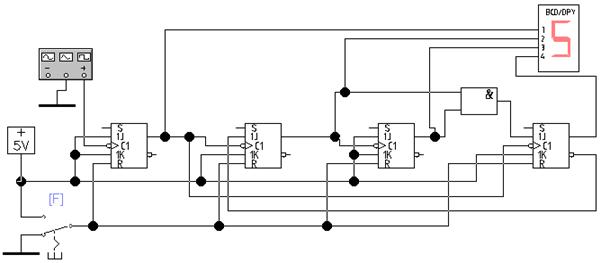

2 Цифрлық құрылғылардың схематехникасы

2.1 Негізгі логикалық операциялар мен логикалық элементтер

Логикалық функциялар – екі мәнді қабылдайтын функциялар:

F=0, егер хабарлама жалған болса;

F=1, егер хабарлама шын болса.

Логикалық операциялар логикалық функциялар арасындағы байланысты сипаттайды.

Элементарлы логикалық операцияларды жүзеге асыратын электрлік схемалар логикалық элементтер деп аталады (ЛЭ).

Қарапайым ЕМЕС, НЕМЕСЕ, ЖӘНЕ деген 3 логикалық операциялар бар.

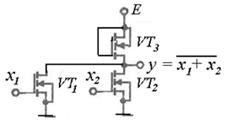

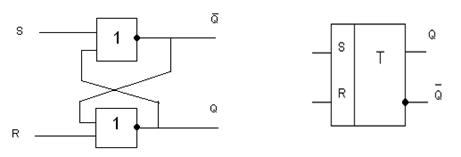

2.1 сурет

а) ЕМЕС операциясы – инверсияның логикалық мойындамауы.

![]() (F А-ға тең емес)

(F А-ға тең емес)

ЕМЕС операциясын орындайтын ЛЭ инвертор деп аталады (2.1 суретті қара).

б) НЕМЕСЕ операциясы – логикалық қосу,

дизъюнкция.

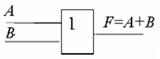

2.2 сурет

F=АÚВ, немесе F=А+В (F дегеніміз А-ға тең немесе В).

НЕМЕСЕ операциясын орындайтын ЛЭ құрастыру немесе дизъюнктор деп аталады (2.2 суретті қара).

в) “ЖӘНЕ” операциясы – логикалық көбейту немесе конъюнкция.

2.3 сурет

F=A![]() B (F

дегеніміз А-ға және В-ға тең);

B (F

дегеніміз А-ға және В-ға тең);

F=AÙB.

ЖӘНЕ операциясын орындайтын ЛЭ сәйкестік схемасы немесе конъюнктор деп аталады (2.3 суретті қара).

ЖӘНЕ, ЕМЕС, НЕМЕСЕ элементтер жинағы негізгі базис немесе элементтердің функционалды толық жүйесі деп аталады. Яғни осы элементтердің көмегі арқылы ғана кез-келген логикалық схема құруға болады.

Схематехникада басқа да

базистердің элементтері кеңінен қолданылады – олар екі сатылы

НЕМЕСЕ-ЕМЕС, ЖӘНЕ-ЕМЕС:

Схематехникада басқа да

базистердің элементтері кеңінен қолданылады – олар екі сатылы

НЕМЕСЕ-ЕМЕС, ЖӘНЕ-ЕМЕС:

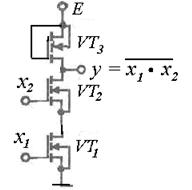

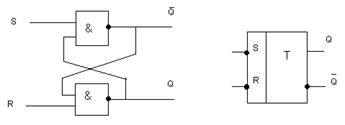

2.4. сурет

а) Пирс тілі, немесе дизъюнкция мойындамауы, немесе НЕМЕСЕ-ЕМЕС операциясы

А¯В = ![]() .

.

Шартты белгіленуі 2.4 суретінде келтірілген. Логикалық элемент Пирс элементі деп аталады.

б) Шеффер штрихы, немесе конъюнкция мойындамауы, немесе ЖӘНЕ-ЕМЕС операциясы

А½В = ![]() .

.

Шартты белгіленуі 2.5- суретінде келтірілген. Логикалық элемент Шеффер элементі деп аталады.

2.5 сурет

НЕМЕСЕ-ЕМЕС немесе ЖӘНЕ-ЕМЕС деген

микросхеманың тек бір ғана түрі арқылы кез-келген логикалық схеманы құрастыруға болады, яғни бұлардың әрқайсысы негізгі базис болып табылады.

Ең кең тарағаны Шеффер элементі ЖӘНЕ-ЕМЕС болып табылады.

Одан басқа, кең таралған көп сатылы логикалық элементтер:

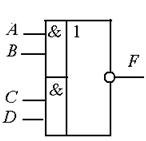

а)

![]() операциясын

орындайтын 2ЖӘНЕ-НЕМЕСЕ-ЕМЕС. Шартты

белгіленуі 2.6 суретте келтірілген;

операциясын

орындайтын 2ЖӘНЕ-НЕМЕСЕ-ЕМЕС. Шартты

белгіленуі 2.6 суретте келтірілген;

2.6 сурет

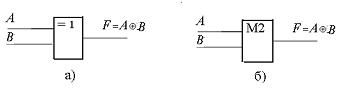

б) ерекшеленген НЕМЕСЕ, немесе екі модулі бойынша қосынды, немесе тең емес мәндік функция мына түрге ие

F =![]() Бұл дегеніміз F немесе A-ға,

немесе B-ға тең. Ерекшеленген НЕМЕСЕ логикалық

элементі кейде «бірдеңе, бірақ барлығы емес» деп

аталады.

Бұл дегеніміз F немесе A-ға,

немесе B-ға тең. Ерекшеленген НЕМЕСЕ логикалық

элементі кейде «бірдеңе, бірақ барлығы емес» деп

аталады. ![]() символы

(жалған плюс), А және В кірістері ерекшеленген НЕМЕСЕ

логикалық функциямен байланысты екенін білдіреді.

символы

(жалған плюс), А және В кірістері ерекшеленген НЕМЕСЕ

логикалық функциямен байланысты екенін білдіреді.

Алгебра логикасынан белгілі:

![]() ;

; ![]()

![]() ;

;

![]() .

.

2.1 к е с т е

|

А |

В |

А |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Ерекшеленген НЕМЕСЕ элементінің шындық кестесі 2.1 кестесінде келтірілген.

Кестеден, кірістердің біріне (бірақ барлығына емес) логикалық бірлік берілген болса, онда шығысында да бірлік пайда болатыны көрінеді. Тең емес мәнді элементтің шартты белгісі 2.7,а суретте келтірілген. Бұл элемент 2 модулі бойынша қосу операциясын орындағандықтан, оны 2.7,б суреттегідей белгілейді.

2.7 сурет

в) ерекшеленген НЕМЕСЕ-ЕМЕС, немесе тең мәнді емес функция мына түрге ие.

![]() . Бұл F инверсияға, немесе А-ға,

немесе B-ға тең.

. Бұл F инверсияға, немесе А-ға,

немесе B-ға тең.

Ерекшеленген НЕМЕСЕ-ЕМЕС шындық кестесі 2.2 кестеде келтірілген. Элементтің шартты белгіленуі 2.8 суретінде келтірілген.

2.2 к е с т е

|

А |

В |

|

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

2.8 сурет

Логика алгебрасы жағдай алгебрасы болып табылады және келесілерді қамтамасыз етеді:

а) электрондық құрылғының жұмысын логикалық функция түрінде түсіндіреді;

б) теңдеулерден электронды схемаларға көшеді;

в) оптималды схемаларды синтездеу.

ЕМЕС – ЖӘНЕ – НЕМЕСЕ операцияларын орындау реттері.

Логика алгебрасының аксиомаларынан бөлек функцияны түрлендіру үшін кең түрде де Морган формуласы қолданылады

![]() ;

;

![]() .

.

2.2 Логикалық интегралды схемалар

2.2.1 Логикалық интегралдық микросхемалардың негізгі параметрлері.

а) логикалық бірдің кіріс U1кір және шығыс U1шығ кернеулері – микросхеманың кірісі және шығысындағы жоғары деңгейлі кернеудің мәні;

б) логикалық нөлдің кіріс U0кір және шығыс U0шығ кернеулері – микросхеманың кірісі және шығысындағы төмен деңгейлі кернеудің мәні;

в) логикалық бірдің кіріс I1кір және шығыс I1шығ токтары, логикалық нөлдің кіріс I0кір және шығыс I0шығ тоқтары;

г)

сигналдың

логикалық ауысуы ![]() ;

;

д) шектік кернеу Uшек кір – кірістегі кернеу, мұнымен бірге микросхеманың жағдайы кері мәнге ауысады;

е) логикалық ИМС-ның кіріс кедергісі – кіріс кернеу өсімшесінің кіріс тогы өсімшесіне қатынасы (R0кір және R1кір деп айырады), шығыс кедергі – шығыс кернеу өсімшесінің шығыс тогы өсімшесіне қатынасы (R0шығ және R1шығ деп айырады);

ж) статикалық бөгеуілдерге тұрақтылық – кіріс кернеудің жоғарғы

U1бөг және төменгі U0бөг деңгейлері бойынша статикалық бөгеуілдің максималды мүмкін кернеуі, бұл жағдайда микросхеманың шығыс кернеуінің деңгейі әлі өзгермейді;

и) өткенде көрсетілген орташа тұтынушы қуат Pтұт орт = (P0тұт + Р1тұт)/2 , мұндағы P0тұт және Р1тұт – микросхеманың шығысында сәйкесінше нөл және бір жағдайындағы тұтынылатын қуаттар;

к) кіріс бойынша біріктіру коэффициенті Кбір, берілген схеманың кірісіне қанша аналогтық логикалық ИМС қосуға болатынын көрсетеді, және логикалық ИМС кірістерінің максималды санын анықтайды;

л) шығыс бойынша айырылыс коэффициенті Кайыр, берілген ИМС шығысына қанша аналогтық жүктеу микросхемаларын қосуға болатынын көрсетеді және логикалық ИМС-ның жүктеулік қабілетін сипаттайды.

Цифрлық интегралдық схемалар цифрлық ақпаратты өңдеу, түрлендіру және сақтауға арналған. Олар сериялармен шығарылады. Әрбір серияның ішінде функционалдық белгісі бойынша біріктірілген құрылғылар топтары: логикалық элементтер, триггерлер, регистрлер, санағыштар, дешифраторлар, шифраторлар, мультиплексорлар, демультиплексорлар және т.б. бар. Серияның функционалды құрамы неғұрлым үлкен болса, берілген серия микросхемасының негізінде жасалған цифрлық құрылғы соғұрлым көп мүмкіншіліктерге ие болады. Әрбір серияның құрамына кіретін микросхемаларда бірдей конструктивті-технологикалық атқаруы, бірдей қоректендіру кернеуі және логикалық нөл мен логикалық бірдің бірдей сигнал деңгейлері болады. Мұның бәрі бір серияның микросхемаларын бір-біріне сәйкестендіреді.Цифрлық микросхемалардың әрбір сериясының негізі логикалық элемент болып табылады. Негізі, базалық логикалық элементтер ЖӘНЕ – ЕМЕС, немесе НЕМЕСЕ – ЕМЕС операцияларын орындайды, және құрастырылу принципі бойынша келесі негізгі типтерге бөлінеді: резистивті-транзисторлы логика (РТЛ) элементтері, диодты-транзисторлы логика (ДТЛ), транзисторлы-транзисторлы логика (ТТЛ), эмиттерлі-байланысқан логика (ЭБЛ), интегралды-инжекционды логика (ИИЛ), биполярлы транзисторларда орындалған базалық элементтер. Комплементарлы МДП-құрылымдағы (КМДП) микросхемаларда металл-диэлектрик- р- және n-типті жартылай өткізгіш құрылымды МДП-транзисторлар жұбы қолданылады.

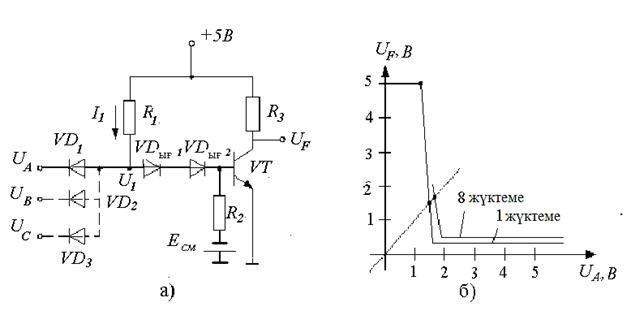

2.2.2 ДТЛ – диодты-транзисторлы логика схемасы.

ДТЛ негізгі схемасы 2.16,а суретінде келтірілген. Мұндағы VD1, VD2, VD3 диодтары және R1 резисторы конъюнктор (ЖӘНЕ) болып табылады, VT, R2, R3 элементтері – инвертор (ЕМЕС), VDСМ1, VDСМ2 жылжымалы диодтары – ЖӘНЕ және ЕМЕС логикалық элементтері арасындағы байланысты жүзеге асырады, U1 кернеуіне қатысты VT база потенциалын қозғалтады (төмендетеді). R2 резистрі ЕСМ ығысуын VT транзисторына беруге және кіріс диодтарының ашық кезінде оны кепілді түрде жабық ұстауға және транзистордың жабылу кезіндегі базаның кері тогының қосымша тізбегі ретінде қызмет атқарады.

2.9 сурет

Кірістегі кернеудің жоғары деңгейі жағдайында UA = UB = UC = U1, VD1…VD3 диодтары жабық, VDығ1, VDығ2 нүктесінің потенциалдары көтеріледі, жылжығыш диодтары ығысады, VT базасының тогы ағады.

Коллектордағы UF кернеуі нөлге дейін түседі, яғни, F = 0.

Ең болмағанда кірістердің біреуінде UA немесе UB немесе UC төмен деңгейлі кернеулері U0-ге тең болса, сәйкес диод ығысады, U1 потенциалы азаяды, VDығ1, VDығ2 жылжымалы диодтары жабылады. Uшығ = UF = U1, яғни элемент шығысында логикалық бір пайда болады.

Егер схеманың бір бөлігін алып тастасақ (2.9,а суретті қара), ол инвертерге айналады. 2.16,б суретінде оның UF = f(UA) сипаттамасы көрсетілген.

А кірісіндегі кернеу нөлге тең болса, онда VD1 диоды тура бағытта ығысқан және U1 кернеуі +0,6 В-ке тең. Бұл мән VDСМ1, VDСМ2 диодтарының ашылуына және VТ транзисторының база-эмиттерлік ауысуына жеткіліксіз. Сондықтан I1 тогы диоды арқылы ағып, сигнал көзі UA және жерлендіріледі. VТ транзисторы жабық, бұл жағдайда UF = +5 В. Егер үлкейсе, онда U1 1,2 В-қа жетпейінше өсе береді. Бұл мезетте VDСМ1, VDСМ2, VТ ашылады және I1 тогы VТ транзисторы арқылы ағып, оны толтырады. UA кернеуінің ары қарай өсуі VD1 диодын жауып тастайды, бірақ U1 мәніне және VТ транзисторының жағдайына әсер ете алмайды. Логикалық күйі 0 и 1-ге сәйкес келетін кернеу интервалдары шамамен 0 ≤ U0 ≤ 1,2 B, 1,5 ≤ U1 ≤ 5 В тең екені графиктен көрініп тұр.

Практикалық U0 әдетте 0,4 В-тан кіші, ал U1 5 В-қа жақын, бұл тұрақты ток бойынша жақсы шулық қорды (шумовой запас) қамтамасыз етеді.

Егер кіріске логикалық 1-ге сәйкес келетін кернеу берілсе, диоды теріс бағытта ығысады, алдыңғы схеманың минималды қуатын қолданады. Бірақ, кірісте логикалық 0 кернеуі болса, онда I1 тогы элементтің ішкі клеммасынан транзистор арқылы жерге ағуы керек. Бұл бірлік жүктемеге сәйкес келеді. Егер бір шығысқа n кірістер саны қосылған болса, транзистор I1-ден n есе көп ток өткізілуі керек. Егер n үлкейсе, UА кернеуі де өседі, бұл шығыс транзистор кернеуінің өсуімен бірдей. Бұл эффект 2.16,б суретінде көрсетілген.

Егер 2.9,а суретіндегі схемаға VD2,

VD3 диодтарын қосса, кірістердің біреуі

логикалық 0-ге сәйкес келген жағдайда UF

кернеуі логикалық 1-ге сәйкес келетін болады. Барлық

кірістерде логикалық бірдің кернеулері болған жағдайда

ғана шығыста логикалық нөлді алуға болады,

яғни берілген схема орындайтын логикалық операция келесі

түрде болады: ![]() ,

бұл ЖӘНЕ-ЕМЕС операциясына сәйкес келеді. Кіріс көлемін

үлкейту мақсатында қосымша диодтарды қосу арқылы

ДТЛ ЖӘНЕ-ЕМЕС базалық элементінде кіріс саны 20-ға дейін

жеткізілуі мүмкін.

,

бұл ЖӘНЕ-ЕМЕС операциясына сәйкес келеді. Кіріс көлемін

үлкейту мақсатында қосымша диодтарды қосу арқылы

ДТЛ ЖӘНЕ-ЕМЕС базалық элементінде кіріс саны 20-ға дейін

жеткізілуі мүмкін.

Типтік ДТЛ элементі үшін жіберу кідірісі 30 нс құрайды. Бұл салыстырмалы үлкен мән көп жағдайларда өткенде көрсетілген.

2.2.3 ТТЛ түрлі – схемасы.

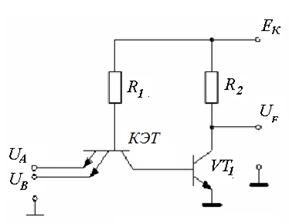

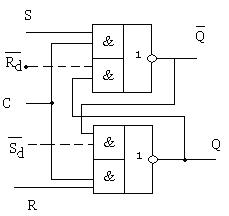

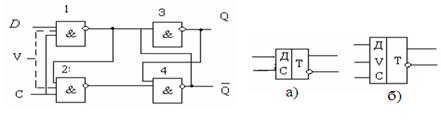

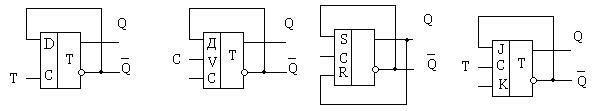

2.2.3.1 Қарапайым инвертерлі ТТЛ – транзисторлы-жеткілікті болып табылады.

Транзисторлы-транзисторлы логика схемасы (2.10 суретті қара) – ДТЛ-ның дамуының нәтижесі. Диодтар матрицасы көпэмиттерлік транзистормен (КЭТ) ауыстырылады.

2.10 сурет

Бұл диодтық логикалық схемалар мен транзисторлық күшейткішті қосатын интегралды құрылғы. КЭТ құрамында бірнеше эмиттерлер бар, олар бір-бірімен тура әрекеттеспейтін етіп орналастырылған. КЭТ тез-әрекеттесуді үлкейтуге, қолданылатын қуатты төмендетуге және микросхемаларды дайындау технологиясын кемелдендіруге мүмкіндік береді. КЭТ интегралды схемотехника кезеңінде дайындалғандықтан, дискретті компонентті ТТЛ аналогтары болмады.

ТТЛ потенциалды элементтерге жатады. ЭЕМ схемаларын құру кезінде олардың негізінде олар потенциалды байланыспен, яғни конденсатор мен трансформаторларсыз байланыстырылады.

Логикалық бірдің кернеуі U1 = 2,4 В, логикалық нөлдің кернеуі

U0 < 0,4 В.

2.10 суретінің схемасындағы VD1…VD3 диодтары КЭТ-дің эмиттерлік ауысуларымен, ал Dығ1, Dығ2 – КЭТ-дің коллекторлық ауысуларымен алмастырылған. Бұл жағдайда ЕСМ диодында R2 қажеттілігі жоғалады.

ТТЛ базалық элементі ДТЛ секілді ЖӘНЕ-ЕМЕС логикалық операциясын орындайды. Сигналдың төменгі деңгейінде (логикалық 0) КЭТ көпэмиттерлік транзистордың кірістердің ең болмағанда біреуінде транзистор қанныққан күйде болады, ал VT1 жабық. Схема шығысында кернеудің жоғары деңгейі (логикалық бір) болады. Барлық кірістерінде сигналдың жоғары деңгейі болғанда КЭТ активті инверсті режимде жұмыс жасайды (эмиттерлік ауысу кері бағытта жылжыған, ал коллекторлық – тура бағытта), VT1 қаныққан күйде болады. Схема шығысында сигналдың төмен деңгейі, яғни нөл.

Мұнда жазылған ТТЛ базалық элементі, дайындалу технологиясының қарапайымдылығына қарамастан, кейбір сипаттамаларына байланысты үлкен қолданысқа ие болған жоқ, яғни бөгеуілдерге тұрақтылығы төмен, сыйымдылықты жүкетемемен жұмыс кезіндегі тез-әрекеттілігі аз, жүктемелік қабілеттілігі төмен.

Төмен жүктемелік қабілеттілік және кіші айырылыс коэффициенті келесі түрде түсіндіріледі. VT1 транзисторының жабық күйінде R2 арқылы жүктемелік элементтердің кіріс токтары ағады, және олар көп болса, R2 коллекторлық жүктемесінде кернеудің төмен түсуі көбейеді. VT1 коллекторындағы кернеу, яғни жоғарғы логикалық деңгейдің мәні, азаяды, схема жұмысы бұзылады. Сондықтан күрделі инвертерлі ТТЛ қолданылады.

2.11 сурет

2.2.3.2 Күрделі инвертерлі ТТЛ схемасы.

Күрделі инвертерлі ТТЛ схемасы (2.11 суретті қара) екі бөліктен тұрады:

а) КЭТ көпэмиттерлі транзисторды қосатын И конъюнкторы және R1 резисторы. И схемасының 2-ден 8-ге дейін кірістері болуы мүмкін (кірістер санының көбеюі ТТЛ-дің логикалық мүмкіндіктерін кеңейтеді);

б) құрамында VT1, VТ2, VТ3, VD, R2, R3, R4 бар ЕМЕС күрделі инвертері.

Күрделі инвертерді фаза-ажыратушы каскад пен кіріс күшейткішінен тұрады деп қарастыруға болады.

Фаза-ажыратушы немесе фазоинверсті каскад (VT1, R2, R3-тен тұрады) VТ2 және VТ3 транзисторларын басқару үшін қызмет етеді. VТ1 транзисторы ауыстырып қосу шегін (порог переключения) үлкейтеді, ТТЛ-дің бөгеуілдерге тұрақтылығын арттырады.

Кірістік күшейткіш (VТ2, VТ3, VD, R4) эмиттерлік қайталағыш болып табылады.

VТ1, VТ3 транзисторлары құрамдас транзистор немесе Дарлингтон жұбы болып табылады. Жұмыстың статикалық режимдерінде VT3 схемалары VT1 күйін қайталайды. VT1 жабылса, VT3 транзисторының базасы R3 резисторы арқылы корпусқа қосылады, сонда VT3 жабық күйі қамтамасыз етіледі.

VТ2 транзисторы қаныққан және кесіліп тасталған күйде жұмыс істей алады. Жұмыстың статикалық режимдерінде оның күйі әрқашан VT3 күйіне, сәйкесінше VT1 күйіне қарама-қарсы болады. VT3 транзисторының қаныққан күйінде VT2 жабық немесе керісінше. VТ2, VТ3 транзисторлары екітактілі қуат күшейткіші болып табылады.

VD диоды VТ3 ашық кезінде VТ2 транзисторын берік жабу мақсатында қызмет етеді. VT3 транзисторының қаныққан күйі кезінде VT2 ашылу шегін көтеру арқылы оның жабық күйін қамтамасыз етеді. Шынымен:

UБЭ2 = UКЭН1 + UБЭ3 – UКЭН3 – UVD ≈ U БЭ3 - UVD < Uтаб2, мынадай мәндерге ие болғандықтан: UБЭ = 0,7 В; UКЭ=0,3 В; UVD = 0,7 В; Uтаб = 0,6 В.

UБЭ2 = UБ2 ‑ (UD+UКЭ3) = UКЭ1+UБЭ3 – UVD ‑ UКЭ3 =

=0,3 + 0,7 ‑ 0,7 ‑ 0,3 = 0.

Егер VD жоқ болса, UБЭ2 = UКЭ1 + UБЭ3 ‑ UКЭ3 = 0,7 В, мұнда VТ2 ашық.

UБЭ2 = UБ2 ‑ UЭ2 = (UКЭ1+UБЭ3н) ‑ (UКЭ3н+UD) = 0.

Егер VT1 қаныққан болса, VT3 базасы арқылы ток ағады

IБ3 = IЭ1 – IR3 = [(EК ‑ UКЭН1 – UБЭ3)/a2·R2] – (UБЭ3/R3).

VT2 транзисторы және VD диодының жабық кезіндегі VT3 транзисторының қаныққан күйін қамтамасыз ету үшін келесі шартты орындау кажет

IБ3·В3 ≥ IКН = n·I0кір жүкт ,

мұндағы В – үлкен сигнал режиміндегі токты жіберу коэффициенті;

n – қарастырылып жатқан схеманың шығысына қосылған жүктемелі ТТЛ-схемалар саны;

I0кір жүкт – жүктемелі ТТЛ-схеманың кіріс тогы.

Осы жерден берілген схеманың жүктемелік қабілеттілігін анықтауға , яғни VT3 транзисторы әлі де қаныққан режимде жұмыс істей алатын кездегі жүктемелік схемалардың максималды санын анықтауға болады:

nМАКС = IБ3·В3 / I0кір жүкт.

R4 резисторы төменгілер үшін қажет:

а) кірісте қысқа тұйықталу жағдайында VТ2 және VD қорғау;

б) схеманы логикалық нөлден логикалық бірге ауыстырған кезде коллекторлық тогын шектеу. VT1 жабылғаннан соң, VT2 транзисторы VT3 қаныққан транзисторынан бұрын ашылады, өйткені транзисторына қанығу режимінен шығу үшін біршама уақыт қажет. Нәтижесінде, біршама уақыт аралығында, VT2 және VT3 транзисторлары ашық, және Ек, VT2, VD и VT3 элементтерінен тұратын тізбек бойынша, Ек қоректендіру көзінен тұтынылып жатқан ток ағады, және қоректендіру шинасы бойыша бөгеуіл импульсі пайда болады. Бөгеуіл амплитудасын шектеу үшін, шамамен бірнеше ондаған Омға тең R4 резисторы қойылады.

ТТЛ схемасы келесі түрде жұмыс жасайды. Егер ең болмағанда кірістердің біреуінде төмен деңгейлі U0kip кернеуі болса, КЭТ эмиттерлік ауысуы ашылады да, ток ағады: +ЕК-дан, R1 арқылы, база-эмиттер ауысуы жерге. КЭТ коллекторлық ауысуы кері бағытта жылжыған (КЭТ активті режимде). База тогы IБ1 = 0, сәйкесінше, VT1 транзисторы жабылады. VT1 коллекторында кернеудің жоғары деңгейі UК1 = ЕК. VT1 эмиттеріндегі кернеу UЭ1 = 0.

VТ2 транзисторы токпен R2 резисторы арқылы ашылады. UБ3 = UЭ1 = 0 болғандықтан, VT3 транзисторы жабық және Uшығ= U1шығ.

Егер ТТЛ-дің барлық кірістерінде U1 жоғары деңгейлі болса, КЭТ эмиттерлік ауысулары жабылады, база потенциалы үлкейеді, КЭТ коллекторлық ауысуы тура бағытта жылжиды. КЭТ активті инверсті режимде жұмыс жасайды.

VТ1 және VТ3 транзисторлары ашық және қаныққан. VТ2 транзисторы және VD диоды жабық. ТТЛ шығысында төмен деңгейлі = U0 = 0. Өз кезегінде, ТТЛ ЖӘНЕ-ЕМЕС операциясын орындайды, яғни Шеффер элементі болып табылады.

ТТЛ-схемаларының тез-әрекет ету қабілеті негізінен транзисторды ауыстырып қосу кезіндегі ауыспалы процестерімен, сонымен қатар СН паразитті қосынды сыйымдылығының зарядымен анықталады. Қарапайым инвертерлі ТТЛ схемасында (2.11 суретті қара) СН сыйымдылығының заряды үлкен тұрақты уақыттан R2 резисторы арқылы шығады, бұл схеманың тез-әрекет ету қабілетін төмендетеді.

Күрделі инвертерлі ТТЛ схемасында жүктемелік сыйымдылықтың тұрақты заряды азаяды, өйткені сыйымдылығы эмиттерлік қайталағыш схемасындағы VT3 транзисторының шығыс резисторы арқылы зарядталады (Rвых 3 << R2). Осының арқасында тез-әрекет ету қабілеті артады.

2.2.3.3 ТТЛ схемаларының түрлері.

ТТЛ схемаларының келесі түрлері практикада кеңінен қолданылады:

а) Шығысының үш күйі бар ТТЛ схемасы.

Базалық ТТЛ схемаларын, қоректендіру көзінен үлкен ток қолданылғандықтан, сонымен қатар шығыс сигнал деңгейі логикалық түрде анықталмағандықтан, шығыс бойынша біріктіру мүмкін емес.

Бірақ кейде (мысалы, екі бағытты ақпараттық шиналарды дайындау кезінде) шығыстарды біріктіру керек. Бұл үшін үшінші күйі бар (жоғары-импедансты) шығысты ТТЛ қызмет етеді.

ТТЛ-дің базалық схемасына (2.12 суретті қара) қосымша R5 резисторы және VТ4 транзисторы қосылған (2.12 суретті қара). Z кірісіне төмен деңгейлі UZ = U0кір кернеуін берген кезде, VТ4 жабық және ТТЛ жұмысына әсер етпейді. Схема шығысында кіріс сигналдарына байланысты 1 немесе 0 болады.

2.12 сурет

VТ4 кірісіне жоғары деңгейлі UZ = U1ВХ бергенде, VТ4 транзистор қанығады. UК4 = 0. Бұл VТ2 және VТ3 жабылуын қамтамасыз етеді. ТТЛ толығымен жүктемеден ажыратылады, яғни токты қолданбайды да, бермейді де. Бұл күй UА және UВ кіріс сигналдарынан тәуелді емес. Бұл схемаларды шығыстары бойынша бір ортақ жүктемеге біріктіруге болады, және кез келген уақыт мезетінде жүктеме кез келген элементпен күтілуі керек, ал қалған элементте үшінші күйде қалуы қажет;

б) Шоттки транзисторлы ТТЛ схемалары

Базалық элемент схемасында қарапайым транзисторлар орнына активті режимде жұмыс істейтін Шоттки транзисторларын қолданып, ТТЛ-схемаларынң тез әрекет ету қабілеттілігін көтеруге болады. Мұнда схема транзисторларының ауыстырып қосу уақыты қысқарады. Шоттки транзисторлары негізінде жасалған логикалық ТТЛ микросхемаларын ТТЛШ микросхемалары деп атайды;

в) Ашық коллекторлы ТТЛ схемалары.

Ашық коллекторлы ТТЛ схемасы сыртқы атқарушы және индикаторлық құрылғылардың логикалық схемаларын қиыстыруға арналған, мысалы, жарықдиодты индикаторлар, лампалар, реле орамдары және т.б. Алдыңғы қарастырылғаннан айырмашылығы шығыс қуатты күшейткішінің біртактілік схема бойынша жеке жүктемелік резисторынсыз жасалуында.

Мұндай элементтің принципиалды электрлік схемасы 2.23-суретте көрсетілген. Бұл элементте, сонымен қатар, сызықсыз коррекция тізбегі жоқ. Элементтің логикалық құрылғының шығысына қойылуы және оған сигнал кванттау талаптарының төмен дәрежеде қойылуымен байланысты. Әдетте, схеманың VT2 кіріс транзисторы қарапайым элементке қарағанда, коллекторлық ток пен кернеудің үлкен мәндерінде орындалады.

Кернеудің қауіпті кері әсерлі кіріс ауысуларынан КЭТ-ті қорғау үшін ТТЛ-де эмиттерлер мен жер арасында қосымша диодтар қосылады (2.13-суретте VD1 және VD2).

2.2.4 ЭБЛ схемасы‑ эмиттерлі-байланысқан логика схемасы.

2.2.4.1 ЭБЛ схемаларының ерекшеліктері.

ТТЛ схемаларына қарағанда, эмиттерлі-байланысқан логиканың цифрлық микросхемаларының тез әрекет ету қабілеттілігі жоғарырақ. Олар қазіргі уақытта субнаносекундтық диапазонға қол жеткізді, себебі:

а) транзисторлардың қанығуы болмайды (артық заряд тасушыларды тарату уақыты t тар = 0);

б) схемада эмиттерлік қайталағыштар (ЭҚ), сыйымдылық зарядының процесін жылдамдататын жүктемелер қолданылады, эмиттерлік қайталағыштың Rшығ шығыс кедергісі аз болғандықтан, шығыс тогы үлкен;

в) логикалық ауысу азырақ ![]() .

.

Парафазды шығыстың болуы түзу және инверсті мәндер алуға мүмкіндік береді, бұл қолданылатын микросхемалар санын азайтады.

ТТЛ-дың қарапайым схемаларынан айырмашылығы – логикалық мүмкіндіктерді шешу үшін, ЭБЛ бірнеше элементтерінің шығыстарын біріктіруге болады.

2.2.4.2 Ток ауыстырып қосқышы.

ЭБЛ ерекшелігі – логикалық элемент схемасы интегралды дифференциалды күшейткіш (ДК) негізінде, токты ауыстырып қосып және ешқашан қанығу режиміне кірмейтін екі транзистордан жасалған (2.13 суретті қара) кілттік режимде (ток кілті) құрылады. Дифференциалды күшейткіш деп екі кіріс сигнал айырмасын күшейтуге арналған күшейткішті айтады. Мұнда алынған шығыс кернеуі кіріс сигналдарының абсолютті мәндеріне, сонымен қатар, қоршаған орта температурасы және басқа факторларға тәуелді болмауы керек.

![]() ,

,

мұндағы КК — күшейткіштің күшейту коэффициенті.

Транзисторлардың біреуінің

базасына, мысалы, VTтip, бір тұрақты тіреуіш

кернеу Uтip берілген.

Транзисторлардың біреуінің

базасына, мысалы, VTтip, бір тұрақты тіреуіш

кернеу Uтip берілген.![]()

![]() . Кіріске берілетін Uкір кернеуінің

Uтip-нен төмен немесе жоғары өзгеруі Iэ

эмиттерлік тұрақты тогының таратылуына әкеліп

соғады, бұл ток токтұрақтандырғыш Rэ

резисторы арқылы, VT1 және VTтip

транзисторлары арасына берілген.

. Кіріске берілетін Uкір кернеуінің

Uтip-нен төмен немесе жоғары өзгеруі Iэ

эмиттерлік тұрақты тогының таратылуына әкеліп

соғады, бұл ток токтұрақтандырғыш Rэ

резисторы арқылы, VT1 және VTтip

транзисторлары арасына берілген.

Мұнда транзисторлар қанығу режиміне кірмейді, сәйкесінше, кілтте принципиалды түрде негізсіз тасушыларды тарату уақытының интервалы болмайды.

Схеманың елеулі кемшілігі – шығыстардың шығыс кедергісі үлкен, бұл схеманың жоғары тез-әрекет ету қабілеттілігін қамтамасыз ете алмайды. Шығыс кедергісін төмендету үшін коллекторлық шығыстарға эмиттерлік қайталағыштарды қосады. Бірнеше логикалық кірістерді алу үшін бір шектік

транзистор және бірнеше параллельді

2.13 сурет қосылған кіріс транзисторларын

қолданады.

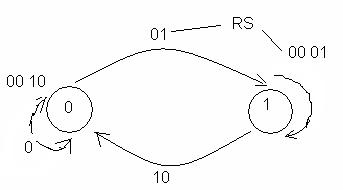

2.4.3 ЭБЛ базалық схемасының жұмыс істеу принципі

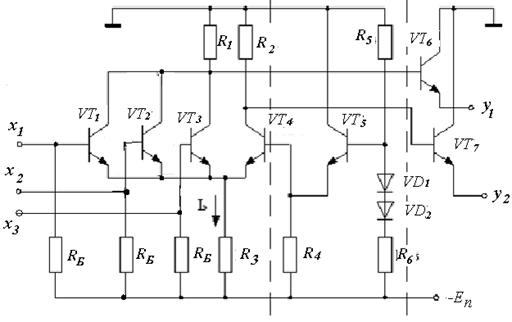

ЭБЛ функционалды схемасы үш түйіннен (тораптан) тұрады (2.14 сурет қара):

а)

VT1

¸

VT4 транзисторлары

негізіндегі ток ауыстырып-қосқышы және

R1¸R3

резисторларынан. Құрамында екі

тармақ бар: кірістік – VТ1

¸ VТ3 транзисторларында (ең көп дегенде, 9

кіріс болуы мүмкін) және R1 резисторы, VТ4,

R2 резисторы. Транзисторлар кілттік режимде жұмыс

жасайды, дәлірек айтсақ: ашық – активті режим,

қанығуға кірмейді, және жабық режим.

Тармақтардың ортақ R3 кедергісі бар.

Қоректендіру көзі En және R3

кедергісі ток генераторын құрайды, мұнда R3

>> R1, R2. Бұл эмиттерлік токтың

тұрақтылығын береді ![]() ;

;

б) тіреуіш кернеу көзінен тұрады, ол R5, VD1, VD2, R6 элементтерінде параметрлік стабилизатор қосады, және VT5 мен R4 негізіндегі эмиттерлік қайталағыш. VD1, VD2 – Uтip температуралық компенсацияны қамтамасыз етеді;

2.14 сурет

в) VT6 және VT7

транзисторлары негізіндегі шығыстық эмиттерлік

қайталағыштардан тұрады. VT6 және VT7

транзисторларының жүктемелер тізбегі ЭБЛ-ден алынған,

бұл ондағы қуаттың шашырауының азаюына және

функционалды мүмкіндіктерінің көбеюіне мүмкіндік

туғызады. VT6 және VT7

негізіндегі эммиттерлік қайталағыштары деңгейлер

жылжытқышы болып табылады, Uкір қайталайды,

төмен ![]() және

жоғары

және

жоғары ![]() деңгейлерінің

кірісі мен шығысын қамсыздандыру үшін оны 0,7 В-қа

жылжытады.

деңгейлерінің

кірісі мен шығысын қамсыздандыру үшін оны 0,7 В-қа

жылжытады.

Осылайша VT6 және VT7 негізіндегі эмиттерлік қайталағыштар келесілерді қамтамасыз етеді:

1) кіріс сигналдардың қалыптасуын;

2) ток ауыстырып-қосқышы мен жүктеме арасындағы шешілімдер;

3) жоғары жүктемелік қабілеттілік;

4) жүктеме сыйымдылығының, шығыс кедергісінің аздығы арқасында тез қайта зарядталуын.

Схемада +Еп шинасы ортақ шина болып табылады, соның нәтижесінде схема нүктелерінің потенциалы жалпы шинаға қатысты кері болады. Бірақ ТТЛ схемаларындағы секілді, ЭБЛ схемасында да оң логика принципі шыңдалған, мұнда үлкен шығыс кернеуіне логикалық бір, ал кішісіне – логикалық нөл сәйкес келеді.

Транзисторлар қанығу режиміне кірмегендіктен, ток ауыстырып-қосқышының тез әрекет ету қабілеттілігі жоғары, сонымен қатар, логикалық бір мен нөл мәндері арасындағы кернеудің логикалық өзгерістері аз. Бұл R1 және R2 резисторларының аз мәнді кедергілерін таңдау арқылы қамтамасыз етіледі, бұл транзистордың шығыс сыйымдылығының тұрақты қайта зарядталу уақытын азайту тұрғысынан өте пайдалы.

Қарастырылып жатқан схеманың y1 шығысы бойынша НЕМЕСЕ-ЕМЕС операциясын, ал у2 шығысы бойынша НЕМЕСЕ операциясын орындайтынын байқау қиын емес.

![]() ;

;

![]() .

.

VТ1 ¸ VТ3 транзисторларының базалары және En арасына қосылған RБ резисторлары, кіріс сигналдары болмаған жағдайда бұл транзисторлардың жабық күйін қамтамасыз етеді. Бұл ИС-тің қолданылмайтын кірістерінің қоректендіру көзінің шығысына қосылуы жөнінде қам жемеуге мүмкіндік береді.

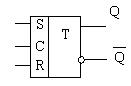

ЭБЛ шартты белгісі келесідей:

2.15 сурет

2.2.5 Өрістік транзисторлар негізіндегі логикалық элементтер.

2.2.5.1 МДЖ негізіндегі логикалық элементтер.

2.16 сурет

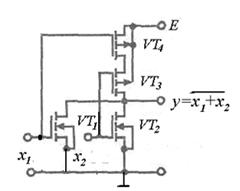

ЕМЕС, НЕМЕСЕ-ЕМЕС, ЖӘНЕ-ЕМЕС логикалық элементтерін қарастырайық.

а) МДЖ негізіндегі инвертер схемасы 2.16-суретте келтірілген.

VT1 транзисторы кілттік режимде, VT2 – әрқашан активті режимде жұмыс істейді. VT2 сызықсыз жүктеме болып табылады.

VT1 жабық болғанда, VT2

транзисторы – активті режимде, қанығуға жақын, VT1

қаныққан күйінде VT2 транзисторы –

активті, тоқтауға жақын.

VT1 жабық болғанда, VT2

транзисторы – активті режимде, қанығуға жақын, VT1

қаныққан күйінде VT2 транзисторы –

активті, тоқтауға жақын.

х кірісіне төмен деңгейлі кернеу берілгенде VT1 жабылады, VT2 қанығуға жақын, кілт шығысында кернеудің жоғары деңгейі болады. х кірісіне жоғары деңгейлі кернеу берілгенде VT1 ашылады, VT2 тоқтауға жақын, кілт

шығысында кернеудің төмен деңгейі болады.

2.17 сурет ![]() операциясы орындалады;

операциясы орындалады;

б) НЕМЕСЕ-ЕМЕС екікодылық схемасында (2.27 суретті

қара) VT1 и VT2 кірістік

транзисторлары паралелді жалғанған. Егер ең болмағанда

кірістердің біреуіне кернеудің жоғары деңгейі берілген

болса, сәйкес транзистор ашылады, және схема шығысында

төмен деңгей болады. Тек схеманың барлық кірістеріне

төмен деңгей бергенде ғана, VT1 және VT2

транзисторлары жабылып,

шығыста

транзисторлары жабылып,

шығыста

2.18 сурет жоғары

деңгей пайда болады. ![]()

2.18 суреттегі операция орындалады;

в) ЖӘНЕ-ЕМЕС екікодалық схемасында (2.18 суретті

қара) VT1 және VT2 кірістік

транзисторлары тізбектей жалғанған. Егер ең болмағанда

кірістердің біреуіне кернеудің төмен деңгейі берілген

болса, сәйкес транзистор жабылады, ток кірістік транзисторлар

арқылы жүрмейді, схема шығысында жоғары деңгей

болады. Тек схеманың барлық кірістеріне жоғары деңгей

бергенде ғана, VT1 және VT2

транзисторлары ашылып, ток жүріп, шығыста төмен деңгей

пайда болады. ![]() операциясы

орындалады.

операциясы

орындалады.

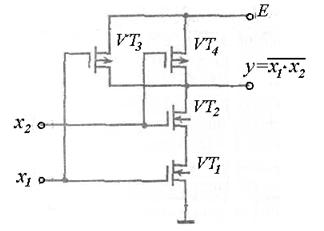

2.2.5.2 КМДЖ негізіндегі логикалық операциялар

КМДЖ микросхемаларының негізін әртүрлі типті өткізуші VT1 және VT2 МДЖ-транзисторларының ағындары арқылы жалғанған (2.19 суретті қара) кілттік каскад құрайды. VT1 транзисторында өткізгіштігі n-типті канал бар; VT2 – өткізгіштігі р-типті канал. Бірге жалғанған қақпаларға (затворы) x кірістік сигналы беріледі. деңгей, ал нөл төменгі деңгейде болып қабылданған.

2.19 сурет

Оң полярлы Е қоректендіру көзінің кернеуі 3-тен 15 В-қа дейін болады. КМДЖ микросхемалары үшін төмен деңгейдің кернеуі 0,001 В, ал жоғары деңгейлі кернеу қоректендіру көзінің кернеуіне тең.

Кіріске

жоғары деңгей кернеуін бергенде

VT1

ашылады, ал VT2![]() транзисторы жабылады. Шығыста төмен

деңгей кернеуі орнайды. Кіріске төмен деңгей кернеуін

бергенде VT1

жабық, ал VT2

транзисторы жабылады. Шығыста төмен

деңгей кернеуі орнайды. Кіріске төмен деңгей кернеуін

бергенде VT1

жабық, ал VT2![]() транзисторы ашық. Қоректендіру

көзінің кернеуі

VT2

ашық транзисторы

арқылы каскад шығысына беріледі — бұл жоғары

деңгей кернеуі. Осылайша, берілген кілттік каскад ЕМЕС

логикалық функциясын іске келтіреді.

транзисторы ашық. Қоректендіру

көзінің кернеуі

VT2

ашық транзисторы

арқылы каскад шығысына беріледі — бұл жоғары

деңгей кернеуі. Осылайша, берілген кілттік каскад ЕМЕС

логикалық функциясын іске келтіреді.

КМДЖ-кілт пен интегралды схемалардың тағы бір ерекшелігін атап өткен жөн — статикалық режимде қоректендіру көзінен тұтынылатын қуат, ТТЛ және ТТЛШ ең аз қуатты логикалық элементтерінің қуатымен салыстырғанда аздау. Бұл статикалық режимде транзисторлардың біреуінің жабық екендігі, сәйкесінше, ток кілт арқылы өтпейтіндігімен түсіндіріледі.

КМДЖ-кілті негізіндегі НЕМЕСЕ-ЕМЕС логикалық элементінің схемасы 2.30-суретте көрсетілген. Егер екі кіріске де төмен деңгей сигналы берілген болса, онда өткізгіштігі р-типті каналы бар болғандықтан VT3 және VT4 транзисторлары ашық, ал VT1 және VT2 транзисторлары жабық, өйткені олардың өткізгіштігі n-типті каналы бар. Осылайша, шығысында жоғары деңгей кернеуі (логикалық бір) орнатылады. Ең болмағанда кірістердің біреуіне жоғары деңгей кернеуін бергенде сәйкес келетін VT3 немесе VT4 жабылады, яғни олар арқылы ток өтпейді, ал VT1 немесе VT2 транзисторлары сәйкесінше ашылады. Шығысында төмен деңгей кернеуі (логикалық нөл) орнатылады. Бұл схема НЕМЕСЕ-ЕМЕС логикалық функциясын орындайтыны көрініп тұр.

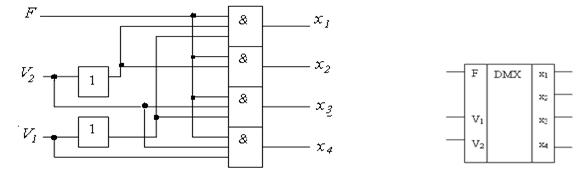

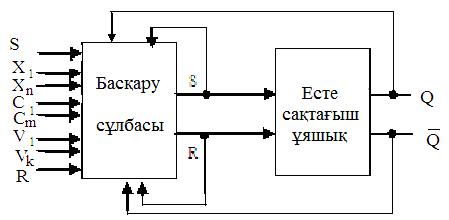

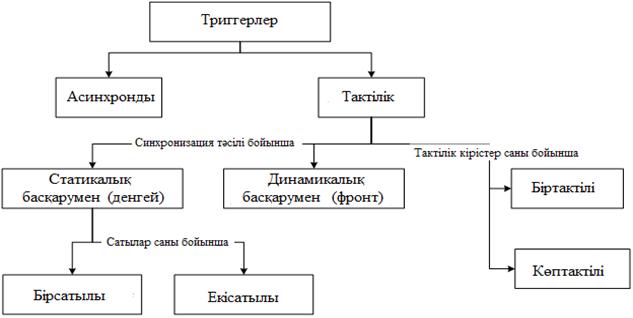

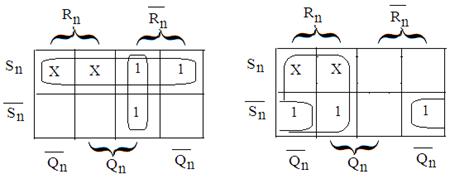

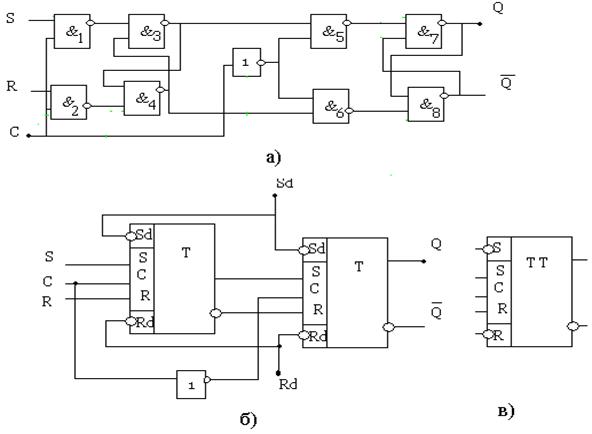

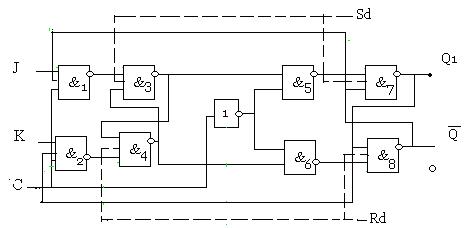

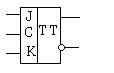

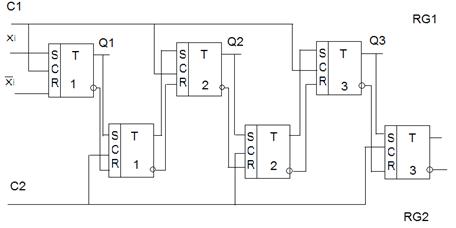

ЖӘНЕ-ЕМЕС базалық элементінің құрылғысы НЕМЕСЕ-ЕМЕС элементінің құрылғысына кері: р-типті каналды транзисторлары параллелді, ал – п-типті каналды тізбектей жалғанған, (2.20 суретті қара).