Некоммерческое акционерное общество

АЛМАТИНСКИЙ УНИВЕРСИТЕТ ЭНЕРГЕТИКИ И СВЯЗИ

Кафедра «Электроника»

ОСНОВЫ МИКРОПРОЦЕССОРНОЙ ТЕХНИКИ

Методические указания к выполнению лабораторных работ

для студентов всех форм обучения специальности

5B070300 – Информационные системы

Алматы 2011

СОСТАВИТЕЛЬ: У.Т. Шанаев. Основы микропроцессорной техники. Методические указания к выполнению лабораторных работ по первой части курса “Основы микропроцессорной техники” для студентов всех форм обучения специальности 5B070300 – Информационные системы. – Алматы: АУЭС, 2011. – 21 с.

Предлагаемые в методической разработке работы предназначены изучению внутренней структуры отдельных составляющих блоков микропроцессорной системы (памяти, устройств ввода/вывода, интерфейсных устройств) и их функциональных возможностей (различным принципов организации передач данных). Выполнение этих работ, организовыванная в виде виртуальных экспериментов, осуществляемых посредством моделирования исследуемых устройств в программной среде Electronics Workbench, предоставит студентам широкие возможности как для освоения изучаемого учебного материала, так и для приобретения практических навыков по организации экспериментальных упражнений.

Методические указания к лабораторным работам предназначены для студентов всех форм обучения по специальности 5B070300 – Информационные системы. Они могут быть использованы и для организации лабораторных занятий по идентичным темам аналогичных дисциплин, запланированных для других специальностей.

Ил. 11, библиогр. – 11 назв.

Рецензент: докт. физ-мат. наук, проф. С. Б. Бимурзаев

Печатается по плану издания Некоммерческого акционерного общества “Алматинский институт энергетики и связи” на 2010 г.

© НАО “Алматинский университет энергетики и связи”, 2011 г.

Введение

Курс “Основы микропроцессорной техники”, посвященный изучению структурных принципов построения микропроцессорных систем и их функциональных основ, состоит из двух взаимосвязанных и взаимообусловленных частей: аппаратная часть (hardware) и программная часть (software). Известно, что немаловажную роль в усвоении технических дисциплин играет выполнение лабораторных работ по основополагающим темам курса. Традиционно задания для выполнения лабораторных работ по этому курсу посвящены в основном обучению основам программирования на языке ассемблера, а аппаратной части курса не уделяется достаточного внимания. Это объясняется, прежде всего, сложностью постановки соответствующих лабораторных работ. Но в то же время, составление программ на языке ассемблера, основанное на регистровой модели системы, требует наиболее полного представления об аппаратной части системы, о происходящих в ней процессах, о путях прохождения информации и управляющих сигналов при выполнении конкретных команд программы. Следовательно, для наиболее полного усвоения курса требуется усвоение как аппаратной, так и программной части курса.

Предлагаемые в методической разработке работы предназначены изучению внутренней структуры отдельных составляющих блоков микропроцессорной системы (памяти, устройств ввода/вывода, интерфейсных устройств) и их функциональных возможностей (различным принципов организации передач данных). Выполнение этих работ, организовыванная в виде виртуальных экспериментов, осуществляемых посредством моделирования исследуемых устройств в программной среде Electronics Workbench, предоставит студентам широкие возможности как для освоения изучаемого учебного материала, так и для приобретения практических навыков по организации экспериментальных упражнений.

Методические разработки, посвященные изучению структуры и принципов организации работы микропроцессора и составлению программ работы микропроцессорных систем на языке Ассемблер, запланированы к отдельному изданию.

1 Лабораторная работа. Запоминающие устройства типа ROM

Цель работы:

- освоение принципов построения ROM;

- приобретение навыков программирования PROM.

1.1 Оборудование рабочего места и файлы:

- компьютер;

- программа Electronics Workbench Professional (C:\EWB5PRO);

- папка BMPT(Bases of the Microprocessor Technology);

- файл 1.1.ROM(M) 16x7.ewb;

- файл 1.2.PROM 16x7.ewb.

1.2 Практические сведения

Первое задание лабораторной работы посвящено изучению структуры и принципов работы постоянного запоминающего устройства (ПЗУ) с неизменяемой информацией для отображения шестнадцатеричных символов на 7-сегментном индикаторе (см. рисунок 1.1).

Блок ПЗУ (подсхема ROM_16x7) cостоит из дешифратора на 16 выходов (микросхема 74154) и матрицы памяти с организацией 16x7, оформленных в виде подсхем с соответствующими наименованиями. Разрешение на работу дешифратора обеспечивается положительным уровнем сигнала от клавиши E (Enable). Адреса строк памяти (7-разрядных ячеек) формируются посредством 4-разрядного счетчика (подсхема add4).

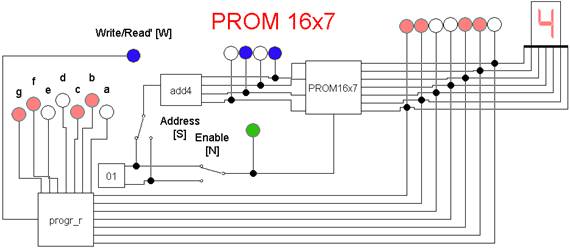

Второе задание посвящено изучению структуры (см. рисунок 1.2) и принципов программирования (прошивки) заготовки микросхемы (в нашем случае подсхемы chip 16x7), в где исходном состоянии имеются все перемычки в пересечениях шестнадцати горизонталей (выходных линии дешифратора) и семи вертикалей (разрядных линии).

Программирование микросхемы осуществляется в следующем порядке:

- нажатием кнопки пуска (Activate simulation), активизировать схему;

- клавишей W (Write/Read) перевести установку в режим программирования (светится соответствующий светодиод);

- установить адрес программируемой строки матрицы памяти;

- подготовить информацию для программирования нажатием клавиш, соответствующих ликвидируемым сегментам предполагаемого к размещению на этой строке символа;

- кратковременным нажатием клавиши P (programming) обеспечить программирование строки (прошивку информации).

- восстановить исходные состояния клавиш сегментов;

- клавишей W (Write/Read) перевести установку в режим чтения информации и проверить прошитые в строках матрицы памяти информацию.

Рисунок 1.1

Рисунок 1.2

1.3 Рабочее задание

1.3.1 ROM

1.3.1.1 Открыть файл 1.1.ROM(M) 16x7.ewb, раскрыть подсхемы различных блоков (см. рисунок 1.1) и изучить их структуру.

1.3.1.2 Изменяя адреса ячеек памяти клавишей A (Address), проверить записанную в соответствующих строках памяти информацию.

1.3.2 PROM

1.3.2.1 Открыть файл 1.2.PROM 16x7.ewb (см. рисунок 1.2) и изучить структуру матрицы chip16x7 и устройство программатора (programmer), раскрыв соответствующие подсхемы.

1.3.2.2 Запрограммировать строки матрицы памяти для отображения символов из следующего списка: L, J, H, P, S, U, –, _, e, n, q, r и др.

1.4 Контрольные вопросы

1. В чем состоит назначение ROM?

2. Какие элементы памяти используются в различных типах ROM?

3. Как и кем программируются PROM?

4. В чем состоит различие EPROM и EEPROM?

2 Лабораторная работа. Базовые структуры ЗУ

Цель работы:

- изучение базовых структур ЗУ и освоение принципов их построения.

2.1 Оборудование рабочего места и файлы:

- компьютер;

- программа Electronics Workbench Professional (C:\EWB5PRO);

- папка BMPT(Bases of the Microprocessor Technology);

- файл 2.1.RAM 2D_8x4.ewb;

- файл 2.2.RAM_3D_16x4.ewb:

- файл 2.3.RAM 2DM_32x4.ewb.

2.2 Практические сведения

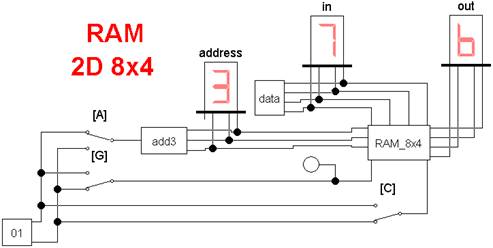

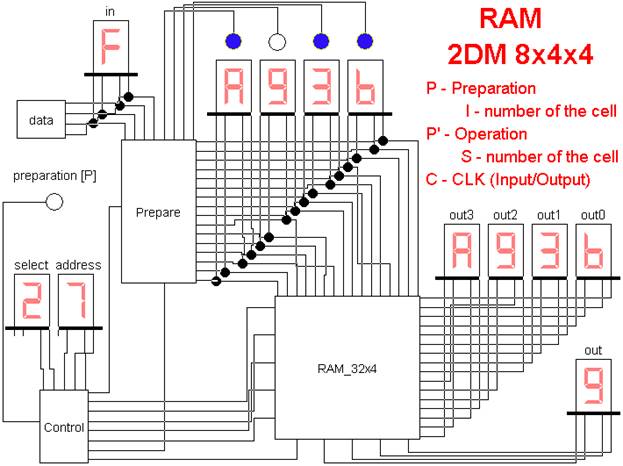

Данная работа, посвященная изучению различных структур систем памяти (2D, 3D, 2DM) и принципов их работы выполняется на соответствующих моделях (см. рисунки 2.1-2.3).

Рисунок 2.1

Рисунок 2.2

Рисунок 2.3

Схема для исследования системы памяти по структуре 2D (см. рисунок 2.1) состоит из следующих блоков, оформленных в виде соответствующих подсхем:

- трехразрядный формирователь адреса (add3) на основе счетчика;

- четырехразрядный источник данных (data) на основе счетчика;

- система памяти RAM_8x4, в состав которой входят дешифратор на восемь выходов (dc8) и матрица запоминающих ячеек (8x4), содержащая 8 ячеек (rg4) на основе регистров. Каждый из ячеек матрицы памяти снабжен индикатором, что позволяет вести наблюдение за выбором ячейки памяти во время эксперимента.

Схема для исследования системы памяти по структуре 3D (см. рисунок 2.2) состоит из следующих блоков, оформленных в виде соответствующих подсхем:

- четырехразрядный формирователь адреса (add4) на основе счетчика;

- четырехразрядный источник данных (data) на основе счетчика;

- система памяти RAM_16x4, в состав которой входят сдвоенный дешифратор (2dc4) и матрица запоминающих ячеек (16x4), содержащая 16 ячеек (rg4) на основе регистров.

Схема для исследования системы памяти по структуре 2DM (см. рисунок 2.3) содержит в своем составе следующие блоки:

- блок памяти RAM_32x4 по структуре 2DM;

- блок подготовки данных Prepare;

- блок управления Control.

Блок памяти RAM_32x4 состоит из следующих подблоков:

- матрица элементов памяти 32х4;

- блок дешифрации строки dc8;

- блок выбора ячейки из строки (при чтении) mux4.

Матрица памяти 32х4 представляют собой (логически) 8 строк, в каждой из которых размещен блок cell_4x4, состоящая из четырех 4-разрядных ячеек памяти rg4. Физически блок памяти 32х4 реализован (с целью удобства соединения и обзора) в виде объединения двух блоков 16х4, составленных из четырех блоков cell_4x4. Каждый из внутренних блоков матрицы памяти 32х4 снабжен индикатором, что позволяет вести наблюдение за выбором строки и ячейки памяти во время эксперимента.

Блок dc8, предназначенный для выбора строки памяти, представляет собой дешифратор на восемь выходов.

Блок mux4, собранный на двух сдвоенных 4-входовых мультиплексорах, позволяет выбрать ячейку из активизированной строки.

Блок Prepare предназначен для предварительной подготовки четырех 4-разрядных слов, предполагаемых для одновременной записи в одну из строк матрицы памяти. На этапе подготовки эти слова временно сохраняются во внутреннем блоке in_4, составленного из четырех 4-разрядных ячеек памяти in. Выбор одной из этих ячеек осуществляется с помощью дешифраторного блока dc4 и блока его адресации 0_3.

В блоке Control объединены управляющие клавиши и дополнительные элементы, обеспечивающие все режимы работы устройства. Устройство может работать в трех режимах:

- режим подготовки данных для записи;

- режим записи;

- режим чтения.

Режим подготовки данных осуществляется следующим образом:

- клавишей P (Prepare) перевести устройство в режим подготовки данных (светится соответствующий индикатор);

- клавишей I (In) выбрать одну из четырех ячеек блока in_4 (указывает соответствующий индикатор);

- клавишей С (CLK) записать в эту ячейку одну из чисел, формируемых блоком данных data.

Перевод в режим записи/чтения осуществляется повторным нажатием клавиши P (индикатор гаснет).

В режиме записи:

- клавишей A выбрать необходимую строку матрицы памяти (указывает соответствующий 7-сегментный индикатор);

- клавишей С (CLK) записать подготовленные данные в выбранную строку матрицы памяти.

В режиме чтения:

- клавишей A выбрать необходимую строку матрицы памяти (указывает соответствующий 7-сегментный индикатор);

- клавишей S (Select) выбрать определенную ячейку из активизированной строки матрицы памяти (указывает соответствующий 7-сегментный индикатор).

2.3 Рабочее задание

2.3.1 Структура 2D

2.3.1.1 Открыть файл 2.1.RAM 2D_8x4.ewb, где представлена схема для исследования системы памяти по структуре 2D и изучения принципа ее работы (см. рисунок 2.1). Раскрыть подсхемы блоков и изучить их структуру.

2.3.1.2 Исследовать работу представленной системы памяти, записывая в ячейки определенную информацию и проверяя затем их сохранность.

2.3.2 Структура 3D

2.3.2.1 Открыть файл 2.2.RAM 3D_16x4.ewb, где представлена схема для исследования системы памяти по структуре 3D и изучения принципа ее работы (см. рисунок 2.2). Раскрыть подсхемы блоков и изучить их структуру.

2.3.2.2 Исследовать работу представленной системы памяти, записывая в ячейки определенную информацию и проверяя затем их сохранность.

2.3.3 Структура 2DM

2.3.3.1 Открыть файл 2.3.RAM 2DM_32x4.ewb, где представлена схема исследования блока памяти по структуре 2DM (см. рисунок 2.3) и изучить структуру ее составных блоков, раскрывая их и изучая соответствующий пояснительный текст.

2.3.3.2 Исследовать работу устройства памяти RAM_2DM, записав информацию во все строки матрицы, а затем проверить возможность считывания из конкретной ячейки памяти.

2.4 Контрольные вопросы

1. Назовите основные параметры запоминающих устройств.

2. Какая схемотехника элементов памяти обеспечивает максимальное быстродействие RAM?

3. В чем состоит принципы построения RAM с одномерной и двумерной адресацией?

4. Сравните преимущества и недостатки структур 2D и 3D.

5. Объясните принципы осуществления структуры памяти 2DM и его основные достоинства по сравнению с остальными структурами.

3 Лабораторная работа. Устройство ввода информации

Цель работы:

- освоение принципов построения устройств ввода информации на основе приоритетных шифраторов;

- приобретение навыков по совершенствованию работы устройства;

- приобретение навыков по созданию многорежимных устройств.

3.1 Оборудование рабочего места и файлы:

- компьютер;

- программа Electronics Workbench Professional (C:\EWB5PRO);

- папка BMPT(Bases of the Microprocessor Technology);

- файл 3.1.Input Unit (addressable).ewb;

- файл 3.2.Input Unit (multiplexing).ewb;

- файл 3.3.Input Unit (integration).ewb.

3.2 Практические сведения

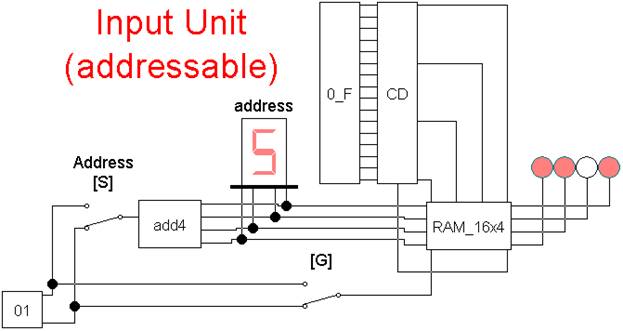

В первом задании рассматривается возможность реализации устройства ввода от шестнадцати клавиш на основе микросхем приоритетных шифраторов (см. рисунок 3.1). Сформированные коды сохраняются в ячейках памяти (подсхема RAM_16x4), исследованной в предыдущей работе. Для записи используется изменение уровня сигнала на выводе CS микросхем шифраторов. В этом устройстве адрес необходимой ячейки памяти подготавливается с помощью счетчика, как и в предыдущих работах.

Рисунок 3.1

Основными блоками схемы подсхемы 0_F и СD, представляющие собой набор клавиш и шифраторы соответственно. На сигнальной линии каждой клавиши в блоке 0_F установлены формирователи импульсов отрицательной полярности продолжительностью 10 ns (подсхемы, обозначенные символом l).

Основу блока CD составляет схема кодирования на двух приоритетных шифраторах 74148. Здесь же вырабатывается импульс записи длительностью 10 ns, формирующийся с задержкой 20 ns относительно начала формирования кода (момента нажатия клавиши). Параметры сформированных импульсов (относительный сдвиг сигнала записи) обеспечивают своевременное формирование кода нажатой клавиши и его запись в память.

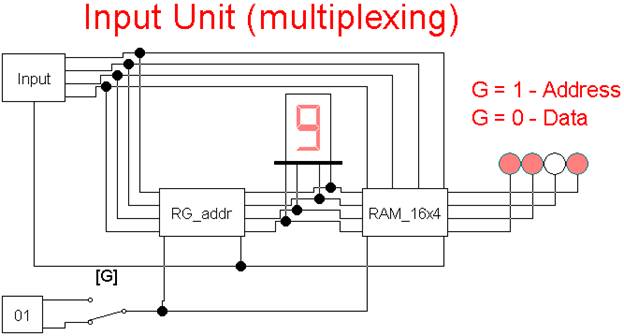

В следующей схеме (см. рисунок 3.2), рассматриваемой в данной работе, реализована возможность формирования как адреса, так и записываемой информации с помощью одних и тех же клавиш, т.е. осуществляется мультиплексирование передачи адреса и данных по одной и той же шине. Здесь блоки 0_F и СD объединены в подсхему Input.

Рисунок 3.2

Мультиплексирование осуществляется уровнем сигнала от клавиши G: при G=1 – передача адреса, который записывается в адресный регистр (подсхема RG_addr); при G=0 – передача записываемых в память данных.

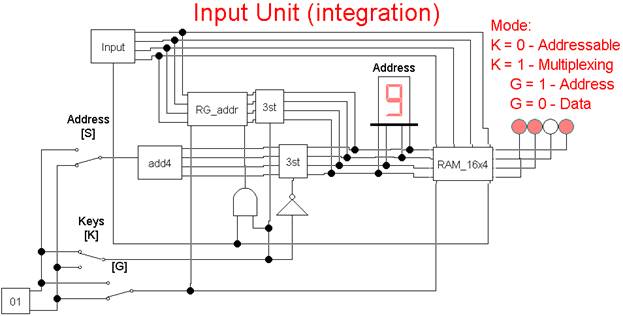

Еще более усовершенствованный вариант устройства рассматривается в следующей схеме (см. рисунок 3.3), где интегрированы оба рассмотренные ранее варианты. В этой схеме формирование адреса может быть реализовано в двух режимах: от счетчика (add4) и от блока кодирования (Inter). Переключение между этими источниками, т.е. их мультиплексирование осуществляется двумя блоками, построенными на основе элементов с тремя состояниями (подсхемы 3st), управляемых уровнем сигнала от клавиши K (при K=0 – add4 и при K=1 – Inter). В обоих случаях передача адреса осуществляется при G=1, а адреса – при G=0.

Рисунок 3.3

3.3 Рабочее задание

3.3.1.1 Открыть файл 3.1.Input Unit (addressable).ewb, где представлена схема для исследования устройства ввода на основе шифратора (см. рисунок 3.1). Раскройте подсхемы, размещенные в схеме, и изучите их структуру.

3.3.1.2 Проверьте работу устройства, устанавливая сначала адрес ячейки памяти клавишей S, а затем записывая в выбранную ячейку определенную информацию, нажимая соответствующую клавишу (0 … F).

3.3.1.3 Открыть файл 3.2.Input Unit (multiplexing).ewb, где представлена схема для исследования устройства ввода с мультиплексированием передачи адреса и записываемой информации от одного источника (см. рисунок 3.2). Раскройте подсхемы, размещенные в схеме, и изучите их структуру.

3.3.1.4 Проверьте работу устройства, устанавливая сначала адрес ячейки памяти (при G=1), а затем записывая в выбранную ячейку определенную информацию (при G=0), нажимая соответствующую клавишу (0 … F).

3.3.1.5 Открыть файл 3.3.Input Unit (integration).ewb, где представлена схема, в которой объединены оба предыдущих устройства (см. рисунок 3.3). Раскройте подсхемы, размещенные в схеме, и изучите их структуру.

3.3.1.6 Исследуйте работу устройства в различных режимах.

3.4 Контрольные вопросы

1. Объясните работу схемы в блоке CD.

2. Объясните назначение подсхем 3st и работу их структурных элементов.

3. Объясните принципы работы устройств, исследованных в лабораторной работе.

4 Лабораторная работа. Помехоустойчивое кодирование данных

Цель работы:

- освоение принципов организации диагностики и коррекции ошибок передачи данных;

- знакомство с методами формирования помехоустойчивых кодов.

4.1 Оборудование рабочего места и файлы:

- компьютер;

- программа Electronics Workbench Professional (C:\EWB5PRO);

- папка BMPT(Bases of the Microprocessor Technology);

- файл 4.AntiNoise Coding.ewb.

4.2 Практические сведения

Для исследования корректирующих возможностей кодов Хемминга была создана модель системы параллельной передачи 4-разрядных данных с использованием кодов Хемминга. Назовем его для дальнейшего изложения кодером/декодером Хемминга (КДК Хемминга).

Короткое 4-разрядное слово взято, чтобы обеспечить возможность наблюдения за динамикой процесса преобразования кодов. Хотя динамика моделирования в спроектированном устройстве максимально замедлена, очевидно, что одновременное наблюдение за всеми модификациями кодов данных с большим числом разрядов, а именно проверить значения сформированных контрольных разрядов в передаваемых данных, сопоставить значения битов в переданных и полученных данных, следить за производимыми коррекциями ошибочных данных, было бы затруднительной задачей для исследователя. Но в то же время данное 4-разрядное устройство позволяет получить достаточно ясное представление о принципах формирования кодов Хемминга и о возможностях его применения для коррекции ошибок передачи, что и является целью создания данной модели и выполнения этой лабораторной работы.

Охарактеризуем назначение и функции структурных блоков представленной на рисунке 4.1 модели КДК Хемминга.

Блок data, построенный на основе микросхемы 4-разрядного счетчика 7493, является динамическим формирователем данных. Роль источника предназначенных для передачи данных играет блок rg (на основе микросхемы регистра 74194), куда соответствующие данные записываются кратковременным нажатием клавиши С.

Блок Hem, формирующий контрольные разряды и расширяющий код данных до кода Хемминга построен в виде 8-разрядного регистра, составленного из двух 4-разрядных регистров (микросхемы 74194) и схемы свертки s,составленного из блоков 3x, 4x, 7x на основе элементов сложения по модулю 2 (XOR).

Рисунок 4.1

Ввиду того, что исследуемое устройство предназначено для исследования воздействия внешних и внутренних возмущающих факторов (в том числе и интерференционного влияния передаваемых данных между собой) на передаваемые данные, в схему устройства был введен блок Int, имитирующий эти помехи. Схема этого блока, составленного на основе дешифратора (микросхема 74138) и элементов XOR, обеспечивает формирование помех случайного характера, оказывающих воздействие на значения отдельных битов передаваемых данных (т.е. инвертирование). Статистика вероятностей этих возмущений распределена в виде 0,6/0,3/0,1, т.е. 60% случаев пересылки данных осуществляются без искажений, в 30% возникают однократные ошибки и в 10% – двукратные ошибки, что достаточно наглядно имитирует (конечно, условно) естественный характер возникающих возмущений.

Блок Rec (Receiver), представляющий собой 8-разрядный регистр (на основе микросхем 74194), приняв данные с линии, передает их в блок проверки и коррекции V_C (Verification and Correction). Этот блок, представляющий собой декодер Хемминга, составленный на основе схем свертки и микросхемы дешифратора 74138, проверяет соответствие значений контрольных битов полученным данным и при обнаружении однократной ошибки осуществляет ее коррекцию (инвертирует). При этом номер (адрес) разряда с ошибкой высвечивается на индикаторах Syndrome. Например, на рисунке 4.1 захвачен момент возникновения ошибки в третьем разряде полученных данных, что и подтверждается состояниями индикаторов Syndrome.

При обнаружении двукратной ошибки блок V_C формирует сигнал автоматического запроса на повторную пересылку ARQ (Automatic Request for Retransmission), которая осуществляется сигналом тактового генератора после поступления этого сигнала на управляющий вход элемента AND (см. рисунок 4.1).

4.3 Рабочее задание

4.3.1 Открыть файл 4.AntiNoise Coding.ewb, где представлена схема кодера/декодера Хемминга (см. рисунок 4.1), позволяющая изучить принципы формирования кодов Хемминга и применения его для помехоустойчивой передачи данных. Раскрыть подсхемы составных блоков КДК Хемминга и изучить их структуру.

4.3.2 Исследовать работу КДК Хемминга, записывая передаваемые данные (rg), сформированные соответственно им коды Хемминга (Hem), полученные с линии данные (Rec), показания индикаторов Syndrome и принятые данные в виде таблицы. (Передача данных осуществляется нажатием клавиши С).

4.3.3 Проанализировать каждый случай пересылки данных, проверяя правильность формирования кодов Хемминга соответственно передаваемым данным, обращая внимание на возникшие ошибки пересылки и процесс их коррекции.

4.4 Контрольные вопросы

1. Объясните принципы формирования кодов Хемминга для 4-разрядных данных.

2. Объясните принципы применения кодов Хемминга для проверки и коррекции ошибок пересылки данных.

3. Дайте пояснения к структуре исследуемой модели КДК Хемминга и ее функциональных блоков (подсхем).

5 Лабораторная работа. Последовательный интерфейс

Цель работы:

- освоение принципов структурной организации последовательного интерфейса и порядка его работы.

5.1 Оборудование рабочего места и файлы:

- компьютер;

- программа Electronics Workbench Professional (C:\EWB5PRO);

- папка BMPT(Bases of the Microprocessor Technology);

- файл 5.Serial Transeiving.ewb.

5.2 Практические сведения

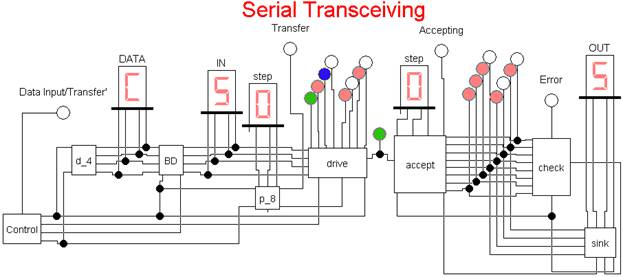

Модель предназначенной для исследования системы последовательной передачи данных состоит из двух блоков: передатчика и приемника (см. рисунок 5.1). Четырехразрядное слово, сформированное источником данных (d_4) и предназначенное для передачи, хранится в буфере данных (BD). Это слово в блоке drive (передать) обрамляется четырьмя служебными битами (старт-бит, стоп-бит, признак проверки четности и бит четности) и восемью тактовыми импульсами, сформированных блоком p_8, передается по единственной связной линии.

Рисунок 5.1

Преобразованное в блоке accept (принять) в параллельную форму восьмиразрядные данные проверяются в блоке check (контроль) на соответствие всех служебных битов, и в случае их правильности, освобожденное от обрамления четырехразрядное слово передается в выходной буфер данных sink (приемник). В случае обнаружения ошибки передачи соответствующий индикатор (Error) оповещает об этом, и четырехразрядное слово не выделяется.

5.3 Рабочее задание

5.3.1 Открыть файл 4.Serial Transeiving.ewb, где представлена схема устройства последовательной передачи информации (см. рисунок 5.1), позволяющая изучить принципы структурной организации последовательного интерфейса и порядок его работы.

5.3.2 Произведите проверку работы последовательного интерфейса следующим образом:

- клавишей D (Data Input/Transfer') установите устройство в режим выбора данных (Data Input) и одноразовым нажатием клавиши С (CLK) выбрать (поймать) какое-либо число и сохранить его в буфере данных BD;

- клавишей D перевести устройство в режим передачи (Transfer).

Дальнейшие действия устройства осуществляются автоматически, остается только наблюдать за результатами преобразования и передачи. После окончания передачи (как в случае правильности передачи, так и в случае ошибки) по показаниям информационных индикаторов проанализировать полученный результат.

Аналогичным путем повторить эксперимент несколько раз.

5.4 Контрольные вопросы

1. Какие функции выполняет последовательный интерфейс?

2. Объясните работу последовательного интерфейса в асинхронном режиме.

3. Объясните структуру и режимы работы периферийного адаптера Intel 8255A (К580ВВ55А).

6 Лабораторная работа. Мультиплексированная передача данных

Цель работы:

- освоение принципов организации мультиплексированной передачи последовательных данных;

- расширение знаний о применении помехоустойчивого кодирования для передачи данных.

6.1 Оборудование рабочего места и файлы:

- компьютер;

- программа Electronics Workbench Professional (C:\EWB5PRO);

- папка BMPT(Bases of the Microprocessor Technology);

- файл 6.Multiplex Transfer.ewb.

6.2 Практические сведения

В микропроцессорных системах, предназначенных для управления технологическими процессами или динамическими объектами, различные данные о параметрах процесса или объекта, снимаемые с соответствующих датчиков, передаются в систему управления. При удаленном размещении системы управления от объекта, эти данные приходится передавать по одной и той же линии, с разделением во времени.

При передаче сначала передаются данные 1-го источника, затем следующего источника и т.д. до последнего источника за номером N, после чего опять передаются данные 1-го источника и процесс повторяется периодически. На приеме устанавливается аналогичный коммутатор, который поочередно подключает линию связи к соответствующим приемникам.

Это означает, что для нормальной работы системы с временным разделением линий связи необходима синхронная и синфазная работа коммутаторов на приемной и передающей сторонах. Для этого одну из линий занимают под передачу специальных импульсов синхронизации.

При временном разделении линии связи, так же как и при других способах организации пересылок данных, существуют взаимные помехи, в основном обусловленные двумя причинами.

Первая состоит в том, что при временном разделении сигналов это приведет к тому, что импульсы одного пакета данных могут накладываться на импульсы других пакетов. Иначе говоря, между передаваемыми пакетами данных возникают взаимные переходные помехи или межсимвольная интерференция.

Кроме того, взаимные помехи могут возникать за счет несовершенства синхронизации тактовых импульсов на передающей и приемной сторонах.

6.3.1 Модель системы передачи данных с временным разделением

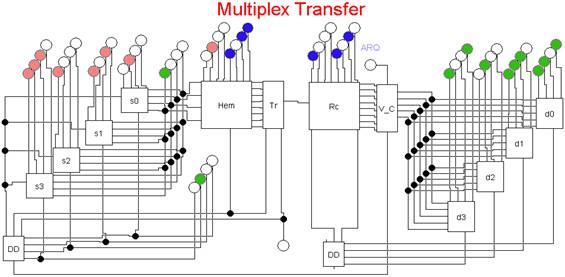

Для исследования работы системы мультиплексной передачи сообщений была создана модель этой системы для последовательной передачи 4-разрядных данных с четырех источников данных, структура которой представлена на рисунке 6.1. Назовем его для простоты изложения в дальнейшем системой MT-4 (Multiplex Transfer). Система MT-4 конструктивно состоит из двух функциональных частей – передатчика и приемника данных, соединенных однобитовой линией, по которой осуществляется последовательная пересылка данных.

Рисунок 6.1

Охарактеризуем назначение и функции структурных блоков передатчика и приемника данных в системе MMT-4.

Передатчик данных в системе MT-4 состоит из следующих структурных блоков:

- блок DD (Digital Demultiplexing) формирует временные интервалы для временного разделения передачи данных из отдельных источников и тактовые сигналы, необходимые для работы системы MT-4;

- идентичные между собой блоки s0, s1, s2, s3 (Sourse) выполняют функции источников сообщений;

- блок Hem в системе MT-4 предназначен для формирования контрольных разрядов и расширения кода данных до кода Хемминга;

- блок передатчика на линию Tr (Transmitter) предназначен для реализации процесса передачи последовательных данных в линию связи. В состав этого блока пристроен подблок N (Noise), формирующий помехи случайного характера, оказывающие воздействие на значения отдельных битов передаваемых данных (т.е. их инвертирование). Введение источника помех N в блок передачи можно интерпретировать как случай возникновения интерференционных помех, возникающее из-за взаимовлияний передаваемых данных.

Приемник данных в системе MT-4 состоит из следующих структурных блоков:

- блок формирования временных интервалов DD (Digital Demultiplexing) в составе приемника сообщений, формирует временные интервалы для временного разделения приема данных с линии и тактовые сигналы, необходимые для работы всех блоков приемника системы MT-4, и его работа синхронизирована по тактовой частоте с работой аналогичного блока в передатчике;

- блок приема информации с линии Rc (Receiver) предназначен для приема последовательно поступающих с линии 8-разрядных данных;

- блок проверки и коррекции принятых данных V_C (Verification and Correction) предназначен для проведения анализа принятых данных и принятия решений по отправке их в конечный приемник данных в случае неискаженного результата и коррекции в случае обнаружения однократной ошибки пересылки. При обнаружении двукратной ошибки блок V_C формирует сигнал автоматического запроса на повторную пересылку ARQ (Automatic Request for Retransmission), который поступает по линии обратной связи в блок временного разделения передатчика и там вырабатывается импульс повторной инициализации процесса передачи. Этот импульс поступает в блок передатчика Tr (Transmitter) и процесс пересылки повторяется;

- идентичные между собой блоки приема сообщений d0, d1, d2, d3 (Destination) осуществляют прием скорректированных данных соответствующего источника.

6.3 Рабочее задание

6.3.1 Открыть файл 6.Multiplex Transfer.ewb, где представлена схема учебной модели исследуемой системы (см. рисунок 6.1).

6.3.2 Изучить структуру модулей системы, раскрывая соответствующие подсхемы и используя приведенное выше ее краткое описание.

6.3.3 Активизировать схему устройства и с

помощью стоп-кадров, осуществляемых нажатием соответствующей кнопки ![]() на рабочем экране, исследовать

различные режимы работы системы:

на рабочем экране, исследовать

различные режимы работы системы:

- передачу данных с одного источника и формирование кодов Хемминга, соответствующих передаваемым данным;

- прием данных с линии и сопоставление их с переданными данными;

- осуществление коррекции в случае возникновения однократной ошибки и вывод их в конечный приемник.

6.4 Контрольные вопросы

1. Объясните принципы организации временного разделения передачи данных;

2. Дайте пояснения к структуре исследуемой модели системы мультиплексированной передачи данных и ее функциональных блоков (подсхем).

Список литературы

1. Токхейм Р. Основы цифровой электроники: Пер. с. англ. – М.: Мир, 1988.

2. Токхейм Р. Микропроцессоры. Курс и упражнеия: Пер. с. англ. – М.: Мир, 1988.

3. Уэйкерли Дж. Ф. Проектирование цифровых устройств: Пер. с. англ. – М.: Постмаркет, 2002.

4. Хамахер К. И др. Организация ЭВМ. Пер. с. англ. – СПб.: Питер, 2003.

5. Угрюмов Е. П. Цифровая схемотехника. – СПб.: БХВ-Петербург, 2004.

6. Сугано Т. Дж., Уидмер Н. С. Цифровые системы. Теория и практика: Пер. с англ. – М.: Издательский дом “Вильямс”, 2004.

7. Шанаев О.Т. Система моделирования Electronic Workbench / на казахском и русском языках. – Алматы: АИЭС, 2003.

8. Шанаев О.Т. Цифрлық құрылғылар және микропроцессорлар: Оқу құралы / Алматы: АЭжБИ, 2009.

9. Шанаев О.Т. Микропроцессорлық жүйелер: Оқу құралы / Алматы: АЭжБИ, 2009.

ОГЛАВЛЕНИЕ

1 Лабораторная работа. Запоминающие устройства типа ROM

2 Лабораторная работа. Базовые структуры ЗУ

3 Лабораторная работа. Устройство ввода информации

4 Лабораторная работа. Помехоустойчивое кодирование данных

5 Лабораторная работа. Последовательный интерфейс