АЛМАТИНСКИЙ ИНСТИТУТ ЭНЕРГЕТИКИ И СВЯЗИ

Кафедра электроники и компьютерных технологий

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ

Методические указания к выполнению лабораторных работ

для студентов всех форм обучения специальностей

050704 – Вычислительная техника и программное обеспечение,

050719 – Радиотехника, электроника и телекоммуникации

Алматы 2009

СОСТАВИТЕЛЬ: У.Т.Шанаев. Микропроцессорные системы. Методические указания к выполнению лабораторных работ по второй части курса “Цифровые устройства и микропроцессоры” для студентов всех форм обучения специальностей 050704 – Вычислительная техника и программное обеспечение, 050719 – Радиотехника, электроника и телекоммуникации. – Алматы: АИЭС, 2009. – 31 с.

В методических указаниях представлены описания лабораторных работ по исследованию структурных принципов основных устройств микропроцессорных систем, выполнение которых определяет фундаментальную основу профессионального образования по второй части курса “Цифровые устройства и микропроцессоры”. Они составлены в соответствии с требованиями квалификационной характеристики специалиста, Государственных стандартов, педагогико-психологических основ организации и проведения лабораторных занятий. Предлагаемые лабораторные работы выполняются путем проведения виртуальных исследований с помощью системы моделирования Electronics Workbench.

Методические указания к лабораторным работам предназначены для студентов всех форм обучения специальностей 050704 – Вычислительная техника и программное обеспечение, 050719 – Радиотехника, электроника и телекоммуникации. Они могут быть использованы и для организации лабораторных занятий по идентичным темам аналогичных дисциплин, запланированных для других специальностей.

Введение

Вторая часть курса “Цифровые устройства и микропроцессоры”, посвященная микропроцессорам, состоит из двух взаимосвязанных и взаимодополняющих разделов: аппаратный раздел (hardware) и программная раздел (software). Известно, что немаловажную роль в усвоении технических дисциплин играет выполнение лабораторных работ по основополагающим темам курса. Традиционно задания для выполнения лабораторных работ по этому курсу посвящены в основном обучению основам программирования на языке ассемблера, а аппаратной части курса не уделяется достаточного внимания. Это объясняется, прежде всего, сложностью постановки соответствующих лабораторных работ. Но в то же время, составление программ на языке ассемблера, основанное на регистровой модели системы, требует наиболее полного представления об аппаратной части системы, о происходящих в ней процессах, о путях прохождения информации и управляющих сигналов при выполнении конкретных команд программы. Следовательно, для наиболее полного усвоения курса требуется усвоение как аппаратной, так и программной части курса.

В предлагаемом в методическом руководстве представлены описания лабораторных работ и соответствующие рабочие задания по аппаратной части курса “Цифровые устройства и микропроцессоры”. Выполнение представленных в методическом руководстве рабочих заданий организовываются в виде виртуальных экспериментов, осуществляемых посредством моделирования исследуемых устройств в программной среде Electronics Workbench. При этом часть заданий могут быть вынесены в качестве задания для самостоятельной работы студентов (СРС). Предлагаемая методика организации лабораторных занятий проверена многолетней практикой преподавания автора и испытана временем. Такая методика организации учебного исследования обеспечивают более глубокие знания студентов по теории изучаемых устройств и способствуют формированию у них практических навыков по проведению практических и моделирующих экспериментов.

Предлагаемые в методическом руководстве задания по выполнению виртуальных исследований с помощью системы моделирования Electronics Workbench в достаточном объеме обеспечивают выполнение целей и задач лабораторных занятий, что создает условия и для самостоятельного применения их в случае учебно-производственной необходимости (например, при выполнении курсовых и выпускных бакалавриатских работ) или в будущей профессиональной деятельности.

По выполненному учебному исследованию студенты должны подготовить отчет. Отчет должен содержать схемы исследования, измеренные и рассчитанные данные, графические построения, определенные (измеренные и рассчитанные) параметры исследуемого устройства, выводы по результатам выполненных экспериментов, результаты выполнения задания на СРС и краткие ответы на вопросы.

Последующее изложение касается тематики предлагаемых лабораторных работ и содержании рабочих заданий. Для раскрытия этого вопроса кратко остановимся на теоретическом содержании рассматриваемой части курса.

В основу построения микропроцессорных систем (МПС) положено три принципа:

- магистральности;

- модульности;

- микропрограммного управления.

Принцип магистральности определяет характер связи между функциональными блоками МПС, который заключается в том, что все блоки системы соединяются между собой единой системной магистралью (системной шиной), через которую и осуществляется обмен информацией между этими блоками.

Принцип модульности состоит в том, что система строится на основе функционально законченных модулей. Каждый модуль имеет вход разрешения работы модуля, уровень сигнала на котором управляет третьим (высокоимпедансным) состоянием модуля, т.е. состоянием подключенности модуля к системной шине.

Принцип микропрограммного управления характеризует возможности осуществления элементарных операций – микрокоманд (пересылок информации, арифметических операций, сдвигов и др.).

В системную магистраль входит три основные информационные шины: адреса, данных и управления.

Шина данных – это основная шина, через которую осуществляется обмен данными между модулями системы. Шина данных всегда двунаправленная, так как она должна обеспечить передачу данных в обоих направлениях.

Шина адреса – это шина, через которую осуществляется доступ к памяти (или к внешним устройствам).

Для снижения общего количества линий связи магистрали часто применяется мультиплексирование шин адреса и данных, т.е. одни и те же линии связи используются в разные моменты времени для передачи как адреса, так и данных (в начале цикла – адрес, в конце цикла – данные).

Шина управления – это шина, сигналы на линиях которой определяют тип текущего цикла и фиксируют моменты времени, соответствующие разным частям или стадиям цикла. Кроме того, управляющие сигналы обеспечивают согласование работы процессора (или другого хозяина магистрали, задатчика, master) с работой памяти или устройства ввода/вывода (устройства-исполнителя, slave).

Самые главные управляющие сигналы – это стробы обмена, т.е. строб записи (вывода) и строб чтения (ввода). Эти сигналы формируются процессором и определяют моменты времени, в которые производится пересылка данных по шине данных в соответствующем направлении.

В состав микропроцессорной системы входят:

- центральный процессор;

- постоянное запоминающее устройство;

- оперативное запоминающее устройство;

- устройства ввода/вывода;

- система прерываний;

- таймер.

Все эти устройства подключены к системной магистрали, и обмен информацией между ними осуществляется именно через эту магистраль.

Для соединения устройств ввода/вывода или внешних устройств (УВВ или ВУ) с системной магистралью их сигналы должны соответствовать определенным стандартам, что реализуется с помощью интерфейсов ввода/вывода.

Выполнение процессором операций записи и чтения данных может происходить в режимах программно-управляемого обмена, прерывания и прямого доступа к памяти, основополагающим из которых является первый.

Исходя из изложенного о структуре МПС, были определены тематика лабораторных работ и содержание представленных в них рабочих заданий.

Первые три работы посвящены различным типам систем памяти и различным принципам их построения.

Четвертая работа посвящена устройствам ввода информации и реализации различных способов их сохранения.

Пятая работа посвящена реализации программно-управляемого обмена в микропроцессорной системе.

Последние две работы посвящены интерфейсам – параллельному и последовательному.

Характер выполнения рабочих заданий от работы к работе носит прогрессирующий характер: если задания первых работ выполняются путем сборки схем устройств в виде отдельных модулей, то в последующих работах схемы собираются использованием ранее подготовленных модулей, а выполнение последних работ осуществляется на полностью готовых моделях. В нескольких работах, касающихся обмену информацией, подчеркнуто уделено внимание применению общей магистрали, и почти во всех работах используются устройства с тремя состояниями выходов.

Тематике предлагаемых лабораторных работ, содержание рабочих заданий и характер (методика) их выполнения, несомненно, будет способствовать закреплению теоретических знанию студентов, полученных ими на лекциях и в результате изучения соответствующей литературы, а также приобретению практических навыков по проведению моделирующих экспериментов с помощью современных программных средств, таких как программа Electronics Workbench.

1 Лабораторная работа №1. Запоминающие устройства типа ROM

1.1 Цель работы:

- освоение принципов построения ROM;

- приобретение навыков создания дополнительных средств, необходимых для проведения экспериментов.

1.2 Теоретические сведения

Запоминающие устройства типа ROM (Read Only Memory) хранят информацию, которая либо вообще не изменяется (в ЗУ типов ROM(M) и PROM), либо изменяется редко и не в оперативном режиме (в ЗУ типов EPROM и EEPROM).

Программирование постоянной памяти заключается в том или ином размещении элементов связи между горизонтальными и вертикальными линиями матрицы запоминающих элементов.

В матрице диодного ROM(M) (см. рисунок 1.1) горизонтальные линии являются линиями выборки слов, а вертикальные – линиями считывания. Считываемое слово определяется расположением диодов в узлах координатной сетки. При наличии диода высокий потенциал выбранной горизонтальной линии передается на соответствующую вертикальную линию, и в данном разряде слова появляется сигнал логической единицы. При отсутствии диода потенциал близок к нулевому, т. к. вертикальная линия через резистор связана с землей. В изображенной матрице при возбуждении линии выборки В0 считывается слово 11010001 (в ячейке номер ноль хранится это слово). При возбуждении В1 считывается слово 10101011 (оно хранится в ячейке номер 1). Шины выборки являются выходами дешифратора адреса, каждая адресная комбинация возбуждает свой выход дешифратора, что приводит к считыванию слова из адресуемой ячейки.

Рисунок 1.1

1.3 Рабочее задание

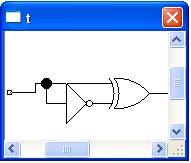

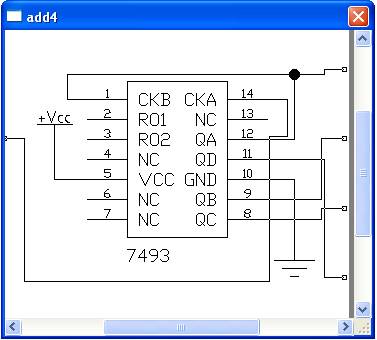

1.3.1 Подготовить подсхемы формирователя одиночного импульса (см. рисунок 1.2) и формирователя адреса в виде четырехразрядного счетчика (см. рисунок 1.3).

Рисунок 1.2

Рисунок 1.3

1.3.2 Собрать схему формирования адреса и проверить ее работу (см. рисунок 1.4).

Рисунок 1.4

1.3.3 Открыть файл C:\EWB5PRO\MPS_Lab\ROM_base, где представлены все блоки, оформленные в виде подсхем и необходимые для сборки следующей (основной) схемы. В состав подсхемы ROM_16x7 входят дешифратор на шестнадцать выходов и матрица запоминающих элементов, содержащая коды семисегментного индикатора для отображения шестнадцатеричных символов. Они оформлены в виде подсхем dc16 и 16x7 соответственно. В качестве элементов связи в матрице используется самооткрывающаяся буферная схема с тремя состояниями, также оформленная в виде подсхемы. Раскройте эти подсхемы и изучите их структуру.

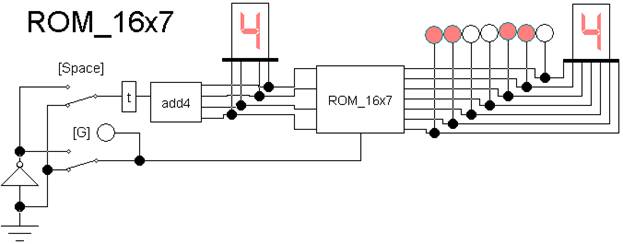

1.3.4 Соберите схему управления ROM (см. рисунок 1.5) и исследуйте ее работу, считывая информацию с каждой из ячеек памяти.

Рисунок 1.5

1.3.5 Измените схему матричного блока, чтобы получить отображение двух символов из следующего списка (по указанию преподавателя) : L, J, H, P, S, U, –, _, e, n, q, r.

1.3.6 Проверьте работу измененной схемы и сохраните его в своей индивидуальной папке под названием, содержащим определенную информацию об исполнителе, например, под названием ROM_ВТ04-Алмат-1.

1.4 Контрольные вопросы

1. В чем состоит назначение ROM?

2. Как организованы схемы ROM?

3. Как программируются ROM(M)?

4. Как программируются PROM?

5. В чем состоит различие EPROM и EEPROM?

2 Лабораторная работа №2. Базовые структуры ЗУ

2.1 Цель работы:

- изучение базовых структур ЗУ и освоение принципов их построения;

- приобретение навыков расширения размерности запоминающих устройств.

2.2 Теоретические сведения

2.2.1 Структура 2D

В простых цифровых устройствах система памяти (как RAM, так и ROM) может быть собран по структуре 2D.

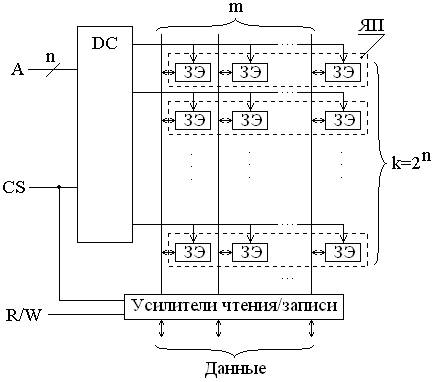

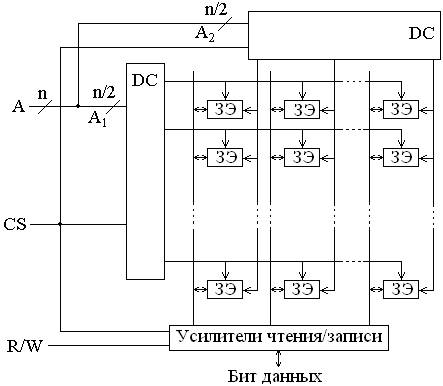

В структуре 2D (см. рисунок 2.1) n-разрядные ячейки памяти ЯП располагаются на одной линии (на рисунке – по вертикали), поэтому такую структуру часто называют линейной структурой.

Рисунок 2.1

Дешифратор адресного кода DC при наличии разрешающего сигнала CS (Chip Select – сигнал выбора микросхемы) активизирует одну из выходных линий, осуществляя доступ к ячейке на выбранной строке, хранящей слово, адрес которого соответствует номеру строки. Соответствующие элементы столбцов соединены вертикальной линией – внутренней линией данных (разрядной линией, линией записи/считывания). Элементы столбца хранят одноименные биты всех слов. Направление обмена определяется усилителями чтения/записи под воздействием сигнала R/W (Read – чтение, Write – запись).

2.2.2 Структура 3D

Структура 3D (также называемая матричной структурой) позволяет резко упростить дешифраторы адреса с помощью двухкоординатной выборки запоминающих элементов (см. рисунок 2.2).

Рисунок 2.2

Здесь код адреса разрядностью n делится на две половины, каждая из которых декодируется отдельно. Выбирается запоминающий элемент (или ячейка), находящийся на пересечении активных линий выходов обоих дешифраторов. Таких пересечений будет как раз

2n/2 х 2n/2 = 2n.

Суммарное число выходов обоих дешифраторов составляет

2n/2 + 2n/2 = 2n+1.

что гораздо меньше, чем 2n при реальных значениях n.

2.3 Рабочее задание

2.3.1 Структура 2D

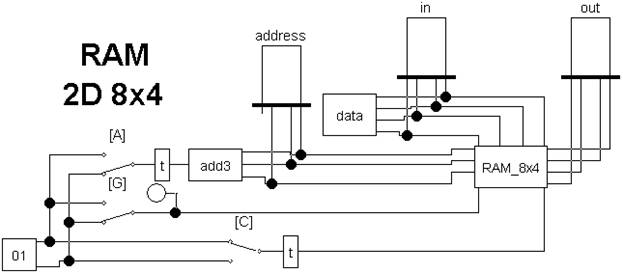

2.3.1.1 Открыть файл C:\EWB5PRO\MPS_Lab\RAM_2D_base, где представлены трехразрядный формирователь адреса (add3), четырехразрядный источник данных (data) на основе счетчиков, оформленные в виде соответствующих подсхем, а также подсхемы RAM_8x4, в состав которого входят дешифратор на восемь выходов (dc8) и матрица запоминающих ячеек (8x4), содержащая 8 ячеек (rg4) на основе регистра. Раскройте эти подсхемы и изучите их структуру.

2.3.1.2 С помощью представленных элементов (подсхем) в этом файле, собрать схему на рисунке 2.3 и исследовать ее работу, записывая в ячейки определенную информацию и проверяя затем их сохранность.

Рисунок 2.3

2.3.1.3 Создать устройство памяти RAM 2D 8x8 и схему его исследования, для чего необходимо подготовить матрицу запоминающих ячеек размерностью 8х8 на основе матрицы 8х4 и восьмиразрядный источник данных.

Проверить работу устройства.

2.3.1.4 Создать устройство памяти RAM 2D 16x4 и схему его исследования, для чего необходимо подготовить матрицу запоминающих ячеек размерностью 16х4 на основе матрицы 8х4 и использовать блоки add4 и dc16 из предыдущей работы (файл ROM_base).

Проверить работу устройства.

2.3.2 Структура 3D

2.3.2.1 Открыть файл C:\EWB5PRO\MPS_Lab\RAM_3D_base, где представлены четырехразрядный формирователь адреса (add4), четырехразрядный источник данных (data) на основе счетчиков, оформленные в виде соответствующих подсхем, а также подсхемы RAM_16x4, в состав которого входят двойной дешифратор на четыре выхода (2dc4) и матрица запоминающих ячеек (16x4), содержащая 16 ячеек (rg4) на основе регистра. Раскройте эти подсхемы и изучите их структуру.

2.3.2.2 С помощью представленных элементов (подсхем) в этом файле, собрать схему на рисунке 2.4 и исследовать ее работу, записывая в ячейки определенную информацию и проверяя затем их сохранность.

Рисунок 2.4

2.3.2.3 Создать устройство памяти RAM 3D 16x8 и схему его исследования, для чего необходимо использовать две матрицы запоминающих ячеек 16х4 и восьмиразрядный источник данных.

Проверить работу устройства.

2.4 Контрольные вопросы

1. Назовите основные параметры запоминающих устройств.

2. Что такое запоминающая ячейка?

3. В чем состоит назначение RAM?

4. Какая схемотехника обеспечивает максимальное быстродействие RAM?

5. В чем состоит принцип построения RAM с одномерной адресацией?

6. В чем состоит принцип построения RAM с двумерной адресацией?

7. Сравните преимущества и недостатки структур 2D и 3D.

8. Как расширить количество ячеек памяти в два раза?

9. Как расширить количество ячеек памяти в четыре раза?

3 Лабораторная работа №3. Cтруктура ЗУ 2DM

3.1 Цель работы:

- освоение принципа построения ЗУ по структуре 2DM.

3.2 Теоретические сведения

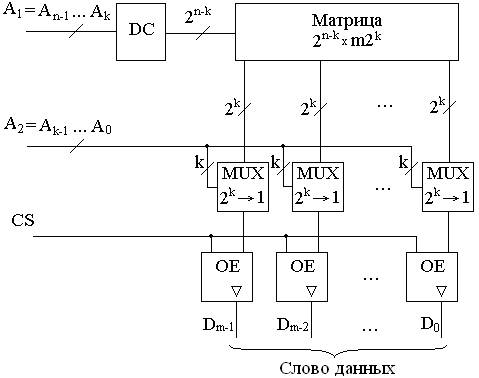

В структурах типа 2DM (2D модифицированная), предназначенной для организации систем памяти в больших системах (в частности, в компьютерах), сочетаются достоинства структур 2D и 3D – упрощается дешифрация адреса и не требуются запоминающие элементы с двухкоординатной выборкой.

Матрица ЗЭ структуры 2DM (см. рисунок 3.1) имеет как бы характер структуры 2D: возбужденный выход дешифратора выбирает целую строку. Однако в отличие от структуры 2D, длина строки не равна разрядности хранимых слов, а многократно ее превышает. Для выбора одной из строк служат часть адресного кода An–1... Ak. Остальные разряды адреса (от Ak–1... A0) используются, чтобы выбрать необходимое слово из того множества слов, которое содержится в строке, которое выполняется с помощью мультиплексоров. Длина строки равна m2k, где m – разрядность хранимых слов. Из каждого “отрезка” строки длиной 2k мультиплексор выбирает один бит. На выходах мультиплексоров формируется выходное слово. По разрешению сигнала CS, поступающего на входы ОЕ управляемых буферов с тремя состояниями, выходное слово передается на внешнюю шину.

Рисунок 3.1

3.3 Рабочее задание

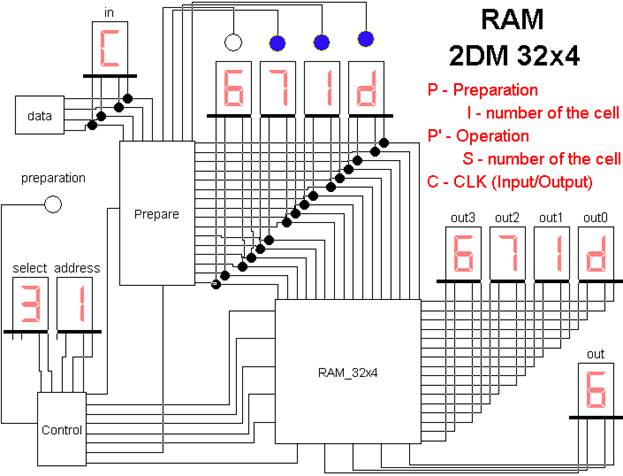

3.3.1 Открыть файл C:\EWB5PRO\MPS_Lab\RAM_2DM, где представлена схема исследования блока памяти по структуре 2DM (см. рисунок 3.2) и изучить структуру ее составных блоков, раскрывая их и изучая последующий пояснительный текст.

Рисунок 3.2

Схема содержит в своем составе следующие блоки:

- 3D блок памяти RAM_32x4;

- блока подготовки данных Prepare;

- блок управления Control.

Блок памяти RAM_32x4 состоит из следующих блоков:

- матрица элементов памяти 32х4;

- блок дешифрации строки dc8;

- блок выбора ячейки из строки (при чтении) mux4.

Матрица памяти 32х4 представляют собой (логически) 8 строк, в каждой из которых размещен блок cell_4x4, состоящая из четырех 4-разрядных ячеек памяти rg4. Физически блок памяти 32х4 реализован (с целью удобства соединения и обзора) в виде объединения двух блоков 16х4, составленных из четырех блоков cell_4x4. Каждый из внутренних блоков матрицы памяти 32х4 снабжен индикатором, что позволяет вести наблюдение за выбором строки и ячейки памяти во время эксперимента.

Блок dc8, предназначенный для выбора строки памяти, представляет собой дешифратор на восемь выходов.

Блок mux4, собранный на четырех 4-входовых мультиплексорах, позволяет выбрать ячейку из активизированной строки.

Блок Prepare предназначен для предварительной подготовки четырех 4-разрядных слов, предполагаемых для одновременной записи в одну из строк матрицы памяти. На этапе подготовки эти слова временно сохраняются во внутреннем блоке in_4, составленного из четырех 4-разрядных ячеек памяти in. Выбор одной из этих ячеек осуществляется с помощью дешифраторного блока dc4 и блока его адресации 0_3.

В блоке Control объединены управляющие клавиши и дополнительные элементы, обеспечивающие все режимы работы устройства. Устройство может работать в трех режимах:

- режим подготовки данных для записи;

- режим записи;

- режим чтения.

Режим подготовки данных осуществляется следующим образом:

- клавишой P перевести устройство в режим подготовки данных (светится соответствующий индикатор);

- клавишой I выбрать одну из четырех ячеек блока in_4 (указывает соответствующий индикатор);

- клавишой С (CLK) записать в эту ячейку одно из чисел, формируемых блоком данных data.

Перевод в режим записи/чтения осуществляется клавишой P (индикатор гаснет). В режиме записи:

- клавишой A выбрать необходимую строку матрицы памяти (указывает соответствующий 7-сегментный индикатор);

- клавишой С (CLK) записать подготовленные данные в выбранную строку матрицы памяти.

В режиме чтения:

- клавишой A выбрать необходимую строку матрицы памяти (указывает соответствующий 7-сегментный индикатор);

- клавишой S (Select) выбрать определенную ячейку из активизированной строки матрицы памяти (указывает соответствующий 7-сегментный индикатор).

3.3.2 Исследовать работу устройства памяти RAM_2DM, записав информацию во все строки матрицы, а затем проверить возможность считывания из конкретной ячейки памяти.

3.4 Контрольные вопросы

1. Объясните принципы осуществления структуры памяти 2DM.

2. Каково назначение отдельных блоков исследовательской схемы?

3. Какие основные достоинства у структуры 2DM по сравнению с другими типами структур?

4 Лабораторная работа №4. Устройство ввода информации

4.1 Цель работы:

- освоение принципов построения устройства ввода информации на шифраторе;

- приобретение навыков по совершенствованию работы устройства;

- приобретение навыков по созданию многорежимных устройств.

4.2 Теоретические сведения

Устройства ввода информации с помощью клавиатуры должен вырабатывать код, соответствующей нажатой клавише, и сформировать при этом импульс записи для сохранения полученного кода.

При модельной (как и при практической) реализации устройства на основе микросхемы шифратора (например, микросхемы 74148) при формировании кода уровень сигнала на выводе CS изменяется, что может быть использовано для формирования импульса записи, создав соответствующий формирователь одиночного импульса. Одновременно с этим необходимо обеспечить временное согласование между продолжительностью вырабатывания кода с моментом формирования импульса записи. В качестве такого формирователя был создана подсхема под названием k, вырабатывающая импульс отрицательной полярности длительностью 10 ns с задержкой 20 ns относительно начала формирования кода (момента нажатия клавиши).

При прямом использовании модели переключателя возникает необходимость возврата его в исходное состояние, т.е. приходится два раза нажимать на клавишу, соответствующую переключателю. Аналогичная проблема возникает и при практической реализации устройства, связанная с продолжительностью нажатия кнопки. Для решения этой проблемы была создана подсхема под названием 5_, формирующая отрицательной импульс длительностью 50 ns.

Следующая задача связана со способом записи сформированных кодов: цепочкой (chain) или адресно (addressing). Для иллюстрации каждой из возможностей были созданы соответствующие файлы, которые и подлежат исследованию. И наконец, в последнем файле скомбинированы оба случая, с возможностью переключения режимов записи, что позволит приобрести студентам опыт по созданию многорежимных устройств. Управление переключением режимов осуществляется с помощью комбинационной схемы m, работающей от переключателей и обеспечивающей изменение направления передачи сигналов в зависимости от режима.

4.3 Рабочее задание

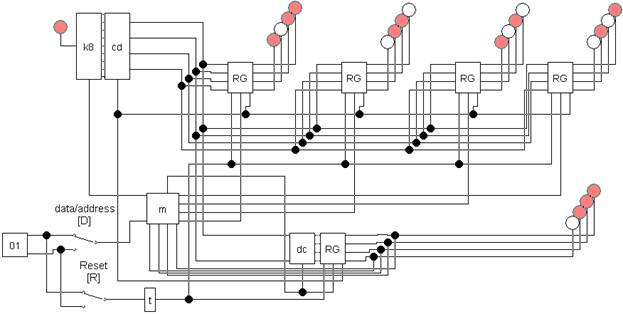

4.3.1 Открыть файл C:\EWB5PRO\MPS_Lab\Input_Chain, где представлена схема устройства ввода на основе шифратора с сохранением вырабатываемых кодов цепочкой, т.е. со сдвигом друг за другом (см. рисунок 4.1). Раскройте подсхемы, размещенные в схеме, и изучите их структуру.

Проверьте работу устройства.

Рисунок 4.1

4.3.2 Открыть файл C:\EWB5PRO\MPS_Lab\Input_Addr, где представлена схема устройства ввода на основе шифратора с сохранением вырабатываемых кодов по адресу (см. рисунок 4.2). Раскройте подсхемы, размещенные в схеме, и изучите их структуру.

Проверьте работу устройства.

Рисунок 4.2

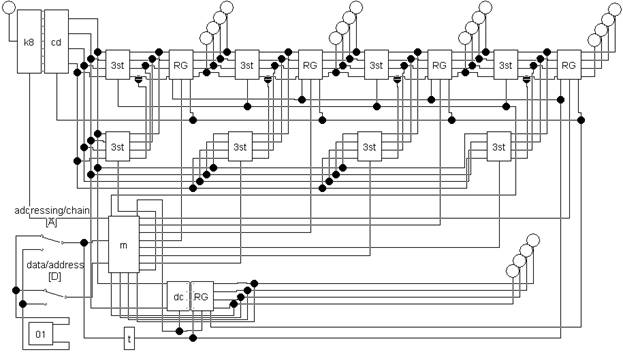

4.3.3 Открыть файл C:\EWB5PRO\MPS_Lab\Input_Comb, где представлена схема устройства ввода на основе шифратора, сочетающего оба способа записи вырабатываемых кодов (см. рисунок 4.3). Раскройте подсхемы, размещенные в схеме, и изучите их структуру.

Проверьте работу устройства.

Рисунок 4.3

4.4 Контрольные вопросы

1. Объясните назначение входных и выходных сигналов микросхемы шифратора 74148.

2. Объясните назначение подсхем 3st в схеме Input_Comb.

3. Объясните работу подсхемы m в схеме Input_Addr.

4. Объясните работу подсхемы m в схеме Input_Comb.

5 Лабораторная работа №5. Программный обмен данными

5.1 Цель работы:

- освоение принципов организации программного обмена данными в микропроцессорной системе;

- приобретение навыков по анализу работы многорежимных устройств.

5.2 Теоретические сведения

5.2.1 Обмен по асинхронной магистрали Q-bus

Организация программно-управляемого обмена по асинхронной мультиплексированной магистрали Q-bus осуществляется следующим образом.

На шине адреса/данных (AD) в начале цикла обмена (в фазе адреса) процессор (задатчик) выставляет код адреса, одновременно с ним отрицательный стробирующий сигнал SYNC’. Фаза адреса одинакова в циклах записи и чтения.

В фазе данных цикла чтения (см. рисунок 5.1) процессор выставляет отрицательный сигнал строба чтения данных DIN’, в ответ на который устройство-исполнитель выставляет свой код данных (читаемые данные), подтверждая выполнение операции обмена сигналом RPLY’.

Рисунок 5.1

Процессор, получив сигнал RPLY’, снимает сигнал DIN’. В ответ устройство-исполнитель заканчивает сигнал подтверждения RPLY’. После этого процессор заканчивает цикл обмена, снимая сигнал SYNC’.

В фазе данных цикла записи (см. рисунок 5.2) процессор выставляет на шину AD код записываемых данных, сопровождая его отрицательный сигналом строба записи данных DOUT’. Получив этот сигнал, устройство-исполнитель принимает данные, подтверждая выполнение операции обмена сигналом RPLY’. Последующие действия процессора и устройства-исполнителя аналогичны действиям при цикле чтения.

На данной магистрали адрес передается синхронно (без подтверждения его получения исполнителем), а данные передаются асинхронно, с обязательным подтверждением их выдачи или приема исполнителем.

Рисунок 5.2

5.2.2 Обмен по синхронной магистрали ISA

Организация программно-управляемого обмена на синхронной немультиплексированной магистрали ISA осуществляется следующим образом.

Оба цикла начинаются с выставления процессором (задатчиком) кода адреса на шину адреса SA, адрес на которой остается до конца цикла. Фаза адреса, одинаковая для обоих циклов, заканчивается с началом строба обмена данными IOR’ или IOW’. В течение фазы адреса устройство-исполнитель, распознавшее адрес, переходит в состояние готовности к обмену.

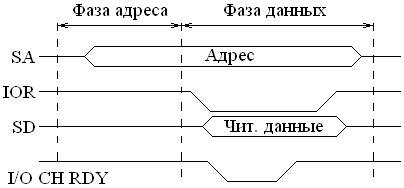

В фазе данных цикла чтения (см. рисунок 5.3) процессор выставляет отрицательный сигнал чтения данных из УВВ IOR’, в ответ на который устройство-исполнитель выставляет на шину данных SD свой код данных (читаемые данные). Через установленное время процессор снимает строб обмена IOR’, затем и код адреса с шины SA.

Рисунок 5.3

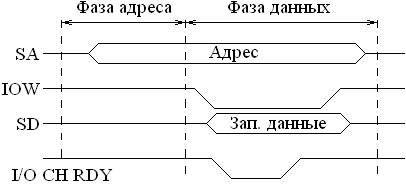

В фазе данных цикла записи по магистрали ISA (см. рисунок 5.4) процессор выставляет на шину данных SD код записываемых данных, сопровождая их стробом записи данных в УВВ IOW’. Получив этот сигнал, устройство-исполнитель принимает с шины SD код записываемых данных.

Рисунок 5.4

5.3 Рабочее задание

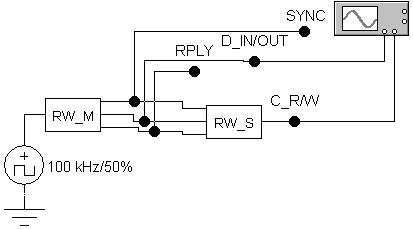

5.3.1 Открыть файл C:\EWB5PRO\MPS_Lab\Q-bus_1, где представлена схема устройства для изучения принципов организации программно-управляемого обмена по асинхронной магистрали Q-bus (см. рисунок 5.5), реализованного в двух блоках: инициатора обмена RW_M (Master) и исполнителя RW_S (Slave). С целью облегчения наблюдения за процессами в устройстве, в качестве сигнала инициализации обмена используется отрицательный перепад сигнала генератора, подключенного на вход SD. Раскройте подсхемы, размещенные в схеме, и изучите их структуру.

Рисунок 5.5

5.3.2 Исследуйте работу устройства, наблюдая за формированием сигналов управления обменом (SYNC, DIN/DOUT, RPLY, C_R/W) с помощью осциллографа. Постройте временные диаграммы сигналов путем наложения с помощью программы Paint и определите временные параметры сигналов (продолжительность, смещение относительно друг друга). Следует иметь ввиду, что процесс работы устройства искусственно замедлен, для удобства наблюдения.

5.3.3 Открыть файл C:\EWB5PRO\MPS_Lab\Q-bus_2, где представлена схема устройства (см. рисунок 5.6), где позволяющее реализовать обмен информацией между микропроцессором (MP) – инициатором процесса (Master) и четырьмя периферийными устройствами (Per) – исполнителями (Slave). Раскройте подсхемы, размещенные в схеме, и изучите их структуру.

Рисунок 5.6

5.3.4 Исследуйте работу устройства в следующем порядке.

1. Этап подготовки данных:

- установить устройство в режим подготовки переключателем M (mode – режим), при этом соответствующий индикатор должен находиться в несветящемся состоянии, т.е. m = 0;

- переключатель V (verify – проверка) также должен быть установлен в нулевое состояние v = 0;

- поставить переключатель A/D в режим ввода адреса (A/D = 1) и ввести адрес периферийного устройства (0 – 3);

- перевести переключатель A/D в режим ввода данных (A/D = 0) и ввести данные в выбранное периферийное устройство одной из клавиш 0 – 7, при этом, если необходимо ввести число значением между 8 и 15, то клавишу 8 поставить в единичное состояние, что подтверждается соответствующим индикатором;

- возвратить устройство в режим адресации (A/D = 1) и аналогично продолжить ввод адреса и различных данных для следующих периферийных устройств;

- также ввести данные в буферный регистр данных микропроцессора (MP), его установочный адрес – 5;

- ввести адрес периферийного устройства (например, 1), с которым MP предполагает осуществить обмен, этот адрес сохраняется в адресном регистре с установочным адресом 4.

2. Этап проверки правильности и сохранности данных:

- перевести устройство в режим проверки установкой клавиши V (Verify – проверка) в единичное состояние;

- устанавливая номер периферийного устройства нажатием клавиши N (Number – номер), проверить их содержимое;

- возвратить клавишу N в нулевое состояние.

3. Этап реализации обмена данных:

- перевести устройство в операционный режим, т.е. в режим реализации обмена данных, установкой клавиши M (Mode – режим) в единичное состояние;

- ввести адрес периферийного устройства, с которым MP предполагает осуществить обмен, в адресный регистр (его установочный адрес – 4) микропроцессора. Для этого необходимо временно перевести устройство в режим подготовки и после ввода адреса возвратить устройство в операционный режим;

- одноразовым нажатием клавиши R (Read) выполнить считывание информации из адресованного периферийного устройства (с установленного ранее устройства 1), т.е. ввести копию его содержимого в регистр данных микропроцессора, результат которого иллюстрируется соответствующим 7-сегментным индикатором;

- установить адрес другого периферийного устройства (например, 3) и нажатием клавиши W (Write) произвести запись копии содержимого регистра данных микропроцессора в это устройство;

- переводом устройства в режим проверки данных (клавиша V) и с помощью клавиши N проверить содержимое периферийных устройств и убедиться, что в результате выполненных операций содержимое регистра данных микропроцессор, а также устройств 1 и 3 стали идентичными;

- повторить операции обмена в различных вариантах, например, осуществить круговой сдвиг информации в периферийных устройствах.

5.4 Контрольные вопросы

1. Объясните принципы организации программно-управляемого обмена по мультиплексированной асинхронной магистрали Q-bus.

2. Как организован в лабораторной работе процесс передачи адреса (синхронно или асинхронно)? А данных?

3. Объясните принципы организации программно-управляемого обмена по немультиплексированной синхронной магистрали ISA.

4. Объясните принципиальные различия в организации асинхронного обмена по магистралям Q-bus и ISA.

6 Лабораторная работа №6. Параллельный интерфейс

6.1 Цель работы:

- освоение принципов структурной организации параллельного интерфейса и порядка его работы.

6.2 Теоретические сведения

К основным элементам интерфейса относят протокол обмена (совокупность правил, регламентирующих способ выполнения заданных функций), аппаратную часть (физическую реализацию устройств) и программное обеспечение.

К простейшим типам параллельных интерфейсов относятся шинные формирователи (ШФ) и буферные регистры (БР). ШФ отключают источник информации от шины, когда он не участвует в обмене. Двунаправленные ШФ позволяют в зависимости от сигнала управления изменять направление передачи информации. БР с тремя состояниями на выходах, наряду с буферизацией данных, обеспечивают портам возможность отключения от магистрали под действием управляющих сигналов. Более сложные операции выполняются периферийными адаптерами (параллельными интерфейсами).

6.3 Рабочее задание

6.3.1 Открыть файл C:\EWB5PRO\MPS_Lab\ParInt_1, где представлена схема устройства параллельной передачи информации (см. рисунок 6.1), позволяющая понять принципы структурной организации параллельного интерфейса и порядок его работы.

Рисунок 6.1

Блоки микропроцессора MP и периферийного устройства PER внешне эмулируют работу соответствующих устройств. В их состав введены полнофункциональные буферы и двунаправленные шинные формирователи.

Исследуйте принципы двунаправленной передачи информации из одного устройства в другое. Передача осуществляется однократным нажатием клавиши C (CLK), а направление передачи управляется клавишей D (Direction).

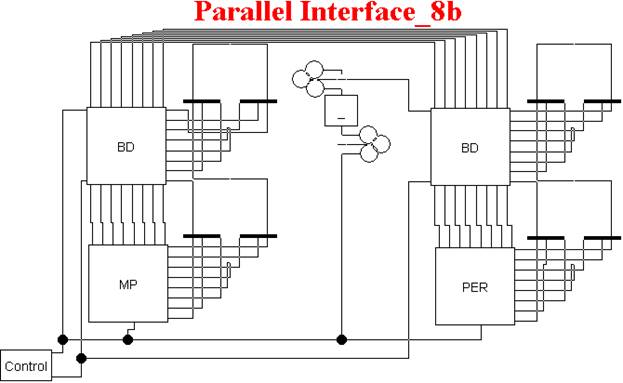

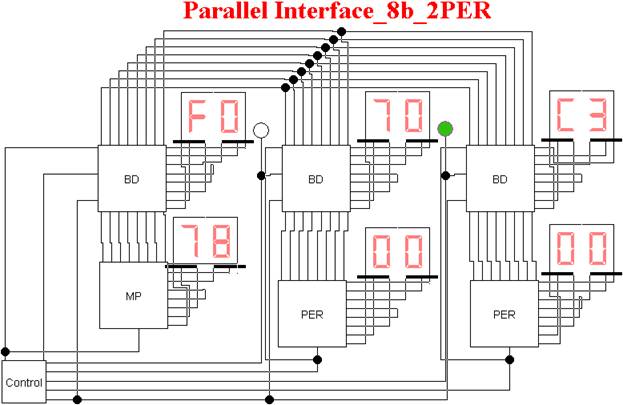

6.3.2 Открыть файл C:\EWB5PRO\MPS_Lab\ParInt_2, где представлена схема устройства (рисунок 6.2), эмулирующего принцип организации и работы микропроцессорной системы с двумя портами.

Исследуйте работу устройства. Активизация одного из периферийных устройств осуществляется клавишей P (Peripheral).

Рисунок 6.2

6.4 Контрольные вопросы

1. Каково назначение шинных формирователей?

2. Какие функции выполняют буферные регистры?

3. Как осуществляется двунаправленность передачи данных на лабораторной модели?

4. Объясните структуру и режимы работы периферийного адаптера Intel 8255A (К580ВВ55А).

7 Лабораторная работа №7. Последовательный интерфейс

7.1 Цель работы:

- освоение принципов структурной организации последовательного интерфейса и порядка его работы.

7.2 Теоретические сведения

При увеличении расстояний, на которые передаются данные, применяют преобразование параллельных данных в последовательные для их передачи по одной сигнальной линии. Кроме того, многие ВУ оперируют с последовательными кодами и для взаимодействия с процессором нуждаются в преобразовании данных из параллельной формы в последовательную и наоборот.

Протоколы последовательного обмена задают два его вида: асинхронный и синхронный.

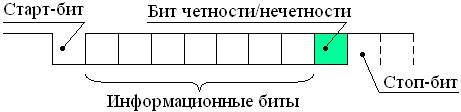

При асинхронных передачах посылка (кадр), т. е. группа битов, отображающих символ, имеет следующий формат: начало посылки отмечается нулевым старт-битом, за ним следуют 5...8 информационных битов (младшим разрядом вперед), затем идет необязательный бит контроля по модулю 2 (бит четности/нечетности) и заканчивается посылка 1; 1,5 или 2 единичными стоп-битами (см. рисунок 7.1). Таким образом, приемник синхронизируется самим сигналом.

Рисунок 7.1

Различают две разновидности синхронных передач – с внутренней и внешней синхронизацией.

При внутренней синхронизации перед массивом данных передаются слова – синхросимволы (одно или два). При отсутствии передачи передатчик не перестает работать, а посылает в линию символы синхронизации.

При внешней синхронизации в канал связи вводится дополнительная линия, по которой передается строб-сигнал, отмечающий интервал времени, соответствующий передаче данных. Фронты строба отмечают начало и конец передачи массива, в котором символы по-прежнему передаются слитно (без старт- и стоп-битов).

7.3 Рабочее задание

7.3.1 Открыть файл C:\EWB5PRO\MPS_Lab\SerInt, где представлена схема устройства последовательной передачи информации (см. рисунок 7.2), позволяющая понять принципы структурной организации последовательного интерфейса и порядок его работы.

Рисунок 7. 2

Устройство состоит из двух блоков: передатчика и приемника. Четырехразрядное слово, сформированное источником данных (d_4) и предназначенное для передачи, хранится в буфере данных (BD). Это слово в блоке drive (передать) обрамляется четырьмя служебными битами (старт-бит, стоп-бит, признак проверки четности и бит четности) и восемью тактовыми импульсами, сформированных блоком p_8, передается по единственной связной линии.

Преобразованное в блоке accept (принять) в параллельную форму восьмиразрядные данные проверяются в блоке check (контроль) на соответствие всех служебных битов, и в случае их правильности освобожденное от обрамления четырехразрядное слово передается в выходной буфер данных sink (приемник). В случае обнаружения ошибки передачи соответствующий индикатор (Error) оповещает об этом, и четырехразрядное слово не выделяется.

Произведите проверку работы последовательного интерфейса следующим образом:

- клавишей D (Data Input/Transfer') установите устройство в режим выбора данных (Data Input) и одноразовым нажатием клавиши С (CLK) выбрать (поймать) какое-либо число и сохранить его в буфере данных BD;

- клавишей D перевести устройство в режим передачи (Transfer).

Дальнейшие действия устройства осуществляются автоматически, остается только наблюдать за результатами преобразования и передачи. После окончания передачи (как в случае правильности передачи, так и в случае ошибки) по показаниям информационных индикаторов проанализировать полученный результат.

Аналогичным путем повторить эксперимент несколько раз.

7.4 Контрольные вопросы

1. Какие функции выполнят последовательный интерфейс?

2. Объясните работу последовательного интерфейса в асинхронном режиме.

3. Объясните структуру и режимы работы периферийного адаптера Intel 8255A (К580ВВ55А).

Список литературы

1. Угрюмов Е. П. Цифровая схемотехника. – СПб.: БХВ-Петербург, 2004.

2. Бойко В.И. и др. Схемотехника электронных устройств. Микропроцессоры и микроконтроллеры. – СПб.: БХВ-Петербург, 2004.

3. Уэйкерли Дж. Ф. Проектирование цифровых устройств. – М.: Постмаркет, 2002.

4. Сугано Т. Дж., Уидмер Н. С. Цифровые системы. Теория и практика: Пер. с англ. – М.: Издательский дом “Вильямс”, 2004.

5. Опадчий Ю. Ф., Глудкин О. П., Гуров А. И. Аналоговая и цифровая электроника / Под ред. О.П. Глудкина. – М.: Радио и связь, 2003.

6. Токхейм Р. Основы цифровой электроники: Пер. с. англ. – М.: Мир, 1988.

7. Шанаев О.Т. Система моделирования Electronic Workbench / на казахском и русском языках. – Алматы, 2003.

Содержание

1 Лабораторная работа №1. Запоминающие устройства типа ROM

2 Лабораторная работа №2. Базовые структуры ЗУ

3 Лабораторная работа №3. Cтруктура ЗУ 2DM

4 Лабораторная работа №4. Устройство ввода информации

5 Лабораторная работа №5. Программный обмен данными

6 Лабораторная работа №6. Параллельный интерфейс