АЛМАТЫ ЭНЕРГЕТИКА ЖӘНЕ БАЙЛАНЫС ИНСТИТУТЫ

Электроника кафедрасы

ЦИФРЛЫҚ ҚҰРЫЛҒЫЛАР ЖӘНЕ МИКРОПРОЦЕССОРЛАР

5В0719 – Радиотехника, электроника және телекоммуникация мамандығындағының барлық оқу түріндегі студенттер үшін курстық жұмысты орындауға арналған тапсырма мен әдістемелік нұсқаулар

Алматы 2010

ҚҰРАСТЫРУШЫЛАР: С.Н. Петрищенко, Г.Д. Мусапирова. Цифрлық құрылғылар және микропроцессорлар. 050719 – Радиотехника, электроника және телекоммуникация мамандығындағы барлық оқу түріндегі студенттер үшін курстық жұмысты орындауға арналған тапсырма мен әдістемелік нұсқаулар. - Алматы: АЭжБИ, 2010. – 14 б.

Бұл әдістемелік нұсқауда (құрастырмада) «Цифрлық құрылғылар және микропроцессорлар» курсы бойынша курстық жұмысқа тапсырма мен оны орындаудың әдістемелік нұсқаулары берілген. Курстық жұмыс микропроцессор негізінде деректер жинау құрылғысын ұйымдастыруға арналған. Микропроцессорлық құрылғыны ұйымдастыру кезінде, оның құрылымдық схемасын құрып, микросхемалар негізінде берілген сыйымдылықты оперативті жадысын ұйымдастырып, құрастырылған алгоритм бойынша ассемблер тілінде және машиналық кодтармен программасын жазу керек, сонымен қатар құрастырылған құрылғының тез әрекеттілігін бағалау қажет.

Әдістемелік құрастырма 050719 – Радиотехника, электроника және телекоммуникация мамандығындағының студенттеріне арналған.

1 Курстық жұмыс және оны орындауға әдістемелік нұсқаулар

Курстық жұмыстың мақсаты: «Цифрлық құрылғылар және микропроцессорлар» курсын оқып үйренуде алған білімдерін бекіту. Микропроцессорлық құрылғы түрінде деректерді жинау құрылғысын ұйымдастыру тәсілдеріне арналған. Студентке күрделі микропроцессорлық техниканы оқып үйренудің бастапқы этапында деректер жинаудың есептеу процессін ұйымдастыру үшін Intel 8080 (аналогтары KP580ИК80 және КР580ВМ80А) немесе i8085 (аналогы K1821BM85A) сегізразрядты қарапайым модельдерін қолдану керек.

Байланыс арналарын өлшеу немесе телеметриялық ақпаратты электронды-есептеу машинасына (ЭЕМ) қабылдау кезінде мәліметтер жинауды қамтамасыз ету қажеттілігі жиі туады. Ол кезде ток немесе кернеу түріндегі аналогтық сигналдарға сұраныс жасау, оларды цифрлық түрге түрлендіріп, одан ары қарай өңдеп және көрсету мақсатымен оперативті жадының (ОЕСҚ) белгілі бір аймағына орналастырумен бірге орындалады

1.1 Курстық жұмысқа тапсырма

Келісі түрде жұмыс істейтін деректерді жинақтау құрылғысын (ДЖҚ) жобалау керек: (АК) арналар коммутаторының F кірістеріне келіп түсетін аналогты сигналдарды тізбек бойынша сұрап шығып, аналогты-цифрлық түрлендіргіш (АЦТ) көмегімен цифрлық сигналға түрлендіріп, (1 байт=8бит разрядты екілік сөз) оларды оперативті есте сақтау құрылғысының (ОЕСҚ) М символдық аты бар адресті ұяшықтан басталатын аймағына орналастыру керек.

ДЖҚ-ның құрамында адрестік сөзінің форматы 2 байт =16 бит және Q = N·n сыйымдылықты ОЕСҚ-сы бар. Микропроцессорлық жүйенің жұмысын синхрондау тактілік импульстер генераторының (ТИГ) көмегімен іске асады. Синхрондау жиілігі f=500 кГц.

Талап етіледі:

а) ОЕСҚ ұйымдастыруды қарастыру;

б) 8-разрядты микропроцессор (МП) негізінде орындалған микропроцессорлық құрылғы түріндегі ДЖҚ-ны іске асыру. Бұл кезде кезекті арналардың адресі 1 кестесіне сәйкес берілген нұсқа бойынша R регистрінде сақталу керек. Микропроцессорлық құрылғыны құрылымдық схема түріне келтіріп жұмыс істеуінің программасын ассемблер тілінде құру керек және программаның жадысында BEG адресті ұяшығынан бастап орналасу кестесін келтіріп, программаны кодалық комбинацияларда (машиналық тілде) жазу;

в) ДЖҚ-ның тезәрекеттілігін анықтау.

Жеке тапсырма нұсқалары 1 кестесінде берілген.

Жеке тапсырма нұсқасы студенттік билет нөмірінің соңғы (Nсоңғы ) және соңғы алдындағы (Nсоң.алд ) сандармен анықталады.

1 кестесі

|

Nсоң.алд |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

F10 |

16 |

8 |

7 |

9 |

10 |

12 |

11 |

13 |

15 |

14 |

|

R |

D |

E |

C |

B |

D |

C |

E |

B |

E |

D |

|

Nсоңғы |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

М |

01А2 |

04F6 |

732С |

003C |

01AE |

0701 |

3614 |

01B0 |

012A |

03E5 |

|

Q |

2048 x 8 |

8192 x 8 |

32768 x 8 |

512 x 8 |

1024 X 8 |

2048 x 8 |

32768 x 8 |

512 x 8 |

32768 x 8 |

1024 x 8 |

|

ВЕG |

03В4 |

1A4D |

56B9 |

0Е21 |

01D8 |

03B6 |

4C82 |

006A |

031A |

071F |

1.2 Курстық жұмысты орындауға әдістемелік нұсқаулар

Қойылған есепті шығару әдісі келесі үлгі бойынша құрастырылған. ДЖҚ-ны жобалау үшін бастапқы шарттар келесідей болсын: F = 1610 ; М = 21А0h; Q = 64K·8, яғни 64·1024 = 65536 1 байт разрядты ұяшықтар; R = B; BEG = 21C8h .

1.2.1 Оперативті есте сақтау құрылғысын (ОЕСҚ) ұйымдастыру

Оперативті жады жартылайөткізгішті ОЕСҚ-ның үлкен интегралды схемаларында (ҮИС) ұйымдастыру керек.

ҮИС-ды таңдау келесі талаптарға сәйкес орындалады:

- апараттар шығындарының ықшамдылығы (корпустар саны);

- қоректену қуатының ықшамдылығы;

- МПЖ және басқаларының тезәрекеттілігін өсіру мүмкіндігі.

Талап етілген Мт сыйымдылықты оперативті жадының m микросхемалар саны келесі формуламен анықталады

![]() m

= Mт /

M1

m

= Mт /

M1

бұл жерде М1 – таңдалған микросхемалардың бірінің сыйымдылығы.

Разрядтылықты өсіру үшін жолақтар ұйымдастырылады. Әр жолақтағы микросхемалар саны

m1 = n тал / nтаң

бұл жерде n тал – талап етілген разрядтылық;

nтаң – таңдап алынған микросхема разрядтылығы.

mжол жолақтар саны келесі формуламен берілген

mжол = m / m1 .

![]()

![]()

![]()

![]() Екі

жолақтың бірін іске қосу үшін жолақтар арасына

ЕМЕС логикалық элементін қолдану керек, ал жолақтардың

саны одан көп болса, кірісіне жолақ адресінің екілік коды берілетін

дешифратор қолдану керек. Дешифратор шығысын барлық

микросхемалардың

СS

(кристалл таңдау) кірісімен

қосу керек.

СS =

1 кезінде бұл жолақтағы

микросхемаларға қосылу мүмкін емес (сақтау режімі).

СS

= 0

кезінде

–

қосылу

мүмкін.

СS

сигналын қалыптастыру

кезінде адрестік шинаның іске аспаған жоғарғы

разрядтары қолданылады.

Екі

жолақтың бірін іске қосу үшін жолақтар арасына

ЕМЕС логикалық элементін қолдану керек, ал жолақтардың

саны одан көп болса, кірісіне жолақ адресінің екілік коды берілетін

дешифратор қолдану керек. Дешифратор шығысын барлық

микросхемалардың

СS

(кристалл таңдау) кірісімен

қосу керек.

СS =

1 кезінде бұл жолақтағы

микросхемаларға қосылу мүмкін емес (сақтау режімі).

СS

= 0

кезінде

–

қосылу

мүмкін.

СS

сигналын қалыптастыру

кезінде адрестік шинаның іске аспаған жоғарғы

разрядтары қолданылады.

![]()

![]()

![]() ОЕСҚ

микросхемаларына екілік сөздерді жазу мен одан оқу режімдерін

қамтамасыз ету үшін

RD/WR

(оқу/жазу) кірістері

қарастырылған.

RD/WR

= 0

кезінде жазу

режімі, ал

RD/WR

= 1 болғанда оқу режімі.

ОЕСҚ

микросхемаларына екілік сөздерді жазу мен одан оқу режімдерін

қамтамасыз ету үшін

RD/WR

(оқу/жазу) кірістері

қарастырылған.

RD/WR

= 0

кезінде жазу

режімі, ал

RD/WR

= 1 болғанда оқу режімі.

2 кестесінде оперативті жадының кейбір микросхемаларының негізгі параметрлері берілген.

2 кестесі

|

Микросхема типі |

Сыйымдылығы |

Цикла уақыты (таңдау), нс |

Қоректену қуаты, мВт |

Қоректену кернеуі, В |

Технология |

|

К155РУ5 |

256Х1 |

90 |

< 735 |

5 |

ТТЛ |

|

КР537РУ13А |

1КХ4 |

120 |

350 |

5 |

КМДП |

|

КР541РУ5 |

1КХ8 |

(55) |

< 500 |

5 |

ИИЛ-ТТЛ |

|

КР537РУ10 |

2КХ8 |

220 |

350 |

5 |

КМДП |

|

КМ132РУ13А |

2КХ8 |

(55) |

900 |

5 |

n-МДП |

|

К537 РУ14А |

4КХ1 |

110 |

250 |

5 |

КМДП |

|

КМ132РУ12А |

4КХ4 |

(50) |

700 |

5 |

n-МДП |

|

КР132РУ6А |

16КХ1 |

75 |

400 |

5 |

n-МДП |

|

КМ132РУ10А |

64КХ1 |

90 |

420 |

5 |

n-МДП |

Ақпаратты шығынды ықшамдау тұрғысынан 2 кестесінен КМ132РУ10А ОЕСҚ микрасхемасын таңдаймыз. Ол разрядтылығы 1 бит 64К ұяшығынан тұрады. 64КХ8 сыйымдылықты ОЕСҚ құру үшін осындай 8 микросхема қажет. Өйткені:

.

.

1 суретінде бұндай ОЕСҚ-ның құру сұлбасы берілген. Әр сұлбаның адрестік кірістер саны А = 16, яғни 216 1 бит разрядтылықты 65536 ұяшық жадыларының адрестеуін қамтамасыз етеді. ОЕСҚ-ның 8 микросхемасын бір жолақта ұйымдастыру кезінде талап етілген Q = 64K·8 сыйымдылығы алынады.

Барлық сегіз микросхеманы бір

уақытта жұмысқа қосу үшін олардың CS кірістеріне логикалық нөл беруді

қамтамасыз ету керек. DI (data input) кірістері бойынша жазу, DO

(data output) бойынша жады микросхемасына жазылған ақпаратты

оқу орындалады.

Барлық сегіз микросхеманы бір

уақытта жұмысқа қосу үшін олардың CS кірістеріне логикалық нөл беруді

қамтамасыз ету керек. DI (data input) кірістері бойынша жазу, DO

(data output) бойынша жады микросхемасына жазылған ақпаратты

оқу орындалады.

:

◊

0

1 суреті

1.2.2 8-разрядты микропроцессор базасында микропроцессорлық құрылғы түрінде ДЖҚ-ны іске асыру.

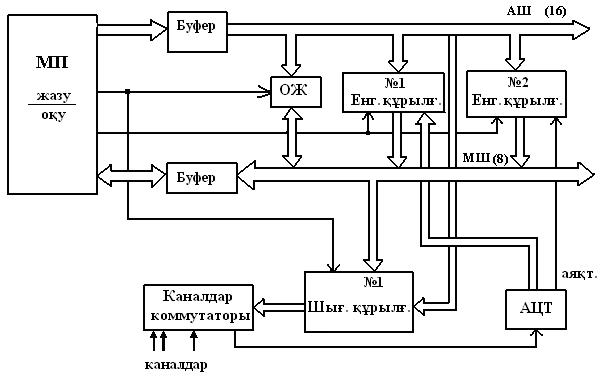

Микропроцессорлық құрылғы (МПҚ) түрінде құрастырылған ДЖҚ-ның құрылымдық схемасы 2 суретінде көрсетілген. МПҚ құрамында микропроцессор, АЦТ, оперативті жады (ОЖ) аналогты арналар коммутаторынан басқа екі енгізу және бір шығару құрылғылары бар, олардың жұмысын программалы-басқармалы регистр-порттар атқарады. Мысалы, К589ИР12 көпрежімді буферлік регистрлер (КБР). Бұл вариант бойынша МПҚ мен басқару шинасы екі жолақтан ғана тұра алады: ЖАЗУ және ОҚУ.

2 суреттегі схемада қарапайымдылық үшін АЦТ түрлендіруінің соңын білдіретін сигналды көрсететін АЦТ-ның триггер-жалауы (Тжалау) көрсетілмеген.

ОЖ-ның 21АОh адресінен басталатын жады ұяшықтары мәліметтер жинақтауға арналған және бұл адрес HL регистрлер жұбында сақталады. Тапсырмаға сәйкес аналогты арнаның кеезекті адресін В регистріне орналастырамыз (біздің мысалда тапсырмаға сәйкес R = В).

2 суреті

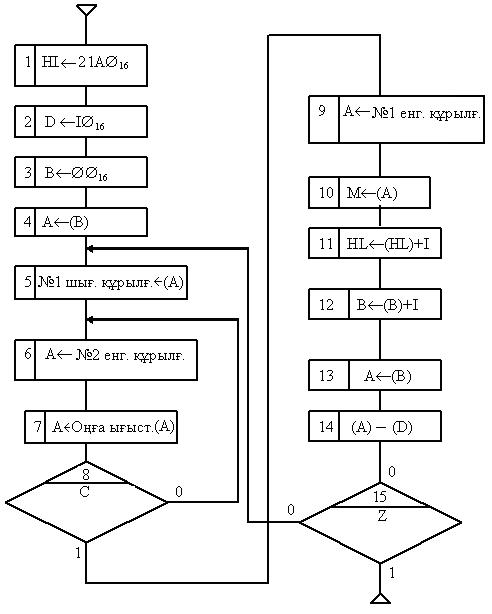

0 нөмірлі (адрес) аналогты арнадан бастап ақпаратты қабылдаймыз. Мәліметтерді жинақтау циклының соңын білдіретін белгіні қалыптастыру үшін F санын (аналогты каналдар саны) D регистріне орналастырамыз. Біздің мысалда F = 1610. Онда мәліметтер жинау алгоритмінің блок-схемасы 3 суретінде көрсетілген.

Блок-схемаға қысқа түсініктеме берейік. I блокта HL регистрлер жұбына M = 21АОh бастапқы адресі енгізіледі. II блокта D регистріне 1610 (10h ) санын енгізу керек. III блокта R = B регистрі аналогты каналдар санының санағышы қызметін атқарады. Оған алғашқы каналдың адресі ØØh енгізіледі. Келесі кезекте бұл адрес аккумулятор және №1 шығару құрылғысы арқылы (4 пен 5 блоктары) 2 суретінде көрсетілгендей коммутатордың адрестік кірісіне келіп түседі. Коммутатор адресі көрсетілген арнаны АЦТ кірісіне қосады да түрлендіруді орындайды. АЦТ түрлендіру жұмысын аяқтағанша МПҚ күту режіміне көшеді (6, 7 және 8 блоктары). АЦТ-ның аяқт. шығысынан сигнал №2 енгізу регистр-портының кіші разрядына келеді. Аяқт.=0 болса АЦТ жұмысы аяқталмағанын білдіреді. Бұл кезде 6-8 блоктары нөл триггер-жалауының жұмысын қамтамасыз етеді және программа кіші цикл бойынша орындалады. Бағдарламаның осылай орындалу режімі АЦТ-ның аяқт. шығысындағы сигнал 1 болғанға дейін қайталанады. Бұл күту режімін қамтамасыз етеді. Аяқт.=1 болғанда ғана 8 блогының командасы орындалып АЦТ шығысындағы түрленген сигнал С=1болады, яғни аналогты сигнал цифрлыға түрленеді және № 1 енгізу құрылғысы арқылы микропрцессордың аккумуляторына келіп одан берілген оперативті жады ұяшығына жазылады (9 және 10 блоктары).

3 суреті

11 және 12 блоктарында кезекті аналогты арна мен келесі ақпаратты жазуға жады ұяшығының адрестері қалыптасады. Арнаның жаңа адресі аккумуляторға жіберіледі (13 блогы). 14 блогында В және D регистрлеріндегі деректер салыстырылады. В = D = 0 теңдігі барлық арналардағы ақпарат оқылып, z = 1 нөлдік белгісі шыққанын, яғни деректерді жинақтау аяқталғанын көрсетеді. Егер z = 0 болса, яғни салыстыру операциясынан кейін аккумулятордағы мәлімет өзгермесе адресі 13 блогында енгізілген келесі арнадан ақпарат оқылады. 12 блогында көрсетілген В регистріндегі кезекті аналогты арнаның адресі IÆ16 санына тең болғанша программа үлкен цикл бойынша қайталанады. Ассемблер тіліндегі программасы 3 кестесінде келтірілген.

3 кестесі

|

Командалар № Команды |

Белгі |

Мнемокод |

Операнд (тар) |

Түсініктеме |

Байттар |

Циклдар |

Тактілер |

|

1 |

|

LXI |

H,21A0h |

HL ← 21A0h |

3 |

3 |

10 |

|

2 |

|

MVI |

D,10h |

D ← 10h |

2 |

2 |

7 |

|

3 |

|

MVI |

B,00h |

B ← 00h |

2 |

2 |

7 |

|

4 |

|

MOV |

A,B |

A ← B |

1 |

1 |

5 |

|

5 |

К2 |

OUT |

1 |

№1шығ.құрылғ.← (A) |

2 |

3 |

10 |

|

6 |

К1 |

IN |

2 |

A ← №2 енг.құрылғ. |

2 |

3 |

10 |

|

7 |

|

RRC |

|

A ← оңға ығыст. (А) |

1 |

1 |

4 |

|

8 |

|

JNC |

K1 |

8 блогы ШӨ |

3 |

3 |

10 |

|

9 |

|

IN |

1 |

А ← №1 енг.құрылғ. |

2 |

3 |

10 |

|

10 |

|

MOV |

M,A |

M ← (A) |

1 |

2 |

7 |

|

11 |

|

INX |

H |

HL ← (HL) + 1 |

1 |

1 |

5 |

|

12 |

|

INR |

B |

B ← (B) + 1 |

1 |

1 |

5 |

|

13 |

|

MOV |

A,B |

A ← (B) |

1 |

1 |

5 |

|

14 |

|

CMP |

D |

(A) - (D) |

1 |

1 |

4 |

|

15 |

|

JNZ |

K2 |

15 блогы ШӨ |

3 |

3 |

10 |

3 кестесінде келесі қысқартулар келтірілген: оңға ығыст. (А) – А регистріндегі (аккумулятор) деректі оңға ығыстыру, ШӨ – шартты өту.

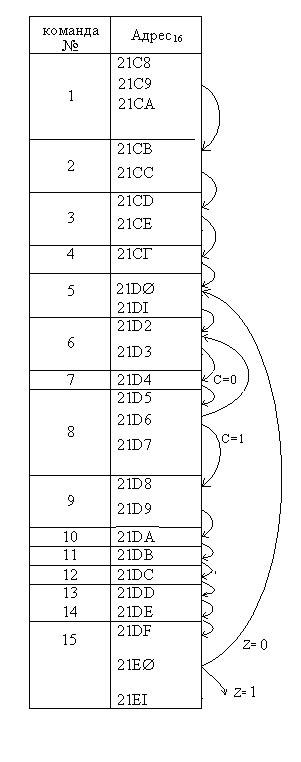

Программаның жадыда орналасуы 4 кестесінде келтірілген.

4 кестесі

Командаға керек ОЖ ұяшықтар саны команданың байттар санымен анықталады. 4 кестесінде сілтеуішпен командалардың орындалу кезектілігі көрсетілген. Шартты өту командаларында шартқа байланысты қастарында шарт-сигналы көрсетілген қос сілтеме берілген.

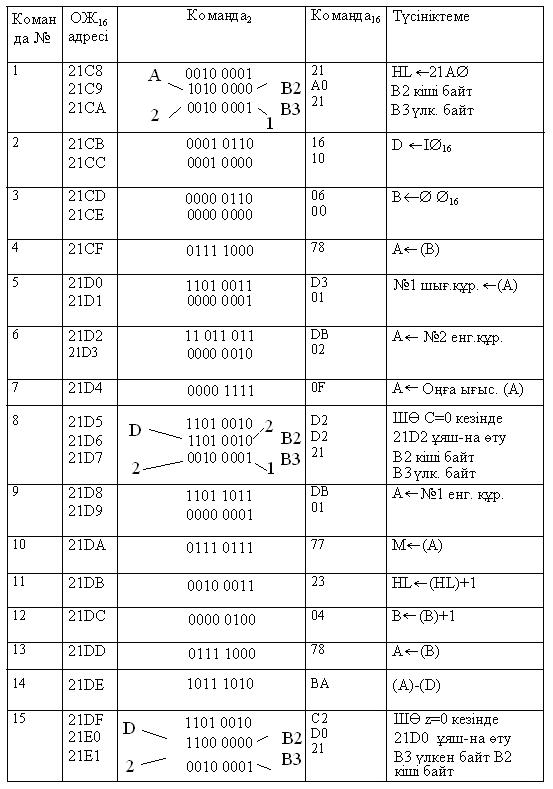

5 кестесінде программа кодалық комбинация түрінде көрсетілген.

5кестесі

1.2.3 Микропроцессорлық құрылғының тезәрекеттілігін бағалау

Микропроцессорлық құрылғының

тезәрекеттілігін бағалау үшін АЦТ түрлендіруінің

ұзақтығы ![]() синхроимпульстар периодынан

аз деп есептеп кіші циклдың өту уақытын есепке алмаймыз. 3

кестесіне сәйкес 1 ÷ 4 командаларының

орындалуына жұмсалатын тактілер саны 10+7+7+5=29.

синхроимпульстар периодынан

аз деп есептеп кіші циклдың өту уақытын есепке алмаймыз. 3

кестесіне сәйкес 1 ÷ 4 командаларының

орындалуына жұмсалатын тактілер саны 10+7+7+5=29.

Үлкен цикл бойынша бір рет өту үшін керек тактілер саны (5 ÷ 15 командаларының орындалуына) 10+10+4+10+10+7+5+5+5+4+10=80. Бұл үлкен цикл F=1610 рет орындалады, және 80∙16=1280 тактілер болады. Нәтижесінде деректерді жинақтау жұмысы t = (29+1280) ∙2 мкс=2618 мкс уақытта орындалады.

Әдебиеттер тізімі

1. Бойко В.И., Гуржий А.Н., Жуйков В.Я. и др. Схемотехника электронных устройств. Цифровые устройства.- СПб.: БХВ. – Петербург, 2004. – 512 с.

2. Бойко В.И., Гуржий А.Н., Жуйков В.Я. и др. Схемотехника электронных устройств. Микропроцессоры и микроконтроллеры.- СПб.: БХВ – Петербург, 2004. – 464 с.

3. Калабеков Б.А. Цифровые устройства и микропроцессорные системы. Учебник для техникумов связи.- М.: Горячая линия –Телеком. – 2000. – 336 с.

4. Лебедев О.Н. и др. Изделия электронной техники. Цифровые микросхемы. Микросхемы памяти. ЦАП и АЦП: Справочник.- М.:Радио и связь. – 1994. – 248 с.

5. Лебедев О.Н. Применение микросхем памяти в электронных устройствах: Справочное пособие. – М.: Радио и связь. – 1994. – 216 с.

6. Гольденберг Л.М. и др. Цифровые устройства и микропроцессорные системы. Задачи и упражнения: Учебное пособие. - М.: Радио и связь. – 1992. - 256 с.

7. Цифровая и вычислительная техника: Учебник под ред. Э.В.Евреинова.- М.: Радио и связь. – 1991. - 464 с.

8. Пухальский Г.И. Проектирование микропроцессорных систем. Учебное пособие для вузов.- СПб.: Политехника, 2001.–544 с.

9. Угрюмов Е.П. Цифровая схемотехника.- СПб.: БХВ – Санкт-Петербург, 2000. - 528 с.

10. Калабеков Б.А. Микропроцессоры и их применение в системах передачи и обработки сигналов. – М.: Радио и связь, 1988. – 368 с.

Мазмұны

1 Курстық жұмыс және оны орындауға әдістемелік нұсқаулар

1.1 Курстық жұмысқа тапсырма

1.2 Курстық жұмысты орындауға әдістемелік нұсқаулар

1.2.1 Оперативті есте сақтау құрылғысын (ОЕСҚ) ұйымдастыру

1.2.2 8-разрядты микропроцессор базасында микропроцессорлық құрылғы түрінде ДЖҚ-ны іске асыру

1.2.3 Микропроцессорлық құрылғының тезәрекеттілігін бағалау

Әдебиеттер тізімі