Некоммерческое акционерное общество

АЛМАТИНСКИЙ УНИВЕРСИТЕТ ЭНЕРГЕТИКИ И СВЯЗИ

Кафедра

электроники

ИНТЕГРАЛЬНАЯ И МИКРОПРОЦЕССОРНАЯ СХЕМОТЕХНИКА

Методические указания и задания по

расчетно-графическихработах №1,2 и 3

для студентов специальности5В071600 -

Приборостроение

Алматы 2014

СОСТАВИТЕЛЬ: С.Н.Петрищенко. Интегральная и микропроцессорная схемотехника. Методические указания и задания по расчетно-графическихработах №1,2 и 3 для студентов специальности5В071600 – Приборостроение. - Алматы: АУЭС, 2014. – 15 с.

В методической разработке приводятся три задания на выполнение расчетно-графических работ и методические указания к их выполнению. Первое задание связано с синтезом комбинационных устройств, второе – с синтезом последовательностных устройств на примере создания счетчика с произвольным коэффициентом счета, а третье – с программированием на языке ассемблера 8-ми разрядного микропроцессора.

Ил. 12, табл. 6,библиогр. - 9 назв.

Рецензент: доцент каф.ЭППБашкиров М.В.

Печатается по плану издания некоммерческого акционерного общества «Алматинский университет энергетики и связи» на 2014 г.

© НАО «Алматинский университет энергетики и связи» , 2014 г.

Введение

Расчетно-графические работы по дисциплине «Интегральная и микропроцессорная схемотехника» предназначены для бакалавров специальности «Приборостроение» с целью закрепления и углубления знаний по вопросам синтеза комбинационных устройств, конечных автоматов и программирования на ассемблере 8-и разрядного микропроцессора i8085.

1 Задания к расчетно-графическим работам(РГР) и методические указания к их выполнению

1.1 РГР №1.Синтез комбинационных устройств

Синтезировать комбинационное устройство ( КУ ) в виде логических схем для мозаичного знакогенератора, предназначенного для отображения буквенно-цифровой информации на светодиодном матричном индикаторе с числом элементов 7х5.

Согласно таблицам 1.1. и 1.2 и неполной принципиальной схемы знакогенератора, представленной на рисунке 1.2, необходимо :

- рассчитать рабочую частоту генератора тактовых импульсов ( ГТИ );

- составить таблицу истинности для символа, заданного в таблице1.2;

- найти совершенные дизъюнктивные нормальные формы (СДНФ) для каждого столбца таблицы истинности заданного символа;

- минимизировать полученные СДНФ одним из существующих графических методов (карты Карно или диаграммы Вейча);

- для минимизированных СДНФ построить логические схемы в базисе И-НЕ.

В таблице 1.1 дано соответствие между номером задания и номером, который соответствует положению студента в списочном составе группы в журнале преподавателя.

Таблица 1.1

|

№ студента |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

|

№ задания |

14 |

13 |

12 |

15 |

16 |

17 |

18 |

11 |

19 |

20 |

|

№ студента |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

|

№ задания |

7 |

3 |

2 |

9 |

6 |

10 |

8 |

1 |

5 |

4 |

Примечание -Если в группе более 20 человек, то номера студентов повторяются по циклу.

В таблице 1.2 представлены варианты задания на параметры расчетно-графической работы.

Таблица 1.2

|

№ задания |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

|

R, кОм |

0.39 |

0.51 |

0.82 |

1.0 |

1.1 |

1.2 |

1.3 |

1.5 |

1.6 |

1.7 |

|

С, нФ |

62 |

47 |

30 |

24 |

22 |

20 |

18 |

16 |

15 |

13 |

|

Символ |

F |

2 |

Е |

4 |

P |

6 |

Z |

9 |

А |

Я |

|

№ задания |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

|

R, кОм |

0.3 |

0.4 |

0.5 |

1.25 |

1.3 |

1.45 |

1.35 |

1.55 |

1.75 |

1.8 |

|

С, нФ |

50 |

30 |

40 |

25 |

20 |

10 |

18 |

16 |

15 |

13 |

|

Символ |

3 |

5 |

8 |

7 |

1 |

Н |

L |

0 |

Г |

I |

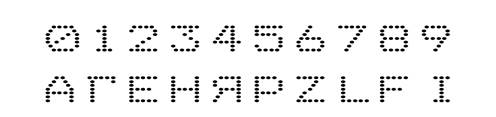

На рисунке 1.1 приведены примеры символов, которые должен высвечивать матричный индикатор, согласно заданному варианту.

Рисунок 1.1-Примеры символов, высвечиваемых матричным индикатором 7х5

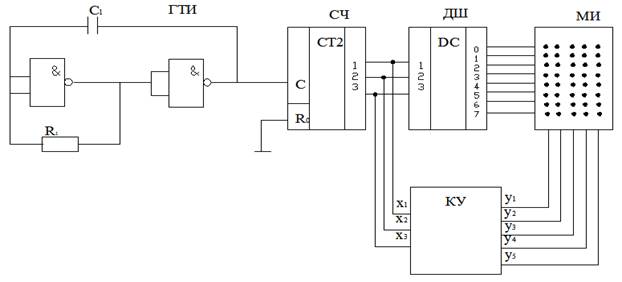

На рисунке 1.2 представлена неполная принципиальная схема знакогенератора, в состав которой входят генератор тактируемых импульсов (ГТИ), двоичный счетчик (СЧ), дешифратор 3 на 8 (ДШ) и матричный индикатор 7 на 5 (МИ).

Рисунок 1.2-Неполная принципиальная схема знакогенератора

1.2Методические указания к выполнению РГР №1

Проиллюстрируем решение задачи на примере синтеза комбинационного устройства для высвечивания на индикаторе символа К.

Согласно заданному варианту рабочая частота генератора тактовых импульсов рассчитывается по следующей формуле:

![]()

Находим форму для символаК и составляем для него таблицу истинности, представленную в таблице 1.3.

Т а б л и ц а 1.3

|

X3 |

X2 |

X1 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

1 |

Ф |

Ф |

Ф |

Ф |

Ф |

Запишем совершенные дизъюнктивные нормальные формы (СДНФ) столбцов таблицы истинности символаК:

![]() ;

;

![]() ;

;

![]() ;

;

![]() ;

;

![]() .

.

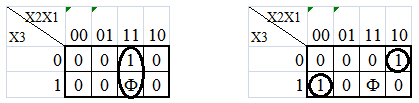

Минимизируем совершенные дизъюнктивные нормальные формы символаК методом карт Карно, как показано на рисунке 1.3.

Минимизации подлежат четыре логических выражения Y2, Y3, Y4, и Y5, каждому из которых будет соответствовать своя карта Карно на восемь клеток, поскольку 2n = 23 = 8, где n – число входных переменных. Объединяем клетки, в которых логическая функция принимает единичное или факультативное значение. При объединении двух клеток исчезает та переменная, которая в зоне объединения принимает два противоположных значения 0 и 1.

![]()

![]()

Рисунок 1.3 – Карты Карно для минимизации логических функций

Учитывая, что для обеспечения питающим напряжением светодиодов матричного индикатора необходимо подать на выводы столбцов светодиодной матрицы сигнал, инверсный к сигналу строк, и, применяя правило де Моргана, запишем Y1-Y5 в базисе И-НЕ:

![]()

![]()

![]()

![]()

![]() .

.

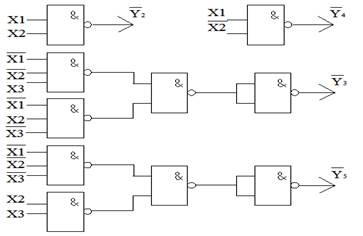

На основании полученных логических выражений строим логические схемы, представленные на рисунке 1.4.

Рисунок 1.4-Логические схемы КУ для матричного знакогенератора

1.3РГР № 2. Синтезпоследовательностных устройств

Синтезировать последовательностное устройство в виде синхронного счетчика с заданным коэффициентом счета на основе триггеров заданного типа. Построить схему формирования сигнала аварийной тревоги.

Параметры счетчика представлены в таблице 2.1.Номер варианта определяется номером студента в списке группы.

Таблица 2.1

|

Вариант |

Тип счетчика |

Тип триггера |

Ксч |

|

0 |

суммирующий |

JK– триггер |

5 |

|

1 |

вычитающий |

JK– триггер |

6 |

|

2 |

суммирующий |

JK– триггер |

7 |

|

3 |

вычитающий |

Т– триггер |

6 |

|

4 |

суммирующий |

T - триггер |

7 |

|

5 |

вычитающий |

T - триггер |

5 |

|

6 |

суммирующий |

D - триггер |

5 |

|

7 |

вычитающий |

D - триггер |

3 |

|

8 |

суммирующий |

D - триггер |

6 |

|

9 |

вычитающий |

D - триггер |

7 |

|

11 |

суммирующий |

JK – триггер |

6 |

|

12 |

вычитающий |

JK – триггер |

5 |

|

13 |

суммирующий |

JK – триггер |

7 |

|

14 |

вычитающий |

Т – триггер |

5 |

|

15 |

суммирующий |

T - триггер |

6 |

|

16 |

вычитающий |

T - триггер |

7 |

|

17 |

суммирующий |

D - триггер |

7 |

|

18 |

вычитающий |

D - триггер |

5 |

|

19 |

суммирующий |

D - триггер |

3 |

|

20 |

вычитающий |

D - триггер |

6 |

Согласно варианту таблицы 2.1 необходимо:

-выбрать тип счетчика, триггера и коэффициент счета;

-определить количество используемых триггеров и число избыточных состояний счетчика ;

-построить граф переходов синтезируемого счетчика;

- на основании графа и одной из управляющих таблиц рисунка 2.1, согласно заданному варианту, построить таблицу переходов счетчика;

- минимизировать полученные функции возбуждения;

- построить схему синтезируемого счетчика;

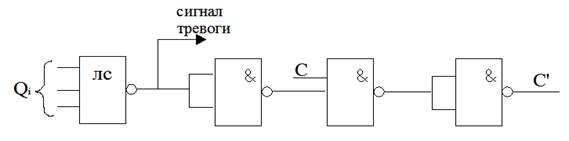

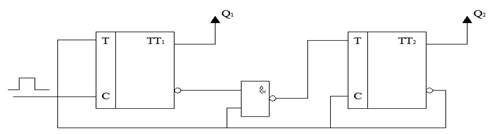

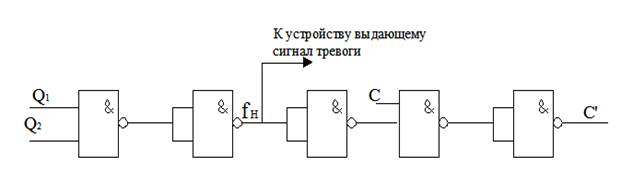

- определить функцию неиспользуемых состояний, реализовать ее в базисе И-НЕ в виде логической схемы для подстановки в схему запуска сигнала аварийной тревоги и блокировки синхроимпульса, представленной на рисунке 2.2.

|

Qt |

Qt+1 |

J |

K |

Qt |

Qt+1 |

D |

Qt |

Qt+1 |

T |

||

|

0 |

0 |

0 |

* |

0 |

0 |

0 |

0 |

0 |

0 |

||

|

0 |

1 |

1 |

* |

0 |

1 |

1 |

0 |

1 |

1 |

||

|

1 |

0 |

* |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

||

|

1 |

1 |

* |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

Рисунок 2.1- Управляющие таблицы для JK, Dи Т триггеров

Рисунок 2.2– Неполная схема формирования блокирующего сигнала синхронизации и сигнала аварийной тревоги

1.4 Методические указания к выполнению РГР №2

Рассмотрим порядок синтеза двоичного счетчика на примере суммирующего счетчика, построенного на Т-триггерах с коэффициентом счета, равным трем.

1.4.1Синхронный счетчик с Ксч=3 строится на основе двоичного счетчика, состоящего из двух Т-триггеров, так как

n=]log2Ксч[=]log23[=1.58≈2,

где n – число триггеров в счетчике;

]log2Ксч[ - двоичный логарифм заданного коэффициента пересчета Ксч, округленный до большого целого числа.

1.4.2Число избыточных состояний счетчика равно

М=2n–Ксч=22– 3=1,

где 2n – число устойчивых состояний двоичного счетчика.

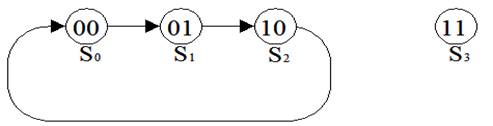

1.4.3Граф переходов данного счетчика будет иметь вид, как показано на рисунке 2.3, где S0, S1, S2 – внутренние состояния счетчика,S3 – избыточное состояние счетчика.

Рисунок 2.3 – Граф переходов счетчика с Ксч = 3

1.4.4На основании управляющей таблицы для Т – триггера и графа переходов счетчика, составляем таблицу переключений счетчика, представленной в таблице 2.2.

Таблица2.2

|

Q2t |

Q1t |

Q2t+1 |

Q1t+1 |

T2 |

T1 |

|

0 |

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

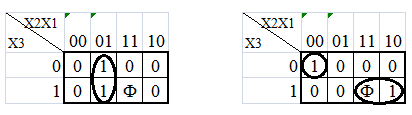

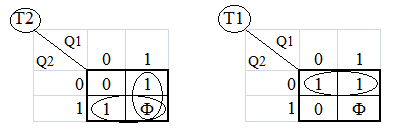

1.4.5Сигналы, присутствующие на управляющих входах триггеров, т.е. функции возбуждения, определяются путем минимизации с помощью карт Карно.

![]() T1=

T1=![]() .

.

Рисунок 2.4 – Карты Карно для минимизации функций возбуждения

1.4.6На основе полученных минимизированных логических функций Т2 и Т1 строим схему реализации синтезируемого счетчика, показанную на рисунке 2.5.

Рисунок 2.5- Схема суммирующего двоичного счетчика с Ксч=3

1.4.7Для реализации схемы блокирующего сигнала синхронизации и сигнала аварийной тревоги определяем по карте Карно функцию неиспользуемых состояний

![]() ,

,

где ![]() - получена путем охвата клетки со знаком Ф

(факультативное или неиспользуемое состояние).

- получена путем охвата клетки со знаком Ф

(факультативное или неиспользуемое состояние).

Выражение, описывающее новый сигнал синхронизации, будет иметь вид

![]() .

.

Значит,

при ![]() синхроимпульсы будут отсутствовать (

синхроимпульсы будут отсутствовать (![]() , пока счетчик не выйдет из запрещенного состояния.

, пока счетчик не выйдет из запрещенного состояния.

Схема, формирующая сигнал аварийной тревоги и сигнал блокировки синхроимпульса, будет иметь вид, как показано на рисунке 2.6.

Рисунок 2.6 – Схема аварийной тревоги

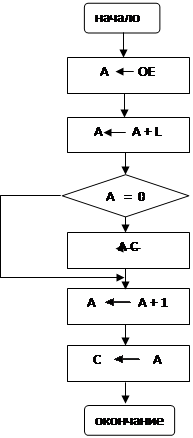

1.5 РГР № 3. Анализ фрагмента ассемблерной программы 8–ми разрядного микропроцессора i8085

Варианты индивидуальных заданий приведены в таблице 3.1 и определяются по предпоследней (Nпред) и последней (Nпосл) цифрам номера студенческого билета.

В таблице представлены:

- номер ячейки, которая соответствует первой команде фрагмента программы;

- частота генератора тактируемых импульсов в МГц;

- фрагменты ассемблерной программы.

Необходимо:

- составить блок-схему алгоритма фрагмента программы, в котором определен порядок выполняемых действий;

- проанализировать фрагменты программы и оформить в виде таблицы 3.1, согласно приведенному ниже примеру. В этой таблице определить выполняемую операцию, ее результат и число тактов, затрачиваемых на ее выполнение;

- рассчитать время выполнения фрагмента программы, исходя из заданной тактовой частоты и числа тактов фрагмента.

Таблица 3.1

|

Nпред |

0 |

1 |

2 |

3 |

4 |

|

Номер ячейки |

0013 |

0101 |

0006 |

000А |

00ВС |

|

|

2,0 |

2,1 |

2,2 |

2,3 |

2,4 |

|

Nпосл |

0 |

1 |

2 |

3 |

4 |

|

Фрагменты программ |

MOV C,A2 ADI 00 JZ 1C00 LDA 1211 DCR A |

JMP 0901 MOV A, A2 LDA 1211 SUB A HLT |

MVI A, AA ANA 26 ORA C ANI 82 RRC |

MVI M, 01 LDA 1211 MOV B, M XRA B RLC |

MOV M, A INR M INR L MVI M, 10 MOVB, M LDA EDBC ORA B |

Продолжение таблицы 3.1

|

Nпред |

5 |

6 |

7 |

8 |

9 |

|

Номер ячейки |

0000 |

0000 |

0000 |

0000 |

0103 |

|

|

2,5 |

2,6 |

2,7 |

2,8 |

2,9 |

|

Nпосл |

0 |

1 |

2 |

3 |

4 |

|

Фрагменты программ |

MVI A, 05 MVI B, 00 INR B SUB B JNZ 0400 MOV A, B OUT 05 |

ANI 00 INR A CPI FF JNZ 0200 HLT |

MVI A, EE SUI 11 JM 0200 NOP NOP NOP OUT 05 |

MVI A, 0A MOV C, A NOP NOP DCR A JNZ 0300 MOV A, C |

IN 06 MVI B, 64 MVI C, FA DCR C JNZ 0901 DCR B JNZ 0701 OUT 05 |

1.6 Методические указания к выполнению РГР №3

Рассмотрим порядок выполнения задания на следующем примере.

Допустим задан фрагмент программы, представленный на рисунке 3.1. Из фрагмента программы видно, что начальный адрес размещения первой команды в памяти равен 0005. Последующие адреса ячеек памяти определяются исходя из количества тактов, за которые выполняется команда.

Например, команда MVIA,0E имеет непосредственную адресацию и выполняется за два такта, поэтому адрес следующей команды 0007.

0005 MVIA,OE

0007 ADD L

0008 JNZ OC00

000BMOV A, C

000CINR A

000DMOVC, A

Рисунок 3.1 – Фрагмент программы

Из рисунка 3.2 мы видим, что некоторое 8-ми разрядное число OE, необходимо отправить в аккумулятор и сложить с числом, находящимся в регистре L. Далее, если результат не будет равен нулю, то его надо отправить в ячейку памяти под номером 0C00. В противном случае, вступают в действие три последующие команды: содержимое регистра С отправляется в аккумулятор, увеличивается на1 и возвращается в регистр С.

Блок-схема алгоритма этого фрагмента будет иметь следующий вид

|

нет

да

Рисунок 3.2 - Блок-схемаалгоритма заданного фрагмента

В таблицу 3.1 заносим фрагмент программы с более подробным его анализом.

Таблица 3.1

|

Адрес ячейки |

Содержимое (мнемокоды и операнды) |

Выполняемая операция |

Результат операции |

Число тактов |

|

0005 0006 0007 0008 0009 000A 000B 000C 000D |

MVI A OE ADD L JNZ 0C 00 MOV A, C INR A MOV C, A |

(A)

(A)

Переход к 000С, если (A) (A)

(A)

|

(A) = 00001110 (A) = 11111010 Переход к 000C Пропуск (A) = 11111011 (C) = (A) = 11111011 |

7 4 10 5 5 5 |

Всего тактов N = 31 (команда MOVA, C не выполняется), время выполнения t = 15,5 мкс, содержимое аккумулятора после выполнения программы (A) = FB.

Список литературы

1. Угрюмов Е.П. Цифровая схемотехника.- СПб.: БХВ – Санкт-Петербург, 2007. - 788 с.

2. Бабич Н.П. и др. Компьютерная схемотехника. Методы построения и проектирования. Учебное пособие. – К.: «МК-Пресс», 2004.-576 с.

3.Бойко В.И. и др. Схемотехника электронных устройств. Цифровые устройства.- СПб.: БХВ – Петербург, 2004. – 512 с.

4. Калабеков Б.А. Цифровые устройства и микропроцессорные системы. Учебник для техникумов связи.- М.: Горячая линия –Телеком, 2007. – 336 с.

5. Гольденберг Л.М. и др. Цифровые устройства и микропроцессорные системы. Задачи и упражнения: Учебное пособие. - М.: Радио и связь,1992 . - 256 с.

6. Цифровая и вычислительная техника: Учебник под ред. Э.В.Евреинова.- М.: Радио и связь, 1991. - 464 с.

7.Петрищенко С.Н. Цифровые устройства и микропроцессоры. Конспект лекций для студентов специальности 050719 – Радиотехника, электроника и телекоммуникации дистанционной формы обучения. – Алматы: АИЭС, 2006. – 36 с.

8. Петрищенко С.Н. Цифровые устройства и микропроцессоры. Конспект лекций для бакалавров специальности 5В100200 – Системы информационной безопасности – Алматы: АУЭС, 2013. – 49 с.

Содержание

Введение3

1 Задания к расчетно-графическим работам и методические указания к их выполнению

1.1 РГР №15

1.2 Методические указания к выполнениюРГР №1

1.3 РГР №2 7

1.4 Методические указания к выполнению №2 8

1.5 РГР № 3

1.6 Методические указания к выполнению РГР №3

Список литературы

Сводный план 2014 г., поз.209

Святослав Николаевич Петрищенко

ИНТЕГРАЛЬНАЯ И МИКРОПРОЦЕССОРНАЯ СХЕМОТЕХНИКА

Методические указания и задания по расчетно-графическихработах

№1,2 и 3

для студентов специальности5В071600 -

Приборостроение

Редактор

Н.М.Голева

Специалист по стандартизации Н.К.Молдабекова

Подписано в печать ________

Формат 60x84 1/16

Тираж 100 экз.

Бумага типографская №1

Объем 9,0 из.л.

Заказ 450 тн.

Копировально-множительное

бюро

некоммерческого

акционерного общества

«Алматинский

университет энергетики и связи»

050013,

Алматы, Байтурсынова, 126