Некоммерческое акционерное общество

АЛМАТИНСКИЙ УНИВЕРСИТЕТ ЭНЕРГЕТИКИ И СВЯЗИ

Кафедра Инженерной кибернетики

ПРОГРАМНЫЕ СРЕДСТВА УПРАВЛЕНИЯ

НА МИКРОПРОЦЕССОРНЫХ

КОНТРОЛЛЕРАХ В ЗАДАЧАХ АВТОМАТИЗАЦИИ

Конспект лекций

6М070200 – Автоматизация и управление

Алматы 2013

СОСТАВИТЕЛЬ: А.А.Копесбаева. Программные средства управления на микропроцессорных контроллерах в задачах автоматизации. Конспект лекций для магистрантов специальности 6М070200 – Автоматизация и управление - Алматы: АУЭС, 2013 - 50 с.

Настоящие конспекты лекций включают в себя краткое содержание теоретического материала по дисциплине «Программные средства управления на микропроцессорных контроллерах в задачах автоматизации» в рамках дисциплин по выбору для специальности «Автоматизация и управление».

Конспекты лекций предназначены для магистрантов специальности 6М070200 – Автоматизация и управление.

Ил. 12, прил. 6, библиогр. – 14 назв.

Рецензент: доцент Башкиров М.В.

Печатается по плану издания некоммерческого акционерного общества «Алматинский университет энергетики и связи» на 2013 г.

©НАО «Алматинский университет энергетики и связи», 2013 г.

Содержание

1.Лекция №1. Введение. Основные понятия и характеристики архитектуры

2. Лекция №2. Этапы развития архитектуры универсальных микропроцессоров. Структура 32-разрядного универсального микропроцессора

3. Лекция №3. Регистровая структура универсального микропроцессора

4. Лекция №4. Интерфейсы современных микроконтроллеров управления в задачах автоматизации

5. Лекция №5. Интерфейсы микроконтроллеров (продолжение) - аналоговые интерфейсы

6.Лекция №6. Программы сопровождения проектов программирования микроконтроллеров. Языки программирования микроконтроллеров

7. Лекция №7. Основные направления развития архитектуры универсальных микропроцессоров

8. Лекция №8. Перспективные микроконтроллеры управления Texas Instruments

1 Лекция № 1. Введение. Основные понятия и характеристики архитектуры

Цель лекции: анализ понятия архитектуры микропроцессоров, изучение основных отличительных черт микропроцессоров различных типов архитектуры.

1.1 Введение

В предыдущих дисциплинах по микропроцессорной техники были использованы понятия и термины, которые требуют уточнений и определений с точки зрения современного состояния микропроцессорной техники. Разберем эти понятия в том порядке, в котором мы изучали их по дисциплинам. Прежде всего, микропроцессор является цифровым элементом системы автоматизации. Микропроцессор входит в состав почти всех элементов и средств системы автоматизации. Вместе с тем появились и другие понятия сопровождающие эволюцию развития микропроцессорной техники. Разберем их классические определения, изложенные в литературе [1-3]. Определения: Микроконтро́ллер (англ. Micro Controller Unit, MCU) — микросхема, предназначенная для управления электронными устройствами.

Микропроцессор (МП) - это программно управляемое устройство, которое предназначено для обработки цифровой информации и управления процессом этой обработки и выполнено в виде одной или нескольких больших интегральных схем (БИС).

Микропроцессорная система (МПС) представляет собой функционально законченное изделие, состоящее из одного или нескольких устройств, основу которой составляет микропроцессор.

Архитектура МП - это совокупность программно-аппаратных свойств, предоставляемых пользователю. Сюда относятся система команд, типы и форматы обрабатываемых данных, режимы адресации, количество и распределение регистров, принципы взаимодействия с оперативной памятью и внешними устройствами (характеристики системы прерываний, прямой доступ к памяти и т. д.).

1.2 Классификация микропроцессоров по архитектуре

В дисциплине «Микропроцессорные комплексы в системах управления» была предложена классификация микропроцессорных систем по их функциональным особенностям и месту применения в системах автоматизации. Однако, в литературе чаще встречается классификация микропроцессорных устройств по архитектуре. Это и понятно, для специалистов по проектированию электронной техники, радиоэлектронике и телекоммуникациям микропроцессорное устройство это отдельная микросхема. Для специалиста по автоматизации микропроцессорное устройство это элемент системы автоматизации, которое выполняется как законченный аппарат управления (свободно-программируемый логический контроллер) или является средством проектирования других устройств автоматизации (микроконтроллер или микропроцессорная интегральная схема). В дисциплине «Микропроцессорные комплексы в системах управления» подробно изучены этапы проектирования систем автоматизации на базе СПЛК, в данном предмете будут рассматриваться вопросы проектирования систем автоматизации на базе микроконтроллеров и микропроцессорных интегральных схем. Приведем классификацию микропроцессоров по архитектуре (см. рисунок 1).

Рисунок 1.1 – Классификация микропроцессоров по архитектуре

Универсальные микропроцессоры предназначены для решения задач цифровой обработки различного типа информации от инженерных расчетов до работы с базами данных, не связанных жесткими ограничениями на время выполнения задания. Этот класс микро процессоров наиболее широко известен. К нему относятся такие известные микропроцессоры, как МП ряда Pentium фирмы Intel и МП семейства Athlon фирмы AMD.

Характеристики универсальных микропроцессоров: разрядность; виды и форматы обрабатываемых данных; система команд, режимы адресации операндов; емкость прямоадресуемой оперативной памяти: определяется разрядностью шины адреса; частота внешней синхронизации; производительность. Разделение универсальных микропроцессоров по архитектуре RISC и CISC связано с наиболее определяющей характеристикой архитектуры количеством и составом команд (инструкций). Определения RISC-архитектура с сокращенным списком команд (англ. Reduced Instruction Set Computer), CISC-микропроцессоры с расширенным списком команд (Completed Instruction Set Computing).

Однокристальные микроконтроллеры (ОМК или просто МК) предназначенные для использования в системах промышленной и бытовой автоматики получили свое наименование по технологии изготовления интегральной микросхемы. Микроконтроллеры выполнялись на одном кристалле и представляли собой законченное цифровое устройство с универсальным или специализированным назначением. Особый класс контроллеров процессоры цифровой обработки сигналов ЦОС, или цифровые сигнальные процессоры. В альтернативу однокристальным микропроцессорам существовали секционированные микропроцессоры, которые отличались технологией изготовления в несколько секций, каждая из которых представляла собой отдельное вычислительное устройство. Современные микропроцессорные устройства выполняют несколько операций одновременно, даже если они являются однокристальными, поэтому секционированных микропроцессоров практически нет. Остановимся подробнее на каждом из разновидностей архитектур микропроцессоров.

1.3 Структура микропроцессора с RISC-архитектурой

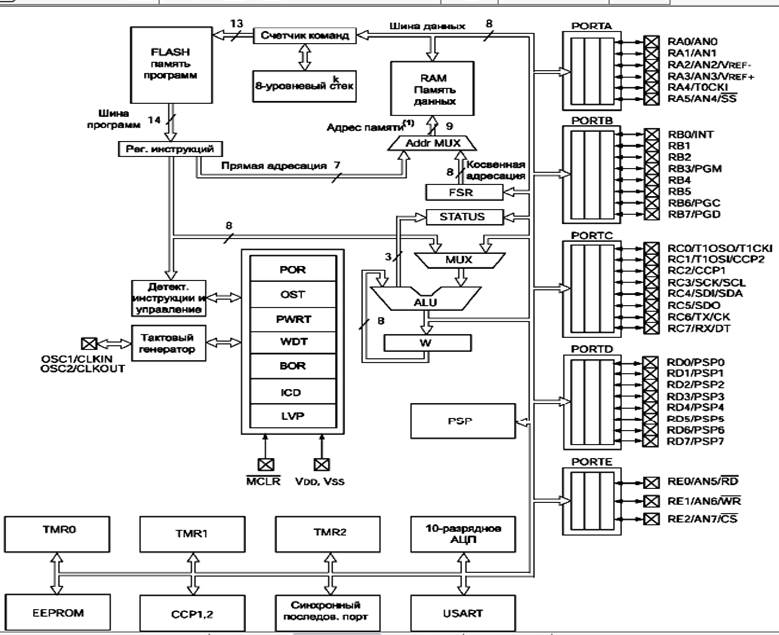

Рисунок 1.2 - Структура микропроцессора с RISC-архитектурой

Отличительные особенности RISC архитектуры однокристальных микроконтроллеров:

- физическое и логическое разделение памяти команд и памяти данных (гарвардская архитектура), в то время как в классической неймановской архитектуре программы и данные находятся в общем запоминающем устройстве и имеют одинаковый механизм доступа;

- упрощенная и ориентированная на задачи управления система команд: в МК, как правило, отсутствуют средства обработки данных с плавающей точкой, но в то же время в систему команд входят команды, ориентированные на эффективную работу с датчиками и исполнительными устройствами, например, команды обработки битовой информации;

- простейшие режимы адресации операндов; в фон-неймановской архитектуре огромное количество способов определения операндов, соответственно этому множество способов адресации и разновидностей команд, в Гарвардской архитектуре благодаря тому, что есть разделение памяти данных и команд адресация возможна только прямая и косвенная.

1.4 Другие разновидности микропроцессоров

Секционированные микропроцессоры (другие названия: микропрограммируемые и разрядно-модульные) - это микропроцессоры, предназначенные для построения специализированных процессоров. Они представляют собой микропроцессорные секции относительно небольшой (от 2 до 16) разрядности с пользовательским доступом к микропрограммному уровню управления и средствами для объединения нескольких секций.

Процессоры цифровой обработки сигналов, или цифровые сигнальные процессоры представляют собой бурно развивающийся класс микропроцессоров, предназначенных для решения задач цифровой обработки сигналов - обработки звуковых сигналов, изображений, распознавания образов и т.д.

Электрические характеристики МП безусловно имеют значения, так как каждый из поколений микроконтроллеров претендует на универсальность применения своих микросхем, пользователь должен обратить внимание на следующие электрические характеристики микропроцессоров:

- Обеспечение требований к синхронизации - максимальная частота и стабильность номинальной частоты.

- Количество и номиналы источников питания, требования к их стабильности безусловно определяют стабильность программного и аппаратного обеспечения микропроцессора. Номиналы источников питания за последние 10 лет снизились от 15 вольт до 1 вольта. Несомненно, этот фактор значительно повлиял на показатели мощности рассеяния и уровни сигналов логического нуля и логической единицы, которые связаны с номиналами источников питания.

- Тип корпуса - позволяет оценить пригодность схемы для работы в тех или иных условиях, а также возможность использования новой интегральной схемы в качестве замены существующей на плате.

- В эксплуатационной характеристике - температура окружающей среды, при которой может работать схема, выделяют два диапазона: коммерческий (0 0С … +700С) и расширенный (-40 0С … +85 0С).

- Помехоустойчивость - определяет способность схемы выполнять свои функции при наличии помех.

- Нагрузочная способность, или коэффициент разветвления по выходу, определяется числом схем этой же серии, входы которых могут быть присоединены к выходу данной схемы без нарушения ее работоспособности.

- Надежность - это способность схемы сохранять свой уровень качества функционирования при установленных условиях за установленный период времени.

- Характеристики технологического процесса. Основной показатель здесь - разрешающая способность процесса. В настоящее время она составляет 32 нм, то есть около 30 тыс. линий на 1 мм.

2 Лекция № 2. Этапы развития архитектуры универсальных микропроцессоров. Структура 32-разрядного универсального микропроцессора

Цель лекции: обзор этапов развития архитектуры универсальных микропроцессоров, а также знакомство с основными чертами архитектуры IA-32.

2.1 Этапы развития архитектуры универсальных микропроцессоров

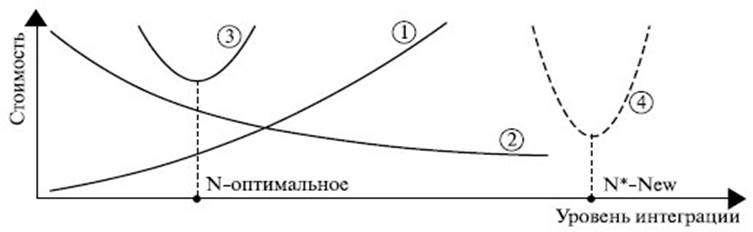

История развития микропроцессорной техники началась с появления идеи архитектуры цифрового вычислительного устройства в 40-х годах 20-го века. Доминирующей архитектурой была признана фон-неймановская, согласно которой долгие годы происходило развитие микропроцессоров фирмы Intel. В 1965 году Гордон Мур сформулировал гипотезу, известную в настоящее время как «закон Мура», согласно которой каждые 1,5-2 года число транзисторов в расчете на одну интегральную схему будет удваиваться. Это обеспечивается непрерывным совершенствованием технологических процессов производства микросхем. Первый же патент на однокристальную микро-ЭВМ был выдан в 1971 году инженерам М. Кочрену и Г. Буну, сотрудникам Texas Instruments. На рисунке 3 представлен график затрат на производство микропроцессорной системы.

Здесь:

1) затраты на изготовление БИС (чем больше степень интеграции элементов на кристалле, тем дороже обходится производство схемы);

2) затраты на сборку и наладку микропроцессорной системы (с увеличением функциональных возможностей МП потребуется меньше схем для создания МПС);

Рисунок 2.1 - Затраты на производство микропроцессорной системы

3) общая стоимость микропроцессорной системы, которая складывается из затрат (1) и (2). Она имеет некоторое оптимальное значение для данного уровня развития технологии;

4) переход на новую технологию (оптимальным будет уже другое количество элементов на кристалле, а общая стоимость изделия снижается).

Наиболее развитая в технологическом отношении фирма Intel выделяет следющие этапы развития архитектуры универсальных микропроцессоров:

1) Первый микропроцессор был разработан фирмой Intel в 1971 году. Он получил название I-4004, имел 4-разрядную структуру и был ориентирован на использование в калькуляторах. Впоследствии этой же фирмой был выпущен еще один 4-разрядный микропроцессор - I-4040.

2) В 1972 году на рынке появился 8-разрядный МП I-8008, а вслед за ним, в 1974 году,- I-8080. Последний микропроцессор сыграл значительную роль в развитии микропроцессорной техники. Во многом он заложил основы архитектуры для всех последующих поколений микропроцессоров. Он имеет раздельные 8-разрядную шину данных и 16-разрядную шину адреса, возможность подключения памяти емкостью до 64 Кбайт и до256 внешних устройств.

3) Очередным крупным шагом в развитии микропроцессорной техники стало появление в 1978 году 16-разрядных универсальных микропроцессоров. Здесь прежде всего следует выделить микропроцессор I-8086, выпускавшийся советской электронной промышленностью в составе семейства К1810. Эти микропроцессоры, заложившие основы архитектуры x86, использовались при проводстве первых персональных ЭВМ.

4) Появившийся вслед за этим в 1982 году микропроцессор i286 явился переходной ступенью к 32-разрядным универсальным микропроцессорам. В процессоре i286 было реализовано два режима работы - защищенный и реальный. В реальном режиме работы процессор был полностью совместим с выпускавшимися ранее 16-разрядными микропроцессорами с архитектурой x86. В формировании адреса участвовали только 20 линий, поэтому максимальная емкость адресуемой памяти в этом режиме осталась прежней - 1 Мбайт. В защищенном режиме процессор мог адресовать до 1 Гбайт виртуальной памяти. Шина адреса увеличена до 24 бит, поэтому емкость адресуемой памяти составляла 16 Мбайт. Для защиты от несанкционированного доступа к программам и данным и выполнения привилегированных команд, которые могут кардинально изменить состояние всей системы, в процессоре i286 была введена защита по привилегиям. С этой целью микропроцессор поддерживал 4 уровня привилегий. Для выполнения операций над числами с плавающей точкой была разработана отдельная БИС - математический сопроцессор 80287.

5) В 1985 году был выпущен 32-разрядный универсальный микропроцессор i386 - первый полноценный представитель архитектуры IA-32 (Intel Architecture-32). Развитие этой архитектуры продолжалось вплоть до последних моделей микропроцессора Pentium 4. Данную архитектуру отличает ряд изменений, некоторые из которых имеют чисто количественное значение, а другие носят принципиальный характер. Главным внешним отличием является увеличение разрядности шины данных и шины адреса до 32 бит. Это, в свою очередь, связано с изменениями в разрядности внутренних элементов микропроцессора. Большие качественные изменения произошли на уровне работы микропроцессора в защищенном режиме, который был существенно развит по сравнению с i286.

6) К основным нововведениям микропроцессора i486, выпущенного в 1989 году, относятся два, которые связаны с расширившимися технологическими возможностями. Это размещение непосредственно на кристалле БИС двух важных блоков, которые раньше выполнялись в виде отдельных микросхем: кэш-памяти и блока процессора обработки чисел с плавающей точкой (floating point unit - FPU). Кэш-память имела объем 8 Кбайт и педазначалась для хранения программ и данных.

7)Основным нововведением разработанного в 1997 году микропроцессора Pentium MMX стал блок, обеспечивавший новую схему обработки целочисленной информации - SIMD (Single Instruction - Multiple Data: одна команда - множество данных). До этого обработка велась по классической схеме SISD: каждая команда выполняла действия над своей парой операндов. Введение SIMD-операций позволило обрабатывать одновременно несколько операндов с использованием одной команды, что дало возможность существенно поднять производительность микропроцессора на тех задачах, где над большими массивами однородной информации выполнялись одинаковые операции, например, в мультимедийных приложениях. Появление таких возможностей потребовало введения в систему команд 57 новых инструкций, но егистровая структура микропроцессора не изменилась.

8) В 2001 году фирмой Intel был выпущен микропроцессор Itanium, положивший начало новой 64-разрядной архитектуре - IA-64, которая сменила архитектуру 32-разрядных микропроцессоров IA-32, господствовавшую на протяжении более 15 лет.

2.2 Структура 32-разрядного универсального микропроцессора

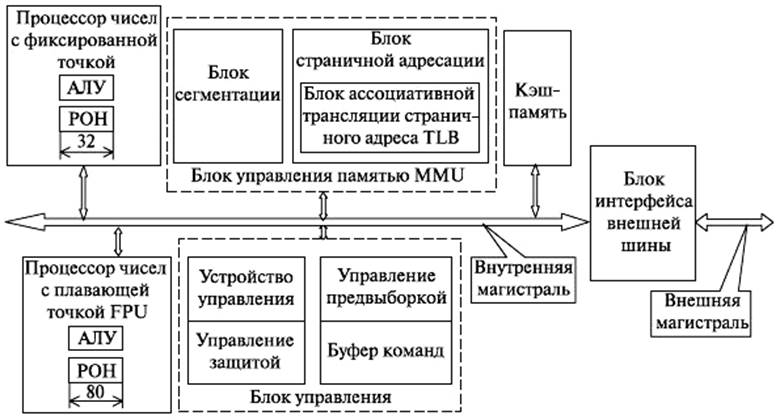

Рассмотрение архитектуры IA-32 начнем с микропроцессора i486. В нем впервые появились те блоки, которых не было на кристалле первого 32-разрядного микропроцессора i386, - кэш-память и процессор обработки чисел с плавающей точкой. Именно его архитектуру можно рассматривать как базовую для IA-32. Структура микропроцессора i486 представлена на рисунке 2.2.

Рисунок 2.2 - Структура универсального микропроцессора

Процессор обработки чисел с фиксированной точкой содержит 32-раз- рядное АЛУ и блок регистров общего назначения. АЛУ предназначено для обработки двоичных чисел длиной 1, 2 или 4 байта без знака или со знаком, а также двоично-десятичных чисел, не превышающих 99. Двоичные числа со знаком представляются в дополнительном коде. Блок регистров общего назначения содержит восемь 32-разрядных регистров, часть из которых допускает 16- и 8-разрядное обращение.

Процессор обработки чисел с плавающей точкой состоит из 80-разряд- ного АЛУ, блока из восьми 80-разрядных регистров общего назначения, а также управляющих регистров. Главным образом он предназначен для обработки чисел с плавающей точкой, но также используется для обработки целых чисел со знаком длиной 8 байт и двоично-десятичных чисел величиной от 100 до 99…9 (18 цифр). На первых этапах развития SIMD-обработки регистры FPU использовались для хранения операндов, представленных в новых форматах.

Блок управления памятью (Memory Management Unit - MMU) состоит из двух основных блоков в соответствии с организацией памяти. В общем случае память в микропроцессоре делится на сегменты, которые, в свою очередь, делятся на страницы. В соответствии с этим, MMU содержит блок сегментации (или блок сегментного преобразования адреса) и блок страничного преобразования, в состав которого входит так называемый буфер ассоциативной трансляции адресов страниц (TLB).

Кэш-память представляет собой промежуточную ступень между оперативной памятью и регистрами микропроцессора и предназначена для хранения наиболее часто используемой информации.

В состав блока управления входят:

- собственно устройство управления, то есть та классическая схема, которая под действием кода команды вырабатывает набор управляющих сигналов, поступающих на разные узлы, как самого микропроцессора, так и на блок интерфейса внешней шины;

- управление защитой памяти: обеспечивает аппаратную защиту программ и данных при управлении памятью и по привилегиям;

- блок управления предвыборкой команд: реализует опережающее заполнение буфера команд, представляющего собой некоторую буферную память. Буфер команд имеет емкость 32 байта и заполняется командами из следующих ячеек памяти команд по мере своего освобождения. Этим обеспечивается ускорение обработки микропроцессором следующей команды. Данный блок подвергался, пожалуй, наиболее существенным переработкам по мере развития архитектуры IA-32 - причина в широком последующем использовании конвейерной организации работы МП и связанной с этим необходимости постоянного совершенствования блока предсказания адреса следующей команды.

Блок интерфейса внешней шины осуществляет электрическое согласование параметров внутренней магистрали с сигналами внешних магистралей, формирование необходимых сигналов на внешнюю магистраль и прием сигналов извне.

Особый интерес представляют три режима работы микропроцессора: реальный, защищенный и режим виртуального МП i8086. В реальном режиме обеспечивается совместимость на уровне объектных кодов с микропроцессором i8086 и микропроцессором i286, работающем в реальном режиме. В этом режиме архитектура 32-разрядного микропроцессора почти полностью идентична архитектуре 16-разрядного МП. Для программиста же он вообще представляется как МП i8086, выполняющий написанные программы с большей скоростью и обладающий расширенной системой команд и регистрами. Благодаря этим качествам фирма Intel сохранила прежних клиентов, которые хотели модернизировать свои системы, не отказываясь от имевшегося задела в области программного обеспечения, и привлекла тех, кому изначально требовалась высокая скорость обработки информации.

Одно из основных ограничений реального режима было связано с предельной емкостью адресуемой памяти, равной 1 Мбайт. От него свободен защищенный режим, позволяющий воспользоваться всеми преимуществами архитектуры нового МП. Размер адресного пространства в этом случае увеличивается до 4 Гбайт, а общий объем поддерживаемого адресного пространства - до 64 терабайт (1 Тбайт = 240 байт). МП, работающие в защищенном режиме, обладают более высоким быстродействием и возможностями организации истинной многозадачности.

Наконец, режим виртуального МП открывает возможность одновременного исполнения программ, написанных для МП i8086, i286 и i386.

Поскольку емкость памяти, адресуемой микропроцессором, не ограничена значением 1 Мбайт, этот режим позволяет формировать несколько виртуальных сред i8086.

2 Лекция № 3. Регистровая структура универсального микропроцессора

Цель лекции: рассмотреть состав, назначение и особенности использования различных групп регистров, входящих в состав универсального микропроцессора.

3.1 Регистровая структура микроконтроллеров Гарвардской архитектуры

Регистры - это внутренняя память процессора. Каждый из регистров служит своего рода черновиком, используя который процессор выполняет расчеты и сохраняет промежуточные результаты. У каждого регистра есть определенное назначение. Предположим, что у процессора возникла необходимость сложить два числа. Для этого ему нужно считать из памяти первое слагаемое, затем - второе слагаемое, сложить их и, если необходимо, отправить результат снова в оперативную память. Стало быть, процессору необходимо где-то хранить первое и второе слагаемое, а затем и результат. Для этого служит внутренняя ячейка самого процессора, называемая сумматор, или аккумулятор. Кроме того, процессору необходимо знать, из какой ячейки оперативной памяти считывать очередную команду. Об этом ему сообщает содержимое его внутренней ячейки , называемой счетчиком команд. Сама команда после извлечения из оперативной памяти помещается в ячейку - регистр команд. Полученный после выполнения команды результат может быть переписан из регистра в ячейку ОЗУ.

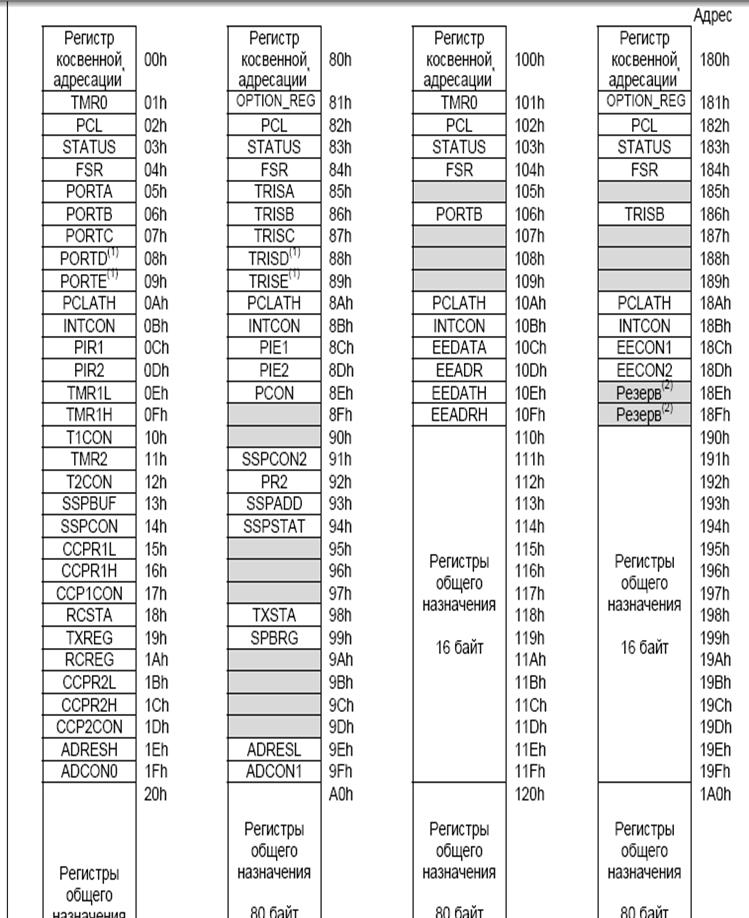

В приложении 1 представлена карта памяти данных микроконтроллеров PIC16F87* Гарвардской архитектуры. Все регистры контроллера Гарварской архитектуры разделяются на регистры специального назначения и регистры общего назначения.

Регистры специального назначения:

- регистр «Аккумулятор» -W;

- регистр команд (инструкций);

- регистры косвенной адресации INDF, FSR;

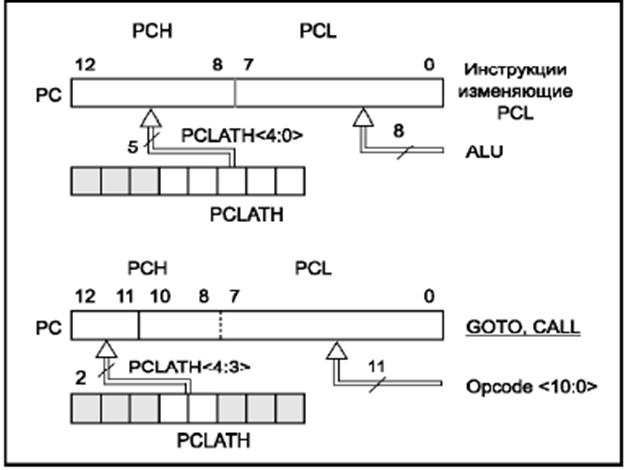

- регистры счетчика команд – PC (PCL, PCLATH);

- регистр состояния – STATUS;

- регистры портов и настройки портов;

- регистры настройки и обеспечения режимов контроллера.

Регистр аккумулятор является основным регистром микроконтроллера, через него выполняются операции преобразования данных микроконтроллера. Например:

ADDWF f,0 – сложить аккумуляторную переменную с регистровой с

сохранением результата в аккумуляторе;

SUBWF f,1 - вычесть из аккумуляторной переменной регистровую с

сохранением результата в регистре;

DECF f,0 - вычесть из аккумуляторной переменной единицу с

сохранением результата в аккумуляторе;

MOVWF f - передать данные из аккумулятора в рабочий регистр.

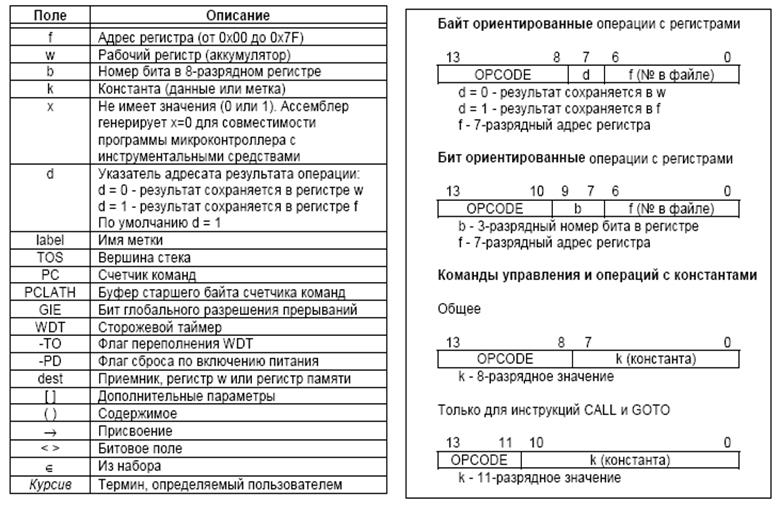

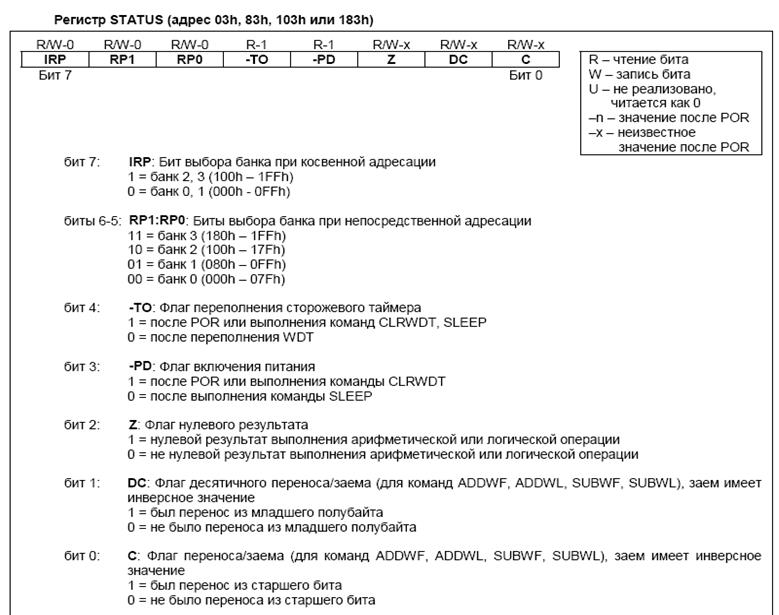

Регистр команд (инструкций) (см. приложение 1) предназначен для хранения кода выполняемой команды. Очень часто его путают с регистром счетчиком команд (см. приложение 4), который предназначен для хранения адреса выполняемой команды. В отличии от этого регистра регистр команд хранит КОД выполняемой команды. Чтобы точнее отразить назначение этого регистра, обратимся к примеру кода команд микроконтроллера Гарвардской архитектуры, представленной в приложении 1. В зависимости от формата команды (см. приложение 2) микроконтроллера Гарвардской архитектуры адрес (код адреса) записывается напрямую или через символьное имя регистра. Например, регистр статуса (см. приложение 3) имеет программируемые (с 5-го по 7-ой) и непрограммируемые (с 0-го по 4-ый) разряды. Байт ориентированные команды будут влиять только на программируемые разряды, хотя относятся целиком к команде. Если применить команду CLRF STATUS будут очищены только программируемые разряды. Бит ориентированные команды понятно также изменят только программируемые разряды регистра специального назначения.

Регистр счетчик команд (см. приложение 4) микроконтроллера Гарвардской архитектуры, для хранения четырнадцатиразрядного адреса команды должен быть реализован на базе двух восьмиразрядных регистров. Таковыми регистрами для микроконтроллеров PIC* являются регистры PCL и PCLATH. Заметим, что регистр PCLATH программирует верхний регистр счетчика команд PCH, который является непрограммируемым (то есть пользователь не может изменить его содержимое напрямую). Это обстоятельство можно пояснить механизмом изменения регистра счетчика команд. Счетчик команд инкрементируется автоматически в ходе выполнения программы, если младшие биты адреса указывают на номер адреса в страничном диапазоне, то старшие адреса указывают на номер страницы. Номер страницы меняют обычно команды перехода. Таким образом, предпочтение отдается командам операционной системы, только потом учитываются команды пользователя.

Регистры статуса и косвенной адресации подробно рассматриваются на лабораторных занятиях, поэтому в конспектах лекций упустим их описание. Регистры общего назначения расположены в программируемом контроллере по адресам: 0-ой банк : с 20h по 7Fh; 1-ый банк: c A0h по FFh; 2-ой банк: с 110h по 17Fh; 3-ий банк: c 190h по 1FFh.

3.2 Регистровая структура универсальных микропроцессоров

Группы регистров универсальных МП ещё более многообразны в силу развитости архитектуры. В классическом представлении они разделены на следующие группы:

- основные функциональные регистры;

- регистры процессора с плавающей точкой;

- системные регистры;

- регистры отладки и тестирования.

Рассмотрим

только несколько наиболее используемых регистров, чтобы иметь представление об

особенностях программирования универсальных микропроцессоров. Из состава основных

функциональных регистров выделим регистр статуса. Вот некоторые из флагов

управления этого регистра универсального микропроцессора: флаг управления df

(Directory Flag).

Он находится в 10-м бите регистра eflags и используется цепочечными командами.

Значение флага df определяет направление поэлементной обработки в этих

операциях: от начала строки к концу (df = 0) либо наоборот, от конца строки к

ее началу (df = 1). Для работы с флагом df существуют специальные команды: cld

(снять флаг df) и std (установить флаг df).

Применение этих команд позволяет привести флаг df в соответствие с алгоритмом и

обеспечить автоматическое увеличение или уменьшение счетчиков при выполнении операций

со строками.

5 системных флагов, управляющих вводом/выводом, маскируемыми прерываниями,

отладкой, переключением между задачами и виртуальным режимом. Прикладным

программам не рекомендуется модифицировать без необходимости эти флаги, так как

в большинстве случаев это приведет к прерыванию работы программы. Флаг переноса

(Carry Flag) cf1 — арифметическая операция произвела перенос из старшего бита

результата.

Регистр указатель команд eip/ip (Instraction Pointer register) - имеет разрядность 32/16 бит и содержит смещение следующей подлежащей выполнению команды относительно содержимого сегментного регистра cs в текущем сегменте команд. Этот регистр непосредственно недоступен программисту, но загрузка и изменение его значения производятся различными командами управления, к которым относятся команды условных и безусловных переходов, вызова процедур и возврата из процедур. Возникновение прерываний также приводит к модификации регистра eip/ip.

При переходе к 32-разрядной архитектуре стало необходимым обеспечить возможность адресации памяти емкостью до 232 байт. Кроме того, введение защищенного режима работы микропроцессора потребовало хранения большого количества дополнительной информации о сегменте: его длине, которая стала переменной, уровне привилегий, его типе и т. д. Простое увеличение разрядности сегментных регистров до 32 бит не обеспечило бы возможности хранения всей этой информации. Поэтому все данные о сегменте стали размещаться в специальных структурах - дескрипторах (описателях) сегментов, которые хранятся в таблицах дескрипторов, расположенных в памяти, а сегментные регистры, сохранив свою первоначальную длину в 16 разрядов, содержат так называемый селектор (указатель), который используется для того, чтобы найти нужный дескриптор в этих таблицах. Сегментные регистры используются при формировании линейных адресов памяти. Вторым компонентом для формирования линейного адреса является смещение, называемое также эффективным адресом (применительно к архитектуре IA-32 эти называния равноправны, хотя первое применяется намного чаще).

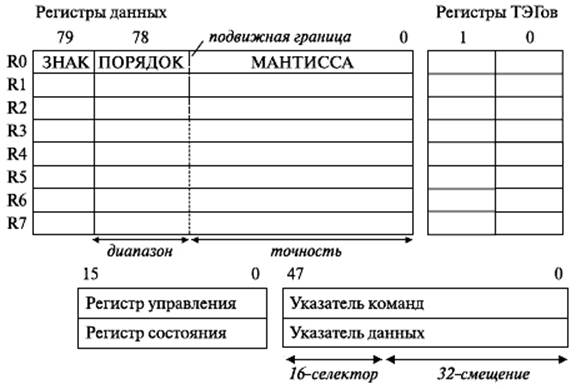

3.3 Регистры процессора с плавающей точкой

Процессор вычисления операций с плавающей запятой FPU, особенность присущая универсальным микропроцессорам и отсутствующая в Гарвардской архитектуре микропроцессоров, отметим эту особенность, чтобы выделить особенности этих регистров. К этой группе регистров относятся (см.рисунок 3.1):

- регистры данных;

- регистры тегов;

- регистр состояния;

- указатели команд и данных FPU;

- регистр управления FPU.

Регистр тегов FPU содержит 16-разрядное слово, включающее восемь двухбитовых тегов. Каждый тег (признак) характеризует содержимое одного из регистров данных.

Блок регистров данных доступен либо как стек (его вершина TOP определена в регистре состояний FPU ), либо как набор пронумерованных регистров.

Регистр состояния содержит указатель вершины блока данных, работающего в режиме стека (TOP), признаки результата и ошибок, возникающих при выполнении операции в FPU, а также флаг переполнения и антипереполнения стека регистров данных.

Рисунок 3.1 - Структура регистров процессора с плавающей точкой

Регистр управления управляет округлением (к ближайшему значению, вниз, вверх, к нулю), точностью (длина мантиссы 24, 53 или 64 бита), а также содержит маску признаков ошибок, фиксируемых в регистре состояния. Указатели команд и данных содержат адрес команды, вызвавшей ошибку, и адрес использованного операнда. Эти регистры имеют 48-разрядный формат: 16 разрядов содержат селектор соответствующего сегмента, а остальные 32 разряда - смещение в нем. В лекции рассмотрены назначение и состав регистровой структуры универсального микропроцессора, во многом определяющие архитектурные особенности микропроцессора.

4 Лекция № 4. Интерфейсы современных микроконтроллеров управления в задачах автоматизации

Цель лекции: изучение основных интерфейсных связей микроконтроллеров управления, применяемых в традиционных задачах управления.

4.1 Интерфейсы универсальных микропроцессорных систем

МПС - сложная система, включающая в себя большое количество различных устройств. Основой ее является микропроцессор. Связь устройств в традиционной фон-неймановской архитектуре между собой осуществляется с помощью сопряжений, которые в вычислительной технике называются системными интерфейсами.

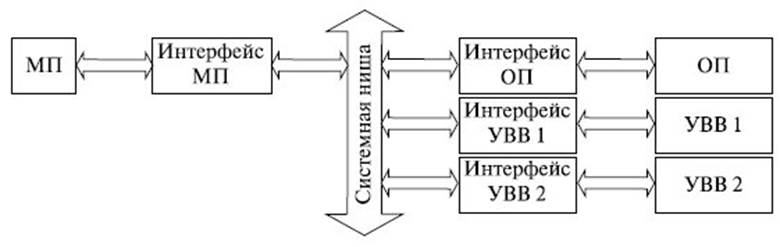

Рисунок 4.1 - Магистрально-модульный принцип построения микропроцессорной системы

Микропроцессор формирует адрес внешнего устройства или ячейки оперативной памяти и вырабатывает управляющие сигналы - либо IOR/IOW при обращении на чтение/запись из внешнего устройства, либо MR/MW для чтения/записи из оперативной памяти.

Для обмена информацией с внешними устройствами в МП имеются только 2 команды:

- команда ввода IN AX, DX записывает в регистр AX число из внешнего устройства, адрес которого находится в регистре DX ; при этом вырабатывается сигнал IOR ( INput/OUTput Read ));

- команда вывода OUT DX, AX выводит информацию из регистра AX во внешнее устройство, адрес которого находится в регистре DX ; при этом вырабатывается сигнал IOW ( INput/OUTput Write ).

Сигналы IOR/IOW формируются при выполнении только этих команд. Формирование сигналов MR/MW происходит в командах, для которых операнд и/или приемник результата располагаются в оперативной памяти, например, ADD [EBX], AX.

В связи с этим возможны два основных способа организации адресного пространства микропроцессорной системы: с общим адресным пространством внешних устройств и оперативной памяти; с независимыми адресными пространствами.

В первом случае к портам ввода/вывода можно обращаться как к ячейкам оперативной памяти. Достоинством такого подхода является возможность использовать различные режимы адресации при обращении к внешним устройствам, а также выполнять над содержимым портов ввода/вывода различные арифметико-логические операции. Но в то же время при этом сокращается емкость адресуемой ОП и снижается защищенность системы, так как она лишается дополнительных средств защиты, связанных с выполнением команд ввода/вывода (не работает поле IOPL регистра флагов). К тому же нарушение в логике работы программы (формирование неверного адреса оперативной памяти) может привести к ложному срабатыванию внешнего устройства.

Если первый недостаток не столь существенен при современных объемах запоминающих устройств, то второй может весьма негативно сказаться на работе МПС. Возможность использования сложных режимов адресации при обращении к внешним устройствам для микропроцессорных систем на основе универсальных МП не столь важна. Поэтому в настоящее время при построении МПС предпочтение отдается второму подходу.

Микропроцессор формирует адрес внешнего устройства или ячейки оперативной памяти и вырабатывает управляющие сигналы - либо IOR/IOW при обращении на чтение/запись из внешнего устройства, либо MR/MW для чтения/записи из оперативной памяти.

4.2 Интерфейс прямого доступа в память

В МПС используются два основных способа организации передачи данных между памятью и периферийными устройствами: программно управляемая передача и прямой доступ к памяти ПДП ( Direct Memory Access - DMA ).

Программно управляемая передача данных осуществляется при непосредственном участии и под управлением процессора. Например, при пересылке блока данных из внешнего устройства в оперативную память процессор должен выполнить следующую последовательность шагов:

1) сформировать начальный адрес области обмена ОП;

2) занести длину передаваемого массива данных в один из своих внутренних регистров, который будет играть роль счетчика;

3) выдать команду чтения информации из ВУ; при этом на шину адреса из МП выдается адрес ВУ, на шину управления - сигнал чтения данных из ВУ, а считанные данные заносятся во внутренний регистр МП;

4) выдать команду записи информации в ОП; при этом на шину адреса из МП выдается адрес ячейки оперативной памяти, на шину управления - сигнал записи данных в ОП, а на шину данных выставляются данные из регистра МП, в который они были помещены при чтении из ВУ;

5) модифицировать регистр, содержащий адрес оперативной памяти;

6) уменьшить счетчик длины массива на длину переданных данных;

7) если переданы не все данные, то повторить шаги 3-6, в противном случае закончить обмен.

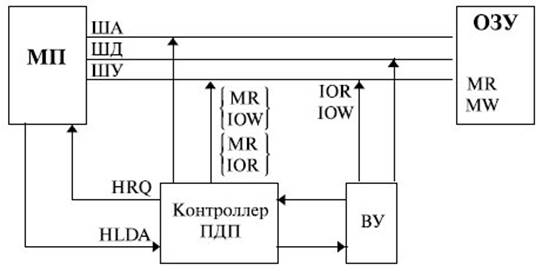

Последовательность действий КПДП при запросе на прямой доступ к памяти со стороны внешнего устройства следующая:

1)Принять запрос на ПДП (сигнал DRQ ) от ВУ.

2)Сформировать запрос к МП на захват шин (сигнал HRQ ).

3)Принять сигнал от МП ( HLDA ), подтверждающий факт перевода микропроцессором своих шин в третье состояние.

4)Сформировать сигнал, сообщающий устройству ввода-вывода о начале выполнения циклов прямого доступа к памяти ( DACK ).

Рисунок 4.2 - Структура МПС с контроллером прямого доступа к памяти

5) Сформировать на шине адреса компьютера адрес ячейки памяти, предназначенной для обмена.

6) Выработать сигналы, обеспечивающие управление обменом ( IOR, MW для передачи данных из ВУ в оперативную память и IOW, MR для передачи данных из оперативной памяти в ВУ).

7) Уменьшить значение в счетчике данных на длину переданных данных.

8) Проверить условие окончания сеанса прямого доступа (обнуление счетчика данных или снятие сигнала запроса на ПДП). Если условие окончания не выполнено, то изменить адрес в регистре текущего адреса на длину переданных данных и повторить шаги 5-8.

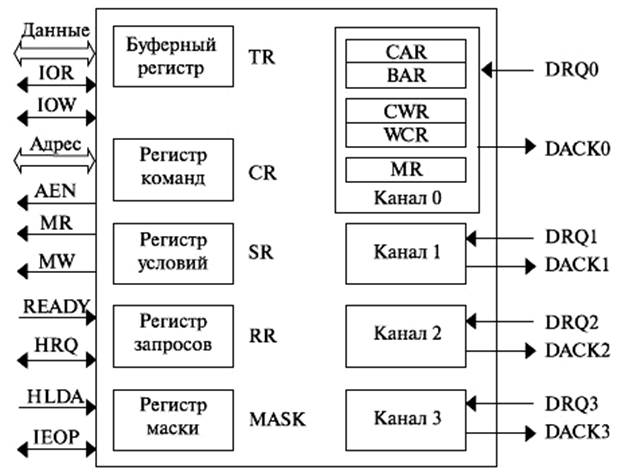

Контроллер состоит из 4 идентичных каналов (см. рисунок 4.3), позволяющих подключить к системе до четырех устройств, работающих в режиме ПДП.

В состав каждого канала входят следующие регистры:

- MR ( Mode Register ) - регистр режима. Определяет следующие параметры передачи: порядок изменения (увеличения или уменьшения) адреса ОП при передаче; возможность автоинициализации; режим обслуживания: одиночная передача (контроллер возвращает магистраль процессору после каждого цикла ПДП); блочная передача (контроллер владеет магистралью в течение передачи всего массива); по требованию (окончание передачи определяется снятием сигнала DRQ или подачей сигнала IEOP на внешний вход КПДП); каскадирование.

- CAR ( Current Address Register ) - регистр текущего адреса;

- BAR ( Base Address Register ) - базовый регистр адреса;

- CWR ( Current Word Register ) - текущий счетчик данных;

- WCR ( W0ord ConTRol Register ) - базовый счетчик данных.

Значения в регистрах BAR и WCR устанавливаются при инициализации и в ходе циклов ПДП не меняются. В регистры CAR и CWR в начале выполнения ПДП заносятся значения из регистров BAR и WCR соответственно. При выполнении ПДП эти регистры изменяются.

Рисунок 4.3 - Структура контроллера прямого доступа к памяти

Управляющие регистры, общие для всего контроллера:

- CR (Command Register) - регистр команд - определяет: режим память-память или обычный. В режиме память-память осуществляется обмен по схеме ПДП между двумя областями ОП (только для каналов 0 и 1) с использованием буферного регистра TR (Temporary Register); запрет/разрешение ПДП; порядок изменения приоритетов каналов: фиксированный приоритет; циклическое изменение приоритета после обработки запроса на ПДП по одному из каналов; явное указание наиболее приоритетного канала; уровень сигналов DRQ и DACK (настройка на активный уровень сигналов под особенности работы внешних устройств);

- SR (Status Register) - регистр условий: используется для фиксации признаков обмена по каждому из каналов и программных запросов на ПДП.

Во избежание ложных срабатываний внешних устройств, не использующих в данный момент режим прямого доступа, контроллер ПДП во время режима ПДП вырабатывает сигнал AEN, который блокирует работу остальных внешних устройств.

5 Лекция № 5. Интерфейсы микроконтроллеров (продолжение) - аналоговые интерфейсы

Цель лекции: изучение основных видов интерфейсов микроконтроллеров управления в задачах автоматизации.

5.1 Общие принципы организации передачи информации по интерфейсам микроконтроллера

Интерфейс - это совокупность программных и аппаратных средств, предназначенных для передачи информации между компонентами МПС и включающих в себя электронные схемы, линии, шины и сигналы адресов, данных и управления, алгоритмы передачи сигналов и правила интерпретации сигналов устройствами.

Задачи интерфейсных микросхем контроллеров:

- обеспечение функциональной и электрической совместимости сигналов и протоколов обмена модулей и системной магистрали;

- преобразование внутреннего формата данных модуля в формат данных системной магистрали и обратно;

- обеспечение восприятия единых команд обмена информацией и преобразование их в последовательность внутренних управляющих сигналов.

Неполный список периферии, которая может присутствовать в микроконтроллерах, включает в себя:

- универсальные цифровые порты, которые можно настраивать как на ввод, так и на вывод;

- различные интерфейсы ввода-вывода, такие как UART, I²C, SPI, CAN, USB, IEEE 1394, Ethernet;

- аналого-цифровые и цифро-аналоговые преобразователи;

- компараторы;

- широтно-импульсные модуляторы;

- таймеры;

- контроллеры бесколлекторных двигателей;

- контроллеры дисплеев и клавиатур;

- радиочастотные приемники и передатчики;

- массивы встроенной флеш-памяти;

- встроенный тактовый генератор и сторожевой таймер.

Выводы внешней стандартной периферии:

- Линии данных D0…D7;

- Линия считывания/записи R/W;

- Линии выбора (разрешения) RS;

- Линии адресации внутренних регистров (в зависимости от сложности микросхемы) CS.

Этапы управления периферией:

- обнуление линий R/W;

- установка соответствующего уровня линии RS в зависимости от того, к какому регистру должен обратиться микроконтроллер;

- выдача данных на линии D0-D7;

- установка логической единицы на линию CS, чтобы разрешить прием сообщения;

- установка логического нуля на линии CS, чтобы защелкнуть данные, принятые по линиям D0-D7.

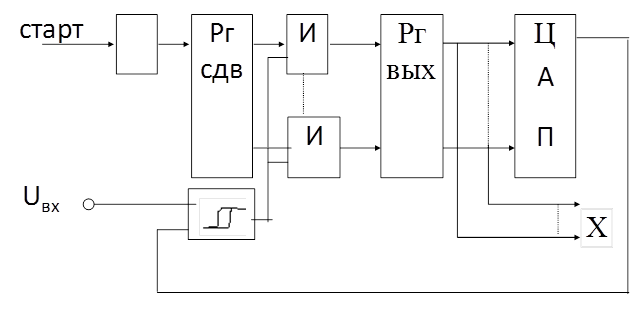

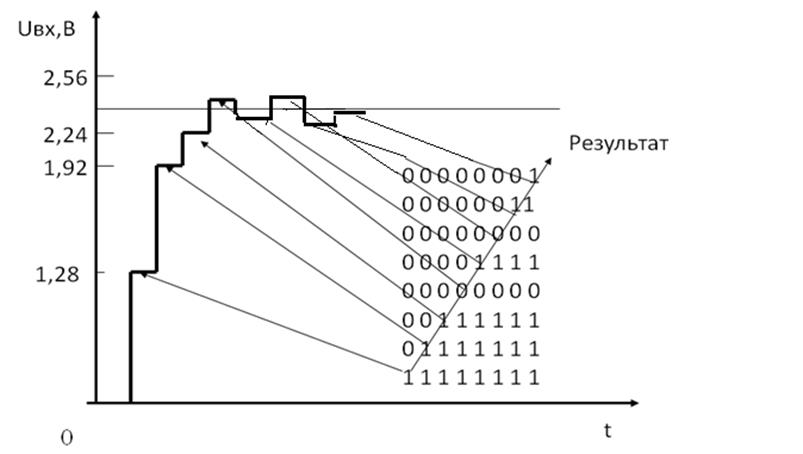

5.2 АЦП PIC-контроллеров

Известны различные методы аналого-цифрового преобразования [3]. В современных микроконтроллерах с широкими вычислительными мощностями не используются простейшие алгоритмы, такие как АЦП с преобразованием напряжения в частоту и АЦП параллельного преобразования. Современные Микроконтроллеры оснащены аналоговыми входами с разрядностью не менее 10. Так, рассматриваемый на практических занятиях микроконтроллер PIC* имеет разрядность 10 и оснащен АЦП поразрядного уравновешивания (см. рисунок 5.1 и 5.2). По стартовому сигналу тактовый генератор выдает логический уровень 1 в регистр выходной, начиная со старшего разряда (см. рисунок 5.2) при условии, что входной сигнал больше выходного сигнала после ЦАП, в примере на рисунке 5.2 это разряды 7,6,5,3,1,0. Если входной сигнал меньше выходного сигнала после ЦАП в выходной регистр записывается логический уровень 0, в примере на рисунке 5.2 это разряды четыре и два.

|

Рисунок 5.1 – Структурная схема алгоритма поразрядного уравновешивания

Аналого-цифровой преобразователь, изучаемого на практических занятиях контроллера использует выше описанный алгоритм. Десятиразрядный результат АЦП записывается в 2 восьмиразрядных регистра ADRESL и ADRESH, а управление процессом преобразования осуществляется регистрами управления ADCON0 и ADCON1. Подробнее о настройке этих регистров и программировании аналогового входа микроконтроллеров рассказывается на практических занятиях.

Рисунок 5.2 – Алгоритм поразрядного уравновешивания

6 Лекция № 6. Программы сопровождения проектов программирования микроконтроллеров. Языки программирования микроконтроллеров

Цель лекции: изучение основных программных единиц сопровождающих проектирование средств автоматизации на микроконтроллерах управления.

6.1 Основные программные среды проектирования микроконтроллеров

Проектирование микропроцессорных систем – это только первый этап его жизненного цикла системы. Дальше происходит изготовления, затем эксплуатация системы, после чего могут быть доработки изготовления. Чтобы сократить этап жизненного цикла создаются все более совершенные программы сопровождения проектов. Это инструментальные средства проектирования и отладки программного обеспечения микроконтроллеров: компиляторы, симуляторы, эмуляторы, внутрисхемные отладчики, программаторы.

После создания микропроцессорного контроллера производится его контроль или тестирование, правильность выполнения всех функций. Если объект находится в неисправном состоянии, то возникает задача диагностики и устранение найденных неисправностей – отладка.

Внутрисхемный эмулятор – это наиболее мощное и универсальное отладочное средство, которое делает процесс функционирования отлаживаемой системы прозрачным, то есть легко контролируемым, произвольно управляемым и модифицируемым. Основная область применения ВСЭ в настоящее время - это разработка встраиваемых систем на базе однокристальных микроконтроллеров. ВСЭ представляет собой программно-аппаратное средство, способное заменить эмулируемый МК в реальной схеме. Например, такими внутрисхемными эмуляторами являются ПЗУ мониторы. ПЗУ мониторы используются для контроля исполнения тестовой задачи.

Эмулятор ПЗУ представляют собой специальным образом подключаемую оперативную память, заменяющую ПЗУ на время отладки системы. Это устройство позволяет пользователю избежать многократных циклов перепрограммирования ПЗУ, связанных с отладкой программы.

Логический анализатор – универсальное гибкое средство, позволяющее разработчику находить причину неисправности сложных аппаратно-программных средств. Основной областью применения ЛА является этап разработки МПС, когда отсутствуют и проверенная аппаратура, и отлаженные программы. Разновидностью логического анализатора являются сигнатурный анализатор. Сигнатурный анализ основан на преобразовании длинных последовательностей двоичных сигналов в двоичное число, называемое сигнатурой. Измеряемые двоичные последовательности возбуждаются в контрольных точках МПС под действием специальной тестовой программы. Сигнатуры контрольных точек определяются на заведомо работоспособной системе и указываются на принципиальной схеме МПС подобно тому, как на схемах аналоговых устройств указываются осциллограммы и некоторые параметры аналоговых сигналов. Сигнатура представляется, как правило, в виде нескольких шестнадцатеричных цифр. В последнее время компании производители микропроцессоров и микроконтроллеров интегрируют в свои новые разработки модули с функциями встроенной отладки - отладчики на кристалле. Для поддержки функций встроенной отладки необходим специальный канал связи с компьютером. Чаще всего в качестве такого канала используется тестовый последовательный интерфейс типа JTAG, поэтому аппаратное средство отладки, построенное на базе встроенного в кристалл отладочного модуля, часто называют JTAG-эмулятором. Аббревиатура JTAG возникла по наименованию разработчика - объединенной группы по тестам JoINT Test Action Group.

Отметим, что интерфейсом JTAG в настоящее время оснащаются не только однокристальные микроконтроллеры и сигнальные процессоры, но и универсальные микропроцессоры вплоть до моделей с наивысшей на сегодняшний день производительностью, например, Intel Core i7, ExTReme Edition. Здесь он позволяет не только тестировать сам процессор (это не представляет особого прикладного интереса), но и организовать зондовый режим отладки (probe mode). Зондовый режим является мощным средством отладки системного программного обеспечения; обычный процессор, связанный с тестовым контроллером интерфейсом JTAG, превращается во внутрисхемный эмулятор.

6.2 Интегрированные среды разработки

Интегрированная среда разработки - это совокупность программных средств, поддерживающая все этапы разработки программного обеспечения от написания исходного текста программы до ее компиляции и отладки, и обеспечивающая простое и быстрое взаимодействие с другими инструментальными средствами (программным отладчиком-симулятором, внутрисхемным эмулятором, эмулятором ПЗУ и программатором).

Строго говоря, интегрированные среды разработки не относятся к числу средств отладки, тем не менее, обойти вниманием данный класс программных средств, существенно облегчающий и ускоряющий процесс разработки и отладки микропроцессорных систем, было бы неправильно.

При традиционном подходе, начальный этап написания программы строится следующим образом:

1) Исходный текст набирается при помощи какого-либо текстового редактора. По завершении набора, работа с текстовым редактором прекращается и запускается кросс компилятор. Как правило, вновь написанная программа содержит синтаксические ошибки, и компилятор сообщает о них на консоль оператора.

2) Вновь запускается текстовый редактор, и оператор должен найти и устранить выявленные ошибки, при этом сообщения о характере ошибок выведенные компилятором уже не видны, так как экран занят текстовым редактором.

И этот цикл может повторяться не один раз. Если программа имеет большой объем, собирается из различных частей, и подвергается длительному редактированию или модернизации, то даже этот начальный этап может потребовать много сил и времени. После этого наступает этап отладки программы и к редактору с компилятором добавляется эмулятор или симулятор, за работой которого хотелось бы следить прямо по тексту программы в текстовом редакторе.

Избежать большого объема однообразных действий и тем самым существенно повысить эффективность процесса разработки и отладки позволяют т.н. интегрированные среды (оболочки) разработки (Integrated Development Environment, IDE).

Работа в интегрированной среде дает программисту:

- возможность использования встроенного многофайлового текстового редактора, специально ориентированного на работу с исходными текстами программ;

- диагностика выявленных при компиляции ошибок, и исходный текст программы, доступный редактированию, выводятся одновременно в многооконном режиме;

- возможность организации и ведения параллельной работы над несколькими проектами. Менеджер проектов позволяет использовать любой проект в качестве шаблона для вновь создаваемого проекта;

- перекомпиляции подвергаются только редактировавшиеся модули;

- возможность загрузки отлаживаемой программы в имеющиеся средства отладки, и работы с ними без выхода из оболочки;

- возможность подключения к оболочке практически любых программных средств.

В последнее время, функции интегрированных сред разработки становятся стандартной принадлежностью программных интерфейсов эмуляторов и отладчиков-симуляторов.

Подобные функциональные возможности, в сочетании с дружественным интерфейсом, в состоянии существенно увеличить скорость разработки программ для микроконтроллеров и процессоров цифровой обработки сигналов.

6.3 Языки программирования микроконтроллеров

Программирование для микроконтроллеров, как и программирование для универсальных компьютеров прошло большой путь развития от программирования в машинных кодах до применения современных интегрированных систем написания программ, отладки и программирования микроконтроллеров. В настоящее время исходный текст программы пишется на одном из языков программирования.

Сами языки программирования в свою очередь делятся на две группы:

1) языки программирования "высокого" уровня;

2) языки программирования "низкого" уровня.

Языки программирования низкого уровня в настоящее время называются ассемблерами (старое название автокоды). Для каждого процессора существует своя группа ассемблеров. Ассемблеры для одного и того же процессора различаются между собой дополнительными возможностями, облегчающими программирование.

Языки программирования "высокого" уровня позволяют заменять один оператор несколькими машинными командами. Это позволяет увеличивать производительность труда программистов. Кроме того, языки "высокого" уровня позволяют писать программы, которые могут выполняться на различных микропроцессорах. (Естественно, что при этом необходимо использовать программы — трансляторы для соответствующего процессора.) В настоящее время наиболее распространены такие языки программирования высокого уровня как С и PLM.

Традиционным языком программирования для МПС, работающих в реальном масштабе времени (а именно к этому классу относится большинство систем управления, сбора и обработки информации на базе однокристальных микроконтроллеров и ЦСП), является Ассемблер. В настоящее время в распоряжение разработчиков практически повсеместно предоставляется также компилятор с языка Си, а иногда Си++ и даже Паскаля. Как правило, в этом случае используются специальные оптимизирующие компиляторы, но даже они не всегда позволяют написать приемлемую по времени выполнения и объему памяти программу, что вызывает необходимость их доработки на Ассемблере.

7 Лекция № 7. Основные направления развития архитектуры универсальных микропроцессоров

Цель лекции: анализ тенденций развития однокристальных микроконтроллеров, процессоров цифровой обработки сигналов и основные направления развития архитектуры универсальных микропроцессоров.

7.1 Тенденции развития однокристальных микроконтроллеров

Основную часть всех выпускаемых в настоящее время изделий данного класса составляют микроконтроллеры разрядностью 8 и 16 бит. Четырехразрядные микроконтроллеры постепенно ушли с рынка. В то же время наиболее интенсивно развиваются высокопроизводительные 32 разрядные микроконтроллеры с богатыми периферийными возможностями. Особенности архитектуры однокристальных микроконтроллеров:

- наличие нескольких видов запоминающих устройств на кристалле;

- системная программируемая Flash-память программ с возможностью программирования (загрузки) по последовательному и USB интерфейсу;

- программируемая энергонезависимая память данных EEPROM и ОЗУ данных;

- программируемые биты защиты от чтения и записи программной памяти и EEPROM, защита кода от несанкционированного доступа для выделенного во Flash-памяти блока;

- 16 или 32 восьмиразрядных регистра общего назначения, которые представляются единым регистровым файлом и не разбиваются на банки регистров;

- RISC-подобное процессорное ядро, использующее многоуровневый конвейер; все регистры непосредственно связаны с арифметико-логическим устройством, которое позволяет выполнять одну команду для двух разных регистров за один такт системного генератора;

- более развитая система прерываний, в том числе уровни приоритетов внешних запросов;

- встроенные в кристалл развитые интерфейсные возможности;

- специальные средства для управления встроенной системой отладки, поддерживающие протокол JTAG и другие;

- FUSE-биты для задания настроек ряда внутренних блоков микроконтроллера путем установки энергонезависимых "перемычек" на этапе программирования МК, что обеспечивает микроконтроллерам существенный запас гибкости при настройке на конкретное приложение.

7.2 Процессоры цифровой обработки сигналов

Процессоры цифровой обработки сигналов представляют собой класс специализированных микропроцессоров, предназначенных для решения задач цифровой обработки сигналов (ЦОС), к которым относятся обработка звуковых сигналов, обработка изображений, распознавание речи, распознавание образов, цифровая фильтрация, спектральный анализ и др.

Часто в литературе такие микропроцессоры называются цифровыми сигнальными процессорами (ЦСП), или DSP ( Digital Signal Processors ).

Цифровая обработка сигналов – это арифметическая обработка последовательности значений амплитуд сигнала, получаемых через равные промежутки времени. Главное, что отличает эту информацию, - она необязательно заносится в память и поэтому может оказаться недоступной в будущем. Следовательно, обрабатывать ее нужно в реальном масштабе времени (РМВ).

К основным особенностям цифровой обработки сигналов, которые во многом определяют архитектуру процессоров DSP, относятся: поточный характер обработки больших объемов данных в РМВ; обеспечение возможности интенсивного обмена с внешними устройствами.

Для эффективной реализации алгоритмов цифровой обработки сигналов необходима аппаратная поддержка базовых операций ЦОС. Поэтому рассмотрим вначале принципы цифровой обработки сигналов, оказывающие особое влияние на архитектуру ЦСП.

Любой аналоговый сигнал можно представить в виде характеристик, либо амплитуда-время, либо частота-амплитуда. Для перехода от одной формы представления к другой используется преобразование Фурье. Операции, выполняющие это преобразование, являются базовыми в цифровой обработке сигналов.

Преобразование Фурье представляет собой в общем случае работу с некоторой непрерывной функцией. С непрерывным преобразованием Фурье удобно работать в теории, но на практике мы обычно имеем дело с дискретными данными. Для обработки звуковых и видеосигналов в компьютере они сначала преобразуются в цифровую форму и представляются в виде некоторого набора отсчетов частот и амплитуд, производимых через определенные промежутки времени (период дискретизации). Поэтому здесь стоит говорить не об интегральном, а о дискретном преобразовании Фурье (ДПФ).

Отметим основные особенности архитектуры процессоров цифровой обработки сигналов:

1) Гарвардская архитектура, основу которой составляет физическое и логическое разделение памяти команд и памяти данных. Ключевые команды DSP-процессора являются многооперандными, и ускорение их работы требует одновременного чтения нескольких ячеек памяти. Соответственно на кристалле имеются раздельные шины адреса и данных (в некоторых типах процессоров - несколько шин адреса и данных). Это позволяет совмещать во времени выборку операндов и исполнение команд. Использование модифицированной гарвардской архитектуры предполагает, что операнды могут храниться не только в памяти данных, но и в памяти команд вместе с программами. Например, в случае реализации цифровых фильтров коэффициенты могут храниться в памяти программ, а значения данных - в памяти данных. Поэтому коэффициент и данные могут выбираться в одном машинном цикле. Для обеспечения выборки команды в том же машинном цикле используется либо кэш-память программ, либо двукратное обращение к памяти программ за время машинного цикла.

2) Для сокращения времени выполнения одной из основных операций цифровой обработки сигнала - умножения - применяется аппаратный умножитель. В процессорах общего назначения эта операция реализуется за несколько тактов сдвига и сложения и занимает много времени, а в DSP-процессорах благодаря специализированному умножителю нужен всего один цикл. Встроенная схема аппаратного умножения позволяет выполнить за 1 такт основную операцию ЦОС - умножение с накоплением (MultIPly-Accumulate -MAC) для 16- и/или 32-разрядных операндов.

3) Аппаратная поддержка циклических буферов. Например, для фильтра, при каждом вычислении отсчета выходного сигнала используется новый отсчет входного сигнала, который сохраняется в памяти на месте самого старого. Для такого циркулирующего буфера может использоваться фиксированная область ОЗУ. При этом во время вычислений генерируются лишь последовательные значения адресов ОЗУ вне зависимости от того, какая операция - запись или чтение - выполняется в настоящий момент. Аппаратная реализация циклических буферов позволяет установить параметры буфера (адрес начала, длина) в программе вне тела цикла фильтрации, что позволяет сократить время выполнения циклического участка программы.

4) Сокращение длительности командного такта. Это во многом обеспечивается приемами, характерными для RISC-процессоров. Главными из них являются размещение операндов большинства команд в регистрах, а также конвейеризация на уровне команд и микрокоманд. Конвейер имеет от 2 до 10 ступеней, что позволяет на различных стадиях выполнения одновременно обрабатывать до 10 команд. При этом используется генерация адресов регистров параллельно с выполнением арифметических операций, а также многопортовый доступ к памяти. Сюда же можно отнести и такой прием, характерный для универсальных микропроцессоров с EPIC-архитектурой, как применение команд со сверхбольшой длиной слова (VLIW), генерируемых на стадии компиляции программы. Этому же служит и рассмотренная выше гарвардская архитектура процессора, характерная для однокристальных микроконтроллеров.

5) Наличие на кристалле процессора внутренней памяти, что роднит ЦСП с однокристальными МК. Встроенная в процессор память обычно имеет значительно большее быстродействие, чем внешняя. Наличие встроенной памяти позволяет значительно упростить систему в целом, уменьшить ее размеры, энергопотребление и стоимость. Емкость внутренней памяти является результатом определенного компромисса. Ее увеличение ведет к удорожанию процессора и увеличивает энергопотребление, а ограниченная емкость памяти программ не позволяет хранить сложные алгоритмы. Большинство DS P-процессоров с фиксированной точкой имеют малую емкость внутренней памяти, обычно от 4 до 256 Кбайт, и невысокую разрядность внешних шин данных, связывающих процессор с внешней памятью. В то же время ЦСП с плавающей точкой обычно предполагают работу с большими массивами данных и сложными алгоритмами и имеют либо встроенную память большой емкости, либо большую разрядность адресных шин для подключения внешней памяти (а иногда и то, и другое).

6) Широкие возможности по аппаратному взаимодействию с внешними устройствами, включающие:

- большое разнообразие интерфейсов, в том числе контроллеры локальной промышленной сети CAN, встроенные коммуникационные (SCI) и периферийные (SPI) интерфейсы, I2C, UART;

- несколько входов для аналоговых сигналов и, соответственно, встроенный АЦП;

- выходные каналы широтно-импульсной модуляции (ШИМ);

- развитую систему внешних прерываний;

- контроллеры прямого доступа в память.

7) В некоторых DSP-семействах предусмотрены специальные аппаратные средства, облегчающие создание мультипроцессорных систем с параллельной обработкой данных для наращивания производительности.

8) DSP-процессоры широко используются в мобильных устройствах, где потребляемая мощность является основной характеристикой. Для снижения энергопотребления в сигнальных процессорах применяется множество методов, в том числе уменьшение напряжения питания и введение функций управления потреблением, например, динамическое изменение тактовой частоты, переключение в спящий или дежурный режим либо отключение не используемой в данный момент периферии. Следует отметить, что эти меры оказывают значительное воздействие на скорость работы процессора и при некорректном использовании могут привести к неработоспособности проектируемого устройства (в качестве примера можно упомянуть некоторые сотовые телефоны, которые в результате ошибок в программах управления энергопотреблением иногда переставали включаться) или к ухудшению его эксплуатационных характеристик (например, значительному времени восстановления работоспособности при выходе из спящего режима).

В настоящее время доминирующее положение на рынке ЦСП занимает фирма Texas Instruments. Среди остальных производителей этой продукции следует выделить фирмы Freescale Semiconductor (ранее подразделение Motorola), Analog Devices, Phillips Semiconductors и Agere Systems (Lucent MicroelecTRonic) . Следует отметить, что данный рынок является очень подвижным, что приводит к его постоянному перераспределению между компаниями и появлению на рынке новых игроков.

7.3 Основные направления развития архитектуры универсальных микропроцессоров

В настоящее время для повышения производительности микропроцессоров используется ряд новых подходов, основными из которых являются:

1) CMP (Chip Multi ProcessINg) - создание на одном кристалле системы из нескольких микропроцессоров (многоядерность);

2) SMT (Simultaneous MultiThreadINg) - многонитевая архитектура;

3) EPIC (Explicitly Parallel INsTRuction ComputINg) - вычисления с явным параллелизмом в командах.

Направление CMP обеспечивается возросшими технологическими возможностями, которые позволяют создать на одном кристалле несколько микропроцессоров и организовать их работу по принципу мультипроцессорных систем. Производители чипов уже не гонятся за частотой, сместив акцент на многоядерную архитектуру, которая позволяет наращивать производительность, сохраняя в приемлемых границах энергопотребление и тепловыделение. Многоядерные процессоры хорошо приспособлены для требовательных мультимедийных задач, таких как обработка видеозаписей, работы с большими базами данных, одновременное выполнение нескольких ресурсоемких заданий, например, компьютерной игры, записи DVD и загрузки файлов из Интернета.

При таком подходе задача повышения производительности работы отдельных приложений требует распараллеливания последних, то есть проблема перемещается с аппаратного на программный уровень. На данный момент сложности заключаются в том, что большая часть существующего программного обеспечения создавалась без расчета на использование в многоядерных и многопроцессорных конфигурациях. Другими словами, прогресс в области аппаратных средств на какое-то время опередил прогресс в области программного обеспечения.

Развитие микропроцессорной техники в этом направлении идет очень быстрыми темпами. Так, компания Tilera в 2007 году начала поставки специализированных процессоров Tile64, насчитывающих 64 ядра. А в 2009 году свет увидели 120-ядерная модификация этого процессора.

Направление SMT в развитии архитектуры микропроцессоров базируется на том, что одна задача не в состоянии полностью загрузить все возрастающие ресурсы микропроцессора. Поэтому на одном процессоре осуществляется запуск нескольких задач одновременно, при этом распараллеливание программ осуществляется аппаратными средствами МП.

Это позволяет более равномерно загрузить ресурсы процессора. Параллельно в разных устройствах МП могут выполняться команды из разных задач. Так, микропроцессор Alpha 21264 поддерживает выполнение до 4 задач одновременно. При поддержке SMT на 4 нити каждый процессор с точки зрения операционной системы выглядит как 4 логических процессора. Исследования показали, что SMT позволяет увеличить производительность данного процессора до двух раз, а дополнительные схемы управления занимают всего около 10 % площади кристалла.

Некоторые микропроцессоры для максимального повышения своей производительности используют оба вышеназванных подхода. Так, компания Sun Microsystems представила новый процессор ULTRaSPARC T2.

Чип снабжен восемью ядрами, каждое из которых может обрабатывать восемь потоков инструкций. Таким образом, он одновременно способен оперировать с 64 потоками. Тактовая частота ULTRaSPARC T2 составляет от 900 МГц до 1,4 ГГц.

Направление EPIC фактически использует известную технологию VLIW (Very Large INsTRuction Word) - очень длинного командного слова. Распараллеливание алгоритма между исполнительными модулями производится компилятором на этапе создания машинного кода, когда команды объединяются в связки и не конкурируют между собой за ресурсы микропроцессора. При этом упрощается блок управления на кристалле.

Особенности архитектуры EPIC:

1) Явный параллелизм в машинном коде. Поиск зависимостей между командами проводит не процессор, а компилятор.

2) Большое количество регистров.

3) Масштабируемость архитектуры до большого количества функциональных устройств (АЛУ, FPU, MMX, SSE и т. п.).

Применение предикатов. Предикатный подход исходит из предпосылки, что возросшие мощности микропроцессоров позволяют запускать параллельно команды из разных ветвей условного ветвления вместо того, чтобы ожидать формирования истинных признаков для выбора правильного направления или полагаться на блок предсказания переходов, рискуя прийти к необходимости перезагрузки достаточно длинных конвейеров в случае неудачного предсказания. Отметим основные достоинства этого подхода:

1) Упрощается архитектура процессора. Вместо логики распараллеливания на EPIC-процессоре можно разместить больше регист ров, функциональных устройств и т. п.

2) Процессор не тратит время на анализ потока команд.

3) Возможности процессора по анализу программы во время выполнения ограничены сравнительно небольшим участком программы, тогда как компилятор способен произвести анализ всей программы.

4) Если некоторая программа должна запускаться многократно (а именно так и бывает в подавляющем большинстве случаев), выгоднее распараллелить ее один раз при компиляции, а не тратить на это время каждый раз, когда она исполняется на процессоре.

Однако архитектуре EPIC присущ и ряд недостатков:

1) Компилятор производит статический анализ программы, раз и навсегда планируя вычисления. Однако даже при небольших изменениях исходных данных путь выполнения программы существенно изменяется.

2) Значительно усложняются компиляторы, следовательно, увеличиваются время компиляции программы и число ошибок в самих компиляторах.

3) Производительность микропроцессора во многом определяется качеством компилятора.

4) Увеличивается сложность отладки, так как отлаживается не исходная программа, а оптимизированный параллельный код. Программисту тяжело определить место и причину появления ошибки, так как в процессе трансляции исходной программы ее отдельные команды будут переставлены компилятором для обеспечения оптимальности работы микропроцессора.

Типичным представителем архитектуры EPIC является микропроцессор Itanium фирмы Intel.

8 Лекция № 8. Перспективные микроконтроллеры управления Texas Instruments

Цель лекции: выполнить обзор новейших решений современных микроконтроллеров управления на примере лидеров производства микроконтроллеров.

8.1 Общие сведения о контроллерах Texas Instruments

В настоящее время из многочисленных производителей микроконтроллеров лидирующее положение занимает компания Texas Instruments — американская компания, производитель полупроводниковых элементов, микросхем, электроники и изделий на их основе.

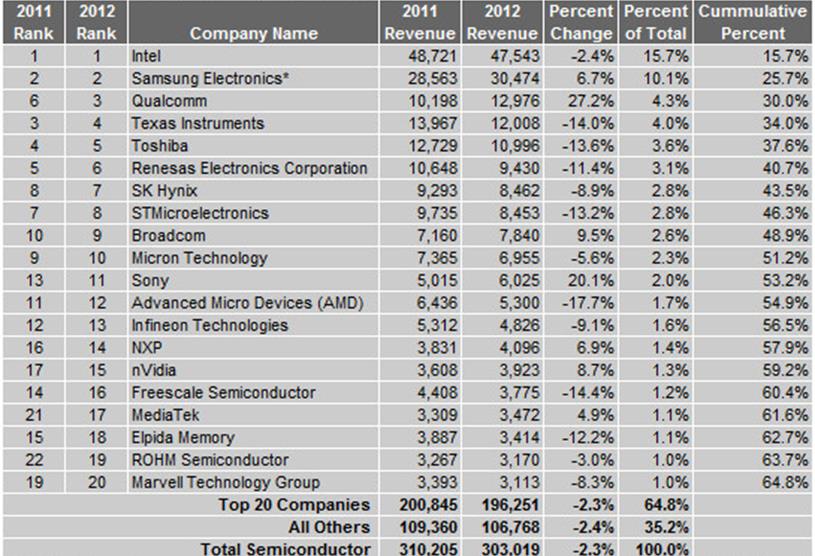

Компания занимает лидирующие позиции в своей сфере, о чем свидетельствуют рейтинги компании в последние годы (см. приложение 5,6,7).

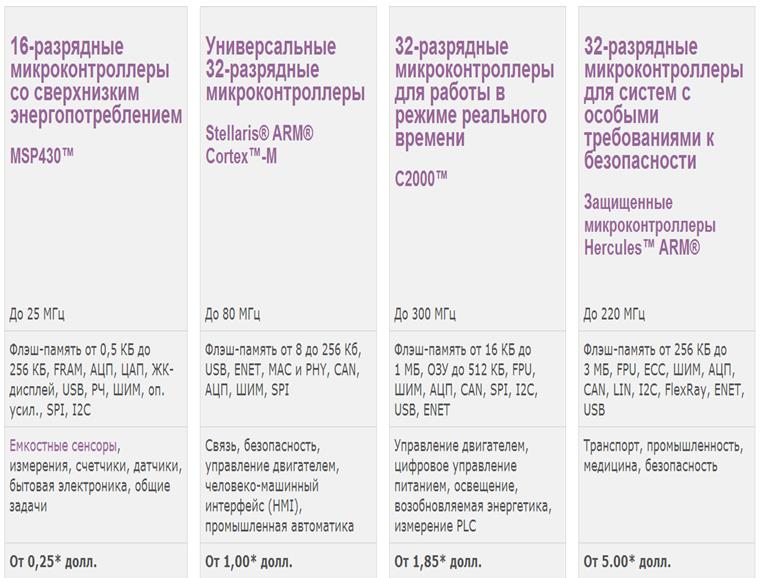

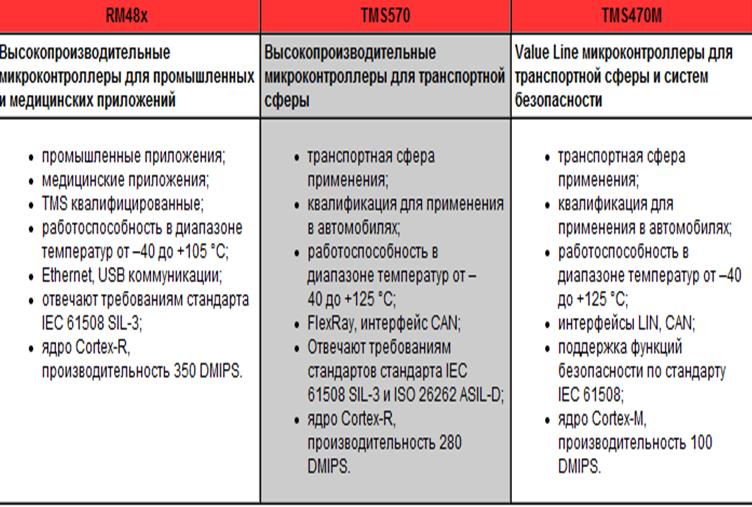

Для менее сложных и требующих не только сверхнизкое энергопотребление, но и компактность размеров Texas Instruments предлагает широкий выбор 16 – разрядных МК MSP430. В тоже время для проектов требующих сверхточных снятий показаний Texas Instruments предлагает серию мощных 32- разрядных МК C2000, Stellaris и Herculles.

8.2 16-разрядные контроллеры MSP430

Микроконтроллеры MSP430 обеспечивают путь для перехода многим разработчикам, использовавшим 8-разрядные микроконтроллеры. При тех же затратах доступные микроконтроллеры MSP430 предлагают 16-разрядную архитектуру, таймеры высокой точности и развитую встроенную периферию, обладая при этом высокой производительностью и низким энергопотреблением. Использование 16-разрядных микроконтроллеров позволяет до 10 раз повысить производительность и во столько же раз снизить энергопотребление по сравнению со многими дешёвыми 8-разрядными устройствами. В настоящий момент ряд микроконтроллеров включает 27 16-разрядных устройств со сверхнизким энергопотреблением, которые обладают аналоговыми устройствами различного уровня интеграции, модулями связи и выпускаются в различных корпусах. При объёмах от 100К единиц цена микроконтроллеров MSP430 серии Value начинается от $0,25, что позволяет разработчикам не увеличивать стоимость при улучшении эксплуатационных характеристик.

Микроконтроллеры семейства MSP430 имеют фон-неймановскую архитектуру и содержат 16 битное RISC ЦПУ, периферийные модули, а также гибкую систему тактирования, объединённые общими шинами адреса (MAB) и данных (MDB). Сочетание современного ЦПУ и отображаемых в памяти аналоговых и цифровых периферийных модулей делает семейство MSP430 пригодным для работы в приложениях, связанных с обработкой смешанных сигналов.

Отличительные характеристики микроконтроллеров семейства MSP430:

1) Архитектура со сверхнизким потреблением, позволяющая увеличить время работы при питании от батарей:

- ток сохранения содержимого ОЗУ — не более 0.1 мкА;

- ток потребления в режиме часов реального времени не более 0.8 мкА;

- ток потребления в активном режиме — 250 мкА/MIPS.

2) Высокоэффективная аналоговая подсистема, позволяющая выполнять точные измерения:

- таймеры, управляемые компаратором, для измерения сопротивления

- резистивных элементов.

3) 16-битное RISC ЦПУ:

- большой регистровый файл устраняет ограничения рабочего регистра;

- произведённое по меньшему техпроцессу ядро позволяет снизить потребление и уменьшает стоимость кристалла;

- оптимизировано для современных языков программирования высокого уровня;

- набор команд состоит всего из 27 инструкций; поддерживается 7 режимов адресации;

- векторная система прерываний с расширенными возможностями.

4) Флэш-память с возможностью внутрисхемного программирования позволяет гибко изменять программный код (в том числе, во время эксплуатации), а также производить сохранение данных.

В семейство MSP430 входят свыше 200 микросхем с высокой степенью интеграции. Они включают в свой состав USB, РЧ-модули, ЖК-контроллеры, 16-разрядный сигма-дельта АЦП. Большое число вариантов дает возможность разработчику выбрать наиболее подходящие микросхемы семейства для различных применений. Высокая степень интеграции MSP430 позволяет уменьшить габаритные размеры изделия и уменьшить число компонентов, входящих в его состав.

8.3 Микроконтроллеры Stellaris

Линейка микроконтроллеров (МК) Stellaris изначально была создана компанией Luminary Micro, которая, несмотря на свое сравнительно непродолжительное пятилетнее существование в качестве самостоятельной компании, оставила заметный след в мировой электронике, став первым производителем общедоступных микроконтроллеров с интегрированным процессором ARM Cortex-M3. В 2009 году Luminary Micro была поглощена гигантом полупроводниковой индустрии – компанией Texas Instruments, которая таким образом смогла в одночасье дополнить цепочку выпускаемых семейств микроконтроллеров недостающим и очень перспективным звеном. В конечном счете, компания Texas Instruments получила возможность предложить рынку самый обширный ассортимент микроконтроллеров Cortex-M3, который насчитывает более 160 позиций и охватывает все наиболее массовые области применения МК. Среди областей применения – бытовая техника, автоматизированный электропривод, системы мониторинга, HVAC-системы, автоматизация зданий, преобразовательная техника, преобразователи интерфейсов, торговые терминалы, контрольно-измерительное оборудование, медицинская техника, игровые устройства и многое другое.

Кроме того, архитектура процессора Cortex-M3 оптимизирована по стоимости, благодаря чему созданные на его основе МК способны конкурировать по цене с 16-битными и даже некоторыми 8-битными МК.

Наследовав перечисленные преимущества процессора Cortex-M3, МК Stellaris были дополнены оригинальной рецептурой встроенных модулей ввода- вывода во множестве типоисполнений, благодаря чему они приобрели ряд уникальных и порой беспрецедентных среди всех выпускаемых МК Cortex-M3 черт. К числу таковых относятся:

- доступность 28-выводных МК, способных конкурировать с 8- и 16-битными контроллерами;

- интеграция во многие МК модуля Ethernet, причем не только со встроенным MAC-контроллером, но и со встроенным трансивером;

- интеграция в некоторые МК ПЗУ со встроенной прошивкой программной библиотеки StellarisWare, которая содержит драйверы встроенных модулей ввода-вывода, функции для программирования Flash-памяти, криптографические таблицы по стандарту AES, а также функции обнаружения ошибок CRC.

Микроконтроллеры Stellaris компании Texas Instruments вошли в историю как первые микроконтроллеры с интегрированным 32-битным процессором ARM Cortex-M3 и, несмотря на появление многих конкурирующих решений, остаются лидерами по ряду особенностей:

- Высочайшая степень интеграции позволяет сэкономить до 3,24 долл. на стоимости системы.

- Более 160 продуктов семейства Stellaris обеспечивают широкий выбор.

- Порты ввода/вывода общего назначения микроконтроллера способны генерировать прерывания, выдерживают 5-В питание и имеют программируемую нагрузочную способность и управляемую скорость нарастания выходного напряжения.

- Улучшенные коммуникационные возможности, контроллеры 10/100.

- Ethernet MAC/PHY, USB и USB OTG, CAN, а также расширенные интерфейсы периферии.

- Аппаратная и программная поддержка сложных алгоритмов управления приводом.

- Встроенные аналоговые компараторы и АЦП обеспечивают возможности для аппаратной и программной оптимизации параметров системы.

- Простота разработки программ с помощью бесплатного ПО StellarisWare.

Приложение 1 - Карта памяти и список команд микроконтроллера PIC*

Приложение 2 – Формат команд микроконтроллеров

Приложение 3 - Регистр STATUS микроконтроллера PIC* и его разряды

Приложение 4 - Регистр счетчик команд микроконтроллера PIC* и его программирование

Приложение 5 – Рейтинг доходов производителей полупроводниковой продукции.

Приложение 6 - Семейства микроконтроллеров Texas Instruments

Список литературы

1. Парр Э. Программируемые контроллеры: руководство для инженера. – М.:БИНОМ. Лаборатория знаний, 2007. – 516 с.: ил.

2. Копесбаева А.А. Микропроцессорные комплексы в системах управления. Учебное пособие. – АИЭС, Алматы 2010 год.

3.Петров И.В. Программируемые контроллеры. Стандартные языки и приемы прикладного проектирования / Под ред. Проф. В.П. Дьяконова.-М.: СОЛОН-Пресс, 2004. – 256 с.: ил. – (Серия «Библиотека инженера»).

4. Копесбаева А.А. Программно-технические комплексы управления. Методические указания к лабораторным работам (для студентов специальности «Автоматизация и управление») – АИЭС, Алматы 2010 год.

5. Копесбаева А.А. Программно-технические комплексы управления. Методические указания к курсовой работе (для студентов специальности «Автоматизация и управление») – АУЭС, Алматы 2011 год.

6. КопесбаеваА.А. Программно-технические комплексы управления. Конспекты лекций. (для студентов специальности «Автоматизация и управление») – АУЭС, Алматы 2012 год.

7. Яценков В.С. Микроконтроллеры Microchip. Практическое руководство. – 2 –е изд. испр. и дополн. – М.: Горячая линия – Телеком, 2005 – 280 с., илл.

8. Харазов В.Г. Интегрированные системы управления технологическими процессами – СПб.: Профессия, 2009 . – 592 с., ил., табл., сх.

9. Елизаров И.А., Мартемьянов Ю.Ф., Схиртладзе А.Г., Фролов С.В. Технические средства автоматизации. Программно-технические комплексы и контроллеры: Учебное пособие. - М.: «Издательство Машиностроение -1», 2004.- 180 с.

10. Уськов А.А., Кузьмин А.В. Интеллектуальные технологии управления. Искуственные нейронные сети и нечеткая логика. – М.: Горячая Линия – Телеком, 2004. – 143 с.: ил.

11.Фрунзе А.В. Микроконтроллеры? Это же просто! Том II - М.: ООО «ИД СКИМЕН» 2002.-292 с., илл.

12.Фрунзе А.В. Микроконтроллеры? Это же просто! Том I - М.: ООО «ИД СКИМЕН» 2002.- 336 с., илл.

13.Корнеев В.В., Киселев А.В. Современные микропроцессоры –3-е изд., перераб. и доп. – СПб.: БХВ – Петербург, 2003.- 448 с. илл.

14.Кэпс Ч., Стаффорд Р. Программирование на языке ассемблера и архитектура. – Пер. с англ. – М.: Радио и связь, 1991.