МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РЕСПУБЛИКИ КАЗАХСТАН

Некоммерческое акционерное общество

«Алматинский институт энергетики и связи»

Т.М.Жолшараева

СХЕМОТЕХНИКА

Учебное пособие

Алматы 2010

УДК 621.3.049

ББК 32.844Я73

Ж79. Схемотехника

Учебное пособие/Т.М.Жолшараева

АИЭС. Алматы, 2010.− 81 с.

ISBN 978−601−7098−73−5

Рассмотрены основные аналоговые и цифровые электронные устройства. Приведены структурные и принципиальные схемы, временные диаграммы и описан принцип действия устройств.

Учебное пособие предназначено для студентов, обучающихся по специальности 5B0704 – Вычислительная техника и программное обеспечение и может быть использовано студентами специальностей 5B0702 – Автоматизация и управление и 5B0719 – Радиотехника, электроника и телекоммуникации.

Табл. 13, Ил. 113, библ. – 15 назв.

ББК 32.844Я73

РЕЦЕНЗЕНТЫ: ТЭАКТ, докт. техн. наук, проф. Ш.Б.Биттеев

АИЭС, доктор техн. наук, проф.З.С.Куралбаев

Печатается по плану издания Министерства образования и науки Республики Казахстан на 2010 г.

ISBN 978−601−7098−73−5

© НАО «Алматинский институт энергетики и связи», 2010 г.

Содержание

1 Схемотехника аналоговых устройств

1.1 Дифференциальный усилитель

1.1.1 Режимы работы дифференциального усилителя

1.1.2 Дифференциальный усилитель с генератором стабильного тока

1.1.3 Разновидности схем дифференциальных усилителей

1.1.4 Дифференциальный усилитель с динамической нагрузкой

1.2 Выходные каскады усилителей

1.2.1 Простейшая двухтактная схема

1.2.2 Усилитель мощности с раздельным начальным смещением

1.3.1 Назначение и основные параметры операционных усилителей

1.3.2 Двухкаскадный операционный усилитель

1.3.5 Неинвертирующий усилитель

1.3.7 Нелинейный режим работы ОУ

1.4 Генераторы электрических сигналов

1.4.1 RC-генератор синусоидальных колебаний

1.4.2 Генераторы релаксационных колебаний

2 Схемотехника цифровых устройств

2.1 Основные логические операции и логические элементы

2.2 Логические интегральные схемы

2.2.1Основные параметры логических интегральных микросхем

2.2.2 Схема ДТЛ – диодно-транзисторной логики

2.2.3 Схемы ТТЛ ‑ транзисторно-транзисторной логики

2.2.4 Схемы ЭСЛ ‑ эмиттерно-связанной логики

2.2.5 Логические элементы на полевых транзисторах

2.3 Комбинационные логические схемы

2.3.1 Синтез комбинационной логической схемы

2.3.2.2 Синтез матричного дешифратора

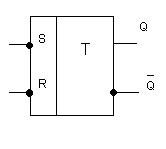

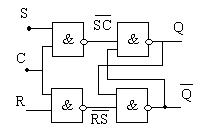

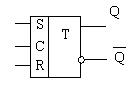

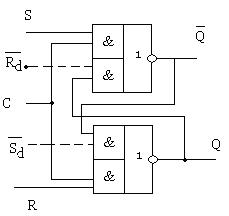

2.4 Последовательностные логические схемы

2.5 Цифровые запоминающие устройства

2.5.1 Классификация запоминающих устройств

2.5.2 Оперативные запоминающие устройства

2.5.4 Постоянные запоминающие устройства

1 Схемотехника аналоговых устройств

1.1 Дифференциальный усилитель

1.1.1 Режимы работы дифференциального усилителя

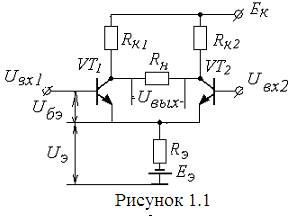

Дифференциальный усилитель (см. рисунок1.1) усиливает

разность входных сигналов, который называется дифференциальным сигналом. Его

можно строить на биполярных и униполярных транзисторах. Он представляет собой

параллельно-балансный каскад или сбалансированный мост. Строится на двух

усилителях постоянного тока с общим эмиттерным сопротивлением Rэ. Коллекторные

нагрузки Rк1 =

Rк2.

Идентичные транзисторы VT1 и VT2

вместе с резисторами Rк1 и Rк2 представляют собой

плечи моста, в одну диагональ которой включен источник питания Ек,

в другую – нагрузка Rн.

Дифференциальный усилитель (см. рисунок1.1) усиливает

разность входных сигналов, который называется дифференциальным сигналом. Его

можно строить на биполярных и униполярных транзисторах. Он представляет собой

параллельно-балансный каскад или сбалансированный мост. Строится на двух

усилителях постоянного тока с общим эмиттерным сопротивлением Rэ. Коллекторные

нагрузки Rк1 =

Rк2.

Идентичные транзисторы VT1 и VT2

вместе с резисторами Rк1 и Rк2 представляют собой

плечи моста, в одну диагональ которой включен источник питания Ек,

в другую – нагрузка Rн.

Питание каскада осуществляется от двух источников Eк = Eэ, т.е. суммарное

напряжение питания ![]() .

.

С помощью ![]() уменьшается потенциал эмиттеров VT1 и VT2

относительно общей точки, при этом отпадает необходимость согласования

потенциалов.

уменьшается потенциал эмиттеров VT1 и VT2

относительно общей точки, при этом отпадает необходимость согласования

потенциалов.

На дискретных транзисторах трудно получить абсолютную симметрию, поэтому качественные ДУ строятся на интегральных микросхемах.

Рассмотрим возможные режимы работы ДУ:

а) режим покоя. Оба входа ДУ закорочены на землю, т.е.

![]() .

.

Напряжения база-эмиттер покоя равны минус Uэ ![]() . В свою очередь напряжение на эмиттере

равно

. В свою очередь напряжение на эмиттере

равно![]()

Следовательно, напряжение на базе![]() .

.

Оба транзистора открыты, работают в активном режиме.

Текут токи покоя ![]() .

Они создают на Rк1 и Rк2 одинаковое падение напряжения, следовательно,

.

Они создают на Rк1 и Rк2 одинаковое падение напряжения, следовательно, ![]() .

. ![]() снимается с Rн

снимается с Rн ![]() .

.

Токи эмиттеров Iэ1= Iэ2; Iэ = Iэ1+ Iэ2.

Достоинства схемы:

- не нужен источник компенсирующей ЭДС;

-

уменьшается дрейф от

нестабильности напряжения питания и от температурной нестабильности. Например,

при увеличении напряжения питания Ек или температуры

окружающей среды приращения напряжения на коллекторах одинаковые ![]() по величине и по знаку,

следовательно, Δ

по величине и по знаку,

следовательно, Δ![]() .

.

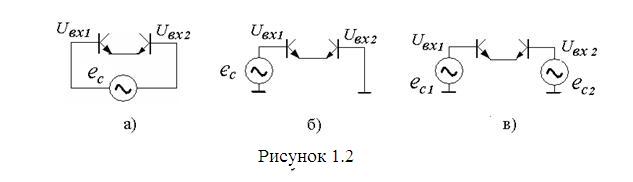

б) режим с входными сигналами. Рассмотрим три способа подачи сигнала:

1) сигнал ес>0

подается между базами транзисторов (см. рисунок1.2,а).Тогда ![]() ,

, ![]() .

.

Приращения коллекторных токов 0<![]() , приращения коллекторных

напряжений 0>

, приращения коллекторных

напряжений 0>![]() .

Выходное напряжение

.

Выходное напряжение ![]() .

.

Изменение тока коллектора вызывает изменение тока

эмиттера 0<![]() ,

общий ток эмиттера

,

общий ток эмиттера ![]() ,

следовательно,

,

следовательно, ![]() – ток эмиттера

постоянный

– ток эмиттера

постоянный

На эмиттере нет приращения напряжения, UЭ также постоянно. Т.е. имеет место стабилизация напряжения по постоянной составляющей, отсутствует обратная связь по переменной составляющей;

|

2) сигнал подается на одну из баз, а другая база заземлена (см. рисунок1.2,б). Такой вход называется дифференциальным входом.

![]()

![]()

![]()

Увеличивается ток базы ![]() . Следовательно, увеличивается ток

коллектора

. Следовательно, увеличивается ток

коллектора ![]() и

ток эмиттера

и

ток эмиттера ![]() .

Напряжение на коллекторе

.

Напряжение на коллекторе ![]() уменьшается. Сумма эмиттерных токов

уменьшается. Сумма эмиттерных токов ![]() постоянна.

Следовательно,

постоянна.

Следовательно, ![]() ,

,

![]() ,

, ![]() . Выходное напряжение,

как и в предыдущем случае

. Выходное напряжение,

как и в предыдущем случае ![]() ;

;

3) сигналы поданы на оба входа ![]() и

и ![]() от двух независимых источников (см. рисунок6.4).

Здесь справедлив принцип суперпозиции.

от двух независимых источников (см. рисунок6.4).

Здесь справедлив принцип суперпозиции.

![]() , где K –

коэффициент усиления ДУ.

, где K –

коэффициент усиления ДУ.

1.1.2 Дифференциальный усилитель с генератором стабильного тока

Разность входных сигналов называется дифференциальным сигналом.

Синфазный сигнал – это сигнал, действующий одновременно на обоих

входах, например, сигнал вследствие изменения напряжения питания, температуры и др., т.е. это помеха, влияние которой

надо ослабить. Для уменьшения действия синфазного сигнала (СС)

необходимо стабилизировать ток эмиттера. Допустим, что на оба входа действует

синфазное напряжение, стремящееся увеличить токи коллекторов Iк1 и Iк2, а их сумма равна Iэ, которая является постоянной величиной. Т.е. ток

коллектора не будет увеличиваться, и напряжения коллекторов и выходное не будет

изменяться. Для стабилизации тока эмиттера можно увеличивать эмиттерное

сопротивление

температуры и др., т.е. это помеха, влияние которой

надо ослабить. Для уменьшения действия синфазного сигнала (СС)

необходимо стабилизировать ток эмиттера. Допустим, что на оба входа действует

синфазное напряжение, стремящееся увеличить токи коллекторов Iк1 и Iк2, а их сумма равна Iэ, которая является постоянной величиной. Т.е. ток

коллектора не будет увеличиваться, и напряжения коллекторов и выходное не будет

изменяться. Для стабилизации тока эмиттера можно увеличивать эмиттерное

сопротивление ![]() ,

но тогда необходимо увеличить напряжение питания, а его не нужно изменять.

Вместо

,

но тогда необходимо увеличить напряжение питания, а его не нужно изменять.

Вместо ![]() целесообразно

ставить источник тока или генератор стабильного тока (ГСТ) на

транзисторах, имеющего небольшое сопротивление по постоянному току и большое – по переменному

(см. рисунок1.3).

целесообразно

ставить источник тока или генератор стабильного тока (ГСТ) на

транзисторах, имеющего небольшое сопротивление по постоянному току и большое – по переменному

(см. рисунок1.3).

В схему ГСТ входят: транзистор VT3, диод VD, резисторы R1, R2, R3 и источник питания – Еэ.

Ток Iэ

является сумой токов эмиттеров транзисторов VT1 и VT2

дифференциального усилителя и задается он генератором стабильного тока на VT3.

Схема ГСТ – это усилитель по схеме с общей базой. Его выходное

сопротивление много больше RЭ

в схеме на рисунке 1.1.

Смещение на базу VT3

подается через делитель R1, VD,

R2.

Диод VD служит для термокомпенсации справедливо

![]() .

.

Должно выполняться условие R1>> R2, Rэ. Ток I1 через R1 постоянный, так как R1 большое и от температуры не зависит. В свою очередь

по первому закону Кирхгофа ![]() .

.

При повышении температуры входная характеристика VT3 смещается влево, т.е. увеличивается ток эмиттера Iэ3. Одновременно уменьшается сопротивление диода VD, увеличивается ток I2, следовательно, уменьшается ток Iб3, равный I1 ‑ I2. Ток Iк3 = a Iб3 также уменьшится. Таким образом, ток эмиттера дифференциального усилителя Iэ поддерживается стабильным.

Определим Iэ аналитическим путем.

Так как Iб3 << Iэ и можно считать Iэ3 = Iк3 = Iэ, то

![]() .

(1.1)

.

(1.1)

Поскольку Iб3 << I1, то I1 = I2. Из рисунка 1.3 находим

![]() . (1.2)

. (1.2)

Из (1.1), учитывая, что ![]() находим Iэ

находим Iэ

![]() , т.е. ток Iэ зависит от температуры

незначительно, что и требуется от ГСТ.

, т.е. ток Iэ зависит от температуры

незначительно, что и требуется от ГСТ.

1.1.3 Разновидности схем дифференциальных усилителей

Основными задачами разработки разновидностей схем ДУ являются увеличение коэффициента усиления усилителя и увеличение входного сопротивления.

Используются следующие разновидности схем ДУ:

а) на входах ДУ ставятся составные транзисторы (пара Дарлингтона), у которых гораздо выше входное сопротивление и коэффициент передачи тока равен произведению коэффициентов передачи тока обоих транзисторов;

б) на входах ДУ ставятся эмиттерные повторители, у которых входное сопротивление сотни килоомов;

в) ДУ с полевыми транзисторами на входах;

г) ДУ с динамической нагрузкой.

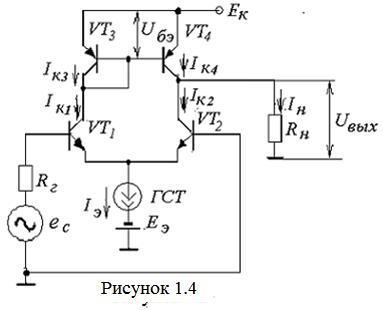

1.1.4 Дифференциальный усилитель с динамической нагрузкой

Для увеличения коэффициента усиления усилителя Ku необходимо

увеличить коллекторную нагрузку Rк, но тогда потребуется увеличить напряжение источника

питания Ек. В интегральных схемах увеличение Rк ведет к

увеличению площади и габаритов микросхемы. Поэтому в ИС используется

динамическая нагрузка, т.е. вместо резисторов ![]() Rк1 и Rк2 ставятся транзисторы VТ3 и VТ4,

которые имеют низкое сопротивление по постоянному току и высокое – по

переменному. Транзисторы VТ3 и VТ4 имеют полярность, противоположную к основным (см.

рисунок1.4).

Rк1 и Rк2 ставятся транзисторы VТ3 и VТ4,

которые имеют низкое сопротивление по постоянному току и высокое – по

переменному. Транзисторы VТ3 и VТ4 имеют полярность, противоположную к основным (см.

рисунок1.4).

Транзисторы VT1 и VT2 (n-p-n-типа) – основные, транзисторы VТ3 и VТ4 (p-n-p-типа) – коллекторная нагрузка. Эти транзисторы соединены коллекторами. Транзистор VТ3 используется в диодном включении. В эмиттерной цепи ставится генератор стабильного тока (ГСТ) для уменьшения влияния синфазного сигнала на схему.

Вход ДУ – дифференциальный, выход ‑ однотактный.

Транзисторы VТ3 и VТ4 включены по схеме токового зеркала – отражателя токов. Ток Iк1, протекая через VТ3, создает одинаковое смещение на базах транзисторов VТ3 и VТ4 Uбэ3=Uбэ4. Поэтому Iк4= Iк3, а Iк3 является током Iк1.

Следовательно Iк4=Iк1. VТ4 повторяет изменения токов VT1, т.е. VТ4 полностью повторяет Iк1, поэтому пара VТ3 и VТ4

называется токовым зеркалом.

Следовательно Iк4=Iк1. VТ4 повторяет изменения токов VT1, т.е. VТ4 полностью повторяет Iк1, поэтому пара VТ3 и VТ4

называется токовым зеркалом.

Найдем ![]() , Uвых и Кu. Допустим, на вход подан сигнал ec. Приращение токов базы

, Uвых и Кu. Допустим, на вход подан сигнал ec. Приращение токов базы ![]() и

и ![]() . Тогда токи коллекторов

. Тогда токи коллекторов ![]() и

и ![]() . Так как

. Так как ![]() , то

, то ![]() . Ток на выходе ДУ равен

. Ток на выходе ДУ равен ![]() . Видно, что ток на

выходе ДУ усилился в b раз и удвоился.

. Видно, что ток на

выходе ДУ усилился в b раз и удвоился.

Выходное напряжение ДУ ![]() , где

, где ![]() - входное сопротивление последующего

каскада.

- входное сопротивление последующего

каскада.

Коэффициент усиления ДУ ![]()

![]() . При

. При![]()

![]() .

.

Сопротивление ![]() может быть обеспечено в несколько сотен

килоом, следовательно, коэффициент усиления ДУ по напряжению может достигать

нескольких сотен и тысяч.

может быть обеспечено в несколько сотен

килоом, следовательно, коэффициент усиления ДУ по напряжению может достигать

нескольких сотен и тысяч.

Таким образом, отражатель токов позволяет получить высокий коэффициент усиления по напряжению и удвоить сигнал на однотактном выходе.

1.2 Выходные каскады усилителей

Выходные каскады – это усилители мощности. Они служат для получения максимальной мощности в нагрузке при максимально возможном КПД и минимальных нелинейных искажениях.

В микроэлектронике класс А обычно используется редко из-за низкого КПД. Более популярны двухтактные усилители класса В и АВ.

1.2.1 Простейшая двухтактная схема

Рассмотрим простейшую двухтактную схему усилителя класса В на комплементарных транзисторах (см. рисунок 1.5).

Транзистор VT1 – n-p-n,

VT2 –

p-n-p –типа.

Транзистор VT1 – n-p-n,

VT2 –

p-n-p –типа.

Нагрузка Rн включена в эмиттерной цепи, т.е. транзистор включен по схеме с общим коллектором, следовательно, этот эмиттерный повторитель дает большое усиление по мощности, обусловленное высоким коэффициентом усиления тока.

В режиме покоя оба транзистора закрыты, т.к. Uэб = 0 (класс В).

При подаче на вход положительной полуволны переменного напряжения VT1 – открывается, VT2 – закрывается. Течет ток от +Е1 ‑ КЭ1 ‑ Rн ‑ – Е1.

При подаче отрицательной полуволны переменного

напряжения VT1 –

закрывается, VT2 –

открывается. Течет ток от +Е2 ‑ Rн ‑ЭК2 ‑ – Е2.

Таким образом, схема работает в два такта: в первом такте открыт VT1, во

втором ‑ VT2,

т.е. на выходе усилителя имеет место двуполярный сигнал. Коэффициент усиления

по мощности ![]() .

.

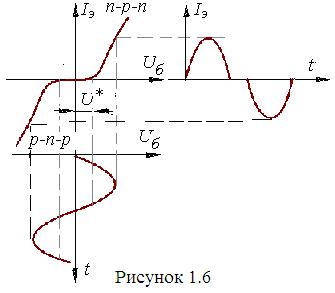

Но недостаток схемы в том, что она имеет высокий коэффициент

нелинейных искажений. На рисунке 1.6 приведена совмещенная передаточная

характеристика

Но недостаток схемы в том, что она имеет высокий коэффициент

нелинейных искажений. На рисунке 1.6 приведена совмещенная передаточная

характеристика ![]() .

Длительность положительной и отрицательной полуволн на выходе меньше

полупериода сигнала (часть синусоиды не усиливается). Выходной ток Iэ носит импульсный

характер, т.е. имеет большое число высших гармоник в своем спектре. Это

особенно существенно при малых Uвх, соизмеримых с U*.

.

Длительность положительной и отрицательной полуволн на выходе меньше

полупериода сигнала (часть синусоиды не усиливается). Выходной ток Iэ носит импульсный

характер, т.е. имеет большое число высших гармоник в своем спектре. Это

особенно существенно при малых Uвх, соизмеримых с U*.

1.2.2 Усилитель мощности с раздельным начальным смещением

Для устранения нелинейных искажений со схемы сдвига

уровня напряжения вводится раздельное смещение на базы транзисторов (см. рисунок

1.7) На диодах VD1 и VD2

создается падение напряжения U*, которое

смещает рабочую точку транзистора VТ1 влево и VT2 – вправо от начала координат (см. рисунок 1.8). Характеристика

передачи будет представлять прямую линию. Следовательно, уменьшатся нелинейные

искажения. Эти диоды всегда открыты, так как суммарное напряжение источников

питания ![]() всегда

всегда

больше, чем

входной сигнал.

больше, чем

входной сигнал.

Рассмотрим разновидность бестрансформаторного

усилителя мощности с делителем напряжения в базовой цепи (см.рисунок 1.9).

Такая схема еще называется схемой с дополнительной симметрией. Здесь R1, R2, R3 ‑ делитель

напряжения для создания смещения в классе АВ.

Рассмотрим разновидность бестрансформаторного

усилителя мощности с делителем напряжения в базовой цепи (см.рисунок 1.9).

Такая схема еще называется схемой с дополнительной симметрией. Здесь R1, R2, R3 ‑ делитель

напряжения для создания смещения в классе АВ.

Должно выполняться условие ![]() .

.

Очевидно, что средняя точка R2 имеет нулевой потенциал. Базы обоих транзисторов можно считать закороченными по переменному току и подавать входное напряжение на одну из баз. Так как сигнал подается в одной фазе на оба транзистора, то они работают поочередно. Вместо R2 обычно ставят диоды. На каждом диоде падает U*= 0,7 В, которое создает смещение, обеспечивающее режим класса АВ.

Схема включения транзисторов – с общим коллектором.

1.3 Операционный усилитель

1.3.1 Назначение и основные параметры операционных усилителей

Операционный усилитель – универсальный усилитель постоянного тока с дифференциальным входом и однотактным выходом.

Идеальный ОУ имеет следующие параметры:

-

коэффициент усиления по напряжению![]() ;

;

-

входное сопротивление![]() ;

;

-

выходное сопротивление ![]() .

.

Такие характеристики позволяют применять глубокую обратную связь (ОС), и свойства ОУ определяются только параметрами элементов цепи ОС. Используя различные ОС, можно осуществлять различные математические операции. Поэтому усилители были названы операционными.

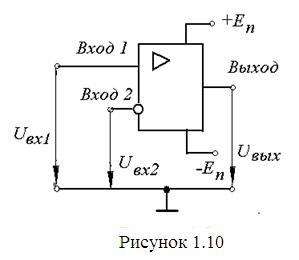

Условное обозначение ОУ приведено на рисунке 1.10.

Условное обозначение ОУ приведено на рисунке 1.10.

Здесь:

вход 1 – неинвертирующий вход, т.е. выходной сигнал совпадает по фазе с входным;

вход 2 – инвертирующий вход, т.е. выходной сигнал в противофазе с входным;

выход – однотактный;

+Еп и ‑Еп –‑ выводы двух источников питания Еп или двуполярного источника.

Реальные ОУ обычно имеют большое число выводов для подключения внешних цепей частотной коррекции, формирующих требуемый вид амплитудно-частотной характеристики (АЧХ) усилителя.

Характеристики реальных ОУ немного отличаются от идеальных.

Основные параметры реальных ОУ:

![]() а) коэффициент усиления дифференциального сигнала

а) коэффициент усиления дифференциального сигнала

![]() ;

;

б) коэффициент усиления синфазного сигнала  ;

;

в) коэффициент ослабления синфазного сигнала ОУ

в децибелах  ;

;

г) входное сопротивление Rвх обычно порядка 400 кОм (может достигать от десятков кОм до десятков МОм);

д) выходное сопротивление Rвых = 20 ¸2000 Ом;

е) амплитудно-частотная характеристика (АЧХ) – ![]() – зависимость

коэффициента усиления от частоты (линеаризованная характеристика в логарифмическом

масштабе – диаграмма Боде) приведена на

– зависимость

коэффициента усиления от частоты (линеаризованная характеристика в логарифмическом

масштабе – диаграмма Боде) приведена на

![]()

![]() рисунке 1.11,а. АЧХ ОУ представляет суммарную АЧХ

отдельных каскадов. Изменение частоты в десять раз (на декаду) приводит к

уменьшению коэффициента усиления по напряжению в десять раз, (т.е. на минус 20

дБ).

рисунке 1.11,а. АЧХ ОУ представляет суммарную АЧХ

отдельных каскадов. Изменение частоты в десять раз (на декаду) приводит к

уменьшению коэффициента усиления по напряжению в десять раз, (т.е. на минус 20

дБ).

Двухкаскадный ОУ имеет два излома АЧХ (каждый каскад вносит один излом);

ж)

фазочастотная характе-ристика (ФЧХ) ОУ – зависимость фазы сигнала от

частоты ![]() (см.

рисунок1.11,б). Каждый каскад на высоких частотах вносит фазовый сдвиг, равный минус

(см.

рисунок1.11,б). Каждый каскад на высоких частотах вносит фазовый сдвиг, равный минус

![]() .

ФЧХ запаздывает на

.

ФЧХ запаздывает на ![]() , где n – число каскадов ОУ.

, где n – число каскадов ОУ.

Для стабилизации работы ОУ требуется коррекция АЧХ и ФЧХ;

и) ![]() ‑ частота единичного усиления, т.е.

частота, при которой коэффициент усиления равен единице;

‑ частота единичного усиления, т.е.

частота, при которой коэффициент усиления равен единице;

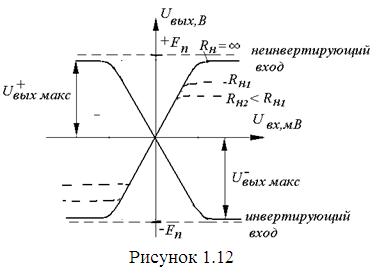

к) амплитудная характеристика или характеристика

передачи сигнала – зависимость выходного напряжения от входного ![]() приведена на рисунке 1.12.

приведена на рисунке 1.12.

Обычно![]() .

.

л) если при Uвх = 0 также и Uвых = 0, имеет место баланс ОУ.

В реальных ОУ внутри схемы может иметь место

разбаланс, из-за которого появляется ![]() при Uвх = 0 (см. рисунок 1.13);

при Uвх = 0 (см. рисунок 1.13);

м) U вх смещ нуля или начальное смещение ‑ это постоянное напряжение, подаваемое на один из входов, чтобы выходное напряжение стало равным нулю. Оно примерно равно 1...3 мВ;

н) разность входных токов ![]() ‑ 5…50 нА;

‑ 5…50 нА;

п) диапазон допустимых синфазных напряжений – это максимальное одинаковое напряжение на обоих входах, чтобы ОУ не вошел в насыщение или отсечку – 3…13 В;

1.3.2 Двухкаскадный операционный усилитель

Схема-модель двухкаскадного операционного усилителя

представлена на рисунке![]()

![]() 1.14. Входной дифференциальный

усилитель построен на транзисторах VT1 ¸ VT4.

Основные транзисторы VT1 и VT2 – p-n-p-типа.

1.14. Входной дифференциальный

усилитель построен на транзисторах VT1 ¸ VT4.

Основные транзисторы VT1 и VT2 – p-n-p-типа.

Динамическая нагрузка (транзисторы VT3 и

VT4 ‑

n-p-n-типа) представляет собой токовое зеркало или

отражатель токов. ДУ с токовым зеркалом имеет дифференциаль-ный вход и

однотактный выход. ГСТ1 в эмиттерной цепи служит для стабилизации

эмиттерного тока и уменьшения дрейфа напряжения. Каскад обеспечивает требуемые

входные параметры ОУ.

Динамическая нагрузка (транзисторы VT3 и

VT4 ‑

n-p-n-типа) представляет собой токовое зеркало или

отражатель токов. ДУ с токовым зеркалом имеет дифференциаль-ный вход и

однотактный выход. ГСТ1 в эмиттерной цепи служит для стабилизации

эмиттерного тока и уменьшения дрейфа напряжения. Каскад обеспечивает требуемые

входные параметры ОУ.

Второй каскад, построенный на составном транзисторе VT5 и VT6 по схеме с общим эмиттером, является усилителем амплитуд. Обеспечивает необходимый коэффициент усиления по напряжению ОУ. В качестве нагрузочного сопротивления каскада служит источник тока ГСТ2. Емкость СК »30 пФ ‑ для коррекции частотной характеристики. Диоды VD1 и VD2 для создания смещения начальной рабочей точки в выходном каскаде.

В выходной каскад входят: комплементарная пара транзисторов

VT7 (n-p-n-типа)

и VT8 (p-n-p-типа),

диоды VD1 и VD2,

генератор стабильного тока ГСТ2, транзистор VT6..

Выходной каскад является двухтактным усилителем мощности класса АВ.

Делитель напряжения, состоящий из ГСТ2, VD1, VD2 и

VT6,

создает смещение рабочей точки транзисторов VT7 и VT8. Причем. ![]() . Необходимое начальное смещение, как было

уже сказано, задается диодами VD1 и VD2. Эти

же диоды обеспечивают температурную стабилизацию режима покоя выходного

усилителя.

. Необходимое начальное смещение, как было

уже сказано, задается диодами VD1 и VD2. Эти

же диоды обеспечивают температурную стабилизацию режима покоя выходного

усилителя.

При отсутствии сигнала на входе ОУ UВХ = 0 ток через нагрузку IН = 0. Через транзисторы VT7 и VT8 течет небольшой начальный ток, обусловленный смещением плюс UVD1 на транзисторе VT7 и минус UVD2 – на транзисторе VT8. Диоды включены в прямом направлении и всегда открыты, так как даже при подаче положительного перепада напряжения с коллектора VT6 за счет источников напряжения питания + Еп1 и ‑ Еп2 на аноды диодов подано более положительное напряжение, чем на катоды. Можно считать, что базы обоих транзисторов закорочены по переменному току, так как сопротивление диодов по переменной составляющей близко к нулю. Транзисторы VT7 и VT8 открыты поочередно. При подаче с коллектора VT6 положительного перепада напряжения транзистор VT8 запирается, а VT7 – отпирается. Ток течет по цепи: + Еп1, кэVT7, Rн, ‑ Еп1. При подаче с коллектора VT6 отрицательного перепада напряжения транзистор VT7 запирается, а VT8 – отпирается. Ток течет по цепи: + Еп2, Rн, кэVT8, ‑ Еп2.

1.3.3 Внешние цепи

В операционных усилителях используются внешние цепи:

а) цепи коррекции частотной характеристики – частотно-зависимые RC-цепи;

б) цепи балансировки для установки нулевого напряжения на выходе при нулевом входном;

в) цепи защиты:

1) от пробоя на входе при высоком входном напряжении;

2) от короткого замыкания на выходе включается последовательно резистор примерно 400 омов;

3) от переполюсовки источника питания при неправильной полярности включения;

4) от перенапряжения источника питания;

г) цепи обратной связи.

Обычно в ОУ используется отрицательная обратная

связь, т.к. без нее даже при ![]() коэффициент усиления стремится к

бесконечности и

коэффициент усиления стремится к

бесконечности и ![]() может

достичь предельного значения.

может

достичь предельного значения.

Отрицательная обратная связь позволяет:

создать схему с заданными функциями;

достичь нужного коэффициента усиления;

повысить стабильность и устойчивость схемы;

добиться необходимых ![]() и

и ![]() ;

;

уменьшить линейные и нелинейные искажения.

Рассмотрим усилители сигналов и решающие усилители.

1.3.4 Инвертирующий усилитель

В

схеме (см. рисунок 1.15)

примем допущения: ![]() ;

; ![]() . (1.1)

. (1.1)

Так как![]() и

и  , то

, то ![]() . Следовательно точку А можно считать

закороченной на землю.

. Следовательно точку А можно считать

закороченной на землю.

По первому закону Кирхгофа ![]() , а так как

, а так как ![]() , то

, то ![]() и, следовательно,

и, следовательно, ![]() .

.

Определим коэффициент усиления инвертирующего усилителя

![]() . (1.2)

. (1.2)

Из (1.2) видно, что коэффициент усиления инвертирующего усилителя не зависит от параметров ОУ, а определяется только элементами обратной связи. Здесь имеет место параллельная отрицательная обратная связь по напряжению.

Если ![]() , то усилитель (см. рисунок 1.15) является

инвертором.

, то усилитель (см. рисунок 1.15) является

инвертором.

Для симметрирования (уравнивания) входных токов ставится резистор R, который определяется как параллельно соединенные Rос и R1

![]() .

.

1.3.5 Неинвертирующий усилитель

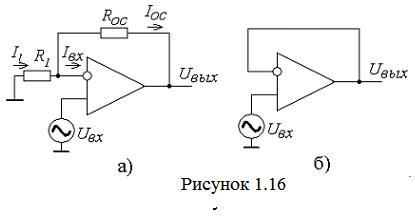

На рисунке 1.16,а

представлена схема неинвертирующего усилителя. Цепь Rос–R1 создает

последовательную отрицательную обратную связь (ООС) по напряжению. Входной

сигнал подается на неинвертирующий вход. Допустим, что выполняются условия (1.1).

Тогда

На рисунке 1.16,а

представлена схема неинвертирующего усилителя. Цепь Rос–R1 создает

последовательную отрицательную обратную связь (ООС) по напряжению. Входной

сигнал подается на неинвертирующий вход. Допустим, что выполняются условия (1.1).

Тогда ![]() и

и ![]() . Из рисунка 1.16,а

находим

. Из рисунка 1.16,а

находим

Uвх = I1R1, Uвых = I1 (R1+Rос), следовательно, коэф-фициент усиления неинвертирующего

усилителя равен ![]() .

.

Если ![]() и

и ![]() (см. рисунок1.16,б), то это повторитель

напряжения. Имеет место 100% последовательная ООС по напряжению.

(см. рисунок1.16,б), то это повторитель

напряжения. Имеет место 100% последовательная ООС по напряжению.

Сигнал на выходе повторяет входной сигнал.

1.3.6 Решающие усилители

1.3.6.1 Инвертирующий сумматор (см. рисунок 1.17)

Из рисунка 1.17 следует, что

Из рисунка 1.17 следует, что ![]() , так как

, так как![]() ,

,  Если

Если ![]() , то

, то

![]() .

.

1.3.6.2 Интегратор инвертирующий (см. рисунок 1.18)

Из условия (1.1) следует, что ![]() . Ток через конденсатор равен

. Ток через конденсатор равен

![]() , входной ток

, входной ток ![]() .

.

Так как выполняется условие (1.1),

Так как выполняется условие (1.1), ![]() и

и ![]() . Следовательно,

. Следовательно,

![]() ;

;

![]()

![]() .

.

Отсюда, проинтегрировав, получим

.

.

![]() линейно зависит от

линейно зависит от ![]() , т.е. схема интегратора является

простейшей схемой генератора линейно изменяющегося напряжения.

, т.е. схема интегратора является

простейшей схемой генератора линейно изменяющегося напряжения.

1.3.6.3 Дифференциатор инвертирующий (см. рисунок 1.19)

Ток через Rос равен ![]() ,

,

ток через емкость С равен ![]() .

.

Так как входной ток равен нулю, то![]() и

и ![]() .

.

Отсюда ![]() .

.

1.3.6.4 Логарифмирующий усилитель (см. рисунок 1.20).

Здесь

Здесь ![]()

где ![]() ,

, ![]() .

.

![]() Следовательно,

Следовательно,  .

.

Прологарифмировав, получаем

1.3.7 Нелинейный режим работы ОУ

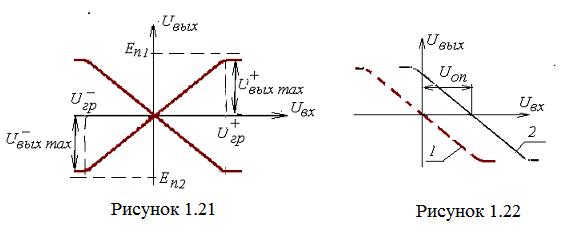

Если ![]() (см. рисунок 1.21), то ОУ работает в

линейном режиме, при

(см. рисунок 1.21), то ОУ работает в

линейном режиме, при ![]() – в нелинейном

ключевом или импульсном режиме.

– в нелинейном

ключевом или импульсном режиме.

При

подаче напряжения на один из входов ОУ передаточная характеристика по

второму входу смещается на это же значение. Например,

на неинвертирующий вход ОУ (см. рисунок 1.22) подано напряжение Uоп, тогда

характеристика по инвертирующему входу (кривая 1) сместится на значение Uоп вправо (кривая 2).

При

подаче напряжения на один из входов ОУ передаточная характеристика по

второму входу смещается на это же значение. Например,

на неинвертирующий вход ОУ (см. рисунок 1.22) подано напряжение Uоп, тогда

характеристика по инвертирующему входу (кривая 1) сместится на значение Uоп вправо (кривая 2).

1.3.8 Компаратор аналоговый

Компаратор аналоговый (см. рисунок 1.23,а) применяется для сравнения аналогового сигнала с опорным напряжением.

На рисунке 1.23,а на неинвертирующий вход подано опорное напряжение Uоп, на инвертирующий вход ‑ аналоговый сигнал Uвх.

При этом выполняются условия (см. рисунок 1.23,б – передаточная характеристика ОУ):

если: Uвх<

Uоп,

то ![]() ,

,

если:Uвх>

Uоп,

то ![]() .

.

При равенстве Uвх = Uоп, Uвых= 0.

Так как коэффициент усиления ОУ сотни тысяч, то выход компаратора

переключается на противоположное значение.

При равенстве Uвх = Uоп, Uвых= 0.

Так как коэффициент усиления ОУ сотни тысяч, то выход компаратора

переключается на противоположное значение.

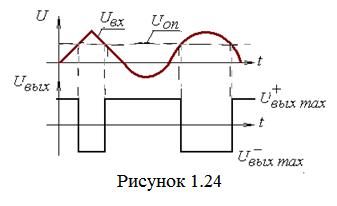

На рисунке 1.24 приведены временные диаграммы входных и выходного напряжений компа-ратора, которые иллюстрируют его работу.

1.3.9 Триггер Шмидта

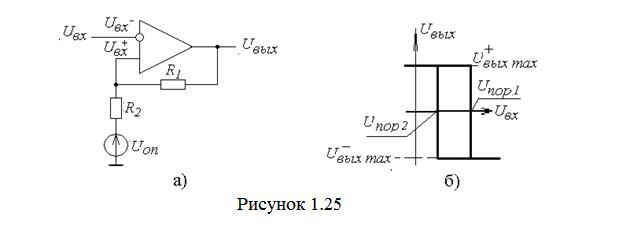

Триггер Шмидта имеет два состояния устойчивого равновесия и преобразует аналоговый сигнал в импульсный.

На рисунке 1.25,а приведена принципиальная схема триггера, на рисунке 1.25,б – его передаточная характеристика.

Резисторы ![]() и

и ![]() создают положительную обратную связь,

которая обеспечивает лавинообразное переключение выхода триггера из

положительного в отрицательное и наоборот. Пороговые напряжения (см. рисунок

1.25,б), при которых происходит переключение триггера, определяются как:

создают положительную обратную связь,

которая обеспечивает лавинообразное переключение выхода триггера из

положительного в отрицательное и наоборот. Пороговые напряжения (см. рисунок

1.25,б), при которых происходит переключение триггера, определяются как:

![]() Из рисунка 1.26 видно, что при Uвх = 0, на выходе

Из рисунка 1.26 видно, что при Uвх = 0, на выходе ![]() , так как на

неинвертирующем входе Uвх+ Uоп>0.

Когда Uвх

возрастет до

, так как на

неинвертирующем входе Uвх+ Uоп>0.

Когда Uвх

возрастет до ![]() ,

равное смещению Uвх+ триггер переключается в

,

равное смещению Uвх+ триггер переключается в ![]() . За счет положительной обратной

связи

. За счет положительной обратной

связи ![]() ,

, ![]() теперь смещение на Uвх+ станет равным

теперь смещение на Uвх+ станет равным ![]() . Когда Uвх уменьшится до

. Когда Uвх уменьшится до ![]() , произойдет обратное переключение триггера

в

, произойдет обратное переключение триггера

в ![]() и т.д.

и т.д.

Так как пороговое напряжение меняется от одного значения к другому скачком, триггер является управляемым компаратором,

1.4 Генераторы электрических сигналов

1.4.1 RC-генератор синусоидальных колебаний

Достоинствами RC-генератора синусоидальных колебаний – на ОУ являются простота, дешевизна, малые масса и габариты и недостатком – невысокая стабильность частоты генерации.

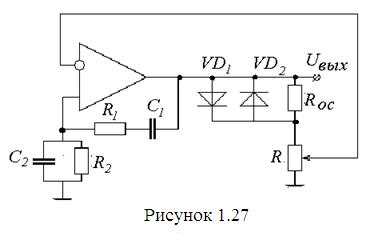

Рассмотрим схему генератора с мостом Вина (см. рисунок 1.27).

![]() Мост Вина (элементы R1, R2, C1, C2

) создает положительную обратную

связь. Коэффициент передачи звена обратной связи равен

Мост Вина (элементы R1, R2, C1, C2

) создает положительную обратную

связь. Коэффициент передачи звена обратной связи равен

на квазирезонансной частоте

на квазирезонансной частоте ![]() .

.

Если

Если ![]() и

и ![]() , то

, то ![]() ,

, ![]() .

.

На рисунке 1.28 приведены АЧХ и ФЧХ

моста Вина, из которого видно, что на квазирезонансной частоте ![]() фазовый сдвиг

фазовый сдвиг ![]() равен нулю, а

коэффициент передачи звена обратной связи

равен нулю, а

коэффициент передачи звена обратной связи![]() равен 1/3. Таким образом выполняется

условие баланса фаз

равен 1/3. Таким образом выполняется

условие баланса фаз ![]() ,

так как фазовый сдвиг усилителя

,

так как фазовый сдвиг усилителя ![]() также равен нулю, потому что сигнал обратной связи подан

на неинвертирующий вход.

также равен нулю, потому что сигнал обратной связи подан

на неинвертирующий вход.

На схеме (см. рисунок 1.27) сопротивление R

включено для подстройки глубины отрицательной обратной связи, которая

необходима для выполнения условия баланса амплитуд ![]() .

Встречно-параллельные диоды VD1 и VD2 включены

для стабилизации амплитуды выходного сигнала. При слишком больших Uвых диоды попеременно

входят в состояние прямой проводимости и увеличивают амплитуду сигнала

отрицательной обратной связи, уменьшая коэффициент усиления сигнала.

.

Встречно-параллельные диоды VD1 и VD2 включены

для стабилизации амплитуды выходного сигнала. При слишком больших Uвых диоды попеременно

входят в состояние прямой проводимости и увеличивают амплитуду сигнала

отрицательной обратной связи, уменьшая коэффициент усиления сигнала.

1.4.2 Генераторы релаксационных колебаний

1.4.2.1 Автоколебательный мультивибратор

Основными свойствами интегральных операционных

усилителей (ОУ), используемых при построении импульсных генераторов,

является большое входное (сотни килоом) и малое (десятки омов) выходное

сопротивление, большой (сотни тысяч) коэффициент усиления и наличие двух

парафазных входов. Полярность выходного напряжения ОУ определяется

большим из напряжений U+вх и ![]() вх на

неинвертирующем и инвертирующим входах соответственно.

вх на

неинвертирующем и инвертирующим входах соответственно.

Принцип построения генераторов прямоугольных импульсов на ОУ основан на получении замкнутой резисторной или резисторно-емкостной цепи положительной обратной связи (ПОС) при соединении выхода ОУ с его неинвертирующим входом. ПОС обеспечивает возникновение лавинообразных процессов.

Рассмотрим работу автоколебательного мультивибратора

на ОУ, в котором ПОС обеспечивается делителем напряжения R1, R2 (см. рисунок 1.29,а)

от выхода к неинвертирующему входу. Переключение мультивибратора из одного

квазиустойчивого равновесия в другое происходит за счет релаксационного

изменения ![]() вх.

вх.

Если в момент t=0 (см. рисунок 1.29,б) включить источник питания ОУ,

начинает расти выходное напряжение Uвых, за счет делителя R1, R2 напряжение на неинвертирующем входе U+вх тоже возрастает, а это приводит к еще большему

увеличению Uвых. В

результате лавинообразного процесса выходное напряжение Uвых скачкообразно

увеличивается до Е+, а входное U+вх до

gE+, где g-= R2/(R1 +R2), Е

– напряжение источника питания интегрального операционного усилителя. ![]() вх при этом измениться не успевает и равно нулю.

Начинается заряд конденсатора С через R. Это

приводит к увеличению

вх при этом измениться не успевает и равно нулю.

Начинается заряд конденсатора С через R. Это

приводит к увеличению ![]() вх,

стремящегося к Е+ с постоянной времени tзар

=RC . В момент t1, когда

вх,

стремящегося к Е+ с постоянной времени tзар

=RC . В момент t1, когда ![]() вх = U+вх =gE+

скачкообразно изменяется режим и

вх = U+вх =gE+

скачкообразно изменяется режим и  Uвых изменяется до

Uвых изменяется до ![]() , а U+вх =g

, а U+вх =g![]() . Процесс этот происходит лавинообра-зно.

. Процесс этот происходит лавинообра-зно.

Конденсатор С, соединенный положи-тельной

обкладкой к ![]() , а отрицательной – к корпусу, стремится

перезарядиться до

, а отрицательной – к корпусу, стремится

перезарядиться до ![]() по цепи: +С, R, выход ОУ,

–С. В момент t2,

когда

по цепи: +С, R, выход ОУ,

–С. В момент t2,

когда ![]() вх =–g

вх =–g![]() , снова

происходит опроки-дывание.

, снова

происходит опроки-дывание.

Процессы эти периодически повторяются.

Длительность импульса равна

![]() .

.

Период повторения импульсов

![]() .

.

Скважность Q=T/tu =2.

Для построения мультивибратора со скважностью Q>2

необходимо, чтобы цепь заряда отличалась от цепи разряда (см. рисунок1.30). Заряд

идет по цепи: Uвых,

R’, VD1, С, корпус, разряд – по

цепи: +С, VD2, R’’, корпус, –С. Длительность положительного

импульса

Для построения мультивибратора со скважностью Q>2

необходимо, чтобы цепь заряда отличалась от цепи разряда (см. рисунок1.30). Заряд

идет по цепи: Uвых,

R’, VD1, С, корпус, разряд – по

цепи: +С, VD2, R’’, корпус, –С. Длительность положительного

импульса

![]() .

.

Длительность отрицательного импульса

![]()

![]() .

.

Скважность ![]()

1.4.2.2 Генератор линейно изменяющегося напряжения на операционном усилителе (ГЛИН).

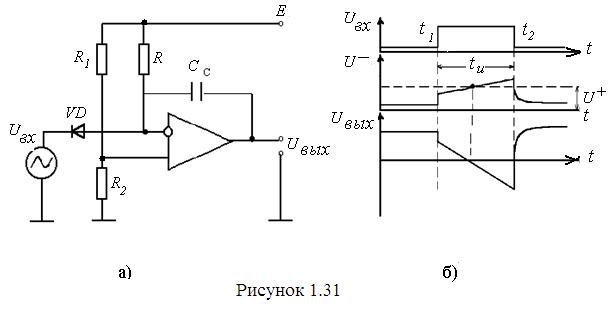

На

рисунке 1.31,а в схеме ГЛИН интегрирующая RC - цепочка включена в цепь отрицательной обратной связи ОУ.

Управляется ГЛИН импульсами положительной полярности Uвх

с длительностью tи, равной времени прямого хода пилы.

Входные импульсы подаются на базу диода VD,

эмиттер которого соединен с инвертирующим входом ОУ.

На

рисунке 1.31,а в схеме ГЛИН интегрирующая RC - цепочка включена в цепь отрицательной обратной связи ОУ.

Управляется ГЛИН импульсами положительной полярности Uвх

с длительностью tи, равной времени прямого хода пилы.

Входные импульсы подаются на базу диода VD,

эмиттер которого соединен с инвертирующим входом ОУ.

Исходное состояние генератора (t < t1),

при Uвх

= 0 диод VD открыт, течет ток от источника

питания через R, диод VD,

источник сигнала Uвх, корпус. ![]() . Напряжение на

неинвертирующем входе

. Напряжение на

неинвертирующем входе ![]() где

где ![]() .

.

Напряжение ![]() превышает

превышает ![]() настолько, чтобы перевести ОУ в режим

ограничения, при котором

настолько, чтобы перевести ОУ в режим

ограничения, при котором ![]() . Конденсатор С при этом заряжен до напряжения

UC (0) = E

. Заряд конденсатора идет по цепи Е+, выход ОУ, С,

VD, источник сигнала Uвх, корпус

. Конденсатор С при этом заряжен до напряжения

UC (0) = E

. Заряд конденсатора идет по цепи Е+, выход ОУ, С,

VD, источник сигнала Uвх, корпус ![]() .

.

Формирование рабочего хода пилы Tпр .

При подаче в момент t1

(см. рисунок 1.31,б) запускающего входного импульса длительностью tu диод VD

запирается. Скачок положительного напряжения ![]() от источника Е переводит ОУ в

линейный усилительный режим и ОУ начинает интегрировать постоянное

напряжение Е, являющееся для него входным. Положительный скачок на входе

от источника Е переводит ОУ в

линейный усилительный режим и ОУ начинает интегрировать постоянное

напряжение Е, являющееся для него входным. Положительный скачок на входе

![]() в момент t1 дает отрицательный скачок на выходе.

в момент t1 дает отрицательный скачок на выходе.

Заряженный конденсатор С начинает

медленно разряжаться, вызывая увеличение напряжения ![]() , которое обусловливает

уменьшение выходного напряжения Uвых.

, которое обусловливает

уменьшение выходного напряжения Uвых.

Длительность рабочего хода Tпр

= tи и постоянная времени RC цепи должны быть рассчитаны так, чтобы к концу

интервала tи конденсатор успел разрядиться до

нуля и перезарядиться до ![]() .

.

Формирование обратного хода пилы Tобр .

В момент t2

окончания входного импульса отпирается диод VD. ![]() скачкообразно

уменьшается до

скачкообразно

уменьшается до ![]() ,

при котором ОУ выходит из режима усиления.

,

при котором ОУ выходит из режима усиления. ![]() увеличивается до Е+,

конденсатор, заряженный до

увеличивается до Е+,

конденсатор, заряженный до ![]() с большой скоростью, определяемой

сопротивлением открытого диода VD, разряжается

до нуля и заряжается до исходного напряжения UС

(t) =

с большой скоростью, определяемой

сопротивлением открытого диода VD, разряжается

до нуля и заряжается до исходного напряжения UС

(t) = ![]() .

.

Определим необходимую постоянную времени RC при заданном Tпр.

Так как ток перезаряда конденсатора ![]() почти постоянен и равен

почти постоянен и равен

![]() , то за время прямого хода пилы Tпр

напряжение на конденсаторе изменится на величину, примерно равную 2Е.

Поэтому

, то за время прямого хода пилы Tпр

напряжение на конденсаторе изменится на величину, примерно равную 2Е.

Поэтому ![]() ,

откуда

,

откуда ![]() , или

для

, или

для ![]()

![]() .

.

Таким образом при известном Tпр, задаваясь С, можно определить значение R или наоборот.

Время восстановления режима работы генератора или обратного хода пилы Tобр.

![]()

![]()

![]()

где ![]() - сопротивление открытого диода.

- сопротивление открытого диода.

Коэффициент нелинейности ![]() .

.

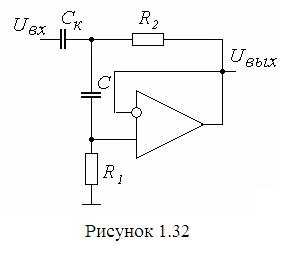

1.5 Гиратор

Гиратор – это электрическая схема, в которой в обратную связь ОУ включена RC- цепь, имитирующая катушку индуктивности. Иногда гираторы называют синтезируемыми индуктивностями. Такие «активные катушки индуктивности» позволяют реализовать большую индуктивность в небольшом легком недорогом корпусе, т.е. эту схему можно использовать в качестве обычной катушки.

Основной недостаток – рабочая частота fраб. не превышает несколько килогерц.

Идея работы гиратора – используя напряжение на конденсаторе Uс, заставить входное напряжение Uвх и входной ток Iвх вести себя подобно напряжению и току в катушке индуктивности (см. рисунок 1.32).

Известно,

что при увеличении частоты индуктивное сопротивление

Известно,

что при увеличении частоты индуктивное сопротивление ![]() возрастает и растет напряжение на

катушке индуктивности. Повторитель напряжения выходное напряжение

возрастает и растет напряжение на

катушке индуктивности. Повторитель напряжения выходное напряжение ![]() в схеме гиратора

воспроизводит на сопротивлении

в схеме гиратора

воспроизводит на сопротивлении ![]() - входе ОУ. При увеличении частоты w напряжение на конденсаторе С Uс уменьшается

вместе с

- входе ОУ. При увеличении частоты w напряжение на конденсаторе С Uс уменьшается

вместе с ![]() = (1

/ w С).

Следовательно, входное

= (1

/ w С).

Следовательно, входное

напряжение

UR1, а

вместе с ним и Uвых

повторителя увеличиваются. Выходное напряжение повторителя Uвых через

сопротивление R2

подается обратно на вход и напряжение на входе растет с увеличение частоты,

т.е. ведет себя аналогично напряжению на катушке индуктивности. Сопротивление ![]() следует выбирать как

можно меньше. Оно выбирается обычно равным минимальному сопротивлению нагрузки

данного операционного усилителя (около 1 кОма). Сопротивление

следует выбирать как

можно меньше. Оно выбирается обычно равным минимальному сопротивлению нагрузки

данного операционного усилителя (около 1 кОма). Сопротивление ![]() должно быть намного

больше, чем

должно быть намного

больше, чем ![]() ,

но не больше, чем 200

,

но не больше, чем 200 ![]() и

и ![]() операционного усилителя. При заданной

величине индуктивности L, используя соотношение

операционного усилителя. При заданной

величине индуктивности L, используя соотношение ![]() можно найти C

можно найти C

![]()

Добротность

гиратора определяется по формуле ![]() .

.

2 Схемотехника цифровых устройств

2.1 Основные логические операции и логические элементы

Логические функции ‑ функции, которые принимают два значения:

F=0, если сообщение ложное,

F=1, если сообщение истинное.

Логические операции описывают связь между логическими функциями.

Электрические схемы, реализующие элементарные логические операции, называются логическими элементами (ЛЭ).

Существуют 3 простейшие логические операции НЕ, ИЛИ, И:

а) операция НЕ - логическое отрицание,

инверсия.

а) операция НЕ - логическое отрицание,

инверсия.

![]() (F равно не А)

(F равно не А)

ЛЭ, выполняющий операцию НЕ, называется инвертором (см. рисунок 2.1).

б) операция ИЛИ ‑ логическое сложение,

дизъюнкция.

б) операция ИЛИ ‑ логическое сложение,

дизъюнкция.

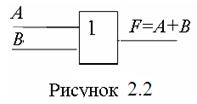

F=АÚВ, либо F=А+В (F есть А или В).

ЛЭ, выполняющий операцию ИЛИ, называется сборкой или дизъюнктором (см. рисунок2.2).

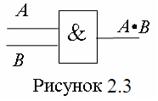

в) операция “И”- логическое умножение или конъюнкция.

F=A

F=A![]() B

(F есть А и В);

B

(F есть А и В);

F=AÙB.

Логический элемент, выполняющий операцию И называется схемой совпадения, или конъюнктором (см. рисунок 2.3).

Этот набор элементов И, НЕ, ИЛИ называется основным базисом или основной функционально полной системой элементов. Т.е. с помощью только этих элементов можно создать любую логическую схему.

Более широко в схемотехнике используются элементы других базисов ‑ двухступенчатые ИЛИ-НЕ, И-НЕ:

а) стрелка Пирса, или отрицание дизъюнкции, или

операция ИЛИ-НЕ

а) стрелка Пирса, или отрицание дизъюнкции, или

операция ИЛИ-НЕ

А¯В = ![]() .

.

Условное обозначение приведено на рисунке 2.4. Логический элемент называется элементом Пирса.

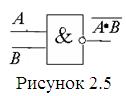

б) штрих Шеффера, или отрицание конъюнкции, или операция И-НЕ

А½В = ![]() .

.

Условное обозначение приведено на рисунке 2.5. Логический элемент называется элементом Шеффера.

С помощью только одного типа микросхем ИЛИ-НЕ,

либо И-НЕ можно построить любую логическую схему, т.е. каждая из них

является основным базисом.

С помощью только одного типа микросхем ИЛИ-НЕ,

либо И-НЕ можно построить любую логическую схему, т.е. каждая из них

является основным базисом.

Самым распространенным является элемент Шеффера И-НЕ.

Также широкое применение нашли многоступенчатые

логические элементы:

Также широкое применение нашли многоступенчатые

логические элементы:

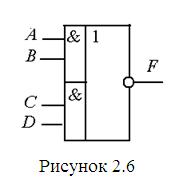

а) 2И-ИЛИ-НЕ, выполняющее операцию ![]() . Условное обозначение

приведено на рисунке 2.6;

. Условное обозначение

приведено на рисунке 2.6;

б) исключающее ИЛИ, или сумма по модулю два, или функция неравнозначности имеет вид

F =![]() Это

означает, что F равно либо A, либо B.

Логический элемент исключающее ИЛИ иногда называют элементом типа «что-нибудь,

но не все». Символ

Это

означает, что F равно либо A, либо B.

Логический элемент исключающее ИЛИ иногда называют элементом типа «что-нибудь,

но не все». Символ ![]() (псевдоплюс)

означает, что входы А и В связаны логической функцией исключающее

ИЛИ.

(псевдоплюс)

означает, что входы А и В связаны логической функцией исключающее

ИЛИ.

Из алгебры логики известно:

![]() ;

; ![]()

![]() ;

; ![]() .

.

Т а б л и ц а 2.1

|

А |

В |

А |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Таблица истинности для элемента исключающее ИЛИ приведена в таблице 2.1.

Из таблицы видно, что, если на какой-либо из входов (но не на все) подана логическая единица, то на выходе также появляется единица. Условное обозначение элемента неравнозначности приведено на рисунке 2.7,а. Поскольку этот элемент выполняет операцию сложения по модулю 2, то его обозначают так же, как на рисунке 2.7,б;

![]()

в) исключающее ИЛИ-НЕ, или функция равнозначности имеет вид

![]() . Это

означает, что F равно инверсии либо A, либо B.

. Это

означает, что F равно инверсии либо A, либо B.

Таблица истинности для элемента исключающее ИЛИ-НЕ приведена в таблице 2.2. Условное обозначение элемента приведено на рисунке 2.8.

Т а б л и ц а 2.2

|

А |

В |

|

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Алгебра логики является алгеброй состояний и позволяет:

а) описывать работу электронного устройства в виде логических функций;

б) от уравнений переходить к электронным схемам;

в) синтезировать оптимальные схемы.

Порядок выполнения операций: НЕ ‑ И – ИЛИ.

Операции деления и вычитания не используются, могут использоваться скобки.

Кроме аксиом алгебры логики для преобразования функций широко используются формулы де Моргана

![]() ;

;

![]() .

.

2.2 Логические интегральные схемы

2.2.1Основные параметры логических интегральных микросхем

а) входное U1вх и выходное U1вых напряжения логической единицы – значение высокого уровня напряжения на входе и выходе микросхемы;

б) входное U0вх и выходное U0вых напряжение логического нуля – значение низкого уровня напряжения на входе и выходе микросхемы;

в) входной I1вх и выходной I1вых токи логической единицы, входной I0вх и выходной I0вых токи логического нуля;

г)

логический перепад сигнала ![]() ;

;

д) пороговое напряжение Uпор вх – напряжение на входе, при котором состояние микросхемы изменяется на противоположное;

е)входное сопротивление логической ИМС – отношение приращения входного напряжения к приращению входного тока (различают R0вх и R1вх), выходное сопротивление – отношение приращения выходного напряжения к приращения выходного тока (различают R0вых и R1вых);

ж)статическая помехоустойчивость – максимально допустимое напряжение статической помехи по высокому U1пом и низкому U0пом уровням входного напряжения, при котором еще не происходят изменения уровня выходного напряжения микросхемы;

и) средняя потребляемая мощность Pпотр ср = (P0потр + Р1потр)/2 , где P0потр и Р1потр – мощности, потребляемые микросхемой в состоянии соответственно логического нуля и единицы на выходе;

к) коэффициент объединения по входу Коб, показывающий, какое число аналогичных логических ИМС можно подключить к входу данной схемы, и определяющий максимальное число входов логической ИМС;

л) коэффициент разветвления по выходу Кразв, показывающий какое количество аналогичных нагрузочных микросхем можно подключить к выходу данной ИМС, и характеризующий нагрузочную способность логической ИМС.

Цифровые интегральные схемы предназначены для обработки, преобразования и хранения цифровой информации. Они выпускаются сериями. Внутри каждой серии имеются объединенные по функциональному признаку группы устройств: логические элементы, триггеры, регистры, счетчики, дешифраторы, шифраторы, мультиплексоры, демультиплексоры и т.д. Чем шире функциональный состав серии, тем большими возможностями может обладать цифровое устройство, выполненное на базе микросхем данной серии. Микросхемы, входящие в состав каждой серии, имеют единое конструктивно-технологическое исполнение, одинаковое напряжение питания и одинаковые уровни сигналов логического нуля и логической единицы. Все это делает микросхемы одной серии совместимыми.

Основой каждой серии цифровых микросхем является базовый логический элемент. Как правило, базовые логические элементы выполняют операции И—НЕ, либо ИЛИ—НЕ и по принципу построения делятся на следующие основные типы: элементы резистивно-транзисторной логики (РТЛ), диодно-транзисторной логики (ДТЛ), транзисторно-транзисторной логики (ТТЛ), эмиттерно-связанной логики (ЭСЛ), интегрально-инжекционной логики (ИИЛ), базовые элементы которых выполнены на биполярных транзисторах. Микросхемы на комплементарных МДП-структурах (КМДП) используют пары МДП-транзисторов со структурой металл - диэлектрик – полупроводник с каналами р- и n-типов.

2.2.2 Схема ДТЛ – диодно-транзисторной логики

Основная схема ДТЛ приведена на рисунке 2.16,а. Здесь диоды VD1, VD2, VD3 и резистор R1 представляют собой конъюнктор (И), элементы VT, R2, R3 ‑ инвертор (НЕ), смещающие диоды VDСМ1, VDСМ2 – осуществляют связь между логическими элементами И и НЕ и смещают (понижают) потенциал базы VT относительно напряжения U1. Резистор R2 служит для подачи смещения ЕСМ на VT и гарантированного удерживания его в запертом состоянии при открытых входных диодах и как дополнительная цепь обратного тока базы при запирании транзистора.

При высоком уровне напряжения на входе UA = UB = UC = U1, диоды VD1…VD3

заперты, повышается потенциал точки U1, отпираются диоды смещения VDСМ1,

VDСМ2,

течет ток базы VT, и транзистор входит в насыщение. Напряжение на

коллекторе UF падает до

нуля, т.е. F = 0.

При высоком уровне напряжения на входе UA = UB = UC = U1, диоды VD1…VD3

заперты, повышается потенциал точки U1, отпираются диоды смещения VDСМ1,

VDСМ2,

течет ток базы VT, и транзистор входит в насыщение. Напряжение на

коллекторе UF падает до

нуля, т.е. F = 0.

Если хотя бы на одном из входов низкий уровень напряжения UA или UB или UC равен U0, отпирается соответствующий диод, понижается потенциал U1, запираются диоды смещения VDCМ1, VDСМ2. На базе транзистора VT низкое напряжение, который запирается. UВЫХ = UF = U1, т.е. на выходе элемента появляется логическая единица.

Если отбросить часть схемы (см. рисунок 2.16,а), изображенную пунктиром, она превращается в инвертор. На рисунке 2.16,б приведена ее передаточная характеристика UF = f(UA),

Если напряжение на входе А равно 0, то диод VD1 смещен в прямом направлении и напряжение U1 равно +0,6 В. Эта величина недостаточна для открывания диодов VDСМ1, VDСМ2 и перехода база-эмиттер транзистора VТ. Поэтому ток I1 течет через диод VD1, источник сигнала UA и на землю. Транзистор VТ закрыт, при этом UF = +5 В. Если UA увеличивается, то U1 также растет до тех пор, пока не достигнет 1,2 В. В этот момент VDСМ1, VDСМ2, VТ открываются и ток I1 течет через транзистор VТ и переводит его в насыщение. Дальнейшее увеличение напряжение UA запирает диод VD1. но не может повлиять на величину U1 или состояние транзистора VТ. Из графика видно, что интервалы напряжений, соответствующие логическим состояниям 0 и 1, примерно равны 0 ≤ U0 ≤ 1,2 B, 1,5 ≤ U1 ≤ 5 В.

Практически U0 обычно меньше 0,4 В, а U1 очень близко к 5 В, что обеспечивает хороший шумовой запас по постоянному току.

Если на вход подано напряжение, соответствующее логической 1, то диод VD1 смещен в обратном направлении и, следовательно, потребляет минимальную мощность с выхода предыдущей схемы. Однако, если на входе поддерживается напряжение логического 0, то ток I1 должен течь из входной клеммы элемента через насыщенный транзистор на землю. Это соответствует одной единичной нагрузке. Если к одному выходу подсоединено n входов, то насыщенный транзистор должен пропускать ток, в n раз больше чем I1. Если n увеличивается, то будет расти и напряжение UА, что эквивалентно увеличению напряжения выходного транзистора. Этот эффект приведен на рисунке 2.16,б, где передаточная характеристика изображена для случая одной выходной единичной нагрузки и для случая восьми единичных нагрузок (максимально допустимое количество для базового элемента ДТЛ).

Если к схеме, в соответствии с рисунком 2.16,а,

добавить диоды VD2, VD3, то

напряжение UF будет

соответствовать логической 1, если хотя бы один из входов будет в состоянии

логического нуля. Логический нуль на выходе можно получить только в том случае,

если на всех входах присутствует напряжение логической единицы, т.е. логическая

операция, выполняемая данной схемой, имеет вид: ![]() , что соответствует операции И-НЕ.

Добавлением дополнительных диодов для расширения объема входа число входов в

базовом элементе ДТЛ И-НЕ может быть доведено до 20.

, что соответствует операции И-НЕ.

Добавлением дополнительных диодов для расширения объема входа число входов в

базовом элементе ДТЛ И-НЕ может быть доведено до 20.

Задержка передачи для типичного элемента ДТЛ составляет 30 нс. Это сравнительно большая величина во многих случаях оказывается вполне приемлемой.

2.2.3 Схемы ТТЛ ‑ транзисторно-транзисторной логики

2.2.3.1 Схема ТТЛ ‑ транзисторно-транзисторной логики с простым инвертором

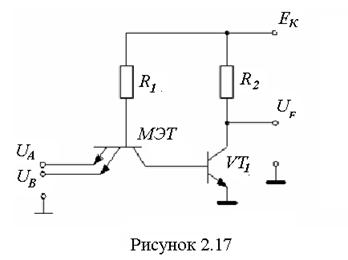

Схема транзисторно-транзисторной логики

(см. рисунок 2.17) – результат развития ДТЛ.

Матрица диодов заменяется многоэмиттерным транзистором (МЭТ).

Схема транзисторно-транзисторной логики

(см. рисунок 2.17) – результат развития ДТЛ.

Матрица диодов заменяется многоэмиттерным транзистором (МЭТ).

Это интегральный прибор, объединяющий функции диодных логических схем и транзисторного усилителя. МЭТ имеет несколько эмиттеров, расположенных так, что прямое взаимодействие между ними исключается. МЭТ позволяет увеличить быстродействие, снизить потребляемую мощность и усовершенствовать технологию изготовления микросхем. Так как МЭТ был разработан лишь на этапе интегральной схемо-техники, то аналогов ТТЛ на дискретных компонентах не было.

ТТЛ относится к потенциальным элементам. При построении схем ЭВМ на их основе они соединяются потенциальными связями, т.е. без конденсаторов и трансформаторов.

Напряжение логической единицы U1 = 2,4 В, напряжение логического нуля U0 < 0,4 В.

Диоды VD1…VD3 в схеме рисунка 2.16 заменены эмиттерными переходами МЭТ, а DСМ1, DСМ2 – коллекторными переходами МЭТ. Тогда отпадает необходимость в ЕСМ и R2.

Базовый элемент ТТЛ так же, как и ДТЛ выполняет логическую операцию И-НЕ. При низком уровне сигнала (логический 0) хотя бы на одном из входов многоэмиттерного транзистора МЭТ последний находится в состоянии насыщения, а VT1 закрыт. На выходе схемы присутствует высокий уровень напряжения (логическая единица). При высоком уровне сигнала на всех входах МЭТ работает в активном инверсном режиме (эмиттерный переход смещен в обратном направлении, а коллекторный – в прямом), VT1 находится в состоянии насыщения. На выходе схемы низкий уровень сигнала, т.е. ноль.

Описанный здесь базовый элемент ТТЛ, несмотря на упрощенную технологию изготовления, не нашел широкого применения из-за низкой помехоустойчивости, малого быстродействия при работе на емкостную нагрузку и малой нагрузочной способности.

Низкая нагрузочная способность или малый коэффициент разветвления объясняется следующим образом. Через R2, при запертом транзисторе VT1, текут входные токи нагрузочных элементов, и, если их много, увеличивается падение напряжения на коллекторной нагрузке R2. Уменьшается напряжение на коллекторе VT1, т.е. значение верхнего логического уровня, нарушается работа схемы. Поэтому используется ТТЛ со сложным инвертором.

2.2.3.2 Схема ТТЛ со сложным инвертором

2.2.3.2 Схема ТТЛ со сложным инвертором

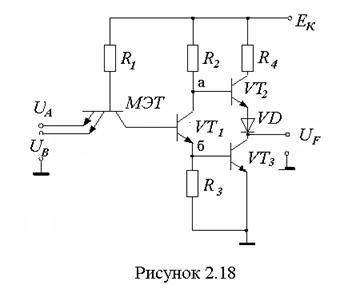

Схема ТТЛ со сложным инвертором (см. рисунок 2.18) состоит из двух частей:

а) конъюнктора И, включающего многоэмиттерный транзистор МЭТ и резистор R1. Схема И может иметь от 2 до 8 входов (увеличение количества входов расширяет логические возможности ТТЛ);

б) сложного инвертора НЕ, включающего в себя VT1, VТ2, VТ3, VD, R2, R3, R4.

В свою очередь сложный инвертор можно рассматривать, состоящим из фазорасщепля-ющего каскада и выходного усилителя.

Фазорасщепляющий или фазоинверсный каскад (состоит из VT1, R2, R3) служит для управления транзисторами VТ2 и VТ3. Транзистор VТ1 увели-чивает порог переключения, повышает помехоустойчивость ТТЛ.

Выходной усилитель (VТ2, VТ3, VD, R4) представляет собой эмиттерный повторитель.

Транзисторы VТ1, VТ3 представляют составной транзистор или пару Дарлингтона. В статических режимах работы схемы VT3 повторяет состояние VT1. При запирании VT1 база транзистора VT3 через резистор R3 подключается к корпусу, чем и обеспечивается закрытое состояние VT3.

Транзистор VТ2 может работать в насыщении и в отсечке. Его состояние в статических режимах работы схемы всегда противоположно состоянию VT3, следовательно, VT1. При насыщенном транзисторе VT3 транзистор VT2 закрыт и наоборот. Транзисторы VТ2, VТ3 представляют собой не что иное, как двухтактный усилитель мощности.

Диод VD служит для надежного запирания VТ2, когда открыт VТ3. Повышая порог отпирания VT2, он обеспечивает его закрытое состояние при насыщенном транзисторе VT3. Действительно:

UБЭ2 = UКЭН1 + UБЭ3 – UКЭН3 – UVD ≈ U БЭ3 - UVD < Uпор2, так как типичны значения: UБЭ = 0,7 В; UКЭ=0,3 В; UVD = 0,7 В; Uпор = 0,6 В.

UБЭ2 = UБ2 ‑ (UD+UКЭ3) = UКЭ1+UБЭ3 – UVD ‑ UКЭ3 = 0,3 + 0,7 ‑ 0,7 ‑ 0,3 = 0.

Если VD отсутствует UБЭ2 = UКЭ1 + UБЭ3 ‑ UКЭ3 = 0,7 В, при этом VТ2 открыт.

UБЭ2 = UБ2 ‑ UЭ2 = (UКЭ1+UБЭ3н) ‑ (UКЭ3н+UD) = 0.

Если VT1 насыщен, то через базу VT3 протекает ток

IБ3 = IЭ1 – IR3 = [(EК ‑ UКЭН1 – UБЭ3)/a2·R2] – (UБЭ3/R3).

Для обеспечения режима насыщения VT3 при закрытых транзисторе VT2 и диоде VD необходимо выполнить условие

IБ3·В3 ≥ IКН = n·I0ВХ НАГР

где В – коэффициент передачи тока в режиме большого сигнала;

n – количество нагрузочных ТТЛ-схем, подключенных к выходу рассматриваемой схемы;

I0ВХ НАГР – входной ток нагрузочной ТТЛ-схемы.

Отсюда можно определить нагрузочную способность данной схемы, т.е. максимальное число нагрузочных схем, при котором транзистор VT3 еще работает в режиме насыщения:

nМАКС = IБ3·В3 / I0ВХ НАГР.

Резистор R4 необходим для:

а) защиты VТ2 и VD в случае короткого замыкания на выходе;

б) ограничения коллекторного тока VТ2 при переключении схемы, из логического нуля в логическую единицу. После запирания VT1 транзистор VT2 откроется раньше, чем закроется насыщенный транзистор VT3, так как для выхода VT3 из режима насыщения потребуется некоторое время для рассасывания неосновных носителей в базе. В результате, в течение некоторого промежутка времени, оба транзистора VT2 и VT3 открыты, и по цепи, состоящей из элементов Ек, VT2, VD и VT3, протекает ток, потребляемый от источника питания Ек, и возникает импульс помехи по шине питания. Для ограничения амплитуды помехи ставится резистор R4, равный примерно нескольким десяткам омов.

Схема ТТЛ работает следующим образом. Если хотя бы на одном из входов низкий уровень напряжения U0ВХ эмиттерный переход МЭТ отпирается и течет ток: от +ЕК, через R1, переход база-эмиттер на землю. Коллекторный переход МЭТ смещен в обратном направлении (МЭТ в активном режиме). Ток базы IБ1 = 0, следовательно, транзистор VT1 запирается. На коллекторе VT1 высокий уровень напряжения UК1 = ЕК. На эмиттере VT1 напряжение UЭ1 = 0.

Транзистор VТ2 отпирается током через резистор R2. Так как UБ3 = UЭ1 = 0, то транзистор VT3 заперт и UВЫХ= U1ВЫХ.

Если же на всех входах ТТЛ высокий уровень U1, эмиттерные переходы МЭТ запираются, потенциал базы увеличивается, коллекторный переход МЭТ смещается в прямом направлении. МЭТ работает в активно-инверсном режиме.

Транзисторы VТ1 и VТ3 открыты и насыщены. Транзистор VТ2 и диод VD заперты. На выходе ТТЛ низкий уровень UВЫХ = U0 = 0. Следовательно, ТТЛ выполняет операцию И-НЕ, т.е. является элементом Шеффера.

Быстродействие схем ТТЛ определяется в основном переходными процессами при переключении транзисторов, а также зарядом паразитной суммарной емкости СН нагрузочных ТТЛ-схем. В схеме ТТЛ с простым инвертором (см. рисунок2.17) заряд емкости СН происходит с большой постоянной времени через коллекторный резистор R2, что ухудшает быстродействие схемы.

В схеме ТТЛ со сложным инвертором постоянная заряда нагрузочной емкости существенно уменьшается, так как емкость СН заряжается через выходное сопротивление транзистора VT3 (Rвых 3 << R2), в схеме эмиттерного повторителя. За счет этого повышается быстродействие.

2.2.3.3 Разновидности схем ТТЛ

Также широко используются на практике разновидности схем ТТЛ:

а) схема ТТЛ с тремя состояниями выхода

Схемы базовых ТТЛ нельзя объединять по выходам из-за потребления большого тока от источника питания, а также, так как логически неопределен уровень выходного сигнала.

Но иногда (например, при разработке двунаправленных информационных шин) необходимо объединять выходы. Для этого служат ТТЛ с третьим (высокоимпедансным) состоянием выхода.

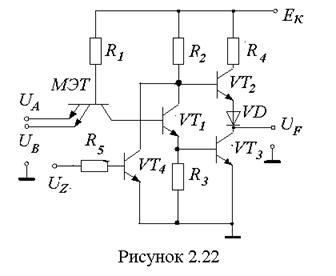

В базовую схему ТТЛ (см. рисунок 2.18) дополнительно включены резистор R5 и транзистор VТ4 (см. рисунок 2.22). При подаче на вход Z низкого уровня напряжения UZ = U0ВХ, VТ4 заперт и не влияет на работу ТТЛ. На выходе схемы в зависимости от входных сигналов будет 1 или 0.

При подаче на вход VТ4 высокого уровня UZ = U1ВХ транзистор VТ4 входит в насыщение. UК4 = 0. Это

обеспечивает запирание VТ2 и VТ3. ТТЛ полностью отключается от нагрузки, т.е.

не потребляет и не отдает ток. Это состояние не зависит от входных сигналов UА и UВ. Эти

схемы можно объединять по выходам на одну общую нагрузку, и в любой момент

времени нагрузка должна обслуживаться любым элементом, и остальные элементы

должны находиться в третьем состоянии;

При подаче на вход VТ4 высокого уровня UZ = U1ВХ транзистор VТ4 входит в насыщение. UК4 = 0. Это

обеспечивает запирание VТ2 и VТ3. ТТЛ полностью отключается от нагрузки, т.е.

не потребляет и не отдает ток. Это состояние не зависит от входных сигналов UА и UВ. Эти

схемы можно объединять по выходам на одну общую нагрузку, и в любой момент

времени нагрузка должна обслуживаться любым элементом, и остальные элементы

должны находиться в третьем состоянии;

б) схема ТТЛ с транзисторами Шоттки

Повысить быстродействие ТТЛ-схем можно, применив в схеме базового элемента вместо обычных транзисторов транзисторы Шоттки, работающие в активном режиме. Тем самым сокращается время переключения транзисторов схемы за счет исключения времени рассасывания носителей заряда в базе транзистора при их запирании. Логические микросхемы ТТЛ, выполненные на базе транзисторов Шоттки, называются микросхемами ТТЛШ;

в) схема ТТЛ с открытым коллектором

Схема ТТЛ с открытым коллектором предназначена

для согласования логических схем с внешними исполнительными и индикаторными

устройствами, например, светодиодными инди-каторами, лампочками накаливания,

обмотками реле и т.д. Ее отличие от ранее рассмотренной заключается в выпол-нении

выходного уси-лителя мощности по однотактной схеме без собственного нагрузоч-ного

резистора.

Схема ТТЛ с открытым коллектором предназначена

для согласования логических схем с внешними исполнительными и индикаторными

устройствами, например, светодиодными инди-каторами, лампочками накаливания,

обмотками реле и т.д. Ее отличие от ранее рассмотренной заключается в выпол-нении

выходного уси-лителя мощности по однотактной схеме без собственного нагрузоч-ного

резистора.

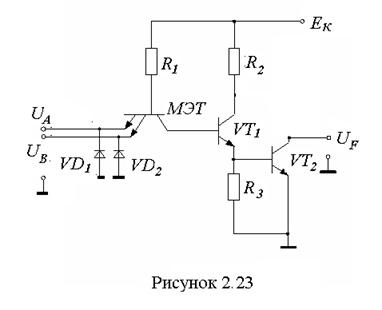

Принципиальная элек-трическая схема такого элемента приведена на рисунке 2.23. В данном элементе также отсутствует цепь нелинейной коррекции. Это связано с тем, что элемент ставится на выходе логического устройства и к нему в меньшей степени предъяв-ляются требования кванто-вания сигнала. Обычно выходной транзистор VT2 схемы выполняется с большими допустимыми значениями коллекторного тока и напряжением, чем обычный элемент.

Для защиты МЭТ от опасных отрицательных входных перепадов напряжения в ТТЛ между эмиттерами и землей включаются дополнительные диоды (на рисунке 2.23 VD1 и VD2).

2.2.4 Схемы ЭСЛ ‑ эмиттерно-связанной логики

2.2.4.1 Особенности схем ЭСЛ

Цифровые микросхемы эмиттерно-связанной логики имеют более высокое быстродействие, чем схемы ТТЛ (даже ценой большей рассеиваемой мощности), достигшее в настоящее время субнаносекундного диапазона, так как:

а) исключается насыщение транзисторов (время рассасывания избыточных носителей заряда t рас = 0);

б) в схеме применяются эмиттерные повторители (ЭП), ускоряющие процесс заряда емкости нагрузки, так как выходное сопротивление эмиттерного повторителя Rвых мало, ток выходной большой;

в) меньше логический перепад ![]() .

.

Наличие парафазного выхода дает возможность снимать прямые и инверсные значения, что позволяет уменьшить число используемых микросхем.

В отличие от простых схем ТТЛ, можно объединять выходы нескольких элементов ЭСЛ для расширения логических возможностей.

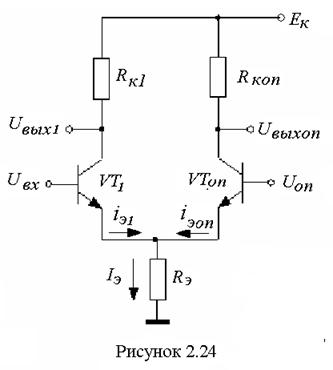

2.2.4.2 Переключатель тока

Особенность ЭСЛ заключается в том, что схема логического элемента строится на основе интегрального дифференциального усилителя (ДУ) в ключевом режиме (токовый ключ), выполненный на двух транзисторах (см. рисунок 2.24), которые могут переключать ток и при этом никогда не входят в режим насыщения. Дифференциальным усилителем называют усилитель, предназначенный для усиления разности двух входных сигналов. При этом полученное выходное напряжение не должно зависеть от абсолютного значения входных сигналов, а также от температуры окружающей среды и других факторов

![]()

где Ку — коэффициент усиления усилителя.

На базу одного из транзисторов, например, VTоп,

подано некоторое постоянное опорное напряжение Uоп. ![]() . Изменение напряжения,

подаваемого на вход UВХ ниже

или выше Uоп приводит к перераспределению постоянного тока

эмиттера Iэ, заданного токостабилизирующим резистором Rэ, между

транзис-торами VT1 и VTоп.

. Изменение напряжения,

подаваемого на вход UВХ ниже

или выше Uоп приводит к перераспределению постоянного тока

эмиттера Iэ, заданного токостабилизирующим резистором Rэ, между

транзис-торами VT1 и VTоп.

При этом транзисторы не входят в режим насыщения, и,

следовательно, в ключе принципиально отсутствует интервал времени рассасывания

их неосновных носителей.

При этом транзисторы не входят в режим насыщения, и,

следовательно, в ключе принципиально отсутствует интервал времени рассасывания

их неосновных носителей.

Существенный недоста-ток данной схемы — выходное сопротивление выходов ве-лико, что не позволяет обеспечить высокое быстро-действие схемы. Для снижения выходного сопротивления к коллекторным выходам подключают эмиттерные повторители. Для получения нескольких логических входов используют один пороговый транзистор и несколько параллельно включенных входных транзисторов.

2.2.4.3 Принцип действия базовой схемы ЭСЛ

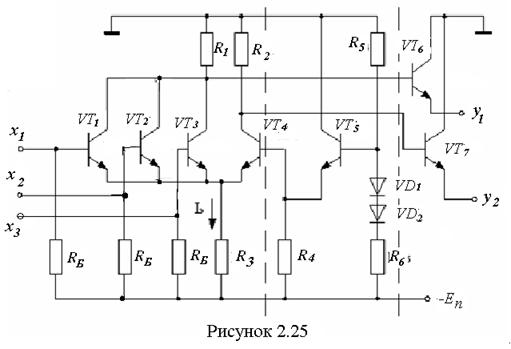

Функционально схема ЭСЛ состоит из трех узлов (см. рисунок 2.25):

а) токового переключателя на транзисторах VT1 ¸ VT4 и

резисторах R1¸R3. Содержит две ветви: входную ‑ на транзисторах VТ1

¸ VТ3

(максимально может быть до 9 входов) и резисторе R1 и опорную на VТ4 и резисторе R2. Транзисторы работают в ключевом режиме, а именно:

открыт – активный режим, не входит в насыщенный, и заперт. Ветви имеют общее

сопротивление R3.

Источник питания En и резистор R3

образуют генератор тока, причем R3 >> R1, R2. Это дает постоянство

эмиттерного тока![]() ;

;

б) источника опорного напряжения, включающего параметрический стабилизатор на элементах R5, VD1, VD2, R6 и эмиттерный повторитель на VT5 и R 4. VD1, VD2 – обеспечивают температурную компенсацию Uоп;

в) выходных эмиттерных повторителей на транзисторах VT6 и VT7.

Цепь нагрузок транзисторов VT6 и VT7

вынесена из ИС ЭСЛ, что способствует снижению рассеиваемой в ней

мощности и расширению функциональных возможностей. Эмиттерные повторители на VT6 и VT7

также являются сдвигателями уровней, повторяют Uвх, но сдвигают его на 0,7 В для обеспечения

входа и выхода низкого ![]() и

высокого

и

высокого ![]() уровней.

уровней.

Таким образом, эмиттерные повторители на VT6 и VT7 обеспечивают:

1) формирование выходных сигналов;

2) развязку между переключателями тока и нагрузкой;

3) высокую нагрузочную способность;

4) быстрый перезаряд емкости нагрузки за счет малого выходного сопротивления.

В схеме общей шиной является шина +Еп, в результате чего потенциалы точек схемы отрицательны относительно общей шины. Однако в схеме ЭСЛ так же, как и в схемах ТТЛ, реализован принцип положительной логики, при которой большему выходному напряжению соответствует сигнал логической единицы, а меньшему – сигнал логического нуля.

Быстродействие токового переключателя высокое, так как транзисторы не входят в насыщение и, кроме того, мал логический перепад напряжений между значениями логического нуля и логической единицы. Это обеспечивается выбором малых значений сопротивлений резисторов R1 и R2 схемы, что крайне полезно с точки зрения уменьшения постоянной времени перезаряда выходной емкости транзистора.

Нетрудно заметить, что рассмотренная схема реализует по выходу y1 операцию ИЛИ-НЕ, а по выходу у2 – операцию ИЛИ

![]() ;

; ![]() .

.

Резисторы RБ, включенные между базами транзисторов VТ1

¸ VТ3

и – En, обеспечивают запертое состояние этих транзисторов при отсутствии

входного сигнала. Это позволяет не беспокоиться о подключении неиспользуемых

входов ИС к выводам источника питания.

Резисторы RБ, включенные между базами транзисторов VТ1

¸ VТ3

и – En, обеспечивают запертое состояние этих транзисторов при отсутствии

входного сигнала. Это позволяет не беспокоиться о подключении неиспользуемых

входов ИС к выводам источника питания.

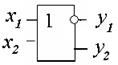

Условное обозначение ЭСЛ имеет вид

2.2.5 Логические элементы на полевых транзисторах

2.2.5.1 Логические элементы на МДП

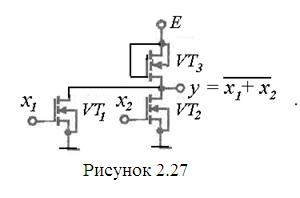

Рассмотрим логические элементы НЕ, ИЛИ-НЕ, И-НЕ.

Рассмотрим логические элементы НЕ, ИЛИ-НЕ, И-НЕ.

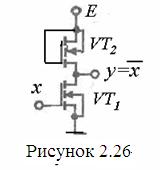

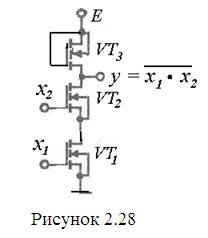

а) схема инвертора на МДП приведена на рисунке 2.26.

Транзистор VT1 работает в ключевом режиме, VT2 – всегда в активном. VT2 является нелинейной нагрузкой.

При запертом VT1 транзистор VT2 ‑ в активном режиме, ближе к насыщению, при насыщенном VT1 транзистор VT2 – в активном, ближе к отсечке.

При подаче на вход х низкого уровня напряжения VT1

запирается, VT2

близок к насыщению, на выходе ключа высокий уровень напряжения. При подаче на

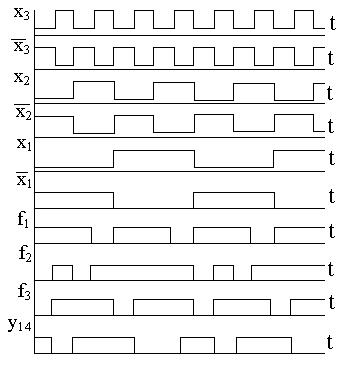

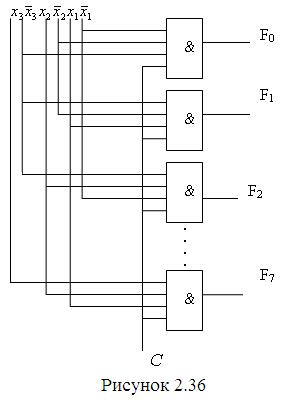

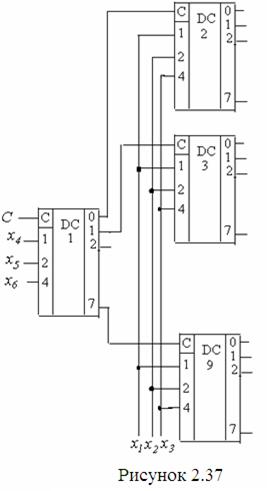

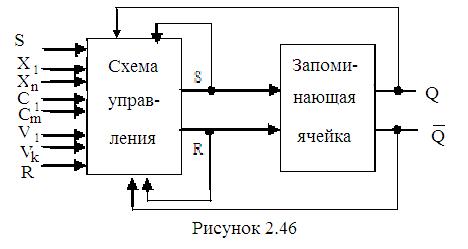

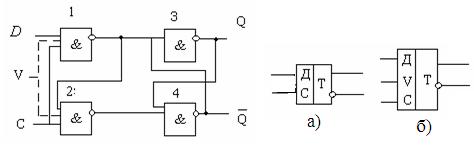

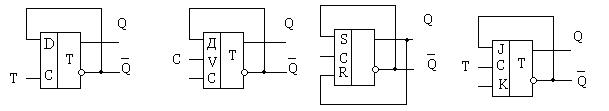

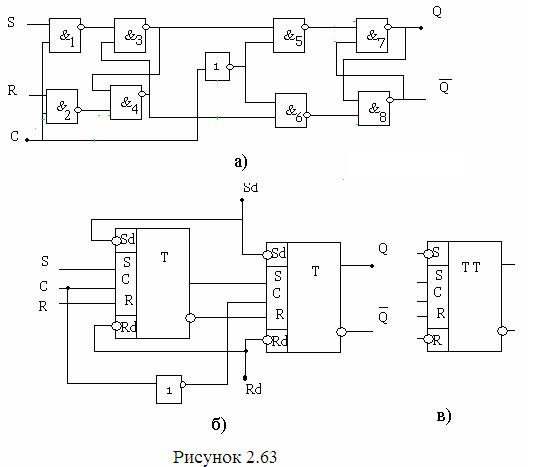

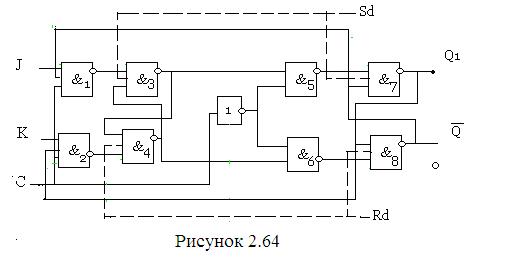

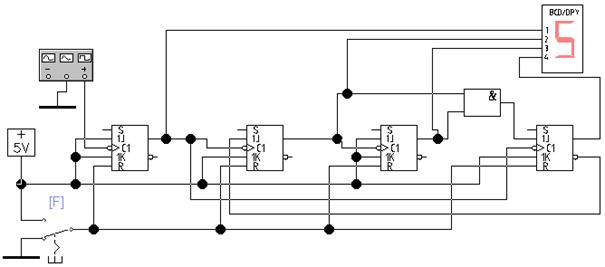

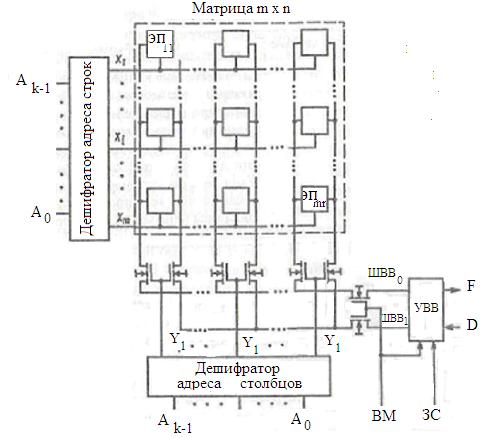

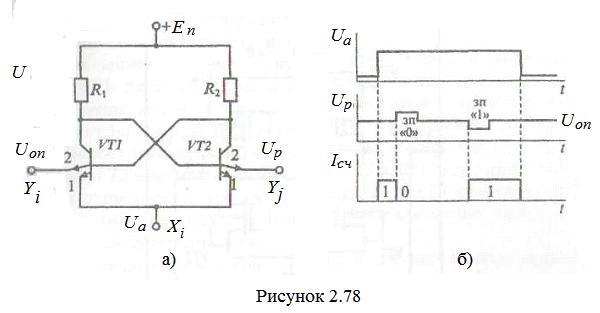

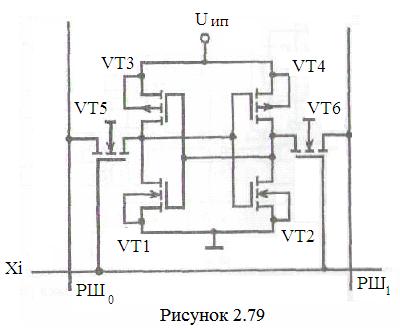

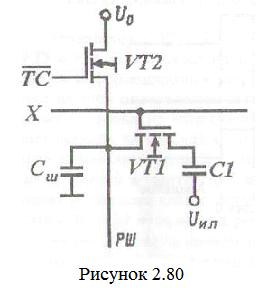

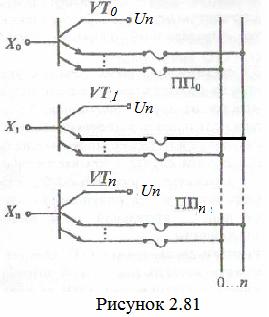

вход х высокого уровня напряжения VT1 отпирается, VT2 близок к отсечке, на выходе ключа низкий уровень