Некоммерческое акционерное общество

АЛМАТИНСКИЙ УНИВЕРСИТЕТ ЭНЕРГЕТИКИ И СВЯЗИ

Кафедра «Электроника»

СХЕМОТЕХНИКА

Методические указания и задания к выполнению лабораторных работ для студентов всех форм обучения специальности 5В070400 – Вычислительная техника и программное обеспечение, 5В070300- Информационные системы

Алматы 2011

СОСТАВИТЕЛЬ: У.К.Дегембаева. Схемотехника. Методические указания и задания к выполнению лабораторных работ для студентов всех форм обучения специальности 5В070400 – Вычислительная техника и программное обеспечение, 5В070300- Информационные системы. - Алматы: АУЭС, 2011. –37 с.

Методические указания содержат задания к лабораторным работам: схемы исследования логических элементов DTL NAND и элементов –инвертора серии ТТЛ, серии ECL NOR, элементов с комплиментарной МОП-структурой. Исследование различных комбинации серий логических элементов, отыскание повреждении на плате 220, триггера Шмитта.

Методические указания к лабораторным работам предназначены для студентов, обучающихся по специальностям 5В070400 – Вычислительная техника и программное обеспечение, 5В070300- Информационные системы.

Ил.24 , табл.16 , библиогр. 18 назв.

Рецензент: канд. техн. наук, доцент Б.С. Байкенов

Печатается по плану издания некоммерческого акционерного общества «Алматинский университет энергетики и связи» на 2011 г.

© НАО «Алматинский университет энергетики и связи», 2011 г.

|

Содержание |

|

|

|

|

|

Описание лабораторного стенда DS и программы EWB |

4 |

|

1 Лабораторная работа. Логические элементы DTL NAND |

6 |

|

2 Лабораторная работа. Исследование логических элементов –инвертора серии ТТЛ |

9 |

|

3 Лабораторная работа. Исследование схемы логической серии ECL NOR |

14 |

|

4 Лабораторная работа. Логические элементы с комплиментарной МОП-структурой |

17 |

|

5 Лабораторная работа. Исследование различных комбинации серий логических элементов |

22 |

|

6 Лабораторная работа. Отыскание повреждении на плате 220 |

24 |

|

7 Лабораторная работа. Триггер Шмитта. Электронный сторож на триггерах Шмитта 8 Список литературы

|

30

34 |

1 Описание лабораторного стенда ДЕГЕМ СИСТЕМС

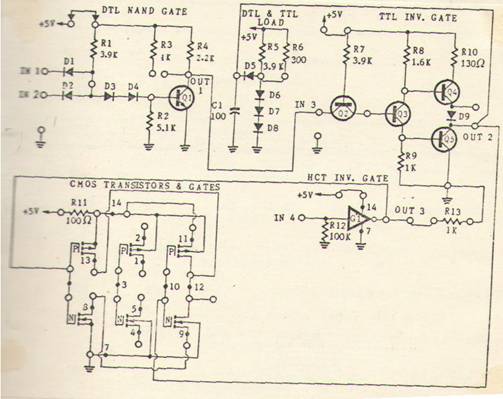

Курс ЕВ -220 первая рабочая панель для проведения экспериментов из серии «Цифровая электроника». Она предназначена для работы с

логическими элементами разных серии – т.е. построена с использованием разных технологии. Стенд состоит из 6 схем:

– логические элементы DTL NAND;

– комплиментарная МОП-структура;

– интегральный инвертор HCT INV GATE;

– инвертор серии ТТЛ;

– серия логических элементов TCL NOR;

–комбинация различных серии, а также представлена возможность

отыскания повреждении на плате ЕВ-220.

На панель ЕВ-220 находится большое количество цоколей и узлов соединений. В качестве источников постоянного тока используются PS-1, PS-2 с напряжением питания +5, в качестве источника переменного тока можно использовать внешний или внутренний генератор.

Целью использования панели ЕВ-220 и программы EWB является приобретение навыков построения и настройки параметров компонентов логических элементов разных серии. Построить инверторные логические элементы CMOS,NAND и NOR.

Оборудование: аппаратный комплекс ДЕГЕМ СИСЕМС и IBM - совместимый персональный компьютер с операционной системой Windows.

В цифровых устройствах и устройствах вычислительной техники используются два сигнала: логический ноль и логическая единица. При этом каждому логическому сигналу соответствует вполне определенное абсолютное значение напряжения. Эти напряжения различны для элементов с положительной и отрицательной логикой. Кроме того, напряжения логической единицы и логического нуля различны для элементов, изготовленных по разным технологиям (ТТЛ-, КМОП-,И2Л, ЭСЛ- элементы).

В каждой серии микросхем существуют базовые элементы, которые в наибольшей степени характеризуют конструкцию всех микросхем данной серии.

В данной работе исследуется, как изменяются выходные напряжения в зависимости от входных напряжений, подаваемых на базовые (т.е. наиболее типичные) логические ТТЛ- и КМОП-элементы.

Источники напряжений U1 и U3 имитируют входные сигналы, причем низкие напряжения соответствуют логическому нулю, а относительно высокие – логической единице. Два транзистора, обозначенные символами VT1, имитируют двухэмиттерный транзистор (к сожалению, таких транзисторов нет в библиотеке элементов EWB).

Источники Х1 и Х2 выполняют аналогичные функции: имитируют входные сигналы.

Рассматриваемые элементы выполняют логическую функцию И-НЕ, поэтому подача на вход двух напряжений высокого уровня приводит к появлению на выходе напряжения, по уровню близкого к нулю вольт.

Плавное изменение входного напряжения приводит к нелинейному изменению выходного напряжения (лишь на некотором участке передаточной характеристики наблюдаются почти линейные участки).

1 Лабораторная работа. Логические элементы DTL NAND

Цель работы: исследовать работу схемы NAND и получить характеристики серии ДТЛ.

1.1 Домашняя подготовка

1.1.1 По рекомендованной литературе (5,17,18) предварительно ответить на теоретические вопросы.

1.1.2 Прочитать методические указания к лабораторной работе.

1.2 Описание элементов серии ДТЛ

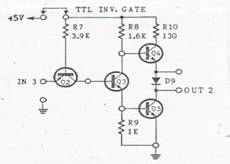

На рабочей панели в верхнем левом углу найти схему экспериментального контура логического элемента серии DTL NAND.

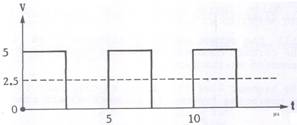

Рисунок 1

1.3 Контрольные вопросы

1 Перечислите основные электрические параметры базовых логических элементов.

2 Дайте определение передаточной характеристики логического элемента.

3 Каково назначение логических схем?

4 Какую операцию выполняет схема И?

5 Какие схемы моделируют логические операции:

а) 1*1=1

б) 1+1=1

6 Что такое канал связи?

7 Что такое модуляция?

8 Какого вида импульсной модуляции не существует?

9 Как называются цепи, состоящие из элементов, параметры которых постоянны и не зависят ни от электрического воздействия, ни от времени?

10) Как называются цепи, состоящие из элементов, параметры которых зависят от электрического воздействия (тока или напряжения), но не зависят от времени?

1.4 Рабочее задание

1.4.1 Предположив, что Ube=0,5 B Uvdiode=0,6 B

Ube,sat=0,7 B Ud,on=0.7 B

Uce,sat=0,2 B βtyp=70,

Вычислите напряжение на выходе out1 для четырех возможных комбинации на in1 и in2. Покажите, что схема в самом деле осуществляет логическую функцию NAND.

1.4.2 Рассчитайте ток, потребляемый схемой из источника питания, когда на выходе логическая 1 или логический 0.

1.4.3 Найдите рабочее напряжение Uce и ток Ic для выходов 0 и 1 при R3 открытом.

2.4.4 Рассчитайте коэффициент разветвления по выходу для идентичных каскадов, присоединенных к выходу.

1.5 Методические указания к выполнению лабораторной работы

1.5.1 Соберите схему, как показано на рисунке 1. Подайте ко входу напряжение 5В, измерьте напряжения также на входах in1 и in2 логических переключателей А и В.

1.5.2 Измерьте выходное напряжение для всех возможных комбинации А и В. Впишите в таблицу 1.1 результаты.

Т а б л и ц а 1.1

|

in1 |

in2 |

Выход |

|

|

(volts) |

Logic level |

||

|

0 |

0 |

|

|

|

0 |

1 |

|

|

|

1 |

0 |

|

|

|

1 |

1 |

|

|

1.5.3 Измерьте ток, потребляемый схемой из источника питания для логической 1 или логического 0 на выходе. Измерьте ток, который течет через Д1 для in1=0 и in2=1.

1.5.4 Измерьте напряжение Uce для логической 1 или логического 0 на выходе (резистор R3 открыт).

1.5.5 Подайте логическую 1 к in1. Подсоедините прямоугольную форму волны генератора с частотой 200 кГц и амплитудой парных импульсов 5 В к in2, как показано на рисунке 2.3. Соедините out1 с осциллографом и измерьте время нарастания. Теперь подсоедините R3 параллельно R4 и проверьте как это влияет на выходной сигнал.

Рисунок 1.2

1.5.6 Подсоедините out1 к цепи нагрузки (DTL§TTL LOAD) c открытым резистором R6. Обратите внимание, что мы сейчас нагружаем схему каскадом, идентичным самому себе.

а) для in1=1 и in2=0 или 1 измерьте и запишите ток, текущий от out1 в цепь нагрузки;

б) теперь подсоедините in2 к выходному прямоугольному сигналу и сравните выходной результат, когда нет нагрузки;

в) подсоедините R6 и R5. Это эквивалентно нагрузке 14-ю идентичными каскадами. Измерьте и запишите выходной ток. Запишите, как нагрузка влияет на выходной сигнал.

1.5.7 Подайте напряжение на два, затем на три входа схемы и запишите результаты в таблицу 3, не забудьте заполнить таблицу истинности.

Рисунок 1.3

1.5.8 Соедините схему инвертора. Затем измерьте ток, отведенный от питающего схему тока, когда имеется или логический 0 или логическая 1. Для выполнения этого измерьте напряжение на резисторе (100 Ом) и рассчитайте соответствующий ток.

1.5.9 При применении резистивной нагрузки один контакт должен быть заземлен.

2 Лабораторная работа. Исследование логических элементов –инвертора серии ТТЛ

Цель работы: изучить, как логические элементы, принадлежащие различным сериям, могут быть скомбинированы.

2.1 Предварительная подготовка

2.1.1 Предварительно, до выполнения лабораторной работы изучить по рекомендованной литературе теоретические сведения по логическим элементам серии ТТЛ.

2.1.2 Изучить задание на лабораторную работу и методические указания к нему.

2.1.3 По справочнику записать паспортные данные и перерисовать характеристики исследуемых типов различных логических элементов.

Используемые приборы и элементы:

– центральный процессор РU–2000;

– печатная плата ЕВ–220;

– цифровой универсальный прибор;

– осциллограф.

2.2. Контрольные вопросы

1 Если заменить Q2 на многоэмиттерный транзистор, какая схема логического элемента будет И-НЕ или НЕ- И?

2 Почему ток текущий через R8 и R10 может быть пренебрежимо мал?

3 Почему происходит увеличение напряжения, соответствующего логическому уровню 0, когда 14 каскадов на выходе подсоединились параллельно?

4 Почему происходило увеличение напряжения, соответствующее логическому уровню 1, когда присоединялась резистивная нагрузка 1 кОм.

5 Назовите и приведите схемные разновидности элементов ТТЛ. Какое их назначение?

6 Назовите основные схемотехнические решения, применяемые при создании базовых логических элементов; сравните их по техническим параметрам.

7 Как решается вопрос о режиме “лишних” входов с учетом конкретного типа используемой схемотехнологии?

8 Как осуществляется наращивание числа входов логических элементов?

9 Перечислите преимущества элементов ТТЛ по сравнению с элементами ДТЛ.

2.3 Задания к лабораторной работе

2.3.1 Проверьте как работает схема и докажите, что она действительно является инвертором. Вы можете принять, что выход Q2 подсоединяется к нагрузочной схеме (DTL &TTL).

2.3.2 Измерьте ток потребляемый из источника питания.

2.3.3 Запишите в таблицу 1 значения тока как функции входного

логического уровня.

2.3.8 Подсоедините R6 паралельно R5 в нагрузочной схеме. Определите как это влияет на уровни напряжения на выходе.

2.3.9 Отсоедините нагрузочную схему, содержащую С1 и подсоедините выход к резистору R12 (предварительно измерив его сопротивление). Вторую сторону резистора надо заземлить. Как эта нагрузка будет влиять на выходной сигнал?

2.4 Расчетное задание

2.4.1 Рассчитайте ток потребляемый из источника питания и сравните с измеренным значением. Если есть различие большое, то попытайтесь оценить почему?

2.4.2 Рассчитайте среднюю потребляемую схемой мощность. Примите, что половину времени на входе схема имеет логический 0, а логическую 1 – оставшееся время. Сравните этот результат с мощностью, потребляемой логическим элементом CMOS.

2.4.3 Сравните результат с мощностью, потребляемой логическим элементом ДТЛ.

2.5 Методические указания к выполнению работы

2.5.1 Вставить печатную плату ЕВ–220 в систему PU–2000.

2.5.2 Собрать схему по рисунку 1.

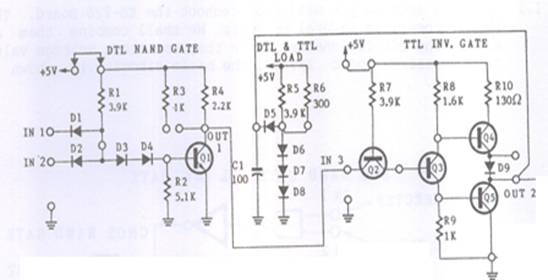

Рисунок 1 – Инвертор серии ТТЛ

Т а б л и ц а 2.1

|

Uвх, В |

Uвых, В |

|

|

|

2.6 Задания и методические указания к выполнению виртуальной части лабораторной работы-исследование передаточной характеристики ТТЛ-элемента

2.6.1 Собрать схему, показанную на рисунке 2.1.

2.6.2 Установить номиналы резисторов в соответствии с номером варианта, взяв необходимые данные из таблицы 1.1. Для всех вариантов U2 = 5V.

2.6.3 Исследовать зависимости выходного напряжения и тока через транзистор VT4 от величины напряжения U1(напряжение U3 поддерживать постоянным U3 = 3,5 B). Результаты исследований занести в таблицу 2.2

Рисунок 2

Т а б л и ц а 2.2

|

Вариант |

R1, кОм |

R2, кОм |

R3, кОм |

R4, кОм |

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

4 4 4 4 4,1 4,1 4,1 4,1 4 4 4 4 3,9 3,9 3,9 3,9 |

1,6 1,6 1,6 1,6 1,6 1,6 1,6 1,6 1,5 1,5 1,5 1,5 1,7 1,7 1,7 1,7 |

0,12 0,13 0,14 0,15 0,12 0,13 0,14 0,15 0,12 0,13 0,14 0,15 0,12 0,13 0,14 0,14 |

0,91 0,92 0,93 0,94 1,1 1,2 1,3 1,4 0,85 0,86 0,87 0,88 1,11 1,12 1,13 1,14 |

Т а б л и ц а 2.3

|

U1,В |

U,В |

I, мА |

|

3,5 2,5 1,5 1,4 1,35 1,3 1,25 1,2 0,8 0,4 0,2 |

|

|

2.6.4 По результатам измерений построить графики: зависимость выходного напряжения U от входного напряжения U =f(U1) и зависимость тока от входного напряжения I= j(U1).

2.6.5 По графику определить напряжения, соответствующие логической единице и логическому нулю. Эти значения занести в отчет.

2.7 Задание Исследование таблицы истинности ТТЛ-элемента с положительной логикой

2.7.1 Исследовать зависимость выходного напряжения U от входных напряжений ТТЛ - элемента (см. рисунок 2). Для этого заполнить таблицу 2.4.

Т а б л и ц а 2.4

|

U1, В |

U3, В |

Uвых., В |

|

0,2 0,2 3,5 3,5 |

0,2 3,5 0,2 3,5 |

|

3 Лабораторная работа. Исследование схемы логической СЕРИИ ECL NOR

Цель работы

– снятие и анализ экспериментальной схемы логической серии ECL NOR;

– по собственному номеру 10102 определить количество логических элементов NOR;

– приобретение навыков работы со справочной литературой по логическому элементу серии ECL NOR.

Контрольные вопросы

1 Какие факторы обеспечивают высокое быстродействие элементов ЭСЛ?

2 Работа схемы описывается следующими зависимостями: хвых.=1 при хвх.=0 и при хвх.=1. Какая это схема?

3 В чем заключается дискретизация сигнала?

4 Как определить количество уровней квантования?

5 Назвать единицу измерения быстродействия ЭВМ.

6 Как происходит переработка информации в компьютере?

3.1 Предварительная подготовка

3.1.1 Предварительно, до выполнения лабораторной работы изучить по рекомендованной литературе теоретические сведения о логическом элементе серии ECL NOR.

3.1.2 Изучить задание на лабораторную работу и методические указания к нему.

Используемые приборы и элементы:

– центральный процессор РU–2000;

– печатная плата ЕВ–121;

– цифровой универсальный прибор;

– осциллограф.

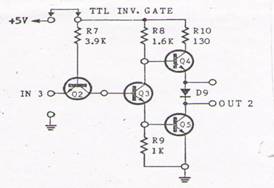

Экспериментальная схема ECL (логическая схема с эмиттерной связью)- часть единой схемы, построенной с использованием ECL и имеющей собственный номер 10102. Этот компонент содержит 4 логических элемента с NOR с двумя входами каждый. Штыри нумеруются как показано на рисунке, мы будем использовать логический элемент с двумя выходами в каждом для того, чтобы получить точные напряжения для логических уровней 0 и 1. Этот логический элемент маркируется на плате как G2. Логические уровни на выходе из G2 будут использованы для анализа логического элемента NOR, маркированного как G3. Он также является логическим элементом ECL.

3.2 Рабочее задание

3.2.1 Собрать схему при отключенных входах С2 и определить логический уровень на OUT15.

3.2 Определить напряжение источника для элемента с номером 10102.

3.2.3 Подключите резисторы R14,R15,R16 к выходам вентиля ИЛИ НЕ ЭСЛ, определите их назначение.

3.2.4 Исследовать схему при включенных С2, запишите значения выходных напряжении при логических «1» и «0».

3.2.5 Определите время спада и время нарастания для типичных значении при температуре Т=250С.

3.2.6 Снять передаточную характеристику логического элемента серии ECL NOR.

3.2.7 Измерьте ток от источника тока, для активации четырех логических элементов (вентилей), когда все имеют выходной логический уровень «0».

3.2.8 Рассчитайте, мощность потребляемую схемой, а также мощность потребляемую одним вентилем ИЛИ НЕ.

3.3 Методические указания к выполнению работы

3.3.1 Соберите экспериментальную схему логического элемента серии ECL NOR, показанную на рисунке 1

Рисунок 3.1

3.3.2 Подсоедините схему к источнику напряжением +5В, запишите уровни напряжении для логических «1» и «0»

3.3.2 Запишите значения напряжении при UCC1 и UCC2, также UEE.

Рисунок 3.2

3.3.3 Для логических схем ЭСЛ время спада = время нарастания, убедитесь в этом.

3.3.5 Снимите зависимость выходного напряжения от входного, занесите данные в таблицу 3.1

Т а б л и ц а 3.1 -Вентиль ИЛИ - НЕ ЭСЛ

|

In5 |

In6 |

Out4 |

|||

|

напряжение |

Логический уровень |

напряжение |

Логический уровень |

напряжение |

Логический уровень |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3.3.6 Потребляемую мощность рассчитать по измеренному значению и напряжению источника питания, а также мощность потребляемую одним вентилем.

3.3.7 Определите действительно ли схема является вентилем ИЛИ НЕ.

4 Лабораторная работа. Логические элементы с комплиментарной МОП-структурой

Цель работы: исследовать характеристики логических серии CMOS (комплиментарной МОП-структурой).

4.1 Домашняя подготовка

4.1.1 По рекомендованной литературе (5,17,18) предварительно ответить на теоретические вопросы.

4.1.2 Прочитать методические указания к лабораторной работе.

4.2 Описание элементов серии CMOS

Стенд состоит из трех схем на рисунках 4.1, 4.2, 4.3, между питающей цепью и исследовательским контуром установлен последовательно соединенный резистор R=100 Ом (он не является необходимым для работы схемы). Расположен он для измерения тока от источника питания.

Контрольные вопросы

1 Перечислите важнейшие статические и динамические параметры логических элементов.

2 Изобразите амплитудную передаточную характеристику ЛЭ

инвертора.

3 Чем определяется быстродействие логических элементов?

4 Что подразумевается под понятием базового логического элемента?

5 В чем причина низкой потребляемой мощности логических элементов на КМОП структурах?

4.3 Рабочее задание

4.3.1 Соберите экспериментальную схему, согласно рисунка 4.1

Проверьте выход, когда на входе подаются логические 0 и 1, результаты запишите в таблицу 1(таблицу истинности).

4.3.2 Подключив схему к функциональному генератору, изменяя напряжение на входе от 0 до 5В, запишите результаты на выходе в таблицу 4.2.

4.3.3 Соберите экспериментальную схему, согласно рисунка 4.1 Проверьте выходы, полученные для различных возможных комбинации входного сигнала, и результаты занесите в таблицу 4.1 (таблицу истинности).

4.3.4 Проверьте резистивную нагрузку, подключив R13, определите какое будет напряжение на выходе для каждого логического уровня.

4.3.5 Проверьте нагрузку CMOS, подключив дополнительный инвертор.

4.3.6 Рассчитайте ток, потребляемый схемой из источника питания, когда на выходе логическая 1 или логический 0.

4.4 Методические указания к выполнению лабораторной работы

4.4.1 Подайте ко входу напряжение 5В и определите напряжение на выходе. Запишите, что будет на выходе.

Т а б л и ц а 4.1

|

Uвх, В |

Uвых, В |

|

0 |

|

|

1 |

|

4.4.2 Уменьшите напряжение на входе PS-1, измерьте выходной сигнал.

Рисунок 4.1

4.4.3 Используя переменный генератор, выполните пункт 4.4.2, заполните таблицу 4.2 и постройте передаточную характеристику.

Рисунок 4.2

Т а б л и ц а 4.2

|

Uвх, В |

Uвых, В |

|

0 |

|

|

1 |

|

|

1,5 |

|

|

Окончание таблицы 4.2 |

|

|

2 |

|

|

2,2 |

|

|

2,5 |

|

|

3 |

|

|

4 |

|

|

5 |

|

4.4.4 Подайте напряжение на два, затем на три входа схемы и запишите результаты в таблицу 3, не забудьте заполнить таблицу истинности.

Рисунок 4.2

Т а б л и ц а 4.3

|

U1 (В) |

U2 (B) |

U3(В) |

Uвых .(В) |

|

|

|

|

|

|

|

|

|

|

4.4.5 Соедините схему инвертора. Затем измерьте ток, отведенный от питающего схему тока, когда имеется или логический 0 или логическая 1. Для выполнения этого измерьте напряжение на резисторе (100 Ом) и рассчитайте соответствующий ток.

4.4.6 При применении резистивной нагрузки один контакт должен быть заземлен.

4.4.6 При применении нагрузки CMOS, подключите дополнительный инвертор, используя пару транзисторов CMOS. Присоедините инвертор к какому-нибудь другому штырю +5 В, не на схеме CMOS. Это дает гарантию того, что измеряется только мощность, отведенная инвертором. Измерьте ток, отведенный от питания с помощью нагрузки CMOS, когда входными сигналами являются один из двух уровней. Используя, результаты рассчитайте мощность для каждого случая.

4.4.7 Измерьте ток стока, включив амперметр между штырями 13 и 3, вместо короткозамкнутого участка, показанного на участке. Измерьте ток непосредственно. Когда на вход инвертора I поступает логический 0, ток потечет в направлении от выхода (ток источника питания). Этот ток течет от источника питания через инвертор I (через PMOS) в инвертор 2 и в землю. Измерьте ток источника питания или движущий ток непосредственно.

4.4.8 Отсоедините универсальный измерительный прибор и закоротите штырь 3 со штырем 13. Подключите сигнал уровня ТТЛ с частотой на генераторе 200 кГц на вход, теперь проверьте, увеличивается ли время нарастания и время спада по сравнению с первичным сигналом.

4.4.9 Измерьте напряжение на резисторе R11 и используйте результат для расчета мощности переменного тока, который поступает на выход инвертора.

4.5 Задания и методические указания на выполнение виртуальной части лабораторной работы-исследование передаточной характеристики КМОП – элемента

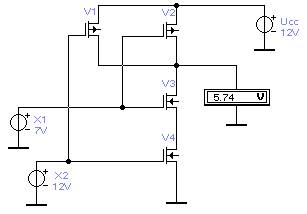

4.5.1 Собрать схему, показанную на рисунке 4.3

Рисунок 4.3

Исследовать зависимость выходного напряжения от величины напряжения Х1 (напряжение Х2 поддерживать постоянным Х2 = 12 B). Результаты исследований занести в таблицу 4.4

Т а б л и ц а 1.4

|

Х1,В |

U,В |

|

|

|

Справочные спецификации для типичных транзисторов PMOS и NMOS

а) б)

Рисунок 4.4-

а) типичные характеистики стока с каналом р-типа

б) стока с каналом n-типа

1 Сток к источнику, Вольт (Uds);

2 Ток стока,мА;

3 Другие входы логического элемента (вентиля) заземлены;

4 Температура окружающей среды;

5 Типичный температурный коэффициент для ТД=-0,3 %0С

5 Лабораторная работа. Исследование различных комбинации серий логических элементов

Цель работы: изучить, как логические элементы, принадлежащие различным сериям, могут быть скомбинированы.

5.1 Предварительная подготовка

5.1.1 Предварительно, до выполнения лабораторной работы изучить по рекомендованной литературе теоретические сведения по различным логическим элементам.

5.1.2 Изучить задание на лабораторную работу и методические указания к нему.

5.1.3 По справочнику записать паспортные данные и перерисовать характеристики исследуемых типов различных логических элементов.

Используемые приборы и элементы:

– центральный процессор РU–2000;

– печатная плата ЕВ–220;

– цифровой универсальный прибор;

– осциллограф.

Контрольные вопросы

1 Если заменить Q2 на многоэмиттерный транзистор, какая схема логического элемента будет И-НЕ или НЕ- И?

2 Почему ток текущий через R8 и R10 может быть пренебрежимо мал?

3 В чем особенность элементов И2Л?

5.2 Задание к лабораторной работе

5.2.1 Проверьте как работает схема и докажите, что она действительно является инвертором.

5.2.2 Измерьте ток потребляемый из источника питания.

5.2.3 Запишите в таблицу 2 значения тока как функции входного логического уровня.

5.2.4 Представьте себе схему, где логический элемент ТТЛ нагружен логическим элементом с комплиментарной МОП-структурой; будет ли она работать правильно?

5.2.5 Измерьте входной ток в каскаде с комплиментарной МОП- структурой.

5.3 Расчетное задание

5.3.1 Рассчитайте ток потребляемый из источника питания и сравните с измеренным значением. Если есть различие большое, то попытайтесь оценить почему?

5.3.2 Рассчитайте среднюю потребляемую мощность схемами логическим элементом CMOS и ТТL. Примите, что половину времени на входе схема имеет логический 0, а логическую 1 – оставшееся время. Сравните этот результат с мощностью, потребляемой мощностью.

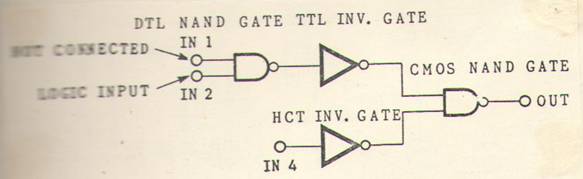

5.4 Методические указания к выполнению лабораторной работы

5.4.1 Подсоедините вход инвертора с комплиментарной МОП – структурой к выходу инвертора ТТЛ. Теперь выход инвертора с комплиментарной МОП – структурой будет следовать за входом инвертора ТТЛ. Измерьте затем уровни напряжения на выходе. Подсоедините схему как на рисунке 1, чтобы ТТЛ- инвертор бы нагружен тремя логическими элементами инвертора с комплиментарной МОП – структурой.

а) Подсоедините штыри 2,11 к +5 В.

б) Подсоедините штыри 4,9 к 7 (земля).

в) Cоедините штыри 1 и 5.

г) Cоедините штыри 13 и 8.

5.4.2 Найдите напряжения для обеих логических уровней на выходе одного из логических элементов с комплиментарной МОП- структурой для входных величин 0 и 1.

5.4.3 Отсоедините нагрузочную схему, содержащую С1 и подсоедините выход к резистору R12 (предварительно измерив его сопротивление). Вторую сторону резистора надо заземлить. Как эта нагрузка будет влиять на выходной сигнал?

Рисунок 5.1 Комбинации серии логических инверторов.

Т а б л и ц а 5.1

|

Uвх, В |

Uвых, В |

|

|

|

6 Лабораторная работа. Отыскание повреждении на плате 220

Цель работы: изучить, как логические элементы, принадлежащие различным сериям, могут быть скомбинированы.

6.1 Предварительная подготовка

6.1.1 Предварительно, до выполнения лабораторной работы изучить по рекомендованной литературе теоретические сведения по различным логическим элементам, кроме компонента схем с эмиттерными связями.

6.1.2 Изучить задание на лабораторную работу и методические указания к нему.

6.1.3 По справочнику записать паспортные данные и перерисовать характеристики исследуемых типов различных логических элементов.

Используемые приборы и элементы:

– центральный процессор РU–2000;

– печатная плата ЕВ–220;

– цифровой универсальный прибор;

– осциллограф.

6.2 Рабочее задание

6.2.1 Проверьте как работает схема и докажите, что она действительно является инвертором. Вы можете принять, что выход Q2 подсоединяется к нагрузочной схеме (DTL &TTL).

6.2.2 Измерьте ток потребляемый из источника питания.

6.2.3 Запишите в таблицу 6.1 значения тока как функции входного логического уровня

6.2.4 Подсоедините R6 паралельно R5 в нагрузочной схеме. Определите, как это влияет на уровни напряжения на выходе.

6.3.5 Отсоедините нагрузочную схему, содержащую С1 и подсоедините выход к резистору R12 (предварительно измерив его сопротивление). Вторую сторону резистора надо заземлить. Как эта нагрузка будет влиять на выходной сигнал?

6.3 Расчетное задание

6.3.1 Рассчитайте ток потребляемый из источника питания и сравните с измеренным значением. Если есть различие большое, то попытайтесь оценить почему?

6.3.2 Рассчитайте среднюю потребляемую схемой мощность. Примите, что половину времени на входе схема имеет логический 0, а логическую 1 – оставшееся время. Сравните этот результат с мощностью, потребляемой логическим элементом CMOS

6.4 Методические указания к выполнению лабораторной работы

6.4.1 Соедините схему на плате как показано на рисунке 3.

6.4.2 Подсоедините схемы NAND, ДТЛ, НСТ и ДТЛ и узел II к +5 В.

6.4.3 Заземлите одну сторону резистора R13.

6.4.4 Подсоедините OUT1 и IN3.

6.4.5 Подсоедините OUT2 к общей точке Д5/СI. Подсоедините R6 и R5 паралельно к 10.

6.4.6 Соедините точки 8 и 9;12 и 13.

6.4.7 Подсоедините OUT3 к точке 6 и к другой стороне R13. Собранная схема должна теперь выглядеть как схема 6.2

Рисунок 6.2- Детально указанные соединения схемы, использованной для поиска повреждений

6.4.8 Подсоедините логические входы к IN2, IN4 (IN1 останется свободным; вспомните, что открытый вход соответствует высокому логическому уровню). Заполните таблицу 6.3.

Т а б л и ц а 6.3

|

IN2 |

IN4 |

OUT1 |

|

0 |

0 |

|

|

0 |

1 |

|

|

1 |

0 |

|

|

1 |

1 |

|

6.4.9 Если схема работает правильно, измерьте уровни напряжения в точках, указанных в таблице 6.4.

Т а б л и ц а 6.4

|

IN2 |

IN4 |

Условие OUT |

OUT3 |

CMOS |

OUT2 |

OUT1 |

Основное соединение |

|||

|

Q1 |

D1 |

D2 |

D3 |

|||||||

|

0 |

0 |

ОК Fault (повреждение)1 Fault8 |

|

|

|

|

|

|

|

|

|

0 |

1 |

ОК Fault1 Fault8 |

|

|

|

|

|

|

|

|

|

1 |

0 |

ОК Fault1 Fault8 |

|

|

|

|

|

|

|

|

|

1 |

1 |

ОК Fault1 Fault8 |

|

|

|

|

|

|

|

|

6.4.10 Подсоедините сигнал ТТЛ/ комплиментарная МОП- структура частотой 200 кГц к IN2. Подсоедините поочередно логический 0 и логическую 1 к IN4. При двух условиях пронаблюдайте за формой волны на OUT и OUT2 и постройте их временные диаграммы.

Рисунок 6.3 - Схема проверки, используемая при поиске поврежений.

6.4.11 Методика поиска повреждении.

В таблице 6.5 и 6.6 описаны основные шаги, которым необходимо следовать при работе на блоке (модуле) РИ-2000 – пуск, определение рабочего режима. Ниже даны следующие шаги кодов для плато ЕВ-220.

Т а б л и ц а 6.5

|

|

РС1 |

РС2 |

|

ЕВ-220 |

805 |

658 |

Т а б л и ц а 6.6

|

STEP 1 |

KEY IN 2 |

DISPLAY 3 |

COMMENTS 4 |

|

1 |

|

PCb/PC1 |

PCb displayed for one second, followed by PC1. 5 |

|

2 |

805 |

805 |

Key in first 3 digits of board code (таблица 5) 6 |

|

3 |

* |

PCb/PC2 |

PCb displayed for one second, followed by PC2. 7 |

|

4 |

658 |

658 |

Key in last 3 digits of board code (таблица 5) 8 |

|

5 |

* |

EB-220 |

Board number displayed in alternating parts 9 |

|

6 7 |

* * |

Idl Id2 |

Omits student number update. If laboratory is connected to computer, key in student number in 3 parts, striking the * after each part. 10 |

|

8 |

* |

Id3 |

|

|

9 |

* |

Fn |

Selects operational mode (function) 11 |

|

10 |

2 |

Fn2 |

Sets Practice Mode 12 |

|

11 |

* |

P.00 |

Practice mode – intsert fault number 13 |

1- Шаг.

2- Включить клавишу.

3- Запись на дисплее.

4- Комментарии.

5- РСв высвечивается в течение 1 секунды с последующим РС1.

6- Включите первые 3 цифры кода платы (Таблица 1).

7- РСв высвечивается в течение 1 секунды, затем следует РС2.

8- Включите 3 последние цифры кода платы (Таблица 1).

9- Номер платы высвечивается поочередно.

10- Если лаборатория соединена с компьютером, разделите номер изуч.

11- Выбор рабочего режима (функции);

12- Серии Practice Mode;

13- Практический режим –вставить число повреждений.

Для того, чтобы ввести некоторые несправности, работайте в режиме Practice Mode согласно шагам, перечисленным в таблице 6.7

Т а б л и ц а 6.7

|

STEP 1 |

KEY IN 2 |

DISPLAY 3 |

COMMENTS 4 |

|

1 |

|

P.00 |

Practice Mode. 00 is the fault number 5 |

|

2 |

XX |

P.XX |

Selecting fault number XX (XX = 0…12 6 |

|

3 |

* |

P.XX |

The display will blink one second; 7 Then the faule will be introduced |

6.4.12 Опишите повреждения в бланках результатов:

а) введите повреждение 8;

б) выполните измерения, указанные в таблице 6.8.

Т а б л и ц а 6.8

|

IN2

1 |

IN4

2 |

Cтатус

3 |

OUT

|

OUT3

|

Terminal 9 on the CMOS circuit 4 |

OUT2

|

OUT1 |

|

0 |

0 |

5 Correct 6 Fault 1 Fault 8 |

|

|

0V Undefined 0mV |

|

|

|

0 |

1 |

Correct Fault 1 Fault 8 |

|

|

Undefined Undefined Undefined |

|

|

|

1 |

0 |

Correct Fault 1 Fault 8 |

|

|

0V Undefined 0V |

|

|

|

1 |

1 |

Correct Fault 1 Fault 8 |

|

|

|

|

|

1 - вход 2.

2 - статус.

3- выход.

4- оконечное устройство 9 в цепи КМОП.

5-корректировка.

6- несправность.

7 Лабораторная работа. Триггер Шмитта. Электронный сторож на триггерах Шмитта

Цель работы:

– снятие и анализ зависимости выходного напряжения от входного в классической схеме триггера Шмитта;

– приобретение навыков работы в программе EWB при работе с классической схемой триггера Шмитта на двух транзисторах с эмиттерными связями;

– приобретение навыков работы со справочной литературой по триггерам Шмитта.

7.1 Предварительная подготовка

7.1.2 Изучить задание на лабораторную работу и методические указания к нему.

Регенеративный компаратор (Триггер Шмидта) используется для предотвращения ложного переключения из-за помех в компьютерных устройствах и цифровых схемах. Компаратор такого рода использует положительную обратную связь.

Используемые приборы и элементы:

– центральный процессор РU–2000;

- программа EWB;

– цифровой универсальный прибор;

– осциллограф.

7.2 Рабочее задание

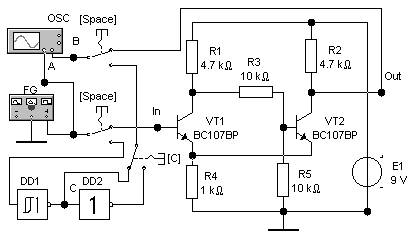

7.2.1 Собрать в программе EWB работу классической схемы триггера Шмитта на двух транзисторах (VT1и VT2) с эмиттерными связями.

7.2.2 Исследовать входной сигнал от функционального генератора FG.

7.2.3 Снять передаточную характеристику триггера.

7.2.4 Исследовать характерный гистерезис при подаче на вход триггера сигналов треугольной формы.

7.2.5 Переключить генератор на режим синусоидальных колебаний реализовав при этом неинвертирующий триггер Шмитта.

7.2.6 Использовать ТШ для отстройки от высокочастотной помехи.

7.2.7 Используя программу EWB показать пример применения ТШ в электронном охранном устройстве МАСТЕР КИТ NS011.

7.2.8 Собрать схему электронного блока.

7.3 Методические указания к выполнению работы

7.3.1 Собрать схему по рисунку 1в программе EWB работу классической схемы триггера Шмитта на двух транзисторах (VT1и VT2) с эмиттерными связями (см. рисунок 7.1).

Рисунок 7.1- Классическая схема триггера Шмитта

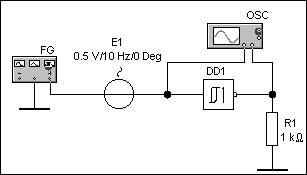

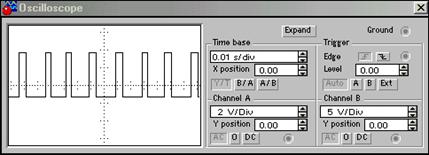

7.3.2 Входной сигнал от функционального генератора FG подается на вход In (база VT1) и канал А осциллоскопа OSC, а выходной снимается с вывода Out (коллектор VT2) и подается на канал В.

7.3.3 Для снятия передаточной характеристики триггера выставим режим генерирования сигналов треугольной формы, с параметрами показанными на рисунке 7.2.

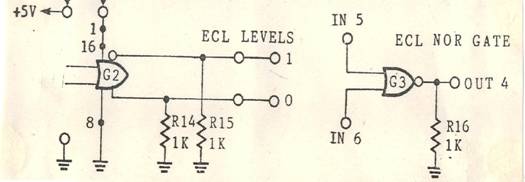

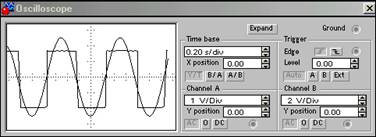

Рисунок 7.2

Для того, чтобы получить зависимость выходного напряжения от входного, на осциллоскопе выберем режим развертки типа В/A (см. рисунок 7.3).

Рисунок 7.3- Выбор режима развертки B/A

Поскольку далее для сравнения будет выполняться моделирование ТШ на типовых базовых логических элементах(DD1 и DD2), то схема предусматривает коммутацию приборов ключами [Space] и [C]. В данном же случае ключи [Space] должны находиться в верхнем положении, а ключ [C] – в любом. Включив моделирование, получим на экране характерную петлю гистерезиса (см. рисунок 7.1).

7.3.4 Характерный гистерезис – отставание величины выходного напряжения от входного. Если частоту следования импульсов уменьшить в десять раз (для этого надо воспользоваться установочными кнопками в окошке Frequency функционального генератора), то можно визуально пронаблюдать, как по мере роста напряжения вычерчивается вся кривая, проходя фигуру против часовой стрелки. Такой своеобразный вид передаточной функции триггера обусловлен его переключением под действием входного напряжения, регулируемого двумя обратными связями: положительной ОС со второго каскада на первый за счет общего резистора R4 и отрицательной ОС по току через этот же резистор, когда открыт транзистор VT1.

7.3.5 Переключите генератор на режим синусоидальных колебаний, а осциллоскоп на развертку сигналов во времени (Y/T), получите синусоидальные колебания на входе, которые превращаются в синфазные (по основной гармонике) прямоугольные колебания на выходе триггера (см. рисунок 7.4), поскольку в данном случае реализован неинвертирующий триггер Шмитта.

Рисунок 7.4- Вид колебаний на входе и выходе триггера

В комплекте базовых логических элементов программы EWB имеется инвертирующий триггер Шмитта (см. компонент DD1 на схеме рисунок 7.1). Для снятия передаточной характеристики этого триггера надо перевести переключатели [Space] в нижнее, а ключ [C] – в левое положение. Установив режим развертки в положение B/A, а генератор на треугольную форму колебаний, получить передаточную характеристику. В ней обход петли гистерезиса наблюдается по часовой стрелке. Если подать теперь на вход ТШ DD1 синусоидальные колебания, на его выходе (в точке С) получатся противофазные (по основной гармонике) колебания прямоугольной формы. Эти колебания можно превратить в синфазные, снимая сигнал с инвертора DD2 (переведя ключ [C] в правое положение).

7.3.6 Триггеры Шмитта позволяют эффективно отфильтровать шумы на пологих фронтах сигналов и являются незаменимыми для стыковки схем с медленно меняющимися сигналами (<1Гц) с логическими устройствами типа счетчиков и регистров, на их основе можно построить генераторы и другие устройства.

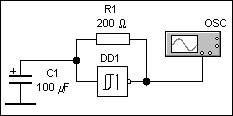

На рисунке 7.5 показано использование ТШ для отстройки от высокочастотной помехи, а на рисунке 7.6 – простейший генератор прямоугольных импульсов на его основе.

Рисунок 7.5 - Схема для отстройки от ВЧ помехи и получения осциллограмм входных и выходных сигналов

Рисунок 7.6 - Схема простейшего генератора прямоугольных импульсов и получения осциллограмм сигнала на выходе генератора

В состав ИМС входят инвертирующие триггеры Шмитта, например, ТТЛ 7414 содержит шесть подобных триггеров, а микросхема КМОП 4093 (аналог К561ТЛ1) состоит из четырех ТШ, на входе каждого из которых стоит двухвходовой элемент И-НЕ.

7.3.7 Описание простейшего устройства, позволяющего подать сигнал тревоги. Пример ваш автомобиль или мотоцикл лишь слегка изменит свое вертикальное положение, например, чуть-чуть качнется. В основе этого электронного сторожа датчик положения, в виде вертикальной металлической трубки, в верхней части которой на шарнире вдоль ее оси свободно подвешен металлический стержень. Трубка заземляется на корпус охраняемого объекта, а внутренний стержень в области подвеса напротив изолируется от корпуса и снабжается выводом к электронному блоку.

7.3.8 Схема электронного блока, входящего в набор NS011 показана на рисунке 7.7

Рисунок 7.7 - Схема электронного блока охранного устройства

Здесь она выполнена средствами программы EWB и несколько отличается от оригинальной (входящей в комплект), но и назначение ее иное: это виртуальная модель, работу которой можно проверить на компьютере. В основе блока лежит микросхема СD 4093, содержащая триггеры Шмитта. На рис. 7 “растащите” эту микросхему поэлементно, дополнив два первых триггера (DD1.2 и DD1.4) расширением входов по И (DD1.1 и DD1.3). Типы выходного транзистора VT1, электромагнитного реле - RL1 и зуммера - BUZZER взяты произвольно, но так чтобы модель была работоспособной. Для подбора этих компонентов в схему дополнительно включен амперметр, регистрирующий выходной ток (в пренебрежении током базы). Остальные номиналы и нумерация выводов ИМС соответствуют оригиналу. После изложенного выше (см. раздел “Триггер Шмитта”) нетрудно видеть, что на элементах DD1.1…DD1.4 выполнен автогенератор, а ТШ DD1.5 является формирователем импульсов. Выходной каскад на VT1 представляет собой усилитель, нагрузкой которого служит электромагнитное реле RL1, к нормально разомкнутым контактам которого подключено устройство для звуковой сигнализации. После включения моделирования программа автоматически ведет расчет и выводит в онлайновом режиме результаты. Если замкнуть ключ [S] на землю, то у светоизлучающего диода (LED) зачернятся выходные стрелки (анимация), амперметр начнет показывать некоторый ток (который будет возрастать) и из штатного динамика ПК (если там таковой имеется) раздастся тональный сигнал тревоги.

Ту же схему повторим используя графический интерфейс корпусов ИМС (см. рисунке 7.8), и проведем на ней те же испытания.

Рисунок 7.8 - Моделирование схемы электронного блока охранного устройства при помощи компьютера

Конечно, возможности моделирования гораздо шире, например, можно подключить осциллоскоп к разным точкам схемы и наблюдать в реальном режиме времени, протекающие там процессы, можно заняться параметрической оптимизацией или схемными изменениями и т.д. и т.п. Однако, можно собрать натуральное охранное устройство, иначе, возможно, уже и охранять-то будет нечего. Кроме того, надо обязательно проверить практикой теорию, т.к. в отрыве от практики она никому и не нужна.

Теперь, запасаясь терпением, надо выполнить сборку устройства согласно приведенной фотографии (см. рисунок 7.9) и монтажной схеме (см. рисунок 7.10), наладить его, разместить на охраняемом объекте в укромном месте и можно спокойно спать, пока оно Вас не разбудит…

Рисунок 7.9- Внешний вид устройства Рисунок 7.10- Монтажная схема охранной сигнализации

Список литературы

1. Т.М.Жолшараева. Схемотехника.Учебное пособие. Алматы.2010.81 с.

2. Лачин В.И., Савелов Н.С.

Электроника: Учеб. пособие – Ростов

н/Д: Феникс, 2009. – 704 с.

3. Опадчий Ю.Ф., Глудкин О.П., Гуров А.И. Аналоговая и цифровая электроника: Учебник для вузов. Под ред. О.П.Глудкина. – М.: Горячая линия‑Телеком. 2005, – 768 с.

4. Гусев В. Г., Гусев Ю. М. Электроника и микропроцессорная техника: Учеб.для вузов – М.: Высш. шк., 2006, – 800 с.

5. Дитмар Бенда-Поиск несправностей в электрических схемах.-Санкт-Петербург-БХВ-Петербург, 2010-245 с.

6. Пейтон А.Дж, Волш.В. Аналоговая электроника на операционных усилителях. – М..: Бином, 1994. – 352 с.

7. Аналоговые и цифровые интегральные микросхемы. Справочное пособие /Под ред. С.В.Якубовского. – М.: Радио и связь, 1985. – 432 с.

8. Павлов В.Н., Ногин В.Н. Схемотехника аналоговых электронных устройств. – М.: Радио и связь, 2005. – 320 с.

9. Фолкенберри Л. Применение операционных усилителей и линейных ИС. – М.: Мир, 1985. – 572 с.

10. Алексенко А.Г. Основы микросхемотехники. ‑3-е изд. – БИНОМ.Лаб.знаний, 2004. – 448 с.

11. Прянишников В.А. Электроника: Полный курс лекций. – СПб.: КОРОНА принт, Бином Пресс, 2006. – 416 с.

12. Жолшараева Т.М. Микроэлектроника. Полупроводниковые приборы: Учебное пособие. Алматы: АИЭС, 2006. – 79 с.

13. Жолшараева Т.М. Микроэлектроника. Интегральные микросхемы: Учебное пособие. – Алматы: АИЭС, 2007. – 81 с.

14. Жолшараева Т.М. Электроника: Учебное пособие. – Алматы: АИЭС, 2010.− 80 с.

15. Т.М.Жолшараева. Электроника. Методические указания к выполнению расчетно-графических работ для студентов всех форм обучения специальности 050702 – Автоматизация и управление. – Алматы: АИЭС, 2008. – 22 с.

16. Шанаев О.Т. Система моделирования Electronic Workbench / на казахском и русском языках. – Алматы: АИЭС, 2003.

17. Нефедов А.В. Транзисторы для бытовой, промышленной и спе-циальной аппаратуры: Справочное пособие. – М.: Солон-Пресс, 2006. – 600 с.

18. Транзисторы для аппаратуры широкого применения: Справочник. /Под редакцией Б.Л.Перельмана. – М.: Радио и связь, 1982. – 656 с.

Сводный план 2011 г., поз 194