Коммерциялық емес акционерлік қоғамы

АЛМАТЫ ЭНЕРГЕТИКА ЖӘНЕ БАЙЛАНЫС УНИВЕРСИТЕТІ

«Электроника» кафедрасы

СХЕМОТЕХНИКА

Дәрістер жиынтығы

5В070400 – Есептеу техникасы және бағдарламалық қамтамасыз ету

мамандығының студенттеріне арналған

Алматы 2011

ҚҰРАСТЫРУШЫЛАР: А.Т. Ибраев, А.Б. Нусибалиева. Схемотехника. 5В070400 – Есептеу техникасы және бағдарламалық қамтамасыз ету мамандығының студенттеріне арналған «Схематехника» пәні бойынша дәрістер жиынтығы

Дәрістер жиынтығында сандық электроника және микропроцессорлық техника негіздерін – заманауи әлемде ерекше орын алатын ғылым мен техниканың қарқынды дамып келе жатқан аймағын қарастырады. Материал жиынтығы студенттің қазіргі заманғы модельдеу және жобалау жүйелерін өздігінен және жүйелі түрде зерттеуге қажетті көлемде қамтамасыз етілген. Дәрістік материал екі бөлімнен тұрады: сандық сызбатехника және микропроцессорлық ҮИЖ.

Бірінші бөлімде комбинациялық тізбекті типті сандық құрылғылар, есте сақтау құрылғылары және прграммалық логикалы матрицалар қарастырылған. Екінші бөлім i8085/8086микропроцессорларының құрылымына, командаларға, сонымен қатар микропроцессорлық жүйенің адаптерлары мен контроллерларына арналған.

Дәріс жиынтығы сандық құрылғылар мен микропроцессорлық жүйелерді құру негіздерін бекіту мақсатында құрастырылған және 5В070400 – Есептеу техникасы және программалық қамтамасыз ету мамандығының студенттеріне арналған.

Без. 84, кестелер 24, әдеб.көрсеткіші – 6 атау.

Пікір беруші: техн.ғыл.д-ры., проф. Ш.А. Бахтаев

«Алматы энергетика және байланыс университеті» коммерциялық емес акционерлік қоғамының 2011 ж баспа жоспарына сәйкес басылады.

© «Алматы энергетика және байланыс университеті» КЕАҚ, 2011 ж.

Кіріспе

Заманауи қоғамның қажеттіліктерінің тез дамуы, экономиканың әртүрлі саласында кең көлемде қолданылатын Hi-Tec (High Technogy) деп аталатын жаңа технологияны талап етуде.

Информатика саласының ірі маманы, академик Е.П.Велихов бір мақаласында «Кімде-кім компьютер құрай білсе, ол әлемді бағындырады» деп өзінің ойын білдірген.

Сандық техникалардың барлық әртүрлі құралдары: дербес компьютерлер, өлшеудің микропроцессорлық жүйелері мен технологиялық процессорлардың автоматизациясы, цифрлық байланыс, теледидар, тұрмыстық техника және т.б. құрамына әртүрлі қиын микросхемалардан тұратын біртұтас элементті базадан - қарапайым операциялардан бастап миллион логикалық элементтерден тұратын қиын бағдарламалық кристалдарды орындайтын логикалық элементтерден құрылады.

Микропроцессорлар мен бағдарламалық құрылымды үлкен интегралдық схемалардың (ҮИС) (БИС), пайда болуынан автоматика құралдарын жасауға және жобалау әдістеріне сапалы өзгерістер болды.

Микропроцессор – бұл бір немесе бірнеше үлкен интегралды схемалар (ҮИС) (БИС) түрінде жүзеге асырылған функционалды процессор.

Микропроцессор өзінің жүйесіне кіретін командаларды орындауға қабілетті. Командалардың тізбектелуін өзгерте отырып, бір микропроцессорда әртүрлі есептерді шешуге болады.

Микропроцессорлы топтама – белгілі бір командалар топтамасы көмегімен жұмысты басқару мүмкіндігіне ие болатын ҮИС жиынтығы.

Микропроцессорлы жүйе өзінің құрылымы бойынша дербес компьютерге ұқсас, бірақта, ішкі әлеммен беттесу құралдарының жиынтығы және жадысының көлемі шектеулі. Микропроцессорлық жүйені құрудың негізінде бағдарламалық-аппараттық принцип жатыр. Бір стандартты микропроцессорлық жүйенің бағдарламасын ауыстыра отырып, оны көптеген құрылғылар мен жүйелерде қолдануға болады: техникалық процестегі автоматты басқаруда, техникалық диагностикалар жүйелерінде және күзету жүйелерін қосу арқылы объектілердің жағдайын бақылауда.

Бағдарламаланатын құрылымды СҮИС-тің негізгі ерекшелігі микросхема құрылымын өзгерте отырып, бағдарламалы түрде әртүрлі блоктарды қоса алуында.

Микропроцессорлар мен СҮИС-ті оқып үйренбес бұрын, микропроцессор құрамындағы маңызды цифрлық элементтермен және құрылғылармен танысуымыз керек.

1 Дәріс. Цифрлық құрылғының логикалық элементтері

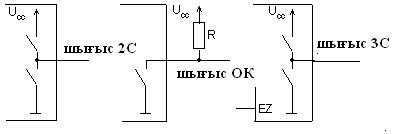

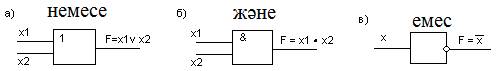

Цифрлық ақпараттарды түрлендіру 0 және 1 логикалық айнымалылары негізінде логикалық ЖӘНЕ, НЕМЕСЕ, ЕМЕС элементтері арқылы жүзеге асады. Логикалық элементтердің шартты белгілері - орындалатын операция таңбасы қойылған тіктөртбұрыш, (терістеу операциясының белгісі дөңгелек түрінде болады).

1.1 сурет – Логикалық элементтердің шартты белгілері

Схемаларда 0 және 1 айнымалылары әртүрлі екі кернеу арқылы кескінделеді: Uo және U1 . Кернеудің екі деңгейінің қайсысы Uo үшін, қайсысы U1 үшін қабылдау керектігін келісу керек. Оң және теріс логикалар деген ұғым бар. Оң логикада U1 > Uo, ал теріс логикада U1 < Uо. Ары қарай, егер қателеспесек, оң логиканы қолданамыз.

Бір түрлі логикалық айнымалыларды түрлендіру әртүрлі формаларда: ЖӘНЕ, НЕМЕСЕ, ЕМЕС операцияларының көмегімен (буль базисі), ЖӘНЕ-ЕМЕС операциялары (Шеффер базисі), НЕМЕСЕ-ЕМЕС операциялары (Пирс базисі), сондай-ақ басқа да көптеген әдістермен беруге болады. Көбіне Пирс және Шеффер базистері кездеседі.

1.1 Логикалық элементтердің статикалық параметрлері

Статикалық параметрлер дегеніміз логикалық элементтердің (ЛЭ) кірісі мен шығысында кескінделетін айнымалылар (0 және 1) шекарасында кескінделетін кернеу мәндері:

1) кірісі бойынша Uкір1min және Uкір0mах.;

2) шығысы бойынша Uшығ1min және Uшығ0max

және ток мәндері:

3) кірісі бойынша Iкір1max және Iкір0mах;

4) шығысы бойынша Iшығ1mах және Iшығ0mах.

Элементтер дұрыс жұмыс жасау үшін логикалық 1 кескіндейтін кернеу мейлінше жоғары, ал логикалық 0 кескіндейтін кернеу төмен болуы талап етіледі. Бұл талаптар Uкір1min және Uкір0mах. параметрлеріне қойылады. Осы элементтің кіріс кернеуі алдыңғы элементтің шығыс кернеуі (сигналдар көзі). Жүктемелік шарттарды орындағанда сақталатын элемент шығысындағы элементтер деңгейі Uшығ1min және Uшығ0max параметрлері арқылы беріледі. Шығыс кернеуінің жоғарғы деңгейінде элемент қорек көзінен ток ағып, жүктеме тізбегі токты сіңіреді. Элемент қорек көзінің шығыс кернеуінің төменгі деңгейінде ток осы элементке құйылып, ал қабылдағыш элементтерінің кіріс тізбегінен токтар ағады.

Сигналдың қорек көзі элементтерінің мүмкіндіктерін сипаттайтын Iшығ1mах және Iшығ0mах токтарын, қабылдағыш элементтеріне қолданылатын Iкір1max және Iкір0mах токтарын біле отырып, схеманың барлық элементтері үшін жүктемелік шектелуді сақтауды бақылауға болады.

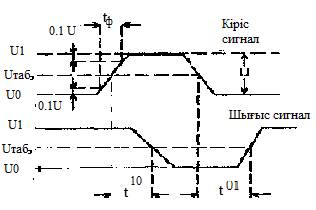

Логикалық элементтердің тезәсерлігі олардың бір күйден екінші күйге ауысу жылдамдығымен анықталады. 1.2 суретте ЕМЕС логикалық элементінің жұмысының уақыттық диаграммасы көрсетілген. Логикалық сигналдың өзгеру уақыты олардың Uтаб, табалдырық деңгейіне жету уақыты болып саналады, ол үшін сигналдың логикалық төмендеуінің ортасын алады 0,5(Uо + U1).

1.2 сурет – ЕМЕС логикалық элементі жұмысының уақыттық диаграммасы

ЦҚ тезәсерлігіне, сондай-ақ қайта зарядтауға уақыт жұмсауды талап ететін сыйымдылықта әсер етеді. Анықтамалық мәліметтерде схема түйіндерінде жүктеме сыйымдылығын есептеуге мүмкіндік беретін логикалық элементтердің кіріс және шығыс сыйымдылықтары келтірілген.

1.2 ЦЭ шығыстарының типтері

Цифрлық элементтердің (логикалық, есте сақтау, буферлі) шығыстарының келесі типтері бар:

- логикалық;

- ашық коллекторлы (стоком);

- үшінші жағдайлы;

- ашық эммиттерлі (истоком).

1.2.1 Логикалық шығыс.

Логикалық шығыс кернеудің екі деңгейін қалыптастырады (Uо және U1). Логикалық шығыстың шығыс кедергісі жоғарғы тезәсерлік алу үшін және сыйымдылықты жүктемені қайта зарядтау үшін үлкен токтарды бөлшектеуге қабілетті. Шығыстың бұл түрі ішкі схемаларда қолданылады (дешифраторларда, мультиплексорларда, сумматорларда).

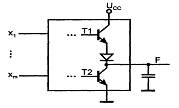

ТТЛ және КМОП элементтерінің логикалық шығыстарының схемалары екі тактілі каскадтарға ұқсас – оларда шығыс кернеудің екі фронты активті транзисторлар қатысуымен қалыптасады, олар шығысты ауыстырудың кез-келген бағытында аз шығыс кедергісін қамтамасыз ету үшін жұмыс жасайды. (1.3 суретті қара).

1.3 сурет - Цифрлы элементтің шығыс тізбегінің схемасы

Бұндай шығыстың ерекшелігі, оларды параллель жалғауға болмайтынында. Біріншіден, шығыстарды байланыстыратын нүктеде логикалық 1 қалыптасады, ал логикалық 0 қалыптасатын шығыста қалыпты нәтиже болмайды. Екіншіден, шығыс кедергінің шамасы аз болғандықтан, теңестіруші ток үлкен шамаға ие болуы мүмкін, ол шығыс тізбектің электрлік элементтерін істен шығаруға әкеп соғады.

1.2.2 Үш шығыс күйі бар элементтер.

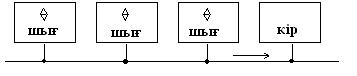

Үш шығыс күйі бар элементтері (ТС типті) 0 және 1 логикалық күйден басқа "ажыратылған" деген күйге ие, бұл кезде шығыс тізбек тогы өте аз болады. Бұл күйде элемент арнайы басқарылатын сигналға ауыстырылады, ол шығыс каскадындағы екі транзистордың (Т1 және Т2) жабық болуын қамтамасыз етеді (1.3 суретті қара). ТС типті элементімен сигналды басқару әдетте ОЕ (Output Enable) деп белгіленеді. Рұқсат (ОЕ = 1) болғанда элементтер өзінің логикалық операцияларын орындайды, ал болмаса (ОЕ = 0), "ажыратылған" күйіне ауысады. ЦҚ–да басқарылмалы сигналдарды таратуда ТС типті буферлі элементтер кең қолданылады. Буферлер терістейтін және терістемейтін болуы мүмкін, ал ОЕ сигналдары — төрт типті буферлік каскадтарға келтіретін Н-активті немесе L-активті болады (14 суретті қара). Элементтерде ТС типті шығыстар үшбұрышты белгілермен белгіленеді.

ТС типті шығыстарды уақыттың кез-келген моментінде олардың тек біреуі ғана активті болған кезде ғана параллель жалғауға болады. Бұл жағдайда ажыратылған шығыстар байланысқан нүктеде сигналдардың активті қалыптасуына кедергі жасамайды. Бұл мүмкіндік ТС типті элементтерді магистральды-модульді микропроцессорларда және бір байланыс желісінде ақпарат көздері кезектесіп қолданылатын жүйелерде қолдануға болады.

1.4 сурет - Үш күйлі буферлік каскадтардың типтері

1.2.3 Ашық коллекторлы шығыс.

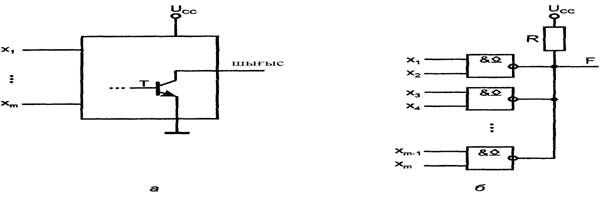

Ашық коллекторлы элементтерде коллекторы микросхема ішіндегі тізбектің ешқайсысымен жалғанбаған жеке транзистормен аяқталатын шығыс тізбегі бар (1.5,а суретті қара). Транзистор элементтің схемасының алдыңғы бөлігінен басқарылады, ол қаныққан немесе жабық күйде болуы мүмкін. Қаныққан күй логикалық 0 секілді, ал жабық логикалық 1 секілді жол салады. Транзистордың қанығуы шығыста Uо (қанығудың ең аз кернеуі коллектор-эмиттер" Uкэқ) кернеуін қамтамасыз етеді. Кернеудің кез-келген деңгейінде транзистордың бекітілуі элемент шығысында болмайды, осы кезде шығыста белгісіз "өзгермелі" мүмкіндікке ие, ол элемент схемасының ешқандай тізбегіне жалғанбаған. Сол себепті, жоғарғы деңгейлі кернеуді қалыптастыру үшін элемент шығысында ашық коллекторда (ОК типті) транзисторды бекіткен кезде, қорек көзіне қосылған ішкі кедергілерді (немесе басқа жүктемелерді) қосу талап етіледі.

ОК типті бірнеше шығыстарды барлық шығыстарға ортақ Ucc - R ( 1.5, б суретті қара) тізбекке қосып, параллель жалғауға болады. Бұл кезде жалпы тізбекте элементтердің кезектесу жұмыс режимін алуға болады, ТС типті элементтер үшін бір элемент активті болса, қалғандарының шығыстары жабық болады. Егер де шығыстары қосылған элементтердің активті жұмыс істеуіне рұқсат етілсе, онда қосымша логикалық операцияларды алуға болады, оны монтажды логика операциясы деп атауға болады.

1.5 сурет - ЦЭ ашық коллекторлы шығыс тізбегінің (а) және ЖӘНЕ операциясын жүзеге асыру (б) схемасы

Монтажды логиканы жүзеге асырғанда ортақ шығыста жоғарғы кернеу тек барлық транзисторларды бекіткенде ғана пайда болады, тек олардың біреуінің ғана қанығуы шығыс кернеуін Uo = Uкэқ деңгейіне дейін төмендете алады. Шығыста логикалық бірлік алу үшін барлық шығыстардың жекелік күйлері талап етіледі: ЖӘНЕ операциясы орындалады. Әрбір элемент өздерінің кіріс айнымалыларымен Шеффер операциясын орындағандықтан, ортақ нәтиже келесідей болады

![]() .

.

ОК элементтердің белгіленуінде таңбадан кейін астында сызығы бар ромб қойылады.

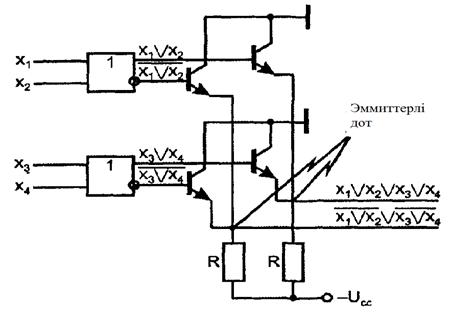

1.2.4 Ашық эммиттері бар шығыс

Ашық эмиттерлі шығыс ЭБЛ (эмиттерлі-байланысқан логика) типті элементтер үшін сипатты. Магистральда жұмыс істеу үшін бұндай элементтер қолданылмайды. Ашық эмиттерлі шығыстарды бір-бірімен біріктіру мүмкіндігі эмиттерлі резисторларды үлкен бір резисторға біріктірген кезде "эмиттерлі дот" деп аталатын схемаға келтіреді (1.6 суретті қара), ол қосымша монтажды логикалық схемалар алу үшін қолданылады.

1.6 сурет - "Эмиттерлі дот" схемасы

ЭБЛ элементтерінің біреуінде НЕМЕСЕ функциясы, ал басқасында НЕМЕСЕ-ЕМЕС функциясы іске асатын фазаға қарсы элементтері бар. Бірнеше элементтердің тура шығыстарын байланыстырып кеңейтілген НЕМЕСЕ алуға болады (байланыстыратын элементтердің кіріс айнымалылары біртұтас дизъюнкция қалыптастырады). Терістелген шығыстарды біріктіріп, кіріс айнымалылар терістелуіне қатысты ЖӘНЕ-НЕМЕСЕ операциясын алуға болады, бұл кезде

![]() .

.

Тура шығысты терістеумен байланыстырып, функцияны мына түрде алуға болады:

![]() .

.

2 Дәріс. Комбинациялы типті ЦҚ

2.1 Жобалау сатылары

Функционалды тораптар комбинациялы және тізбектелген болып екіге бөлінеді. Ары қарай комбинациялық торапты КТ (комбинациялы тізбек) арқылы, ал тізбектелгенді ЖА (жадылы автомат) арқылы белгілейміз. КТ мен ЖА негізгі айырмашылықтары мынадай:

- КТ-ның шығыс шамалары тек ағымдағы кіріс шамаларға (аргументтерге) тәуелді, бастама мәндері жоқ.

КТ-да өтпелі кезең аяқталған соң, олардың шығысында өтпелі кезең сипаттары әсер етпейтін шығыс шамалары қондырылады. Бірақ та, цифрлық құрылғыларда КТ жадылы автоматпен бірге функцияланады: өтпелі кезең кезде КТ шығысында тәуекел деп аталатын уақытша сигналдар пайда болады. Уақыт өткен сайын олар жойылып, КТ шығысында тізбек жұмысын сипаттайтын, логикалық формуламен қарастырылатын мәндерге ие болады. Бірақта, КТ шығысындағы тәуекелдердің жойылып кетуіне қарамастан, ЖА жұмысын радикалды өзгертетін тәуекелдер ЖА жадысының элементтерімен қабылдануы мүмкін. ЦҚ жұмысында тәуекелдер пайда болғандықтан үзіліс болмау үшін, өтпелі кезең уақытында жадының КТ элементтерімен сигнал қабылдауға тиым салынады. КТ шығысынан ақпараттарды қабылдау, КТ-да өтпелі кезең аяқталғаннан кейін жады элементтеріне түсірілетін, тек қана синхрондаудың арнайы сигналдарымен рұқсат етіледі.

Сондықтан, жады элементтерінде жалған сигналдар әсері болмайды. Сәйкес құрылымдар синхронды деп аталады.

Комбинациялы типті туынды логиканы жобалау сатылы түрде жүзеге асады.

Ең алдымен, КТ функциялау сипаты беріледі. Бұл әртүрлі әдістермен жасалынуы мүмкін, көбіне барлық аргументтерді жинақтап, іздеген функция мәндерін беретін ақиқат кестесін қолданды. Кестеден іздеген функция ЖДҚТ –ке (ЖДҚТ (СДНФ) – жетілдірілген дизъюнктивті қалыпты түр немесе конъюктивті мүшелер дизъюнкциясы бірдей мөлшерде) өту оңай. Ол үшін, біртұтас мәндерді қабылдайтын функция, сол аргументтердің жиынтығының логикалық қосындысын құрастырады.

Мысалы, 2.1-кестеде берілген үш аргумент үшін функцияны жаңғырту үшін ЖДҚТ аламыз

![]() .

.

2.1кесте - ЦҚ-ның ақиқат кестесі

|

x1 |

x2 |

x3 |

F |

x1 |

x2 |

x3 |

F |

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

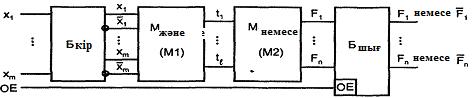

Басқа әрекеттер, заманауи схематехникаға қатысты функцияларды жүзеге асыру құралдарына тәуелді:

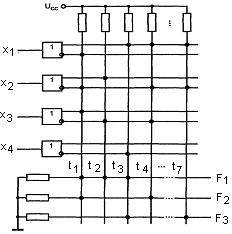

1) Кестелі типті логикалық блоктар (LUTs, Look-Up Tables).

2)ЖӘНЕ мен НЕМЕСЕ элементтерінің тізбектелген матрицасы түріндегі логикалық блоктар (PLA, Programmable Logic Array; PAL, Programmable Array Logic).

3) Мультиплексор (ӘЛМ) негізіндегі әмбебап логикалық блоктар.

4) Кейбір базистардағы логикалық элементтерден құралған логикалық блоктар (SLC, Small Logic Cells).

1. Егер КТ кестелі типті логикалық блоктар негізінде жүзеге асырылса, онда ЖДҚТ функцияның ақырғы өрнегі болады және бұл түрге ары қарай ешқандай түрлендіру талап етілмейді. Кестелі блок функцияның барлық мәндерін сақтауға қажет көп ұялы жадыны көрсетеді, немесе 2m, мұндағы m – функция аргументтерінің саны. Аргументтерді теру функция (0 немесе 1) мәндері сақталатын ұяшықтар мекен-жайы болып табылады. ЖДҚТ–та функцияның біртұтас мәндерін сақтауға қажетті барлық мекен - жайлар бар.

Егерде, іздеген функция қандай-да бір

қысқартылған түрде өрнектелсе, онда оны

ЖДҚТ–ге ауыстыру қажет. Ол үшін хj айнымалысы

жоқ конъюктивті мүшелер дизъюнкцияның тең бірліктеріне

көбейтіледі ![]()

Мысалы,

![]()

![]() .

.

2. Егер бұл жоба ЖӘНЕ мен НЕМЕСЕ элементтерінің тізбектеліп қосылған матрица түрінде логикалық блоктар негізінде жүзеге асса, онда бастапқы ЖДҚТ-ны ықшамдауға болады. ЖӘНЕ мен НЕМЕСЕ матрицалы логикалық блоктар жүйелерді айырып-қосқыш функция ретінде көрсетеді: кірістер, шығыстар және терім сандары. Ықшамдаудың мақсаты функцияның бұл жүйесінде конъюнктивті терімдер санын қысқарту немесе төте дизъюнктивті түрлерді қысқарту болып табылады. Бұл дизъюнктивті қалыпты түрдің (ДҚТ) ең төменгі түрін іздеуге әкеліп соғады.

3. Мультиплексор негізіндегі логикалық блоктар 3-тақырыпта қарастырылған.

4. SLC типті немесе вентильді деңгейде логикалық блокта КТ-ны жинақтау дәстүрлі болып табылады. ("вентиль" терминімен қарапайым операцияларды орындайтын базалы логикалық ұяшықтарды атайды, мысалы, екі-үш кірісі бар ЖӘНЕ-ЕМЕС элементтері).

Бұл нұсқада КТ жобалау келесі сатылардан тұрады:

- логикалық функцияларды ықшамдау;

- берілген логикалық базиске өту .

Ықшамдау – логикалық функцияны берілген шарттан мағынасын оңайлату үшін түрлендіреді. Алғашында схемадағы жүзеге асыратын өрнекте әріптер саны түрінде қиындықтар шартына әкеліп соғатын логикалық элементтер санын ықшамдауға тырысты. Бұл шарттар схеманың барлық логикалық элементтері кірістерінің қосындысы Квайн бағасы бойынша есептеледі. Бұл шарттар бойынша ықшамдау үшін математикалық өрнекті түрлендіру негізінде бірнеше әдістер жасалған, егерде аргументтер саны 6-дан аз болса, Карно картасын (Вейча диаграммасы) қолдану ыңғайлы.

Жобалаудың келесі әдісі – әдетте Буль базисінен (ЖӘНЕ, НЕМЕСЕ, ЕМЕС) алатын бастапқы өрнектен берілген логикалық базиске өту. Бұндай өту ережесі белгілі: олар де-Морген теоремасын қолдануға негізделген. Шеффер базисіне (ЖӘНЕ-ЕМЕС) өту үшін мына қатынас қолданылады.

![]() ,

,

ал Пирс базисіне (НЕМЕСЕ-ЕМЕС) өту үшін, алдымен іздейтін функцияны терістеу жолымен бастапқы буль түрін алған ыңғайлы, содан кейін НЕМЕСЕ-ЕМЕС базисіне келесі қатынаспен өтуге болады

![]() .

.

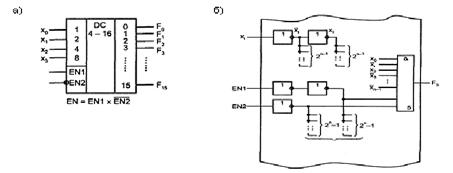

2.2 Екілік дешифраторлар

Дешифратордың шығысында кіріс екілік кодқа тәуелді шығыс тізбегінен бір тек қана біреуі қозғалады. n кірісі бар екілік дешифратордың n-разрядты екілік кодта әртүрлі комбинация мәндеріне сәйкес келетін 2n шығыстары болуы керек.

2.1 сурет - Дешифратордың шартты белгісі (а) және (б) схемасы

Дешифраторлардың шартты белгілерінде DC әріптері көрсетіледі (ағылшынша Decoder). Дешифратор кірістері оларды екілік салмақпен белгілеуге қабылдаған. Дешифратордың ақпараттық кірісінен басқа, EN (Enable) деп белгіленетін бір немесе бірнеше кірістері болады.

![]()

![]()

……………………..

![]()

Стандартты дешифраторлардың аз разрядтылығы олардың разрядтылығын өсіру талабын қояды. Ол үшін кіріс сөздер өрістерге бөлінеді. Кіші разрядты өріс разрядтылығы дешифратор кірістерінің сандарына сәйкес келеді. Қалған үлкен разрядтар өрісі кіші разрядтар өрісінің кодын шешетін дешифраторлардың біреуінен жұмыс істеуге сигналдар алу үшін қызмет етеді.

Мысал ретінде, 2.2-суретте «3-8» және «2-4» дешифраторлары көмегімен бес разрядты екілік код дешифрация схемасы келтірілген.

2.2 сурет - Дешифратор көлемінің өсу схемасы

Керекті 32 шығысты алу үшін «3-8» дешифраторының төртеуінен бағана құрылады. «2-4» дешифраторы кіріс кодының екі үлкен разрядын қабылдайды. Осы дешифратордың қозғалған бірлік шығысы бағананың бір дешифраторын оның кіру рұқсатымен ашады. Бағанадан алынған дешифратор кіріс сөздің үш кіші разрядының шифрын шешеді. Әрбір кіріс сөзге тек бір шығыстың қозғалысы сәйкес келеді.

Мысалы, х4х3х2х1х0 = 110012 = 2510 сөзін шешу кезінде дешифратор кірісінің бірінші белдеуінде оның шығысын үшінші нөмірге қозғалтатын 11 коды бар, ол DC4 жұмысына мүмкіндік береді. DC4 кірісінде 001 коды әсер етеді, сол себепті, бірлік оның бірінші шығысында пайда болады.

Схемалардың жұмысына рұқсат пен тиым бірінші белдеу дешифраторының EN кірісі бойынша жүзеге асады.

2.2.1 Екілік шифраторлар.

Екілік шифраторлар дешифраторға қарама-қарсы операцияларды орындайды: шифратордың бір кірісі қозғалғанда, оның шығысында қозғалған кіріс желінің екілік коды қалыптасады. Екілік шифратор 2n кіріске және n шығыстарға ие.

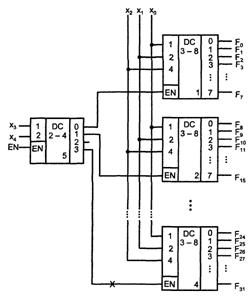

2.3 Мультиплексорлар мен демультиплексорлар

Мультиплексорлар бір кіріс каналдарын шығысқа басқарушы сөз басқаруымен қосуды жүзеге асырады. Арналардың разрядтығы әртүрлі болғандықтан, көп разрядты сөздер коммутациясына арналған мультиплексорлар бір разрядтылардан құралады.

2.3 сурет - Мультиплексор моделі (а) және ЖӘНЕ-ЕМЕС элементтеріндегі мультиплексор схемасы (б)

Мультиплексор кірістері екі топқа: ақпараттық және мекен-жайлық болып бөлінеді. Мультиплексор жұмысын көп позициялы кілттер көмегімен оңай көрсетуге болады (2.3,а суретті қара). Мекен-жайлық А коды айырып-қосқышқа F шығысты хi ақпараттық кірістің біреуімен қосып, нақты дәреже береді.

Нөлдік мекен-жайлық кодта айырып-қосқыштар хо жоғарғы дәрежеге ие, кодты бірлікке көтеріп, көрші дәрежеге х1 өтеді.

Мультиплексор жұмысы былай көрсетіледі

![]() .

.

Мекен-жайлық кодтың кез-келген мәнінде барлық буындардың біреуінен басқасы нөлге тең. Нөлдік емес буын хj тең, мұндағы: j – ағымдағы мекен-жайлық кодтың мәні.

Сұлбатехникалық мультиплексор айырып-қосқыш көрсеткішінің электронды версиясынан ерекшелігі оның біржақты мәліметтер таратуын ескере отырып, жүзеге асырады. 2.3,б суретте төрт ақпараттық, екі мекен-жайлық және Е жұмысқа рұқсат кірістері бар мультиплексор көрсетілген. Жұмысқа рұқсат болмаған кезде (Е = 0) F шығысы ақпараттық және мекен-жайлық сигналдарға тәуелсіз түрде нөлге айналады.

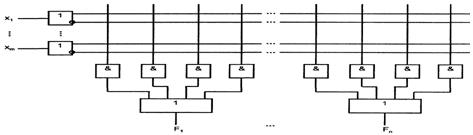

2.4 суретте, «32 - 1» мультиплексорының (қысқартылған MUX ағылшыннан Multiplexer) функцияларын орындайтын және аз көлемді 5 мультиплексорда құрылған пирамидалы схема көрсетілген.

3 Дәріс. Әмбебап логикалық модульдер

Функцияның n-аргументтері

![]() тең

екені белгілі. n өскен сайын функция саны өте тез өседі. ӘЛМ-нің

әмбебаптығы оны аргументтің берілген сандары үшін, кез-келген

функция күйіне келтіруге болады.

тең

екені белгілі. n өскен сайын функция саны өте тез өседі. ӘЛМ-нің

әмбебаптығы оны аргументтің берілген сандары үшін, кез-келген

функция күйіне келтіруге болады.

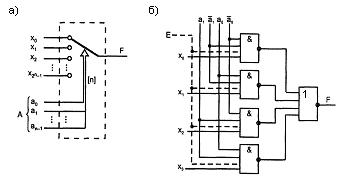

3.1 ӘЛМ-ді күйге келтірудің бірінші әдісі

Күйге келтірудің бірінші әдісі:

кейбір кірістерді бекіту болып табылады. Бұл әдіс үшін n

аргументтер саны мен 2n күйге келетін кірістер саны арасындағы

қатынастар нақтырақ болады. Онда, күйге келтіру коды

үшін комбинация саны функция санына тең –

![]() .

Осы кезде мекен-жайлық кірістерде – функция аргументтері, ал

ақпараттық кірістерде – күйге келтіру сигналдары беріледі (3.1

суретті қара).

.

Осы кезде мекен-жайлық кірістерде – функция аргументтері, ал

ақпараттық кірістерде – күйге келтіру сигналдары беріледі (3.1

суретті қара).

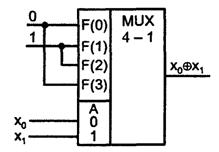

3.1 сурет - ӘЛМ ретінде мультиплексор қолдану схемасы

Сондықтан, ӘЛМ ретінде мультиплексор қолдану үшін оның кірістерінің мәндерін өзгерту керек.

Шынымен де, әрбір аргумент жинауға күйге келтірудің бір шығысына жіберу сәйкес келеді. Егер осы сигнал осы аргумент жинауда функция мәні болса, онда мәселе шешілді. Әртүрлі функциялар үшін күйге келтірудің әртүрлі кодтары сәйкес келеді: 0 және 1.

3.2 суретте, «4 - 1» мультиплексоры көмегімен ![]() мәнді әртүрлі функциялар

келтірілген.

мәнді әртүрлі функциялар

келтірілген.

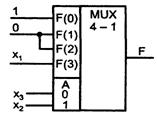

3.2 сурет – «НЕМЕСЕ-ні қоспағанда» функцияны жүзеге асыратын ӘЛМ схемасы

Күйге келтірілетін кірістердің үлкен мәндері ӘЛМ-ді жүзеге асыруды қиындатады.

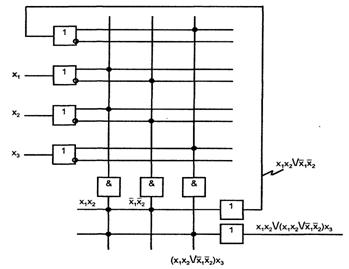

3.2 ӘЛМ-ді күйге келтірудің екінші әдісі

Күйге келтірудің кірістерін азайту күйге келтірілетін сигналдар алфавитін кеңейтумен аяқталады. Егер {0,1} алфавитінен {0,1,xi } алфавитіне өтсек, онда, аргументтердің кірістерінің саны бірге, ал күйге келтіру кірістері екіге кемиді, мұндағы xi – бір аргумент литералы. Бір аргументті күйге келтіру сигналдары қатарына өткізсек, өзімен бірге ешқандай схемалық өзгерту жасамайды. Осы құрылғыда тұрақтыларды күйге келтіруге қарағанда, аргументтер саны бір бірлікке артық функция жүзеге асады.

Жаңа алфавит үшін күйге келтіру коды келесі түрде болады. Аргументтер xi болмағанда, дара xi аргументінің функциясы болатын, оларды бекіту ізделетін функция өрнегіне сәйкес келетін мекен-жайлық кодқа беріледі. Бұл қалдық деп аталатын функцияны күйге келтірілетін кіріске беріп керегі жоқ.

Егер ізделетін функция n аргументке тәуелді болса және күйге келтірілетін сигналдарда кез-келген аргумент ауысуы мүмкін болғандықтан, күйге келтірілетін сигналдар санына бір аргумент ауыстырылса, онда тапсырманы шешудің n нұсқасы пайда болады.

Күйге келтірілетін сигналдар, функциядағы кіру саны ең аз аргументті өткізеді. Бұндай жағдайда, күйге келтірілетін сигналдар арасынан ӘЛМ-ді жүзеге асыру схемасын жеңілдететін тұрақтылар саны көбейеді.

3.3 суретте функцияны көрсететін үш

аргументтің![]() мысалы келтірілген.

мысалы келтірілген.

3.3 сурет - Үш аргументпен функцияны көрсету мысалы

Функцияны көрсетуге енудің минималды саны, күйге келтірілетін сигналдар санына өтетін х1 айнымалыға ие. Қалдық функция 3.1 кестемен анықталады

3.1 кесте

|

x2 |

x3 |

Fост |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

х1 |

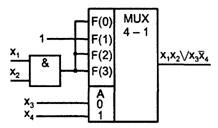

Егерде, күйге келтірілетін сигналдарға екі

аргумент өткізсек, онда қосымша логикалық схемалар

ӘЛМ-ді қиындатпайтын, екі кірісті вентилді болады. Бұл

жағдайда мультиплексорға екі айнымалының барлық

функцияларын қалыптастыратын қалдық функциялардың

өнімінің блогын қосу керек. Күйге келтірудің {0,1,х1,х2}

алфавитінде, төрт аргумент ![]() функциясын көрсету мысалы 3.3 суретте

келтірілген.

функциясын көрсету мысалы 3.3 суретте

келтірілген.

3.3 сурет – Төрт аргумент функциясын көрсету мысалы

Осы мысал үшін қалдық функция 3.2 кестесімен анықталады.

3.2 кесте

|

X4 |

x3 |

Fост |

|

0 |

0 |

х1х2 |

|

0 |

1 |

1 |

|

1 |

0 |

х1х2 |

|

1 |

1 |

х1х2 |

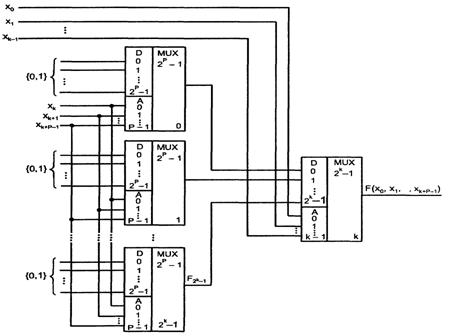

3.3 ӘЛМ-нің пирамидалық құрылымы

Күйге келтірілетін сигналдарда үш немесе одан көп айнымалылар есебінен күйге келтіру алфавиттерін ары қарай кеңейту үш және одан да көп айнымалылардың қалдық функцияларын есептеуді талап етеді. Осындай функцияларды мультиплексор көмегімен есептеу пирамидалық құрылымға келтіреді (3.4 суретті қара), бірінші белдеу мультиплексоры қалдық функцияны жүзеге асырады, ал екінші белдеу мультиплексоры ізделетін функцияны өңдейді.

0 және 1 тұрақтыларымен электронды күйге келтіруде схема n аргументтер функциясын жүзеге асырады, мұндағы n = k + р, k – екінші белдеу мультиплексорына берілетін аргументтер саны, р – қалдық функцияға тәуелді, 0...2k - 1 бірінші белдеу мультиплексорымен көрсетілетін аргументтер саны.

Схемада аппараттық шығынды азайту үшін бағанадағы мультиплексор санын азайтуға тырысу керек, k аз және сәйкесінше р көп болғандықтан, олардың k + р қосындысы n-ға тең.

Бірінші белдеу мультиплексорының күйге келтіру сигналдарын әртүрлі тәсілдермен іздеуге болады:

1) Күйге келтіру сигналдарын және қалдық функцияларды алу үшін мультиплексордың мекен-жайлық кірісіне берілетін аргументтер жиынтығын бекітумен (3.1 және 3.2 кестелерді қара).

2) Шеннон бойынша функцияларды ыдырату көмегімен.

Аргументтерді жекелеп ыдырату келесі түрде болады:

![]() .

.

Екі аргумент бойынша ыдырату келесі түрде болады:

![]() k

аргументі бойынша ыдырату:

k

аргументі бойынша ыдырату:

![]()

![]() .

.

3.4 сурет – ӘЛМ-нің екі белдеулі схемасы

Ыдырату формуласының құрылымы екі белдеулі ӘЛМ-ді толығымен жүзеге асыруға сәйкес келеді. Бірінші белдеуде n - k аргументтеріне тәуелді, k аргументі функциясын көрсететін мультиплексор екінші белдеуді күйге келтіретін Fi, (i = 0,..., 2k - 1) функциясы жүзеге асырылады.

3) Күйге келтірілетін сигналдарды функциялардың ақиқат кестесінен тікелей алуға болады.

Төрт айнымалылы х3х2х1х0

функциясы

және х3 айнымалысы аргументтер векторы үлкен

разрядтар болып саналатын болсын. Функция бірлік мәндерді

қабылдайтын, аргументтер жиынтығы аударым түрінде берілген,

сондай-ақ ондық мәндер жиыны берілген: 3, 4, 5, 6, 7, 11, 15.

Бұл функцияның талдаушылық мәні мынадай:

![]() .

.

Функция мәндері 3.3 кестеде келтірілген.

3.3 кесте

|

х3 |

x2 |

x1 |

x0 |

F |

|

0 0 |

0 0 |

0 0 |

0 1 |

0 0 |

|

0 0 |

0 0 |

1 1 |

0 1 |

0 1 |

|

0 0 |

1 1 |

0 0 |

0 1 |

1 1 |

|

0 0 |

1 1 |

1 1 |

0 1 |

1 1 |

|

1 1 |

0 0 |

0 0 |

0 1 |

0 0 |

|

1 1 |

0 0 |

1 1 |

0 1 |

0 1 |

|

1 1 |

1 1 |

0 0 |

0 1 |

0 0 |

|

1 1 |

1 1 |

1 1 |

0 1 |

0 1 |

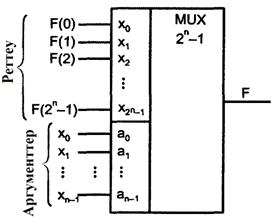

ӘЛМ-ді 0 және 1 тұрақтыларымен электронды күйге келтіргенде «16 - 1» көлемді мультиплексор талап етіледі, ӘЛМ-нің күйге келтірілетін кірістеріне кестедегі функция мәндері беріледі.

Күйге келтірілетін сигналдарға хо ауыстырғанда ({0,1,хо} (күйге келтіру алфавиті), айнымалылар векторы болып табылатын х3х2х1 аргументтермен қалдық функцияны табу керек. Бұл айнымалылардың әрбір комбинациясы 3.3 кестенің екі аралас жолдарымен кездеседі. Кестені жолдардың аралас жолдарымен қарасақ (жеке ұяшықтарға бөлінген), қалдық функцияның 3.4 кестеге сәйкес келетінін көруге болады.

3.4 кесте

|

х3 |

х2 |

х1 |

Fост |

|

0 0 |

0 0 |

0 1 |

0 х0 |

|

0 0 |

1 1 |

0 1 |

1 1 |

|

1 1 |

0 0 |

0 1 |

0 х0 |

|

1 1 |

1 1 |

0 1 |

0 х0 |

ӘЛМ-нің осы нұсқасын жүзеге асыру үшін "8-1" мультиплексоры жеткілікті, бірақ басқа функцияға өту үшін тек күйге келтіру кодын ауыстырып қана қоймай, күйге келтірілетін басқа кірістерде айнымалылар литерін беру үшін оның коммутациясын да ауыстыру қажет.

4 Дәріс. Компараторлар және бақылау схемалары

4.1 Компараторлар

Компараторлар (салыстыру құрылғысы) екі сөз арасындағы қатынасты анықтайды. Басқаларын анықтайтын негізгі қатынастар деп "тең" және "үлкен"-ді айтуға болады.

Компараторлар функция белгіленуіндегі индекстерінде көрсетілген шарт сақталса, онда 1 мәнін қабылдайды. Мысалы, А = В болса, онда FA = B = 1, ал нөлдік мән қабылдаса А ≠ В.

Негізгі қатынас ретінде "тең" және "үлкен" қабылдасақ, онда қалғанын былай жазуға болады:

![]()

Цифрлық элементтер сериясында ретінде әдетте үш кірісті компараторлар бар: "тең", "үлкен" және "кіші" (4.1 суретті қара). Шығыс функциясының индексінде жазбаны қысқарту үшін тек А сөзі көрсетіледі.

4.1 сурет - Үш шығысты компараторлардың шартты белгілері

Тепе-теңдікте салыстыру құрылғысы екі сөздің бір аттас разрядтарында разряд бойынша операция негізінде құрылады. Егерде олардың бір аттас разрядтары тең болса, екеуінде де нөл немесе бірлік болса, онда сөздер тең болады. Разрядтар теңдігі белгісі

![]() .

.

Сөздер теңдігі белгісі

![]()

4.2 суретте ЖӘНЕ-ЕМЕС базисінде тепе-теңдіктегі компаратор схемасы көрсетілген.

4.2 сурет - Тепе-теңдіктегі компаратор схемасы

Бір разрядты сөз үшін "үлкен"-де

компаратор құру ![]() функциясын жүзеге асыруды талап етеді

(4.1 кестеге қараңыз).

функциясын жүзеге асыруды талап етеді

(4.1 кестеге қараңыз).

4.1кесте

|

a |

b |

FA>B |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Жалпы жағдай үшін n-разрядты сөз мынаған тең

![]() .

.

4.2 Бақылау схемасы

Қателерді табу есептері әртүрлі әдістермен жүзеге асады. Бақылау функциясын қосу әрқашанда артықшылықпен байланысты – жаңа мүмкіндіктер үшін төлем қосымша аппараттық және уақытша шығындарға әкеледі.

4.2.1 Мажоритарлы элементтер.

Мажоритарлы элемент тапсырмалары -"дауыс беру" өткізіп, кірістің біршамасына сәйкес келетін шығыс шамасына беру. Мажоритарлы элементтерде кірістер тек қана тақ сан болады.

Функцияланған мажоритарлы элемент F1, F2, және F3 мәндері келіп түсетін кірістерде және дауыс беру нәтижесінде өңделген F шығыс шамасы 4.2 кестеде көрсетілген.

4.2 кесте

|

F1 |

F2 |

F3 |

F |

a1 |

a0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

0 |

0 |

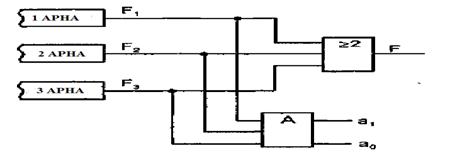

F шығысынан басқа, кестеде F=1 болғандағы бас тартушы арнаның нөмірін көрсетуші, екі разрядты кодтың үлкен және кіші разрядтары - a1, ао шығыстары берілген (4.4 суретті қара). Кестеден, оңай түрленуден кейін төмендегідей келесі функцияны алуға болады:

![]()

4.4 сурет - Мажоритарлы элементтермен дауыс беру схемасы

Схемада мажоритарлы элемент типінен аса көп сенімділік талап етіледі, егер ол бас тартса, онда схеманың барлық қорын пайдасыз қалдырады.

4.2.2 Модуль 2 бойынша бақылау.

ЦҚ қалыпты жұмыс істеу үшін маңызды шарт – мәліметтерді дұрыс тарату мен сақтауды бақылау.

Кодтық комбинация – қабылданған алфавит символдарын жинақтау.

Код – ақпаратты бейнелеуге арналған кодтық комбинация жиынтығы.

Екі кодтық комбинация арасындағы кодтық арақашықтық – осы комбинация бір-бірінен ерекшелінетін разрядтар саны.

Ең аз кодтық арақашықтық dmin – осы кодқа кіретін, кез-келген комбинациялар жұбы үшін ең аз кодтық қашықтық.

Қателер ұзақтығы дегеніміз осы сөздегі қателер саны (дұрыс емес разрядтар саны).

Кодтау теориясынан кодтарды қолданғанда қателерді тауып және түзеу шарттары белгілі:

![]()

мұндағы dmin – кодтың ең аз арақашықтығы;

гтаб және гтүз – сәйкесінше қателерді тауып және түзеу ұзақтығы.

Код салмағы – осы комбинациядағы бірліктер саны.

Екілік код үшін ең аз кодтық қашықтық dmin = 1, сол себепті, ол өзіне әсер ететін қандайда бір мүмкіндікке ие емес. Ең болмаса, бірлік ұзақтықтағы қателерді табу мүмкіндігіне ие болу үшін, ең аз кодтық арақашықтықты 1-ге көтеру керек. Бұл модуль 2 бойынша бақылау үшін жасалған (тақ/жұп бойынша бақылау).

Бақылаудың бұл әдісінде сөздер барлық кодтық комбинациялардың әрқайсысын жұп етіп жасау үшін мәндерді таңдап, бақылау разрядтарымен толықтырылады. Бірлік қатеде жұп (тақ) кодтық комбинацияда оның салмағы өзгереді, ал мұндай комбинация бұл кодқа жатпайды. Екілік қателікте комбинация жұптылығы (тақ) бұзылмайды – мұндай қателер ашылмайды. Бақылау разряды бар кодта

dmin = 2.

Жұп бойынша бақылау кезінде кодтық комбинация салмағы жұп, ал тақ бақылау кезінде тақ болады.

Модуль 2 бойынша бақылау түйіншек схемасы көмегімен жүзеге асады. Машықтану үшін типтік көп белдеулі түйіншек схемасы пирамида типті болады.

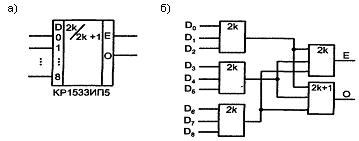

Модуль 2 бойынша ИС түйіншекке мысал ретінде КР1533 сериялы ИП5 микросхемасы қызмет етеді (4.5,а суретті қара). Схема байт түйіншегіне тоғыз бақылау разрядымен жіберілетін 9 кірістен тұрады. Схеманың екі шығысы Е (Even) және О (Odd) болады. Егерде кіріс комбинацияның салмағы жұп болса, онда Е = 1 және О = 0 , егер салмағы тақ болса, керісінше болады.

4.5 сурет - ИКР1533ИП5 микросхемасы

Сұлбатехникалық ИС КР1533ИП5 тақ/жұп типті үш кірісті элементтерден құрылған пирамидалы құрылымды көрсетеді (4.5,б суретті қара).

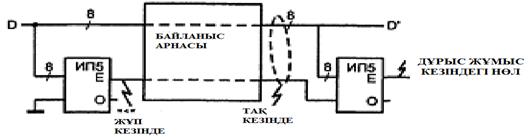

Модуль 2 бойынша бақылаумен мәліметтерді тарату 4.6 суретте көрсетілген. Кіріс мәліметтер D арқылы белгіленген, ал каналдан шығыстағы мәліметтер байланысы D' арқылы белгіленген, олар қателерді іздеуде өзгеруі мүмкін.

4.6 сурет – ИП5-ті байланыс арнасын бақылау үшін қолдану

4.2.3 Хемминг кодын пайдаланып бақылау.

Хемминг кодын қолдану қабылдаудың соңында бірлік қателерді түзетуге мүмкіндік береді. Хемминг кодының кодтық комбинациясын алу үшін ақпараттық сөзге бірнеше бақылау разрядтары қосылады. Қабылдаудың бақылау разрядтарының мәнін анықтау мақсатымен бақылау разрядтары 2i (i = 0, 1, 2,...), немесе 1, 2, 4, … нөмірлі ұстанымдарға ие.

Әрбір бақылау разряды кодтық комбинацияның кейбір топтық разрядтарымен қауымдасады және өзі кіретін топ салмағын жұп/таққа шығарады.

Бірінші бақылау разрядына (1 - реті) екілік кодқа хх...хх1 сәйкес келетін нөмірлі разрядтар тобына кіреді, мұндағы х – о немесе 1. Басқаша айтқанда, бірінші топқа тақ нөмірлі 1, 3, 5, 7, ... разрядтар кіреді.

Екінші бақылау разрядына (2 - реті) екінші оң жақтағы разрядта бірлікке ие немесе хх...х1х екілік кодқа сәйкес келетін нөмірлері бар разрядтар тобына кіреді. Бұл нөмірлер 2, 3, 6, 7, ... .

Үшінші бақылау разрядына (4 - реті) үшінші оң жақтағы разрядта бірлікке ие немесе екілік хх...1хх кодына сәйкес келетін 4, 5, 6, 7, ... нөмірлі разрядтар кіреді.

Бақылау разрядтары өздерінің топтарының салмақтарын жұп/таққа шығарады. Одан кейін, қабылдауды анықтау үшін жұптар бойынша бақылау жүргізіледі. Модуль 2 бойынша тексеру, кодтық комбинацияда қанша бақылау разряды болса, сонша болады. Егерде кодтық комбинацияда қате болса, онда бір тексеруде ол айтылады, ал басқаларда жоқ. Бұл қате болған разрядты анықтауға мүмкіндік береді. Сөздің дұрыс мағынасын анықтау үшін тек қана қате разрядты қайтадан терістеу керек.

Мысалы: төрт разрядты ақпаратты сөз А = а3а2а1а0 = 0110 үшін Хемминг кодын құрыңыз (4.3 кестені қара).

4.3 кесте

|

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

|

р |

а3 |

а2 |

а1 |

р3 |

а0 |

р2 |

р1 |

|

0 1 1 0 1 0 |

0 0 0 0 0 0 |

0 0 0 0 1 1 |

0 0 1 1 0 0 |

0 0 1 1 1 1 |

0 1 0 1 0 1 |

0 1 0 1 1 0 |

0 1 1 0 0 1 |

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

1 0 … 1 |

0 1 … 1 |

1 0 … 1 |

1 0 … 1 |

0 1 … 1 |

1 0 … 1 |

0 1 … 1 |

0 0 … 1 |

Р арқылы кестеде барлық кодтық комбинациялар үшін ортақ бақылау разрядтары белгіленген, p1, р2, р3 арқылы - бірінші, екінші және үшінші бақылау разрядтары.

Р разрядын ескермей-ақ, дұрыс кодтық комбинация түрі мынадай:

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

1 |

Екінші сол жақта ( 6 - разрядта) қате болып, комбинация қабылдансын делік:

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

|

0 |

0 |

1 |

0 |

0 |

1 |

1 |

Бірінші тексеру (тақ нөмірлі разрядтар топтары бойынша) бұл топта қателік жоқ екенін көрсетеді, тексеру нәтижесін нөл деп белгілейміз.

Екінші тексеру (2, 3, 6, 7 разрядтары бойынша) комбинация салмағының жұптылығының бұзылуын байқайды, тексеру нәтижесін бірлікпен белгілейміз.

Үшінші тексеру (4, 5, 6, 7 разрядтары бойынша) мұнда да жұптылық бұзылуы байқалады, нәтижесі бірлікпен белгіленеді.

5 Дәріс. Сумматорлар

Сумматорлар сандарды арифметикалық біріктіру мен азайтуды орындайды, процессорлардың арифметика-логикалық құрылғылар (АЛҚ) схемаларының ұйытқысы болып табылады.

5.1 Бір разрядты сумматор

Бір разрядты сумматордың үш кіріс (екеуі қосылмалы және біреуі алдыңғы разрядтан өтетін) және екі шығысы (келесі разрядқа өтетін және қосылатын) бар.

5.1 кесте - Бір разрядты сумматордың ақиқат кестесі

|

ai |

bi |

ci-1 |

Si |

Ci |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

Қосылатын және өтетін функциялардың талдау өрнектері мынаған тең (С ағылшыннан carry)

![]() .

(5.1)

.

(5.1)

![]() .

(5.2)

.

(5.2)

5.1 кестеден, бірінші және соңғы жолдардан басқасы төмендегідей екенін көруге болады

![]() .

(5.3)

.

(5.3)

(5.3)

формуласы

5.1 кестенің барлық жолдары үшін дұрыс болатынын

көруге болады, егер 1 – жолда ![]() емес,

емес,

![]() болса, онда

(5.3)

формуласы бойынша

0=1∙0 (

болса, онда

(5.3)

формуласы бойынша

0=1∙0 (![]() өткізу функциясын қайтадан терістеу) теңдігі

сақталатын еді және соңғы жолға

өткізу функциясын қайтадан терістеу) теңдігі

сақталатын еді және соңғы жолға

![]() қосыңыз.

қосыңыз.

(5.3) формуласын ескере отырып, мынадай формула аламыз

![]() .

(5.4)

.

(5.4)

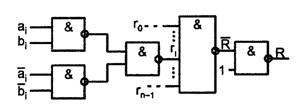

(5.2 және 5.4) өрнектерді жүзеге асыратын сумматордың схемасы 5.1,а суретінде көрсетілген.

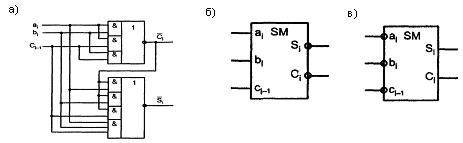

5.1 сурет - Бір разрядты сумматор схемасы және шартты белгісі (б,в)

Si қосылу функциясы мен Ci өту функциясы өздігінен екі түрлі қасиетке ие (5.1кестеге қара): барлық аргументтерді терістегенде функцияның барлық мәндері терістеледі

![]() . (5.5)

. (5.5)

5.2 Тізбектелген сумматор

Тізбектелген операнттарға арналған сумматор тек бір ғана бір разрядты сумматордан тұрады, ол ең кішісінен бастап разрядтарды кезектесіп өңдейді. Кіші разрядтарды қосып, нәтиже мен тасымалдау кіші разрядтары үшін бір разрядты сумматор бір такттіде сақталынатын қосынды өңдеп шығарады. Келесі тактіде кіші разрядтан ауысатын a1 және b1 қосылмалы жаңадан түскен разрядтар жиналады.

Тізбектелген операнттар сумматоры схемасында (5.2,а суретті қара) сумматордан басқа, A,B қосылмалы қозғалатын регисторлар және S қосынды, сондай-ақ, ауысуды есте сақтайтын D-триггер бар. A,B,S регисторлары және D-триггері синхроимпульстармен СИ тактіленеді. 5.2,6 суретте , екі операнттың қосылу операциясына 101 + 110= 1011 немесе ондық өрнекте 5 + 6 = 11 сәйкес келетін уақыттық диаграммасы көрсетілген.

5.2 сурет - Тізбектелген сумматор схемасы (а) және уақыттық диаграмма (б)

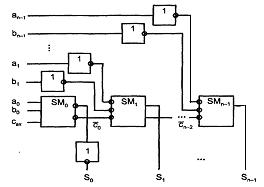

5.3 Тізбектелген тасымалдауы бар параллелді сумматор

Тізбектелген тасымалдануы бар параллельді операнттарға арналған сумматор тасымал тізбегімен тізбектеліп қосылған бір разрядты тізбек секілді құрылады. Қосылу мен ауысу функциялары өздігімен екіжүзділенетін (5.5) болғандықтан, қосылу мен тасымалдың терістелуін өңдейтін бір разрядты сумматордың схемасы үшін тізбек, 5.3 суретте келтірілген түрге ие. Сумматор разрядына терістелген аргументтер берілу керек болса, олардың желісінде терістегіш бар, ал терістелген қосынды өңделсе, онда терістегіш шығыс тізбекке жалғанады.

5.3 сурет - Тізбектелген тасымалдаулы параллельді сумматор схемасы

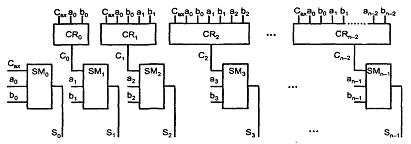

5.4 Параллельді тасымалдауы бар параллельді сумматор

Параллельді операнттар үшін параллельді тасымалдаулы сумматорлар максималды тезәсерлілікті алу үшін жасалған.

Параллельді ауысулы сумматорда разрядты торды жағалай ауысатын тізбектеп таралуы болмайды. Барлық разрядтарда нәтиже біруақытта, уақытқа параллелді өңделеді. Берілген разряд үшін ауысу сигналы, ауысуды өңдеуге қажетті, кірісіне барлық айнымалылар келіп түсетін, оның бар-жоғына тәуелді арнайы схемамен қалыптасады. Разрядты схемалардағы бір разрядты сумматорлар оңайлатылған, олардан ауысу шығысы талап етілмейді, қосылудың бір шығысы жеткілікті (5.4 суретті қара). CR белгіленуі саrrу (ауысу) сөзінен алынған.

5.4 сурет - Параллельді тасымалдаулы сумматор схемасы

Егер берілген разряд шығысында кіріс тасымалдың бар-жоғына қарамастан тасымал пайда болса, генерация функциясы 1 қабылдайды. Бұл gi = аibi функциясы екені белгілі.

Егер, берілген разряд шығысында тасымал тек

кіріс тасымалы болғанда ғана пайда болса, онда

айқындылық функциясы 1 қабылдайды. Бұл функция

hi

=

aivbi.

Нақтап айтқанда,

![]() , бірақта, аi

=

bi = 1

кезінде, НЕМЕСЕ және БЕКІТУШІ НЕМЕСЕ функциялары

арасында айырмашылық пайда болады, ауысым gi = 1

үшін қалыптасады, айқындылық функциясын

дизъюнкцияға ауыстыру мүмкін. Енді,

ауысым сигналы үшін өрнекті мына түрде жазуға болады

, бірақта, аi

=

bi = 1

кезінде, НЕМЕСЕ және БЕКІТУШІ НЕМЕСЕ функциялары

арасында айырмашылық пайда болады, ауысым gi = 1

үшін қалыптасады, айқындылық функциясын

дизъюнкцияға ауыстыру мүмкін. Енді,

ауысым сигналы үшін өрнекті мына түрде жазуға болады

![]() .

.

i нөмірлі туынды разряд үшін былай жазуға болады

![]() . (5.6)

. (5.6)

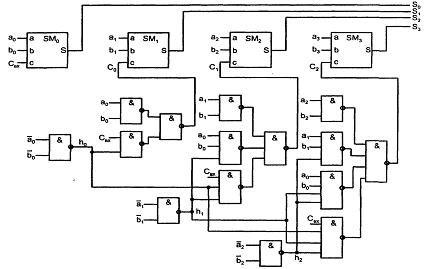

ЖӘНЕ-ЕМЕС элементтеріндегі болжамды схема (стандартты элементтерде ЖӘНЕ бойынша сегіз элементке дейін болады). Алынған өрнектің аударуы ЖӘНЕ-ЕМЕС базисінде мынандай өрнекке ие

![]() ,

,

![]() ,

,

![]() . (5.7)

. (5.7)

5.5 сурет - Параллельді ауысулы сумматор схемасының нұсқасы

Сумматор схемасы алынған өрнекке сәйкес келеді (5.5 суретті қара). Паралельді тасымалдаулы сумматор беделін көтеретін, разрядтылық диапазоны үлкен емес. n = 3...4 дейін тізбектелген ауысулы, n = 8 дейін паралельді ауысулы, n = 8 кейін топтық құрылымды сумматорлар қолданылады.

6 Дәріс. АЛҚ және матрицалық көбейткіштер

6.1 Арифметикалы-логикалық құрылғы

Негізгі АЛҚ (Arithmetic-Logic Unit) схемасы функционалды мүмкіндіктерді кеңейтетін және оның қайта құрылуын бір операциядан басқаға өтуді қамтамасыз ететін сумматор. АЛҚ негізінен төрт разрядты және разрядтылықты өсіру үшін тізбектеліп немесе паралельді тасымалданумен қалыптасу біріктіріледі. Әртүрлі технологияларда АЛҚ-ның логикалық мүмкіндіктері ұқсас болады (ТТЛШ, КМОП, ЭСЛ) .

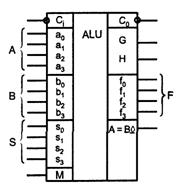

АЛҚ ( 6.1 суретті қара) А және В операнттарының кірістеріне, S операциясын таңдау кірісіне және орындалатын операция типін беретін сигналдың М (Mode) кірісіне ие: логикалық (М = 1) немесе арифметикалы-логикалық (М = 0). Операция нәтижелері F шығыстарында өңделеді, ал G және Н шығыстары АЛҚ көлемін өсіру кезінде паралельді тасымалдауды қамтамасыз ететін, шығыстары айқындылық және генерация функцияларын береді. Со сигналы – шығыс тасымал, ал А = В шығысы ашық коллекторлы тепе-теңдікке салыстыратын шығыс.

6.1 сурет - АЛҚ-ның шартты белгісі

АЛҚ-ның орындайтын операцияларының тізімі 6.1 кестеде келтірілген. S3S2S1S0 екілік жүйедегі қысқалық үшін оларды ондық эквивалентпен көрсеткен. Кіріс тасымал 000Сi сөзінің кіші разрядына келіп түседі. Арифметикалық операцияларда разряд аралық тасымалдар ескеріледі.

Логикалық 16 операциялар екі айнымалының барлық функцияларын шығаруға мүмкіндік береді. Арифметикалы-логикалы операцияларда логикалық және арифметикалық операциялар бір уақытта кездеседі.

Мысалы, ![]() - бастапқыда разряд бойынша терістеу (В),

логикалық біріктіру (АvВ) және логикалық көбейту (АВ)

операцияларын орындайды, содан кейінкөрсетілген үлгімен

алынған екі төрт разрядты сандар арифметикалық түрде

қосылады.

- бастапқыда разряд бойынша терістеу (В),

логикалық біріктіру (АvВ) және логикалық көбейту (АВ)

операцияларын орындайды, содан кейінкөрсетілген үлгімен

алынған екі төрт разрядты сандар арифметикалық түрде

қосылады.

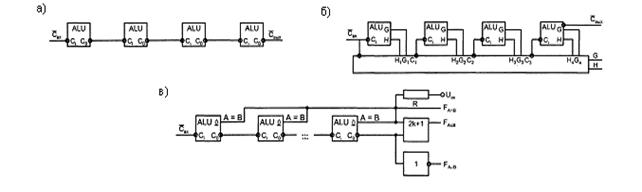

Үлкен көлемді сөздердегі операциялар кезінде АЛҚ тізбектеліп ұйымдасып, (6.2,а суретке қара) немесе паралельді тасымалдаумен бір-бірімен қосылады (6.3,б суретке қара). Соңғы жағдайда, АЛҚ-мен бірге микросхема – АЛҚ жеке айқындық және генерация функцияларын алатын жылдамдататын

тасымал блоктарын, сондай-ақ нақты формула бойынша тасымал сигналдарын шығарушы және кіріс тасымалдары қолданылады.

6.1 кесте – АЛҚ операцияларының тізімі

|

S |

Логикалық функциялар (М=1) |

Арифметикалы-логикалық функциялар (М=0) |

|

0 1 2 3 |

0000 |

A + Ci

1111 +Ci |

|

4 5 6 7 |

|

|

|

8 9 10 11 |

В АВ |

A + AB + Ci A + B + Ci

AB + 1111 + Ci |

|

12 13 14 15 |

1111

А |

A + A + Ci A v B + A + Ci

A + 1111 + Ci |

CRU блогы АЛҚ қызмет ететін барлық топтар үшін қажет болған жағдайда келесі дәреже бойынша паралель тасымалды ұйымдастыруға мүмкіндік беретін айқындылық және генерация функцияларын өңдейді (төрт АЛҚ ішінен бірнеше топтар арасында).

6.2 сурет - Тізбектеліп (а) және параллельді (б) тасымалдану кезіндегі АЛҚ-ның өсу және топтар үшін (в) компаратор функцияларын жүзеге асыру схемалары

6.2,в суретте АЛҚ топтары үшін сөздерді салыстыру үшін сигналдарды өңдеу тәсілдері көрсетілген. Тепе-теңдікке салыстыру шығысы ОК типті ығыстар үшін монтажды логика схемалары бойынша орындалады. Азайту режимінде АЛҚ жұмысы кезінде топтардың шығысында тасымалдау сигналдарын сөздерді теңестіру сигналдарымен құрамдастырып Fa≥b және Fa≤b функцияларын оңай алуға болады. Егер А<В болса, онда азайту кезінде үлкен разрядтан қарыз алу туындайды Fa≤b = 1. Егер де қарыз болмаса (А>В), онда Fa≥b = 1.

6.2 Матрицалы көбейткіштер

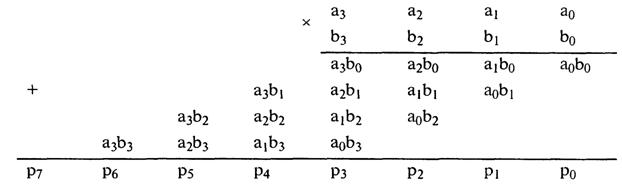

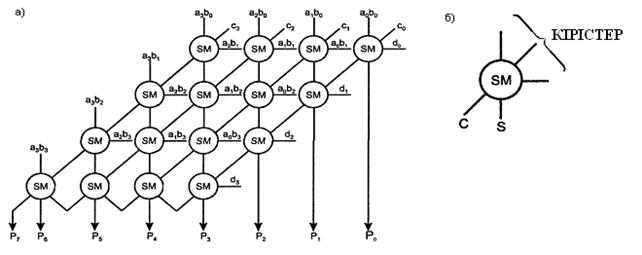

Матрицалы көбейткіштердің құрылымы көбейту операцияларын сипаттайтын математикалық өрнектердің құрылымымен тығыз байланысты. Екі таңбасыз екілік жүйе сандары болсын Am = am-1...ao және Bn=bn-1...bo. оларды еселеу "бағаналарды көбейту" схемасы бойынша орындалады. Егер сандар төрт разрядты болса m = n = 4, онда

aibj мүшелері, мұндағы i = 0... (m - 1) және j = 0... (n - 1), конъюктор уақытымен паралельді түрде өңделеді. Оларды бағана бойынша әртүрлі жолмен

орындауға болатын көбейту көбейткіштер үшін негізгі операцияларды құрайды.

Матрицалы қайта көбейткіштер қарапайым көбейткіш блоктары (КБ) немесе көбейтіп-қосқыш блоктары (КҚБ) болуы мүмкін, соңғысы көбейткіштердің көлемінің өсуіне жағдай жасайды.

КҚБ МСБ Р = Аm х Вn + Сm + Dn операциясын жүзеге асырады, ол туындыға екі буын қосады: біреуі көбейетін разрядтылыққа сәйкес келетін разряды, ал екіншісі m т. е. Көбейткішке екі қосылғыш қосады: біреуі m разрядты, көбейтінді разрядымен сәйкес келетін, екіншісі n разрядты, көбейткіш разрядымен сәйкес келетін.

6.2.1 Көбейткішті-қосындылы блоктар.

Көбейткішті-қосындылы блоктар конъюнкторлар жинағынсыз төртразрядты операндтар үшін, өңделген аibj түріндегі мүшелері 6.3, а суретте көрсетілген ( мұндағы бірразрядты сумматор үшін қолданылған белгілеу 6.3, б суретті қара).

6.3 сурет – Төртразрядты көбейткіштерге арналған КҚБ сызбасы (а) және осы сызба үшін бірразрядты сумматордың белгіленуі (б)

Теңразрядты сандардың КҚБ құру үшін n2 конъюкторлар және n2 бірразрядты сумматорлар керек.

6.2.2 Жедел көбейту сызбалары.

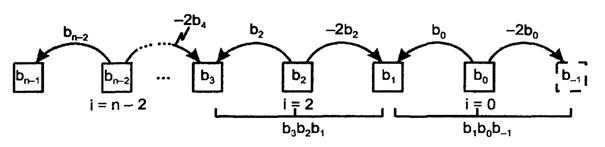

Модифицирленген алгоритм бойынша көбейту процесін қарастыралық. Бұнда көбейту бірден екі разрядқа артады. Жеке көбейткіштердің қосындысын азайту функциясы көбейту уақытын едәуір қысқартады. Осыған төмендегі талдауларға негізделген алгоритм алып келеді.

Мына көбейтіндіні есептеу керек болсын

![]() . (6.1)

. (6.1)

Тікелей (6.1) қатынасын қайта көбейту мына түрдегі жеке көбейтулерді орындаумен тікелей байланысты

Abi2i (i = 0...n - 1). (6.2)

Мұндай көбейтулер саны n көбейткішінің санына тең.

Мына қатынас көмегімен (6.1) өрнегінің түрін өзгертуге болады

![]() .

(6.3)

.

(6.3)

Бұл қатынас жеке көбейткіштер қосындысындағы дәрежелердің тізбектілігін сиретуге мүмкіндік тудырады. Мысалы, 6.4 суретте көрсетілгендей жұп дәрежелерді шығарып тастауға болады.

6.4 сурет – Жұп дәрежелерді шығарып тастау

Жұп (тақ) дәрежелерді шығарып тастау қалған жеке көбейтінділердің мәнін ғана өзгертіп қоймай , сонымен қатар олардың санын жуық шамамен екі есеге азайтып, көбейту нәтижесін тездетеді. (6.3) формуласы бойынша разрядтық торды кеңейту үшін (6.1) өрнегіндегі В көбейткіші үшін b222,bo2o,b-22-2 жұп дәрежелі мүшелерді «көршілерге таратады».

Осыдан соң кез-келген i-ші разряд үшін мына түрге келтіріледі

![]() .

(6.4)

.

(6.4)

Егер (6.1) және (6.4) өрнектерін салыстырсақ, онда жеке көбейтінділер екі есе азайды. Осы алгоритмді қолданған кезде бірден екі разрядқа көбейту туралы (i жұп разрядтан бастап коэффициенттері солдан i+1 және оңнан i-1 ).

(6.4) барлық мүмкін bi+1, bi, bi-1 үшін қолданып, жеке көбейтінділер үшін 6.2 кестесін құруға болады.

6.2 кесте

|

bi+1 |

bi |

bi-1 |

Жақша мәні |

Ri/2i |

Алу операциясы Ri/2i |

|

0 |

0 |

0 |

0 |

0 |

А нөлмен ауыстыру |

|

0 |

0 |

1 |

1 |

А |

А көшіру |

|

0 |

1 |

0 |

1 |

А |

А көшіру |

|

0 |

1 |

1 |

2 |

2А |

А солға жылжыту |

|

1 |

0 |

0 |

-2 |

-2А |

А солға жылжыту және А қос. кодқа ауыстыру |

|

1 |

0 |

1 |

-1 |

-А |

А қос. кодқа ауыстыру |

|

1 |

1 |

0 |

-1 |

-А |

А қос. кодқа ауыстыру |

|

1 |

1 |

1 |

0 |

0 |

А нөлмен ауыстыру |

Мысал.

1010-ды 0111-ге көбейту керек болсын, яғни 10∙7 = 70. Жеке көбейтінділерді сиреткен кезде тек тақтарын ғана қалдырамыз (6.4 суретті қара).

Енді (6.4) формуласы бойынша мынаны аламыз ![]() .

.

Алынған өрнектен көрініп тұрғандай В көбейткішінің разрядтық торын солдан 1 разрядқа және оңнан 2 разрядқа кеңейту керек, яғни

В = b4b3b2b1bob-1b-2 = 0011100.

Бірінші жеке көбейтіндіге bob-1b-2 = 100 үштігі сәйкес келеді. 6.2 кестеден осы үштікке мына жеке көбейтінді сәйкес екенін аламыз

R-1 = -2А∙2-1 = -А,

оны алу үшін қосымша А кодқа көшіру керек. А шамасының өзі разрядтық көбейту тор шегінде 0001010 сияқты болып жазылуы керек, оның кері коды 1110101 және қосымша коды 1110110 болады.

Екінші жеке көбейтіндіге b2b1bo = 111 үштігі сәйкес келеді, осыдан екінші жеке көбейтінді R1 = 0 тең болады ( 6.2 кестені қара).

Үшінші жеке көбейтіндіге b4b3b2 = 001 үштігі сәйкес келеді, осыдан оның түрі R3 = А∙23 = 1010000 ( А-ны 3 разрядқа солға жылжыту ) келтіріледі.

Берілген көбейту нәтижесін алу үшін жеке көбейтінділерді қосу қажет болады:

1110110

1010000

-----------

1000110 = 26 + 22 + 21 = 64 + 4 + 2 =70.

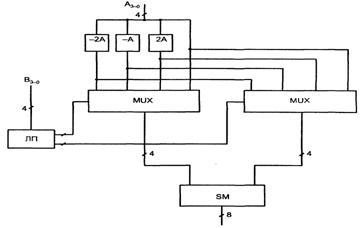

6.5 суретте тез көбейту алгоритмін іске асыру сызбасы көрсетілген

6.5 сурет – Тез көбейту сызбасы

А көбейгіші (-2А, -А, 2А), сызбалық тарату қажет етпейтін А-ның өзінен және нөлден басқа жеке көбейтінділердің барлық мүмкін варианттарын дайындайтын бірнеше түзеткіштер қатарына келіп түседі. В көбейгіші ЛТ логикалық түрлендіргіш ретінде түсіп, разрядтар үштіктерін сараптайды, оларды кодтайды және оларды мультиплексорларға (MUX) жеке көбейтінділердің сол немесе басқа варианттарының сигналдары түрінде береді

( 6.2 кестесін қара). Қорытынды нәтиже олардың разрядтық тордағы өзара ығысуын ескере отырып, жеке көбейтінділерді қосу арқылы алынады. Көбейткіш өлшемділігі «4х4».

7 Дәріс. Триггерлер және регистрлер

7.1 Триггерлер

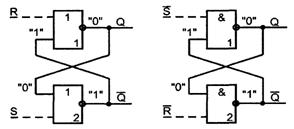

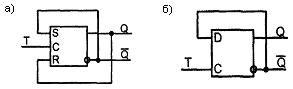

Триггерлер – құрамына сақтау элементі (фиксатор) және басқару сызбасы кіретін элементар автоматтар. Фиксатор бір-бірімен "айқасу" бойынша біреуінің шығысы екіншісінің кірісімен байланысқан екі индикатордан тұрады. Мұндай қосылу екі тұрақты күйлі тізбек береді ( 7.1 суретті қара). Егер инвертор 1 шығысында логикалық нөл болса, онда ол инвертор 2 шығысында логикалық бірді тудырады және керісінше болады.

7.1 сурет – Асинхрондық RS-триггерінің сызбасы

Орнатылған

сигналдар 7.1

суретте үзік сызықтармен көрсетілген. Латын

алфавитінің R әрпімен ( Reset дегеннен ) триггерді 0-ге қою

(ауытқу) сигналы белгіленген, ал S әрпімен ( Set дегеннен) – 1-ге

қою логикалық күй сигналы белгіленген . Триггер күйі Q

сияқты болып белгіленетін тура шығыс мәні бойынша немесе екінші

шығысты ![]() инверсерлік сигналымен есептеледі. RS-триггері

үшін НЕМЕСЕ-НЕ таңдалған сигналы 1 болып табылады, себебі

тек қана ол логикалық элементті 0-ге элементтің басқа

шығыстарындағы сигналдардан тәуелсіз келтіреді ( 7.1, а суретті

қара). RS-триггер үшін элементтердегі ЖӘНЕ-НЕ таңдалған

сигналы нөлдік болып табылады ( 7.1, б суретті қара).

инверсерлік сигналымен есептеледі. RS-триггері

үшін НЕМЕСЕ-НЕ таңдалған сигналы 1 болып табылады, себебі

тек қана ол логикалық элементті 0-ге элементтің басқа

шығыстарындағы сигналдардан тәуелсіз келтіреді ( 7.1, а суретті

қара). RS-триггер үшін элементтердегі ЖӘНЕ-НЕ таңдалған

сигналы нөлдік болып табылады ( 7.1, б суретті қара).

7.1.1 Триггерлерді кластарға бөлу.

Триггерлер логикалық құрылу принциптері мен ақпаратты жазу тәсілдеріне байланысты бірнеше түрге бөлінеді.

Логикалық құрылу принциптеріне қарай триггерлерді RS, D, T, JK және т.б. түрлерге бөледі. Сонымен қатар, бір уақытта бірнеше типтер орын алатын аралас триггерлер және күрделі кірісті логикалы триггерлер (кіріс топтарымен, бір-бірімен өзара логикалық тәуелділікте болатын) қолданылады.

RS түріндегі триггердің екі кірісі болады – бірге орнату (S) және нөлге орнату (R). S орнату және R лақтыру сигналдарын біруақытта беруге рұқсат етілмейді (сигналдардың бұл комбинациясы тиым салынған деп аталады).

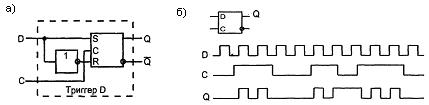

D түріндегі триггер ( Delay сөзінен алынған - ұстау) бір кірісті болып келеді. Оның күйі кіріс сигналын қайталайды, бірақ тактілік сигналымен кешігу анықталады.

Т түріндегі триггер әрбір кіріс сигналы түскен сайын өзінің күйін өзгертіп отырады. Бір кірісі бар триггер есептегіш кірісті немесе есептегіш триггерлер деп аталады.

JK түріндегі триггер (J) орнату кірістері және RS триггерінің кірістеріне ұқсас (К) лақтыру кірістері бар универсалды триггерлер болып келеді. Соңғылардың айырмашылығы бірден екі кіріске (J = К = 1) сигналдарды беру мүмкіндігіне ие болып табылады. Бұл режимде үшінші (тактілі) кіріске қатысты есептегіш триггер ретінде жұмыс істейді.

Аралас триггерлерде бірнеше режим қатар жұмыс жасайды. Мысалы, RST түріндегі есептегіш триггері, сондай-ақ оның орнату және лақтыру кірістері де бар .

Мысал ретінде, күрделі кірісті логикалы триггер ретінде J1J2J3 және К1К2К3, топтық кірістері коньюкциялық операциямен қосылған JK-триггерін алуға болады:

![]() .

.

Триггерлер ақпаратты жазу тәсіліне байланысты асинхрондық (тактілік емес) және синхрондық (тактілік) болып екіге бөлінедіі. Тактілік емес асинхрондық триггерлерде жаңа күйге өту кіріс ақпараттық сигналдарының тікелей өзгеруі арқылы шақырылады. Арнайы кірісі С (Clock сөзінен шыққан) бар, тактіленетіндерде осы кіріске тактілік сигналдарды беру арқылы өту жүреді. Тактілік сигналдар, сондай-ақ синхрондалған, орындалған, командалық және т.б деп аталады.

Тактілік сигналдарды қабылдау тәсіліне қарай - деңгеймен басқарылатын және фронтпен басқарылатын болып бөлінеді. Деңгеймен басқарылу деген, тактілік сигналдың бір деңгейінде триггер кіріс сигналдарын қабылдайды және оларға ықпал етеді, басқасында қабылдамайды және өзгермейтін күйде қалады.

Фронтпен басқарған кезде ауысуға тактілік сигналдың түсу мезетінде (оның фронтында немесе түсуінде) рұқсат етіледі.

Фронтпен басқарылатын триггерлерді, сондай-ақ динамикалық басқарулы триггерлер деп те атайды. Динамикалық кіріс тура немесе инверсілік болуы мүмкін. Тура динамикалық басқару тактілік сигнал нөлдік мәнінен бірлікке ауысуына рұқсат беруді көрсетсе, инверстілік- тактілік сигналдың бірлік мәнінен нөлдік мәнге өзгеруінде қайта қосуға рұқсат береді.

7.1.2 Триггерлердің сызбатехникасы.

Бір жағынан RS мен D триггерлері мен екінші жағынан Т, JK триггерлерінің арасында айтарлықтай айырмашылық бар. RS, D-триггерлер ажыратылған құрылымды болып келсе, ал Т, JK-триггерлері кері байланысты тұйықталған құрылымды, яғни шығыс сигналдарын өздерінің кірістеріне әсер ету үшін қолданады.

D-триггер RS триггерінен алынады, егер S кірісіне D мәнін берсе, ал R кірісіне оның инверсиясын аламыз (7.5,а суретті қара). Ақпараттық сигнал тек С синхроимпульсті мезетінде есте сақталады (7.5,б суретті қара).

7.5 сурет – D-триггер сызбасы (а) және уақыттық диаграмма (б)

Т-триггер RS триггері негізінде құрылады (7.6,а суретті қара). Бұл жағдайда есептегіш кіріс ролін С тактілеу кірісі атқарады.

7.6 сурет – Т-триггер сызбасы

Тактілеу кірісі бойынша ақпаратты қабылдаудың әрбір рұқсат етілуінде СТ – триггер кері байланыстар бойынша қарама-қарсы күйді қабылдайды, яғни қайта қосылады. Т-триггерін осыған ұқсас әдіспен D-триггерінің негізінде де алуға болады (7.6,б суретті қара).

Есептегіш Т-триггердің жұмыс қабілеттілігі қарастырылған құрылымда мөлдір емес триггерді (екісатылы немесе динамикалық басқарымды) немесе ішкі кешігулердің қолданылуымен қамтамасыз етіледі.

JK-триггер сызбасы (7.7 суретті қара) 7.1 кестесіне тәуелді.

7.7 сурет – JK-триггер сызбасы

7.1 кесте – JK-триггер ақиқаттылығының кестесі

|

J |

K |

Qн |

|

0 |

0 |

Q |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

|

Генерация режимін болдырмау үшін, есептегіш Т-триггерлері үшін де, бұл жерде екісатылық типті және динамикалық басқарымды RS-триггерін қолдану қажет.

7.2 Регистрлер

7.2.1 Регистрлерді кластарға бөлу.

Регистрлер көптеген байланысқан сөз құрайтын айнымалылармен жұмыс істейді. Сөздермен бірнеше операция: қабылдау, беру, сақтау, разрядтық торға ығысу, разрядты логикалық операциялар орындалады.

Регистрлер триггерлер мен логикалық элементтері бар разрядтық сызбалардан тұрады.

Айнымалыларды жеткізу сызықтарының санына байланысты регистрлер бір фазалы және жұпфазалы, синхрондау жүйесіне байланысты біртактілік, екітактілік және көптактілік болып бөлінеді.

Бірақ ең басты жіктеу белгісі мәліметтерді қабылдау және беру әдісі болып табылады.

Осы белгісіне байланысты регистрлер параллель (статикалық), тізбекті (жылжымалы) және параллель-тізбекті болып бөлінеді.

Параллель регистрлерде сөзді қабылдау және жіберу барлық разрядтар бойынша біруақытта жүреді. Оларда разрядтық логикалық түрлендіруге ұшыраған сөздер сақталуы мүмкін.

Тізбектік регистрлерде сөз разрядтан разрядқа қабылданады және бөлінеді. Оларды ығыстырушы деп атайды, себебі сөздерді кірістіргенде және шығарғанда тактілейтін сигналдар оларды разрядтық тор бойынша жылжытады. Жылжытушы регистр екі бағытты емес (бірбағытты ығысумен) немесе (екі бағытты ығысу мүмкіндігімен) екі бағытты болуы мүмкін.

Тізбектік-параллель регистрлер біруақытта тізбекті және параллельді түрлі кіріс шығыстары болуы мүмкін. Тізбекті кірісі және параллель шығысы бар (SIPO, Serial Input - Parallel Output), параллель кірісі және тізбекті шығысы бар (PISO) варианттары болуы мүмкін.

Параллель (статикалық) регистрлерде разрядтар сызбалары мәліметтермен өзара алмаспайды. Разрядтар үшін жалпы болып тактілеу тізбектері, ауытқу/қою, шығыс және қабылдау ажыратулары, яғни басқару тізбектері табылады.

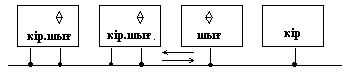

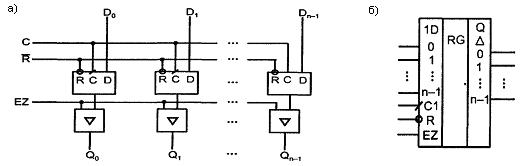

Тура динамикалық кірістерімен Д-триггерлерде қарастырылған, R ауытқу шығыстары және EZ сигналдарымен басқарылатын үшінші күйлі шығыстары болатын статикалық регистр сызбалары 7.8 суретте көрсетілген.

Қазіргі схема техникасы үшін регистрлерді Д-триггерлерде қарастырған сипатты болып отыр. Көптерінен үшінші күйлі шығыстары бар, кейбір регистрлер буферліктер қатарына жатады, яғни үлкен сыйымдылықты немесе төменомдық активті жүктемелермен жұмыс істеуге есептелген. Бұл олардың тікелей магистралда жұмыс жасауын қамтамасыз етеді (қосымша интерфейс схемаларынсыз).

7.8 сурет – Статикалық регистр сызбасы (а) және оның шартты белгіленуі (б)

7.2.2 Ығыстырушы регистрлер.

Тізбектік (ығыстырғыш) регистрлер тасымалдау тізбектерімен байланысқан разрядтық сызбалар тізбегі болып келеді.

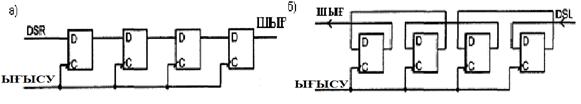

Бір разрядқа оңға ығысулы біртактілі регисторда (7.9, а суретті қара) сөз синхросигнал түскен кезде ығысады. Кіріс және шығыс тізбекті (DSR- Data Serial Right). 7.9,б суретте солға қарай ығысулы регистр сызбасы көрсетілген (DSL - Data Serial Left кіріс мәндері).

7.9 сурет – Регистрдің оңға (а) және солға (б) ығысу сызбалары

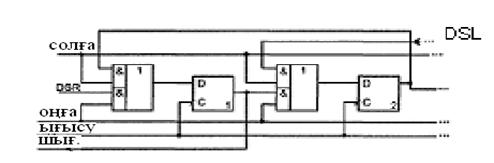

7.10 суретте реверсирленген регистрдің құрылу сызбасы келтірілген, оларда екі көрші разрядтармен триггерлер байланыстары бар, бірақ сәйкес сигналдармен жұмыс жасауға осы байланыстардың тек біреуімен ғана рұқсат етіледі.

7.10 сурет – Реверсивті регистр сызбасы

8 Дәріс. Екілік есептегіштер

Есептегіштерге кіріс импульстары әсерінен бір күйден екінші күйге көшкенде оларға түсетін импульстарда сол немесе басқа кодта тіркейтін автоматтарды жатқызады. Негізгі операциясы есептегіш құрамын бірге өзгерту болып табылады. Мұндай бірлікті қосу – инкрементация (INR) операциясына, ал алу - декрементация ( DCR) азайту операциясына сәйкес келеді.

Есептегіштер М есептеу модулімен сипатталады, олар мүмкін күйлер санын анықтайды. Есептегішке М кіріс сигналдары түскеннен кейін алдыңғыны қайталайтын жаңа цикл басталады.

8.1 Есептегіштерді кластарға бөлу

Ішкі күйлерін кодтау тәсілдеріне қарай екілік есептеуіштер , Джонсон есептеуіштері, «N-нан 1» коды бар есептеуіштерді және басқаларды айтамыз.

Есептеу бағытына қарай есептегіштер: қосушы (тура есептеу), азайтушы (кері есептеу) және реверсивті (есептеу бағытын өзгерту) болып бөлінеді.

Автоматтардың сол және басқа кластарға жатқызуларына байланысты синхрондық және асинхрондық есептегіштер туралы айтылады.

Есептегіштер разрядаралық байланыстары бар разрядтық сызбалардан құрылады.

Сәйкесінше осы байланыстардың құрылуына қарай оларды тізбекті, параллель және аралас тасымалдаулары бар есептегіштер деп бөледі.

Есептегіш жұмысының мүмкін режимдері.

- Есептегішке келіп түскен сигналдар санын тіркеу.

- Жиіліктерді бөлу.

Бірінші режимдегі нәтиже – шығыс сигналдарының екінші режимдегі есептегіштегі құрамы есептегіш импульстарының толып кетуі болып табылады.

Есептегіштің тез әсерлігі ондағы жаңа күйдің орнау уақытымен (бірінші режимі), сондай-ақ кіріс сигналдарының максимал жиілігімен fmax сипатталады. Кез-келген автомат сияқты, есептегішті кез-келген типті триггерлерде құрастыруға болады, бірақ бұл үшін Т- типті (есептегіш) және J = К = 1 болғанда есептеу режимінде болатын JK типті триггерлерді пайдаланған ыңғайлы.

Есептегіш күйі разрядты сызбалардың шығыстары бойынша Qn-1Qn-2…Qo, сөзі сияқты кіріс сигналдары есептегіштің кіші разрядына келіп түседі.

8.2 Екілік есептегіштер

8.2.1 тізбекті және параллельді есептегіштер

Екілік есептегіш М = 2n модуліне ие болатын есептегіш, мұндағы n – бүтін сан. Есептегіш триггер кіріс импульстарының жиілігін екіге бөледі. Сондықтан есептегіш тізбектей жалғанған есептегіш триггерлердің тізбегі түрінде құрылуы мүмкін (8.1,а суретті қара). Есептегішті Т-триггерлер тізбегі ретінде көрсету қосу, сол сияқты азайту варианттары үшін де дұрыс, себебі разрядтарды ауыстыру жиілігіне қатысты заңдылық кестені жоғарыдан төмен (тура есеп), сол сияқты төменнен жоғары (кері есеп) қараған кезде де сақталады.

Бұл кездегі айырмашылық келесі ауыстыруды шақыратын алдыңғы разрядты ауыстыру бағытында болып отыр. Тура есептеу кезінде келесі разряд алдыңғы 1-0 бағытта өткенде, ал кері болғанда 0-1 бағытта өткенде қайта қосылады.

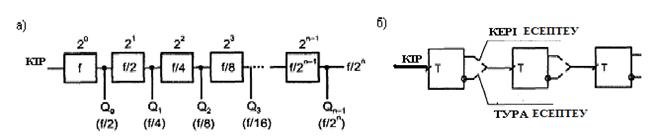

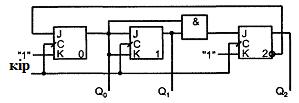

8.1 сурет – Тізбекті есептегіш құрылымы (а) және оның тура динамикалық басқару триггерлердегі іске асуы (б)

Сонымен варианттар арасындағы айырмашылық триггерлер кірістерін алдыңғылардың шығыстарына әртүрлі қосуда болып отыр. Егер тура динамикалық басқарулы есептегіш триггерлерде тұрғызылса, онда қосылу сипаты келесі триггерлердің алдыңғыға қосылу сипаты тура және кері есептеу есептегіштерін алу үшін 8.1,б суреттегі сызбаға сәйкес келуі керек.

Тура және кері есептеу варианттарының айырмашылығынан реверсивті есептегішті құру тәсілі шығады, басқарушы сигнал әсерінен сигналды алу нүктесін триггерден қарама-қарсы шығысқа және-немесе-не , және-немесе суретте көрсетілген элементі арқылы көшіру.

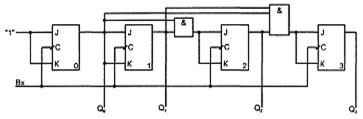

Максималды тез әрекетке паралельді тасымалдауышы бар синхронды есептегіштер ие. Фронтпен басқарумен триггерлерде ұйымдастырылған параллельді тасымалдауышы бар соммалық синхронды есептегіштің құрылымы (8.3 суретті қара).

8.3 сурет – Тура есептеу параллель есептегішінің сызбасы

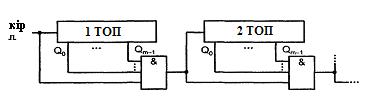

8.2.2 Топты құрылымдық есептегіштер.

Үлкен разрядты параллель есептегіштерді құрастыруға шектеулерге байланысты топты құрылымдық есептегіштер кең өріс алып отыр, онда есептегіш топаралық тасымал тізбектерімен байланысқан топтарға бөлінеді (8.4 суретті қара).

8.4 сурет – Топты құрылымдық есептегіш сызбасы

Топтың барлық триггерлерінің бірлік бұл жағдай кіріс сигналын келесі топқа тура жіберуге топаралық коньюктор даярлайды.

Егер топ разрядтылығын кемітіп және синхронды Т-тиггерлерін пайдаланса, онда тізбекті тасымалды синхронды есептегіш сызбасы алынады (8.5 суретті қара).

8.5 сурет – Тізбекті тасымалды есептегіш сызбасы

Сызба синхрондықтар қатарына жатады, себебі барлық триггерлер бір кіріс сигналы әсерінен біруақытта жұмыс істейді. Осы сызбаның кіріс сигналына тез реакциясы көрініс табады: ол параллель тасымалды есептегіштегі сияқты болады. Бірақ кіріс сигналдарының ең үлкен жиілігі бойынша бұл сызба параллель тасымалды сызбадан едәуір нашар болып түседі.

8.3 Кез-келген модульді екілік-кодталған есептегіштер

2 санының бүтін дәрежесіне тең емес, яғни кез-келген модульді есептегіш бірнеше әдістер негізінде іске асырылады. Осындай екілік есептегіштің 2n - М = L шығарып тастауға жататын артық жағдайлары бар.

Артық жағдайларды шығарып тастау әдістері сан алуан және кез-келген М үшін есептегіштің көптеген мүмкіндіктерін қарастыруға болады. Бірінші күйлердің небір санын шығару арқылы есептегіштің алғашқы нөлдік күйін аламыз, бұл есептің табиғи ретінің жоқтығына және есептегіште артық кодты тіркеуге әкеліп соғады. Соңғы күйлерді шығарып тастау есептеудің табиғи ретін сақтауға мүмкіндік береді.

Кез-келген модульді есептегіштерді құрудың 2 тәсілін қарастыралық: разрядаралық модификациялы байланыстар және ауытқуды басқару.

Модификациялық разрядаралық байланысты есептегіштерді құрастыру кезінде, соңғы, артық күйлер есептегіштің жұмыс істеу кестелерінен тікелей шығарылып тасталады. Осы кезде сызбаны құрғаннан кейін автоматтар синтезі үшін кәдімгі әдіспен есептегіш алынады, оның спецификасы стандартты емес функцияларда триггерлердің қозуы және сәйкесінше, триггерлердің арасындағы стандартты емес байланыста болып отыр. Осы оның атауын да түсіндіреді.

8.3.1 Есептегіштерді құрудың бірінші тәсілі.

Бірінші әдіс бойынша есептегіштерді құруды М = 5 арналған мысалмен көрсетейік, 8.1 кестеден басталық.

8.1 кесте

|

Бастапқы күйі |

Келесі күйі |

Қоздыру функциясы |

||||||

|

Q2 |

Q1 |

Q0 |

Q2 |

Q1 |

Q0 |

J2 K2 |

J1 K1 |

J0 K0 |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 X |

0 X |

1 X |

|

0 |

0 |

1 |

0 |

1 |

0 |

0 X |

1 X |

X 1 |

|

0 |

1 |

0 |

0 |

1 |

1 |

0 X |

X 0 |

1 X |

|

0 |

1 |

1 |

1 |

0 |

0 |

1 X |

X 1 |

X 1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

X 1 |

0 X |

0 X |

Триггерлердің қозу функцияларын табуда 8.2 кестенің «сөздігі» қолданылған.

8.2 кесте

|

Ауысу |

J K |

|

0→0 |

0 X |

|

0→1 |

1 X |

|

1→0 |

X 1 |

|

1→1 |

X 0 |

Ерікті Х сигналының символының орнына

кез-келген айнымалыны (0 немесе 1) қоюға болады. 8.1 кестенің

негізінде жазалық: ![]() (J2 бағанында бар болғаны бір

бірлік қалдырылған), J1 = Q0,

(J2 бағанында бар болғаны бір

бірлік қалдырылған), J1 = Q0,

![]() .

Ki (i = 0, 1, 2) функциясы үшін сигнал көздеріне азырақ

салмақ түсіру үшін тұрақты сандардың

көбірек болатын вариантын таңдалық.

К2= 1, К1 =J1 и К0

= 1 деп қабылдаймыз.

.

Ki (i = 0, 1, 2) функциясы үшін сигнал көздеріне азырақ

салмақ түсіру үшін тұрақты сандардың

көбірек болатын вариантын таңдалық.

К2= 1, К1 =J1 и К0

= 1 деп қабылдаймыз.

Есептегіш сызбасы 8.6-суретте келтірілген.

Есептегіштің жобаланған жүйесінде артық күйлер олар есептегіштің қалыпты жұмысында пайдаланылмайтындықтан алынып тасталған. Бірақ бұзылуларда немесе сызбаға қоректену кернеуінің берілуінен кейін оның жұмысының басында артық күйлер орын алуы мүмкін.

8.6 сурет – Модулі 5 болатын есептегіш сызбасы

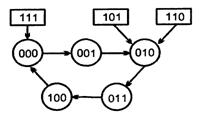

Әрбір артық күйді алып, олардың келесі күйлерге өтуін анықтайтын триггерлердің қозу күйін анықтаймыз. Қажет болған жағдайда дәл осы әдіспен келесі ауысымды да және т.б анықтаймыз. Алынған мысал үшін артық болып 101, 110 және 111 күйлері табылады.

101 жағдайында Q2 = 1, Q1 = 0 және Q0 = 1. Триггерлердің қозу фунциясын біле отырып, J0 = 0, К0 = 1, J1 = K1 = 1, J2 = 0, К2 = 1 екендігін анықтаймыз. Демек, 0 және 2 триггерлері лақтырылады, ал триггер 1 ағымдағы күйге қарама-қарсыға қайта қосылады және 101 артық күйінен есептегіш 010 күйіне өтеді. Ұқсас әдіспен 100 және 111 күйлеріне нәтижелер алуға болады. Нәтижесінде есептегіштің күй диаграммасын тұрғызуға болады (ауысымдар графигі), мұнда тек жұмыс циклі (күйлер - айналмалар) ғана емес, қолданылмайтын күйге түскен (тікбұрыштар) автоматтар мінезі есепке алынған. Мұндай диаграмма 8.7 суретте көрсетілген.

8.7 сурет – Модулі 5 болатын есептегіштің күй диаграммасы

Диаграммадан қарастырылған есептегіштің өздігінен қосылу қасиеті бар екендігін көре аламыз – бастапқы жағдайына тәуелсіз ол жұмыс цикліне жұмыс басталғаннан кейін келеді.

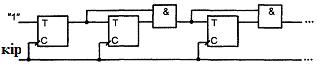

8.3.2 Есептегішті құрудың екінші тәсілі.

Кез-келген модульді есептегішті құрудың екінші әдісі – лақтыруды басқару әдісі - есеп модулін есептегіштің сызбасын өзгертуді қажет етпейтін өте қарапайым әдіспен модуль есебін өзгертуге мүмкіндік береді.

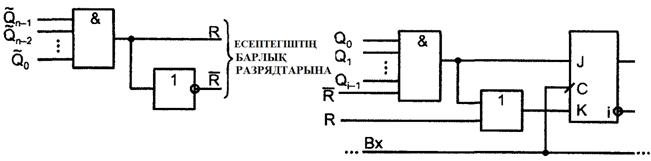

Параллельді ауыстыруы бар синхронды есептегішті енгізуде қолдануға байланысты әдісті қарастырайық (8.3 суретті қара). Аталған типті екілік есептегіштің қозу функциясы, біз білетіндей, мына түрге Jj = Kj = Q0Q1…Qi-1 (J0 = K0 = 1 кіші триггерде) келтірілген. Бұл функцияларға оларды келесідей өзгертіп, лақтыру сигналы R енгізейік:

![]() ,

,

Кi = Ji v R.

8.8 сурет – Лақтыруды басқаруы бар есептегіштің сызбасы

Сигнал болмағанға дейін (R = 0), Jj и Kj функцияларының сәйкес екілік есептегіш функцияларынан айырмашылығы болмайды. R сигналы бірлік мәніне ие болғанда, Ji барлық функциялары нольдік, Kj – бірлік болады, бұл барлық келесі такті келгенде лақтырылуына мәжбүрлейді.

Егер R есептегіште М-1 санының пайда болуы салдарынан орын алса, онда есептің 0, 1, 2,..., М-1, 0... кезегі, яғни М модульді есептегіш жүзеге асырылады.

Лақтыруды басқаруы бар есептегіштердің барлық разрядтарының сызбасы есеп модуліне тәуелді болмайды. Разрядты сызбалардан басқа, М-1 есептегіш мәніне жеткенде лақтыру сигналын қамтамасыз ететін бір коньюктор болады (8.8 суретті қара).

9 Дәріс. Есте сақтау құрылғылары

9.1 Есте сақтау құрылғыларының классификациясы

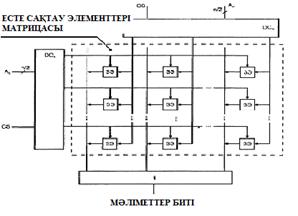

Есте сақтау құрылғыларын классификациялаудың маңызды белгісі мәліметтерге рұқсат алу әдісі болып табылады.

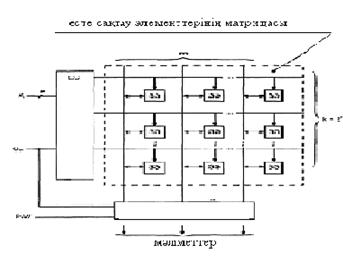

Мекен-жайлық рұқсат кезінде мекен-жайлық кірістегі код алмасу жүретін торшаны көрсетеді. Мекен-жайлық жадының барлық ұяшықтарына айналу мезетінде бірдей қол жетерлік болады.

Мекен-жайлық есте сақтау құрылғылары RAM (Random Access Memory) және ROM (Read-Only Memory) болып бөлінеді. Терминдердің орысша аударылған синонимдері RAM: ОЕСҚ (оперативті есте сақтау құрылғылары) немесе ЕТБЕСҚ (ерікті таңдауы бар есте сақтау құрылғылары). Оперативті есте сақтау құрылғылары ерікті уақыт мезетінде өзгертіле алатын, ағымдағы бағдарламаны жүзеге асыру кезінде ауыстыруға қатысатын мәліметтерді сақтайды. Оперативті есте сақтау құрылғыларының есте сақтау элементтері энергиялық тәуелсіздікке ие емес.

ROM (аударғандағы эквиваленті – ТЕСҚ, яғни тұрақты есте сақтау құрылғылары) құрылғысында мазмұны мүлдем өзгермейді, немесе өзгерсе де, бірақ өте сирек және арнайы режимде болады. Жұмыс режимі үшін бұл «оқуға ғана арналған жады».

RAM статикалық және динамикалық болып бөлінеді. Бірінші нұсқа бойынша есте сақтау элементі болып триггерлер табылады, олар өз қалпын сызба қорек алып тұрғанда және жаңа жазбалар болмаған жағдайда сақтап тұрады. Екінші нұсқада мәліметтер МОП-құрылымды элементтерден түзілетін конденсатор зарядтарының түрінде сақталады. Конденсаторлардың өздігінен разрядталуы мәліметтердің жойылуына әкеліп соғады, сондықтан олар периодты түрде (әрбір бірнеше миллисекунд сайын) регенерациялануы тиіс. Динамикалық есте сақтау құрылғыларында мәліметтердің регенерациялануы (қалпына келуі) арнайы контроллердің көмегімен жүзеге асырылады.

Статикалық есте сақтау құрылғылары – SRAM (Static RAM), ал динамикалық – DRAM (Dynamic RAM) деп аталады.

Динамикалық есте сақтау құрылғылары көбірек ақпараттық сыйымдылықпен және бағасының жоғары болмауымен сипатталады, осы себепті оларды ЭЕМ негізгі жады ретінде пайдаланады.

Flash типіндегі жады есте сақтау элементі бойынша EEPROM (немесе басқаша E2PROM) типіндегі жадыға ұқсас, бірақ өзін бөлек түрге бөлуге мүмкіндік беретін құрылымдық және технологиялық ерекшеліктері бар.

Тізбекті ену есте сақтау құрылғыларында жазылатын мәліметтер белгілі бір кезекті түзеді. Санау сөзбе сөз жазылу кезегімен немесе кері кезекпен жүзеге асырылады. Бұндай есте сақтау элементтерінің моделі болып мәліметтер көршілес элементтердің арасында алмасатын есте сақтау элементінің кезекті тізбегі болып табылады.

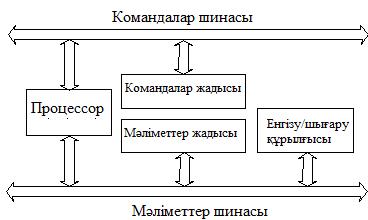

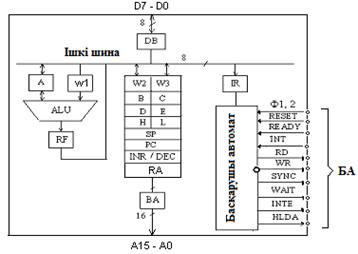

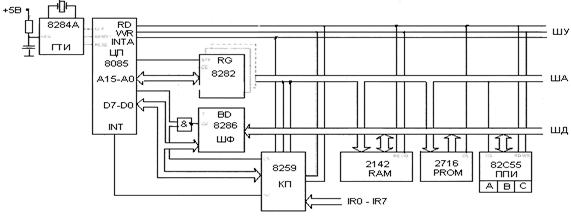

Тура санау реті «бірінші келді –бірінші кетті» тәртібімен жүретін FIFO буферлерінде (First In - First Out), сонымен қатар файлды және циклдық есте сақтау құрылғыларында орын алады.