Некоммерческое акционерное общество

АЛМАТИНСКИЙ УНИВЕРСИТЕТ ЭНЕРГЕТИКИ И СВЯЗИ

Кафедра «Электроника»

СХЕМОТЕХНИКА

КОНСПЕКТ ЛЕКЦИЙ

для студентов специальности

5В070400 – Вычислительная техника и программное обеспечение

Алматы 2011

СОСТАВИТЕЛИ: Б.С. Байкенов, А.Т. Ибраев. Схемотехника. Конспект лекций по дисциплине «Схемотехника» для студентов специальности 5В070400 –. Вычислительная техника и программное обеспечение – Алматы: АУЭС, 2011. – 101 с.

В конспекте лекций рассмотрены основы цифровой электроники и микропроцессорной техники – динамично развивающейся области науки и техники, играющей особую роль в современном мире. Изложение материала построено так и в таком объеме, чтобы подготовить студента к систематическому и самостоятельному изучению современных систем моделирования и проектирования. Лекционный материал состоит из двух разделов: цифровой схемотехники и микропроцессорных БИС.

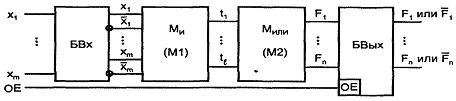

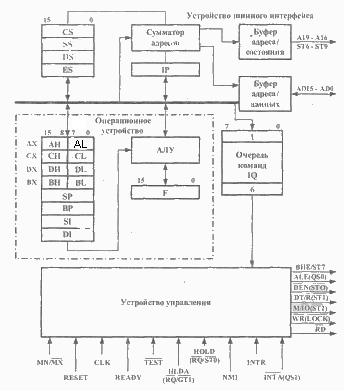

В первом разделе рассмотрены цифровые устройства комбинационного и последовательностного типов, запоминающие устройства и программируемые логические матрицы. Второй раздел посвящен анализу структуры микропроцессора i8085/8086, командам, а также адаптерам и контроллерам микропроцессорной системы.

Конспект лекций составлен в целях закрепления основ построения цифровых устройств и микропроцессорных систем, и предназначена для студентов специальности 5В070400 – Вычислительная техника и программное обеспечение.

Ил. 84, табл. 24, библиогр. – 6 назв.

Рецензент: д-р. техн. наук, проф. Ш.А. Бахтаев

Печатается по плану издания Некоммерческого акционерного общества «Алматинский университет энергетики и связи» на 2011 г.

© НАО «Алматинский университет энергетики и связи», 2011 г.

Введение

Быстрорастущие потребности современного общества требуют широкомасштабного, тотального использования новейших технологий в различных отраслях экономики, так называемого Hi-Tec (High Technogy).

Крупнейший специалист в области информатики, академик Е.П.Велихов в одной из своих статей высказал гениальную по своей простоте мысль: «Тот, кто умеет делать компьютеры, владеет миром».

Все разнообразные средства цифровой техники: персональные компьютеры, микропроцессорные системы измерений и автоматизация технологических процессов, цифровая связь, телевидение, бытовая техника и т.д. строятся на единой элементной базе, в состав которой входят чрезвычайно разные по сложности микросхемы – от логических элементов, выполняющих простейшие операции, до сложнейших программируемых кристаллов, содержащих миллионы логических элементов.

С появлением микропроцессоров и СБИС с программируемой структурой произошло качественное изменение подхода к методам проектирования и изготовления средств автоматики.

Микропроцессор – это процессор, реализованный в виде одной или нескольких больших интегральных схем (БИС), обладающих функциональной завершенностью.

Микропроцессор способен выполнять команды, входящие в его систему команд. Меняя последовательность команд (программу), можно решать различные задачи на одном и том же микропроцессоре. Иначе говоря, в этом случае задачи структура аппаратных средств не связана с характером решаемой задачи. Это обеспечивает микропроцессорам массовое производство с соответствующим снижением стоимости.

Микропроцессорный комплект – набор БИС, в котором имеется возможность управления работой с помощью определенного набора команд.

Микропроцессорная система по своей структуре схожа с персональным компьютером, но имеет усеченный объем памяти и ограниченный набор средств сопряжения с внешним миром. В основе построения микропроцессорных систем лежит программно-аппаратный принцип. Меняя программу, одну и ту же стандартную микропроцессорную систему можно использовать во многих устройствах и системах: автоматического управления технологическим процессом, системах технической диагностики и контроля состояния объекта, включая охранные системы.

Основное отличие СБИС с программируемой структурой состоит в том, что системотехник может изменять структуру микросхемы, программно соединяя различные блоки.

Но прежде чем перейти изучению микропроцессоров и СБИС с программируемой структурой, необходимо ознакомиться с наиболее важными цифровыми элементами и устройствами, из которых собственно и состоит микропроцессор и его периферийные устройства.

1 Лекция. Логические элементы цифровых устройств

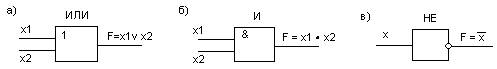

Преобразование цифровой информации сводится к простейшим операциям над логическими переменными 0 и 1, которые реализуются логическими элементами И, ИЛИ и НЕ. Условное обозначение логического элемента - прямоугольник, в котором ставится символ выполняемой операции, (операция инверсии изображается в виде кружка).

Рисунок 1.1 – Условные обозначения логических элементов

В схемах логические переменные 0 и 1 отображаются двумя различными уровнями напряжения: Uo и U1. Необходимо условиться, какой из двух уровней напряжения принять за Uo и какой за U1. Существуют понятие положительной и отрицательной логики. В положительной логике U1 > Uo, а в отрицательной U1 < Uо. В дальнейшем, если не оговорено иное, будем пользоваться положительной логикой.

Одни и те же преобразования логических переменных можно задать в различных формах: с помощью операций И, ИЛИ, НЕ (булевский базис), операции И-НЕ (базис Шеффера), операции ИЛИ-НЕ (базис Пирса), а также многими другими способами. Чаще всего встречаются базисы Шеффера и Пирса.

1.1 Статические параметры логических элементов

К статическим параметрам, задающим границы отображения переменных (0 и 1) на входе и выходе логического элемента (ЛЭ), относятся значения напряжений:

- по входу Uвx1min и Uвх0mах.;

- по выходу Uвых1min и Uвых0max

и токов:

- по входу Iвх1max и Iвх0mах;

- по выходу Iвых1mах и Iвых0mах.

Для нормальной работы элемента требуется, чтобы напряжение, отображающее логическую 1, было достаточно высоким, а напряжение, отображающее 0, - достаточно низким. Эти требования задаются параметрами Uвx1min и Uвх0mах. Входные напряжения данного элемента есть выходные напряжения предыдущего (источника сигналов). Уровни, гарантируемые на выходе элемента при соблюдении допустимых нагрузочных условий, задаются параметрами Uвых1min и Uвых0max. При высоком уровне выходного напряжения из элемента-источника ток вытекает, цепи нагрузки ток поглощают. При низком уровне выходного напряжения элемента-источника ток нагрузки втекает в этот

элемент, а из входных цепей элементов-приемников токи вытекают. Зная токи Iвых1mах и Iвых0mах, характеризующие возможности элемента-источника сигнала, и токи Iвх1max и Iвх0mах, потребляемые элементами-приемниками, можно контролировать соблюдение нагрузочных ограничений, обязательное для всех элементов схемы.

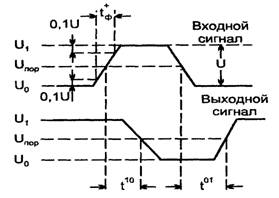

Быстродействие логических элементов определяется скоростями их перехода из одного состояния в другое. На рисунке 1.2 показана временная диаграмма работы логического элемента НЕ. Моментом изменения логического сигнала считают момент достижения им порогового уровня Uпор, за который принимают середину логического перепада сигнала, т. е. 0,5(Uо + U1).

Рисунок 1.2 - Временная диаграмма работы логического элемента НЕ

На быстродействие ЦУ влияют также емкости, на перезаряд которых требуются затраты времени. В справочных данных приводятся входные и выходные емкости логических элементов, знание которых позволяет подсчитать емкости нагрузки в узлах схемы. Предельно допустимая емкость указывает границу, которую нельзя нарушать, поскольку при этом работоспособность элемента не гарантируется.

1.2 Типы выходов ЦЭ

Цифровые элементы (логические, запоминающие, буферные) могут иметь следующие типы выходов:

- логические;

- с открытым коллектором (стоком);

- с третьим состоянием;

- с открытым эмиттером (истоком).

1.2.1 Логический выход.

Логический выход формирует два уровня выходного напряжения (Uо и U1). Выходное сопротивление логического выхода стремятся сделать малым, способным развивать большие токи для перезаряда емкостных нагрузок и, следовательно, получения высокого быстродействия. Такой тип выхода используют в комбинационных схемах (дешифраторах, мультиплексорах, сумматорах, АЛУ и т.д).

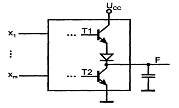

Схемы логических выходов элементов ТТЛ и КМОП подобны двухтактным каскадам - в них оба фронта выходного напряжения формируются с участием активных транзисторов, работающих противофазно, что обеспечивает малые выходные сопротивления при любом направлении переключения выхода (см. рисунок 1.3).

Рисунок 1.3 - Схема выходной цепи цифрового элемента

Особенность таких выходов состоит в том, что их нельзя соединять параллельно. Во-первых, это создает неопределенность, т. к. в точке соединения выхода, формирующего логическую 1, и выхода, формирующего логический 0, не будет нормального результата. Во-вторых, вследствие малых величин выходных сопротивлений уравнительный ток при этом может достигать достаточно большой величины, что может вывести из строя электрические элементы выходной цепи.

1.2.2 Элементы с тремя состояниями выхода.

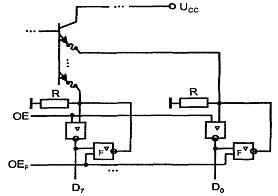

Элементы с тремя состояниями выхода (типа ТС) кроме логических состояний 0 и 1 имеют состояние "отключено", в котором ток выходной цепи пренебрежимо мал. В это состояние (третье) элемент переводится специальным управляющим сигналом, обеспечивающим запертое состояние обоих транзисторов выходного каскада (Т1 и Т2 на рис.1.3) Сигнал управления элементом типа ТС обычно обозначается как ОЕ (Output Enable). При наличии разрешения (ОЕ = 1) элемент работает как обычно, выполняя свою логическую операцию, а при его отсутствии (ОЕ = 0) переходит в состояние "отключено". В ЦУ широко используются буферные элементы типа ТС для управляемой передачи сигналов по тем или иным линиям. Буферы могут быть неинвертирующими или инвертирующими, а сигналы ОЕ — Н-активными или L-активными, что ведет к наличию четырех типов буферных каскадов (см.рисунок 1 4).

Выходы типа ТС отмечаются в обозначениях элементов значком треугольника.

Выходы типа ТС можно соединять параллельно при условии, что в любой момент времени активным может быть только один из них. В этом случае отключенные выходы не мешают активному формировать сигналы в точке соединения выходов. Эта возможность позволяет применять элементы типа ТС в магистрально-модульных микропроцессорных и иных системах, где многие источники информации поочередно пользуются одной и той же линией связи.

Рисунок 1.4 - Типы буферных каскадов с третьим состоянием

1.2.3 Выход с открытым коллектором.

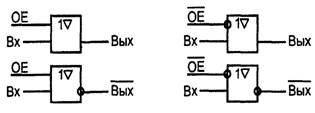

Элементы с открытым коллектором имеют выходную цепь, заканчивающуюся одиночным транзистором, коллектор которого не соединен с какими-либо цепями внутри микросхемы (см. рисунок 1.5,а). Транзистор управляется от предыдущей части схемы элемента так, что может находиться в насыщенном или запертом состоянии. Насыщенное состояние трактуется как отображение логического нуля, запертое - 1. Насыщение транзистора обеспечивает на выходе напряжение Uо (малое напряжение насыщения "коллектор-эмиттер" Uкэн). Запирание же транзистора какого-либо уровня напряжения на выходе элемента не задает, выход при этом имеет фактически неизвестный "плавающий" потенциал, т. к. не подключен к каким-либо цепям схемы элемента. Поэтому для формирования высокого уровня напряжения при запирании транзистора на выходе элементов с открытым коллектором (типа ОК) требуется подключать внешние резисторы (или другие нагрузки), соединенные с источником питания.

Несколько выходов типа ОК можно соединять параллельно, подключая их к общей для всех выходов цепочке Ucc - R (см. рисунок 1.5, б). При этом можно получить режим поочередной работы элементов на общую линию, как и для элементов типа ТС, если активным будет лишь один элемент, а выходы всех остальных окажутся запертыми. Если же разрешить активную работу элементов, выходы которых соединены, то можно получить дополнительную логическую операцию, называемую операцией монтажной логики.

Рисунок 1.5 - Схема выходной цепи ЦЭ с открытым коллектором (а) и реализации операции И (б)

При реализации монтажной логики высокое напряжение на общем выходе возникает только при запирании всех транзисторов, т. к. насыщение хотя бы одного из них снижает выходное напряжение до уровня Uo = Uкэн. To есть для получения логической единицы на выходе требуется единичное состояние всех выходов: выполняется операция И. Поскольку каждый элемент выполняет операцию Шеффера над своими входными переменными, общий результат окажется следующим

![]() .

.

В обозначениях элементов с ОК после символа функции ставится ромб с черточкой снизу.

При использовании элементов с ОК в магистрально-модульных структурах требуется разрешать или запрещать работу того или иного элемента. Для элементов типа ТС это делалось с помощью специального сигнала ОЕ. Для элементов типа ОК в качестве входа ОЕ может быть использован один из обычных входов элемента. Если речь идет об элементе И-НЕ, то, подавая 0 на любой из входов, можно запретить работу элемента, поставив его выход в разомкнутое состояние независимо от состояния других входов. Уровень 1 на этом входе разрешит работу элемента.

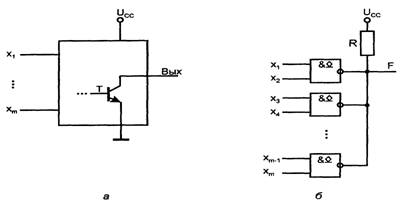

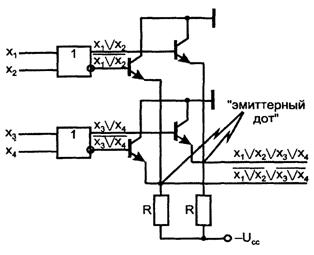

1.2.4 Выход с открытым эмиттером

Выход с открытым эмиттером характерен для элементов типа ЭСЛ (эмиттерно-связанная логика). Для работы на магистраль такие элементы не используются. Возможность соединять друг с другом выходы с открытым эмиттером при объединении эмиттерных резисторов в один общий резистор приводит к схеме (см. рисунок 1.6), иногда называемой "эмиттерный дот" и используемой при построении логических схем для получения дополнительной операции монтажной логики.

Рисунок 1.6 - Схема "эмиттерного дота"

Элементы ЭСЛ имеют противофазные выходы, на одном из которых реализуется функция ИЛИ, на другом — ИЛИ-НЕ. Соединяя прямые выходы нескольких элементов, получают расширение по ИЛИ (входные переменные соединяемых элементов образуют единую дизъюнкцию). Соединяя инверсные выходы, получают операцию И-ИЛИ относительно инверсий входных переменных, т. к. при этом

![]() .

.

Соединяя прямой выход с инверсным, можно получить функцию вида

![]() .

.

2 Лекция. ЦУ комбинационного типа

2.1 Этапы проектирования

Функциональные узлы делятся на комбинационные и последователъностные. В дальнейшем комбинационные узлы будем обозначать через КЦ (комбинационные цепи), а последовательностные через АП (автоматы с памятью). Основное различие между КЦ и АП заключаются в следующем:

- выходные величины КЦ зависят только от текущего значения входных величин (аргументов), предыстория значения не имеет.

После завершения переходных процессов в КЦ на их выходах устанавливаются выходные величины, на которые характер переходных процессов влияния не оказывает. Но в цифровых устройствах КЦ функционируют совместно с АП: во время переходных процессов на выходах КЦ появляются временные сигналы, называемые рисками. Со временем они исчезают, и выход КЦ приобретает значение, предусмотренное логической формулой, описывающей работу цепи. Однако риски могут быть восприняты элементами памяти АП, необратимое изменение состояния которых может радикально изменить работу ЦУ, несмотря на исчезновение сигналов рисков на выходе КЦ. Для исключения сбоев в работе ЦУ из-за явлений риска предусматривают запрещение восприятия сигналов КЦ элементами памяти на время переходных процессов. Прием информации с выходов КЦ разрешается только специальным сигналом синхронизации, подаваемым на элементы памяти после окончания переходных процессов в КЦ.

Таким образом, исключается воздействие ложных сигналов на элементы памяти. Соответствующие структуры называются синхронными.

Проектирование произвольной логики комбинационного типа производится по этапам.

Прежде всего, задается характер функционирования КЦ. Это может быть сделано различными способами, чаще всего пользуются таблицами истинности, задающими значение искомых функций на всех наборах аргументов. От таблицы легко перейти к СДНФ искомых функций (СДНФ - совершенная дизъюнктивная нормальная форма, т. е. дизъюнкция конъюнктивных членов одинаковой размерности). Для этого составляют логическую сумму тех наборов аргументов, на которых функция принимает единичное значение.

Например, для подлежащей воспроизведению функции трех аргументов, заданной таблице 2.1, получим СДНФ

![]() .

.

Таблица 2.1 – Таблица истинности ЦУ

|

x1 |

x2 |

x3 |

F |

x1 |

x2 |

x3 |

F |

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

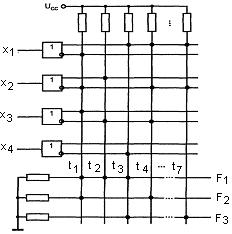

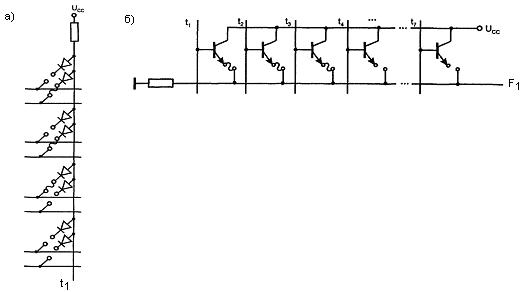

Дальнейшие действия зависят от средств реализации функций, к которым в современной схемотехнике относятся:

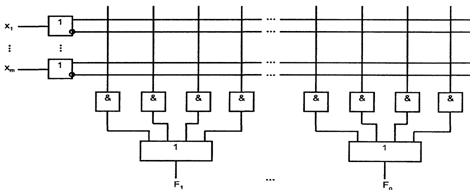

1) Логические блоки табличного типа (LUTs, Look-Up Tables).

2) Логические блоки в виде последовательности матриц элементов И и ИЛИ (PLA, Programmable Logic Array; PAL, Programmable Array Logic).

3) Универсальные логические блоки на основе мультиплексоров (УЛМ).

4) Логические блоки, собираемые из логических элементов некоторого базиса (SLC, Small Logic Cells).

1. Если КЦ будет реализована на основе логических блоков табличного типа, то СДНФ явится окончательным выражением функции, и никаких дальнейших преобразований этой формы не потребуется. Дело в том, что табличный блок представляет собою память, в которой имеется столько ячеек, сколько необходимо для хранения всех значений функций, т. е. 2m, где m - число аргументов функции. Набор аргументов является адресом той ячейки, в которой хранится значение функции на этом наборе (0 или 1). СДНФ как раз и содержит все адреса, по которым нужно хранить единичные значения функции.

Если искомая функция выражена в какой-либо сокращенной

форме, то следует перевести ее в СДНФ. Для этого конъюнктивные члены, не содержащие

переменной хj, умножаются

на равную единице дизъюнкцию ![]()

Например,

![]()

![]() .

.

2. Если данный проект реализуется на логических блоках, в виде последовательно включенных матриц элементов И и ИЛИ либо их эквивалента на другом базисе, то исходную СДНФ можно минимизировать. Логические блоки с матрицами И и ИЛИ воспроизводят системы переключательных функций и имеют параметры: число входов, выходов и термов. Целью минимизации будет сокращение числа конъюнктивных термов в данной системе функций, т. е. поиск кратчайших дизъюнктивных форм. Практически это сводится к поиску минимальных форм дизъюнктивных нормальных форм (ДНФ), о чем говорится далее, и отбору среди них вариантов с достаточно малым числом термов.

3. Логические блоки на основе мультиплексоров рассмотрены в теме 3.

4. Синтез КЦ на логических блоках типа SLC, т. е. на вентильном уровне, является традиционным (термином "вентиль" называют базовые логические ячейки, выполняющие простейшие операции, например, элементы И-НЕ с двумя-тремя входами).

В этом варианте проектирование КЦ содержит следующие этапы:

- минимизацию логических функций;

- переход к заданному логическому базису.

Минимизация - такое преобразование логических функций, которое упрощает их в смысле заданного критерия. В начале было стремление минимизировать число логических элементов в схеме, что приводит к критерию сложности схемы в виде числа букв в реализуемых выражениях. Этот критерий учитывается так называемой ценой по Квайну - суммарным числом входов всех логических элементов схемы. Для минимизации по этому критерию разработано несколько методов, в их числе как аналитические, основанные на преобразованиях математических выражений, так и графические, основанные на применении карт Карно (диаграмм Вейча), удобных в использовании, если число аргументов не больше 6.

Следующий этап проектирования - переход к заданному логическому базису от исходных выражений, которые обычно получают в булевском базисе (И, ИЛИ, НЕ). Правила такого перехода известны: они основаны на применении теоремы де-Моргана. В частности, для перехода к базису Шеффера (И-НЕ) используется соотношение

![]() ,

,

а для перехода к базису Пирса (ИЛИ-НЕ) удобно вначале получить исходную булевскую форму путем инверсии искомой функции, а затем от нее перейти к базису ИЛИ-НЕ по соотношениям

![]() .

.

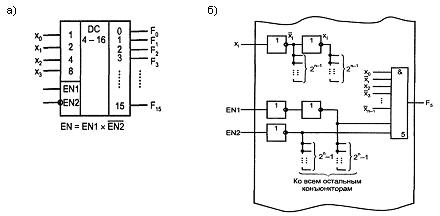

2.2 Двоичные дешифраторы

В зависимости от входного двоичного кода на выходе дешифратора возбуждается одна и только одна из выходных цепей. Двоичный дешифратор, имеющий n входов, должен иметь 2n выходов, соответствующих числу разных комбинаций в n-разрядном двоичном коде.

Рисунок 2.1 - Условное обозначение (а) и схема дешифратора (б)

В условном обозначении дешифраторов проставляются буквы DC (от англ. Decoder). Входы дешифратора принято обозначать их двоичными весами. Кроме информационных входов дешифратор обычно имеет один или более входов разрешения работы, обозначаемых как EN (Enable).

![]()

![]()

……………………..

![]()

Малоразрядность стандартных дешифраторов ставит вопрос о наращивании их разрядности. Для этого входное слово делится на поля. Разрядность поля младших разрядов соответствует числу входов имеющихся дешифраторов. Оставшееся поле старших разрядов служит для получения сигналов разрешения работы одного из дешифраторов, декодирующих поле младших разрядов.

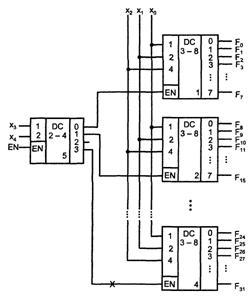

В качестве примера на рисунке 2.2 приведена схема дешифрации пятиразрядного двоичного кода с помощью дешифраторов «3-8» и «2-4».

Рисунок 2.2 - Схема наращивания размерности дешифратора

Для получения нужных 32 выходов составляется столбец из четырех дешифраторов «3-8». Дешифратор «2-4» принимает два старших разряда входного кода. Возбужденный единичный выход этого дешифратора отпирает один из дешифраторов столбца по его входу разрешения. Выбранный дешифратор столбца расшифровывает три младших разряда входного слова. Каждому входному слову соответствует возбуждение только одного выхода.

Например, при дешифрации слова х4х3х2х1х0 = 110012 = 2510 на входе дешифратора первого яруса имеется код 11, возбуждающий его выход номер три (показано крестиком), что разрешает работу DC4. На входе DC4 действует код 001, поэтому единица появится на его первом выходе, т. е на 25 выходе схемы в целом, что и требуется.

Общее разрешение или запрещение работы схемы осуществляется по входу EN дешифратора первого яруса.

2.2.1 Двоичные шифраторы.

Двоичные шифраторы выполняют операцию, обратную по отношению к операции дешифратора: при возбуждении одного из входов шифратора на его выходе формируется двоичный код номера возбужденной входной линии. Полный двоичный шифратор имеет 2n входов и n выходов.

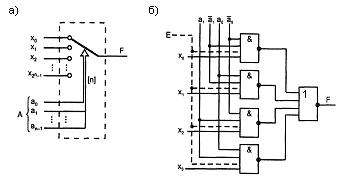

2.3 Мультиплексоры и демультиплексоры

Мультиплексоры осуществляют подключение одного из входных каналов к выходному под управлением управляющего (адресующего) слова. Разрядности каналов могут быть различными, мультиплексоры для коммутации многоразрядных слов составляются из одноразрядных.

Рисунок 2.3 – Модель мультиплексора (а) и схема мультиплексора

на элементах И-НЕ (б)

Входы мультиплексора делятся на две группы: информационные и адресующие. Работу мультиплексора можно упрощенно представить с помощью многопозиционного ключа (см. рисунок 2.3,а.). Адресующий код А задает переключателю определенное положение, соединяя с выходом F один из информационных входов хi.

При нулевом адресующем коде переключатель занимает верхнее положение хо, с увеличением кода на единицу переходит в соседнее положение х1 и т. д.

Работа мультиплексора описывается соотношением

![]() .

.

При любом значении адресующего кода все слагаемые, кроме одного, равны нулю. Ненулевое слагаемое равно хj, где i - значение текущего адресного кода.

Схемотехнически мультиплексор реализует электронную версию показанного переключателя, имея, в отличие от него, только одностороннюю передачу данных. На рисунке 2.3,б показан мультиплексор с четырьмя информационными входами, двумя адресными входами и входом разрешения работы Е. При отсутствии разрешения работы (Е = 0) выход F становится нулевым независимо от информационных и адресных сигналов.

В стандартных сериях размерность мультиплексоров не более 16x1.

Наращивание размерности мультиплексоров возможно с помощью пирамидальной структуры из нескольких мультиплексоров. При этом первый ярус схемы представляет собою столбец, содержащий столько мультиплексоров, сколько необходимо для получения нужного числа информационных входов. Все мультиплексоры столбца адресуются одним и тем же кодом, составленным из соответствующего числа младших разрядов общего адресного кода (если число информационных входов схемы равно 2n, то общее число адресных разрядов равно n, младшее поле n1 адресного кода используется для адресации мультиплексоров первого яруса). Старшие разряды адресного кода, число которых равно n – n1, используются во втором ярусе, мультиплексор которого обеспечивает поочередную работу мультиплексоров первого яруса на общий выходной канал.

Пирамидальная схема, выполняющая функции мультиплексора «32 - 1» и построенная на 5 мультиплексорах меньшей размерности, показана на рисунке 2.4 (сокращение MUX от англ. Multiplexer).

Рисунок 2.4 - Схема наращивания мультиплексоров

Демультиплексоры выполняют операцию, обратную операции мультиплексоров - передают данные из одного входного канала в один из нескольких каналов-приемников. Многоразрядные демультиплексоры составляются из нескольких одноразрядных.

3 Лекция. Универсальные логические модули

Известно, что общее число функций

n-аргументов

равно ![]() . С

ростом n число функций растет чрезвычайно быстро.

Универсальность УЛМ состоит в том, что для заданного

числа аргументов ее можно настроить на любую функцию.

. С

ростом n число функций растет чрезвычайно быстро.

Универсальность УЛМ состоит в том, что для заданного

числа аргументов ее можно настроить на любую функцию.

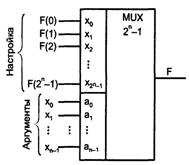

3.1 Первый способ настройки УЛМ

Первым способом настройки является фиксация некоторых

входов. Для этого способа справедливо следующее соотношение между числом

аргументов n и числом настроечных входов 2n.

Тогда число комбинаций для кода настройки, равное числу функций, есть ![]() . При этом на адресные

входы подают аргументы функции, а на информационные входы - сигналы настройки

(см. рисунок 3.1).

. При этом на адресные

входы подают аргументы функции, а на информационные входы - сигналы настройки

(см. рисунок 3.1).

Рисунок 3.1- Схема использования мультиплексора в качестве УЛМ

Таким образом, для использования мультиплексора в качестве УЛМ следует изменить назначение его входов.

Действительно, каждому набору аргументов соответствует передача на выход одного из сигналов настройки. Если этот сигнал есть значение функции на данном наборе аргументов, то задача решена. Разным функциям будут соответствовать разные коды настройки: 0 и 1.

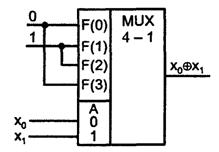

На рисунке 3.2 показан пример воспроизведения функции

неравнозначности ![]() с

помощью мультиплексора «4 - 1».

с

помощью мультиплексора «4 - 1».

Рисунок 3.2 – Схема УЛМ, реализующую функцию «исключающее ИЛИ»

Большое число настроечных входов затрудняет реализацию УЛМ.

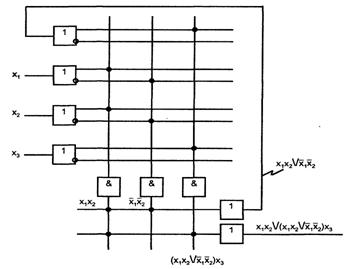

3.2 Второй способ настройки УЛМ

Уменьшение входов настройки заключается в расширении алфавита настроечных сигналов. Если от алфавита {0,1} перейти к алфавиту {0,1,xi }, где xi - литерал одного из аргументов, то число входов аргументов сократится на единицу, а число настроечных входов - вдвое. Перенос одного из аргументов в число сигналов настройки не влечет за собою каких-либо схемных изменений. На том же оборудовании будут реализованы функции с числом аргументов на единицу больше, чем при настройке константами.

Для нового алфавита код настройки находится следующим образом. Аргументы, за исключением xi, подаются на адресующие входы, что соответствует их фиксации в выражении для искомой функции, которая становится функцией единственного аргумента xi. Эту функцию, которую назовем остаточной, и нужно подавать на настроечные входы.

Если искомая функция зависит от n аргументов и в число сигналов настройки будет перенесен один из аргументов, то возникает n вариантов решения задачи, т. к. в сигналы настройки может быть перенесен любой аргумент.

В настроечные сигналы следует переводить аргумент, который имеет минимальное число вхождений в термы функции. В этом случае среди сигналов настройки увеличится число констант, что упрощает схемную реализацию УЛМ.

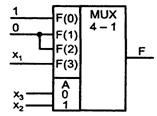

Пример воспроизведения функции трех аргументов ![]() показан на рисунке 3.3.

показан на рисунке 3.3.

Рисунок 3.3 – Пример воспроизведения функции 3-х аргументов

Минимальное число вхождений в выражение функции имеет переменная х1, которую и перенесем в число сигналов настройки. Остаточная функция определится таблице 3.1.

Таблица 3.1

|

x2 |

x3 |

Fост |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

х1 |

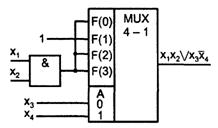

Если в сигналы настройки перевести два аргумента, то дополнительные логические схемы

будут двухвходовыми вентилями, что не усложняет УЛМ. В этом случае

мультиплексору нужно добавить блок выработки остаточных функций, в котором

формируются все функции 2-х переменных (за исключением констант 0 и 1 и

литералов самих переменных, которые не требуется вырабатывать). Пример

реализации функции 4-х аргументов ![]() при алфавите настройки {0,1,х1,х2}

показан на рисунке 3.3.

при алфавите настройки {0,1,х1,х2}

показан на рисунке 3.3.

Рисунок 3.3 – Пример воспроизведения функции 4-х аргументов

Таблица остаточной функции для этого примера приведена в таблице 3.2.

Таблица 3.2

|

X4 |

x3 |

Fост |

|

0 |

0 |

х1х2 |

|

0 |

1 |

1 |

|

1 |

0 |

х1х2 |

|

1 |

1 |

х1х2 |

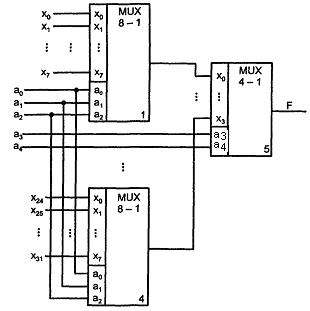

3.3 Пирамидальные структуры УЛМ

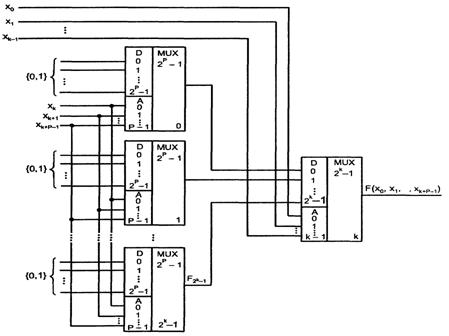

Дальнейшее расширение алфавита настройки за счет переноса трех и более переменных в сигналы настройки требует вычислений остаточных функций трех или более переменных. Вычисление таких остаточных функций с помощью мультиплексоров приводит к пирамидальной структуре (см. рисунок 3.4), в которой мультиплексоры первого яруса реализуют остаточные функции, а мультиплексор второго яруса вырабатывает искомую функцию.

При электронной настройке константами 0 и 1 схема воспроизводит функцию n аргументов, где n = k + р, причем k - число аргументов, подаваемых на мультиплексор второго яруса, р - число аргументов, от которых зависят остаточные функции, воспроизводимые мультиплексорами 0...2k - 1 первого яруса.

Для уменьшения аппаратных затрат в схеме следует стремиться к минимизации числа мультиплексоров в столбце, т. е. минимизации k и соответственно, максимальным р, поскольку их сумма k + р постоянна и равна n.

Сигналы настройки для мультиплексоров первого яруса можно искать разными способами:

1. Подстановкой (фиксацией) наборов аргументов, подаваемых на адресные входы мультиплексоров для получения остаточных функций, и далее сигналов настройки (см. таблицы 3.1 и 3.2).

2. С помощью разложения функции по Шеннону.

Разложение по одному из аргументов имеет вид

![]() .

.

Разложение функции по двум аргументам

![]() Разложение по

k

аргументам

Разложение по

k

аргументам

![]()

![]() .

.

Рисунок 3.4 – Двухъярусная схема УЛМ

Структура формул разложения полностью соответствует реализации двухъярусным УЛМ. В первом ярусе реализуются функции Fi, (i = 0,..., 2k - 1), зависящие от n - k аргументов, которые используются как настроечные для второго яруса, мультиплексор которого воспроизводит функцию k аргументов.

3. Сигналы настройки можно получить непосредственно из таблицы истинности функции.

Пусть имеется функция 4-х переменных х3х2х1х0,

и переменная х3 считается старшим разрядом вектора аргументов. Функция

задана перечислением наборов аргументов, на которых она принимает единичные

значения, причем заданы десятичные значения этих наборов: 3, 4, 5, 6, 7, 11,

15. Аналитическое значение этой функции имеет вид ![]() .

.

Значения функции сведены в таблицу 3.3.

Таблица 3.3

|

х3 |

x2 |

x1 |

x0 |

F |

|

0 0 |

0 0 |

0 0 |

0 1 |

0 0 |

|

0 0 |

0 0 |

1 1 |

0 1 |

0 1 |

|

0 0 |

1 1 |

0 0 |

0 1 |

1 1 |

|

0 0 |

1 1 |

1 1 |

0 1 |

1 1 |

|

1 1 |

0 0 |

0 0 |

0 1 |

0 0 |

|

1 1 |

0 0 |

1 1 |

0 1 |

0 1 |

|

1 1 |

1 1 |

0 0 |

0 1 |

0 0 |

|

1 1 |

1 1 |

1 1 |

0 1 |

0 1 |

При электронной настройке УЛМ константами 0 и 1 требуется мультиплексор размерности «16 - 1», на настроечные входы УЛМ подаются значения самой функции из таблицы.

При переносе хо в сигналы настройки (алфавит настройки {0,1,хо}) требуется найти остаточную функцию, аргументами которой является вектор переменных

х3х2х1. Каждая комбинация этих переменных встречается в двух смежных строках таблицы 3.3. Просматривая таблицу по смежным (выделенные в отдельные ячейки) парам строк, видно, что остаточная функция соответствует таблице 3.4.

Таблица 3.4

|

х3 |

х2 |

х1 |

Fост |

|

0 0 |

0 0 |

0 1 |

0 х0 |

|

0 0 |

1 1 |

0 1 |

1 1 |

|

1 1 |

0 0 |

0 1 |

0 х0 |

|

1 1 |

1 1 |

0 1 |

0 х0 |

Для реализации этого варианта УЛМ достаточен мультиплексор "8-1", но для перестройки на другую функцию потребуется не только смена кода настройки, но и коммутация входов настройки для подачи литералов переменной на другие настроечные входы.

При переносе в сигналы настройки двух переменных (хо и х1) для поиска остаточных функций следует просмотреть четверки смежных строк таблицы 3.4 с неизменными наборами х2х3 - аргументами, подаваемыми на адресные входы УЛМ. Этот просмотр приводит к таблице 3.5.

Таблица 3.5

|

х3 |

х2 |

Fост |

|

0 |

0 |

х1хо |

|

0 |

1 |

1 |

|

1 |

0 |

х1хо |

|

1 |

1 |

х1хо |

Из таблицы 3.5 видно, что для воспроизведения функции достаточно использовать мультиплексор «4 - 1» с дополнительным конъюнктором для получения произведения xlxо. Но при перестройке на другую функцию потребуются и другие функции двух переменных, т. е. универсальный логический модуль должен включать в свой состав дополнительный логический блок.

Логические блоки на мультиплексорах используются в современных СБИС программируемой логики, выпускаемых ведущими мировыми фирмами. Модули относятся к настраиваемым и характеризуются порождающей функцией, реализуемой модулем, когда все его входы используются как информационные (т. е. для подачи на них аргументов). Эта функция при введении настройки, когда часть входов занята под настроечные сигналы, порождает некоторый список подфункций, зависящих от меньшего числа аргументов в сравнении с порождающей функцией. Создается перечень практически важных подфункций для того или иного настраиваемого модуля.

4 Лекция. Компараторы и схемы контроля

4.1 Компараторы

Компараторы (устройства сравнения) определяют отношения между двумя словами. Основными отношениями, через которые можно выразить остальные, можно считать два - "равно" и "больше".

Компараторы принимают значение 1, если соблюдается условие, указанное в индексе обозначения функции. Например, функция FA = B = 1, если А = В и принимает нулевое значение при А ≠ В.

Приняв в качестве основных отношения "равно" и "больше", для остальных можно записать:

![]()

В сериях цифровых элементов обычно имеются компараторы с тремя выходами: "равно", "больше" и "меньше" (см. рисунок 4.1). Для краткости записей в индексе выходных функций указывается только слово А.

Рисунок 4.1 – Условное обозначение компаратора с тремя выходами

Устройства сравнения на равенство строятся на основе поразрядных операций над одноименными разрядами обоих слов. Слова равны, если равны все одноименные их разряды, т. е. если в обоих нули или единицы. Признак равенства разрядов

![]() .

.

Признак равенства слов

![]()

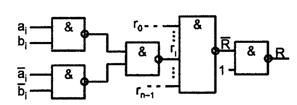

Схема компаратора на равенство в базисе И-НЕ показана на рисунке 4.2.

Рисунок 4.2 – Схема компаратора на равенство

Построение компаратора на "больше" для одноразрядных

слов (см. таблицу 4.1) требует реализации функции ![]() .

.

Таблица 4.1

|

a |

b |

FA>B |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Для общего случая n-разрядных слов имеем

![]() .

.

4.2 Схемы контроля

Задачи выявления ошибок решаются разными методами. Добавление функций контроля всегда связано с избыточностью - платой за новые возможности будут дополнительные аппаратные или временные затраты.

4.2.1 Мажоритарные элементы.

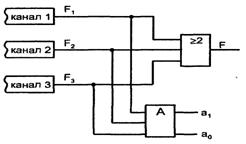

Задача мажоритарного элемента - произвести "голосование" и передать на выход величину, соответствующую большинству из входных. Ясно, что мажоритарный элемент может иметь только нечетное число входов.

Функционирование мажоритарного элемента, на входы которого поступают величины F1, F2, и F3 и по результатам голосования вырабатывается выходная величина F, представлено в таблице 4.2.

Таблица 4.2

|

F1 |

F2 |

F3 |

F |

a1 |

a0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

0 |

0 |

Кроме выхода F, в таблице даны и выходы a1, ао - старший и младший разряды двухразрядного кода, указывающего номер отказавшего канала при F=1 (см. рисунок 4.4). Из таблицы легко получить функции, которые после несложных преобразований приводятся к следующим:

![]()

Рисунок 4.4 – Схема голосования с мажоритарным элементом

В схемах типа (см. рисунок 4.4) от мажоритарного элемента требуется особенно высокая надежность, т. к. его отказ делает бесполезной всю схему резервирования.

4.2.2 Контроль по модулю 2.

Контроль правильности передач и хранения данных - важное условие нормальной работы ЦУ.

Кодовая комбинация - набор из символов принятого алфавита.

Код - совокупность кодовых комбинаций, используемых для отображения информации.

Кодовое расстояние между двумя кодовыми комбинациями - число разрядов, в которых эти комбинации отличаются друг от друга.

Минимальное кодовое расстояние dmin - минимальное кодовое расстояние для любой пары комбинаций, входящих в данный код.

Кратностью ошибки называют число ошибок в данном слове (число неверных разрядов).

Из теории кодирования известны условия обнаружения и исправления ошибок при использовании кодов:

![]()

где dmjn - минимальное кодовое расстояние кода;

гобн и гиспр - кратность обнаруживаемых и исправляемых ошибок соответственно.

Вес кода - число единиц в данной комбинации.

Для двоичного кода минимальное кодовое расстояние dmjn = 1, поэтому он не обладает возможностями какого-либо контроля производимых над ним действий. Чтобы получить возможность обнаруживать хотя бы ошибки единичной кратности, нужно увеличить минимальное кодовое расстояние на 1. Это и сделано для кода контроля по модулю 2 (контроля по четности/нечетности).

При этом способе контроля каждое слово дополняется контрольным разрядом, значение которого подбирается так, чтобы сделать четным (нечетным) вес каждой кодовой комбинации. При одиночной ошибке в кодовой комбинации четность (нечетность) ее веса меняется, а такая комбинация не принадлежит к данному коду, что и обнаруживается схемами контроля. При двойной ошибке четность (нечетность) комбинации не нарушается - такая ошибка не обнаруживается. Легко видеть, что у кода с контрольным разрядом

dmin = 2.

При контроле по четности вес кодовых комбинаций делают четным, при контроле по нечетности - нечетным.

Контроль по модулю 2 реализуется с помощью схем свертки. Для практики типична многоярусная схема свертки пирамидального типа.

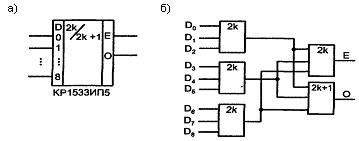

Примером ИС свертки по модулю 2 может служить микросхема ИП5 серии КР1533 (см. рисунок 4.5,а). Схема имеет 9 входов, что допускает свертку байта с девятым контрольным разрядом. Двумя выходами схемы являются Е (Even) и О (Odd). Если вес входной комбинации четный, то Е = 1 и О = 0, и наоборот, если вес нечетный.

Рисунок 4.5 – Микросхема ИКР1533ИП5

Схемотехнически ИС КР1533ИП5 представляет собою пирамидальную структуру из трехвходовых элементов типа четность/нечетность (см. рисунок 4.5,б).

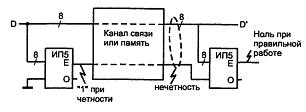

Передача данных с контролем по модулю 2 показана на рисунке 4.6. Входные данные обозначены через D, а на выходе из канала связи данные обозначены через D', поскольку вследствие ошибок они могут измениться.

Рисунок 4.6 – Применение ИП5 для контроля канала связи (памяти)

4.2.3 Контроль с использованием кодов Хемминга.

Применение кодов Хемминга позволяет исправлять единичные ошибки приемном конце. Для получения кодовой комбинации кода Хемминга к информационному слову добавляется несколько контрольных разрядов. C целью определения значений контрольных разрядов примем, что контрольные разряды занимают позиции с номерами 2i (i = 0, 1, 2,...), т.е. 1, 2, 4, …

Каждый контрольный разряд ассоциируется с некоторой группой разрядов кодовой комбинации и выводит вес группы, в которую он входит, на четность/нечетность.

Первый контрольный разряд (1-я позиция) входит в группу разрядов с номерами, соответствующие двоичному коду хх...хх1, где х – 0 или 1. Иными словами в первую группу входят разряды с нечетными номерами: 1, 3, 5, 7, ... .

Второй контрольный разряд (2-я позиция) входит в группу разрядов с номерами, имеющими единицу во втором справа разряде, т. е. номерами, соответствующие двоичному коду хх...х1х. Это номера 2, 3, 6, 7, ... .

Третий контрольный разряд (4-я позиция) входит в группу, у которой номера разрядов имеют единицу в третьем справа разряде, соответствующий двоичному коду хх...1хх, т. е. с номерами 4, 5, 6, 7, ... .

Контрольные разряды выводят веса своих групп на четность/нечетность. Далее для определенности примем, что ведется контроль по четности. Производится столько проверок по модулю 2, сколько контрольных разрядов в кодовой комбинации, т. е. проверяется сохранение четности весов групп. Если в кодовой комбинации произошла ошибка, то в одних проверках она скажется, а в других - нет. Это и позволяет определить разряд, в котором произошла ошибка. Для восстановления правильного значения слова теперь остается только проинвертировать ошибочный разряд.

Пример: составить код Хемминга для четырехразрядного информационного слова А = а3а2а1а0 = 0110 (см. таблицу 4.3).

Таблица 4.3

|

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

|

р |

а3 |

а2 |

а1 |

р3 |

а0 |

р2 |

р1 |

|

0 1 1 0 1 0 |

0 0 0 0 0 0 |

0 0 0 0 1 1 |

0 0 1 1 0 0 |

0 0 1 1 1 1 |

0 1 0 1 0 1 |

0 1 0 1 1 0 |

0 1 1 0 0 1 |

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

1 0 … 1 |

0 1 … 1 |

1 0 … 1 |

1 0 … 1 |

0 1 … 1 |

1 0 … 1 |

0 1 … 1 |

0 0 … 1 |

Через р в таблице обозначен общий контрольный разряд для всей кодовой комбинации, через p1, р2, р3 - первый, второй и третий групповые контрольные разряды.

Не учитывая пока разряд р, получим, что правильная кодовая комбинация имеет вид:

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

1 |

Пусть во втором слева разряде (в 6-м разряде) произошла ошибка и принята комбинация:

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

|

0 |

0 |

1 |

0 |

0 |

1 |

1 |

Первая проверка (по группе разрядов с нечетными номерами) показывает сохранение четности, т. е. в этой группе ошибок нет, результат этой проверки отмечается нулем.

Вторая проверка (по разрядам 2, 3, 6, 7) обнаруживает нарушение четности веса комбинации, ее результат отмечается единицей.

Третья проверка (по разрядам 4, 5, 6, 7) также обнаруживает нарушение четности, ее результат отмечается единицей.

Результаты проверок образуют слово, называемое синдромом. Синдром указывает номер разряда, в котором произошла ошибка. В этом примере результаты проверок дают слово 110 = 610. Проинвертировав разряд номер 6, возвращаемся к правильной кодовой комбинации - ошибка исправлена.

Минимальное кодовое расстояние обычного кода Хемминга равно dmin =3. Добавление p разряда проверки общей четности приводит к модифицированному коду Хемминга с dmin = 4 и, соответственно, добавляет возможность обнаружения двойной ошибки. Обнаружение двойной ошибки основано на сопоставлении наличия или отсутствия признаков ошибки в синдроме и общей четности. Если обозначить через S любое ненулевое значение синдрома, то возможные ситуации, используемые для обнаружения двойной ошибки, окажутся следующими (см. таблицу 4.4).

Таблица 4.4

|

Синдром |

Свертка кода |

Результат |

|

0 |

0 |

Все правильно |

|

S |

1 |

Была единичная ошибка, исправлена |

|

S |

0 |

Есть ошибка двойной и большей кратности, слово использовать нельзя |

|

0 |

1 |

Код Хемминга относится к числу простых. Есть много более сложных кодов с большими корректирующими возможностями (БЧХ, код Файра, код Рида- Соломона и др.).

5 Лекция. Сумматоры

Сумматоры выполняют арифметическое сложение и вычитание чисел, являются ядром схем арифметико-логических устройств (АЛУ) процессоров.

5.1 Одноразрядный сумматор

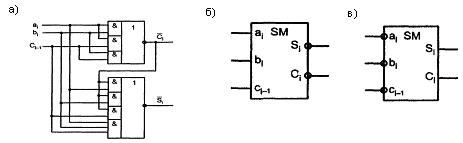

Одноразрядный сумматор имеет три входа (два слагаемых и перенос из предыдущего разряда) и два выхода (суммы и переноса в следующий разряд).

Таблица 5.1 - Таблица истинности одноразрядного сумматора

|

ai |

bi |

ci-1 |

Si |

Ci |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

Аналитические выражения функций суммы и переноса (С от англ. carry) имеют вид

![]() .

(5.1)

.

(5.1)

![]() .

(5.2)

.

(5.2)

Из таблицы 5.1 видно, что во всех строчках, кроме первой и последней,

![]() .

(5.3)

.

(5.3)

Формула (5.3) будет справедливой для всех строк

таблицы 5.1, если в 1-й строке было не ![]() , а

, а ![]() , т.е. по формуле (5.3) соблюдалось

равенство 0=1∙0 (проинвертировать функцию переноса

, т.е. по формуле (5.3) соблюдалось

равенство 0=1∙0 (проинвертировать функцию переноса ![]() ) и в последней строке добавить

) и в последней строке добавить ![]() .

.

С учетом этого формула (5.3) примет окончательный вид

![]() .

(5.4)

.

(5.4)

Схема сумматора, реализующая выражения (5.2 и 5.4), показана на рисунке 5.1,а.

Рисунок 5.1 – Схема одноразрядного сумматора и условные обозначения (б,в)

Функция суммы Si, и функция переноса Ci обладают свойством самодвойственности (см. таблицу 5.1): при инвертировании всех аргументов инвертируется и значение функции, т. е.

![]() .

(5.5)

.

(5.5)

5.2 Последовательный сумматор

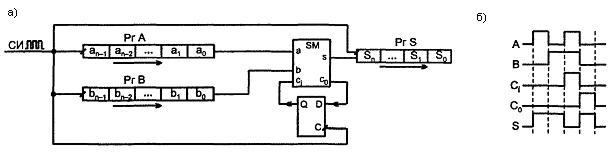

Сумматор для последовательных операндов содержит всего один одноразрядный сумматор, обрабатывающий поочередно разряд за разрядом, начиная с младшего. Сложив младшие разряды, одноразрядный сумматор вырабатывает сумму для младшего разряда результата и перенос, который запоминается на один такт. В следующем такте складываются вновь поступившие разряды слагаемых a1 и b1 с переносом из младшего разряда и т. д.

Схема сумматора последовательных операндов (см. рисунок 5.2,а), помимо сумматора, содержит сдвигающие регистры слагаемых A,B и суммы S, а также D-триггер запоминания переноса. Регистры A,B,S и D-триггер тактируются синхроимпульсами СИ. На рисунке 5.2,6 показана временная диаграмма, соответствующая операции сложения двух операндов 101 + 110= 1011 или в десятичном выражении 5 + 6 = 11.

Рисунок 5.2 – Схема последовательного сумматора (а) и

временная диаграмма (б)

5.3 Параллельный сумматор с последовательным переносом

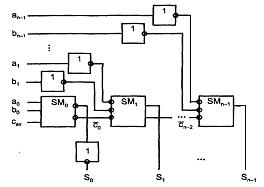

Сумматор для параллельных операндов с последовательным переносом строится как цепочка одноразрядных, соединенных последовательно по цепям переноса. Для схемы с одноразрядными сумматорами, вырабатывающими инверсии суммы и переноса, такая цепочка имеет вид, приведенный на рисунке 5.3, поскольку функции суммы и переноса самодвойственны (5.5). Там, где в разряд сумматора должны подаваться инверсные аргументы, в их линиях имеются инверторы, а там, где вырабатывается инверсная сумма, инвертор включен в выходную цепь.

Рисунок 5.3 – Схема параллельного сумматора с последовательным переносом

5.4 Параллельный сумматор с параллельным переносом

Сумматоры для параллельных операндов с параллельным переносом разработаны для получения максимального быстродействия.

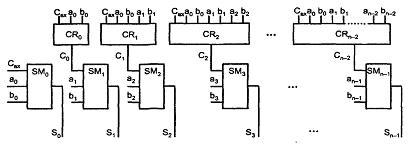

Сумматоры с параллельным переносом не имеют последовательного распространения переноса вдоль разрядной сетки. Во всех разрядах результаты вырабатываются одновременно, параллельно во времени. Сигналы переноса для данного разряда формируются специальными схемами, на входы которых поступают все переменные, необходимые для выработки переноса, т. е. те, от которых зависит его наличие или отсутствие. Одноразрядные сумматоры, имеющиеся в разрядных схемах, здесь упрощены, т. к. от них выход переноса не требуется, достаточно одного выхода суммы (см. рисунок 5.4). Обозначение CR от слова саrrу (перенос).

Рисунок 5.4 – Структура сумматора с параллельным переносом

Функция генерации принимает 1, если перенос на выходе данного разряда появляется независимо от наличия или отсутствия входного переноса. Очевидно, что эта функция gi = аibi.

Функция прозрачности (транзита) принимает 1, если

перенос на выходе данного разряда появляется только при наличии входного

переноса. Эта функция hi

=

aivbi.

Строго говоря, ![]() , но т. к. при аi

= bi

= 1, т. е. в ситуации, где между функциями ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ проявляется

разница, перенос все равно формируется из-за gi = 1, допустимо

заменить функцию прозрачности на дизъюнкцию. Теперь выражение для сигнала

переноса можно записать в виде

, но т. к. при аi

= bi

= 1, т. е. в ситуации, где между функциями ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ проявляется

разница, перенос все равно формируется из-за gi = 1, допустимо

заменить функцию прозрачности на дизъюнкцию. Теперь выражение для сигнала

переноса можно записать в виде ![]() .

.

Для произвольного разряда с номером i можно записать

![]() . (5.6)

. (5.6)

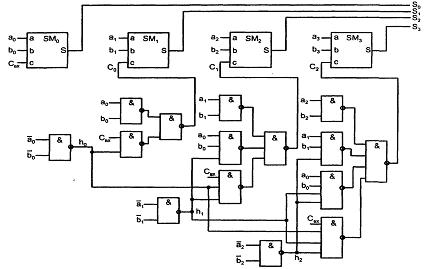

Предпочтительна схема на элементах И-НЕ (у стандартных элементов имеется до восьми входов по И). Перевод полученных выражений в базис И-НЕ дает выражения

![]() ,

,

![]() ,

,

![]() .

(5.7)

.

(5.7)

Рисунок 5.5 – Вариант схемы сумматора с параллельным переносом

Схема сумматора (см. рисунок 5.5) соответствует полученным выражениям. Диапазон разрядностей, в которых проявляются достоинства сумматоров с параллельным переносом, невелик. До n = 3...4 применяются схемы сумматоров с последовательным переносом, до n = 8 с параллельным переносом, а после n = 8 – сумматоры групповой структуры.

5.5 Сумматоры групповой структуры

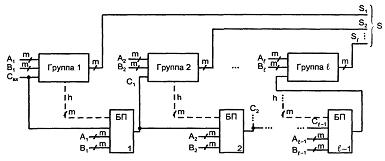

В сумматорах групповой структуры схема с разрядностью n делится на L групп по m разрядов (n = Lm). В группах и между ними возможны различные виды переносов, что порождает множество вариантов групповых сумматоров. Ниже рассмотрены основные варианты: с последовательным и параллельным переносами между группами. Групповой сумматор с последовательным переносом при L группах имеет L - 1 блоков переноса. Блоки переноса включены последовательно и образуют тракт передачи переноса (см. рисунок 5.6). Слагаемые разбиты на m-разрядные поля, суммируемые в группах. Результат также составляется из m-разрядных полей.

Рисунок 5.6 – Схема группового сумматора с последовательным переносом

Блоки переноса БПi (i = 1...) анализируют слагаемые в пределах группы, и если из группы должен быть перенос, то он появляется на выходе блока для подачи на вход следующей группы и в цепочку распространения переноса от младших групп к старшим.

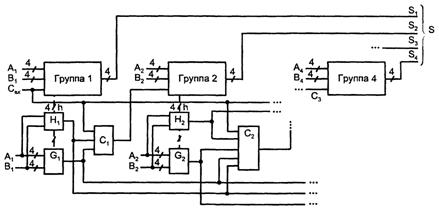

Сумматор с параллельными межгрупповыми переносами строится по структуре, сходной со структурой сумматора с параллельным переносом, в которой роль одноразрядных сумматоров играют группы.

При построении обычного сумматора с параллельными переносами каждый разряд характеризовался функциями генерации и прозрачности gi = aibi и hi = aivbi.

С помощью этих функций вырабатывался сигнал переноса по соотношению

![]() .

.

В групповом сумматоре с параллельными межгрупповыми переносами роль одного "разряда" играет группа, которую также характеризуют функциями генерации и прозрачности. Обозначив эти функции большими буквами, можем записать соотношения:

![]() , (5.8)

, (5.8)

согласно которому группа прозрачна при прозрачности всех ее разрядов, и

![]() ,

(5.9)

,

(5.9)

справедливость которого видна из предыдущего изложения способа построения сумматора с параллельным переносом.

Из групп собирается та же схема ,что и из одноразрядных сумматоров, с параллельными межгрупповыми переносами согласно выражению для переноса на выходе группы с номером i:

![]() .

(5.10)

.

(5.10)

Структура группового сумматора с параллельными межгрупповыми переносами показана на рисунке 5.7, где разрядность и число групп приняты равными 4. Функции прозрачности Н, могут вырабатываться как функции операндов или через использование функций прозрачности разрядов h, которые имеются в группах, если в них организован параллельный перенос (штриховые линии).

Рисунок 5.7 – Схема группового сумматора с параллельным переносом

5.5.1 Сумматор с условным переносом.

Сумматор с условным переносом - СБИС программируемой логики, улучшающая быстродействие сумматоров с последовательным переносом.

Сумматор с n разрядами делят на две равные группы с разрядностями n/2. Старшую группу дублируют, так что в схему входят три сумматора с разрядностью n/2.

Рисунок 5.8 – Схема сумматора с условным переносом

На одном суммируются младшие поля операндов Aмл и Вмл. На втором - старшие поля операндов при условии Свх = 1, в третьем - старшие поля операндов при условии Свх = 0. После получения результата в младшем сумматоре становится известным фактическое значение переноса в старший сумматор, и из двух заготовленных заранее результатов выбирается тот, который нужен в данном случае. Цепь последовательного переноса здесь как бы укорачивается вдвое, т. к. обе половины сумматора работают параллельно во времени.

6 Лекция. АЛУ и матричные умножители

6.1 Арифметико-логические устройства

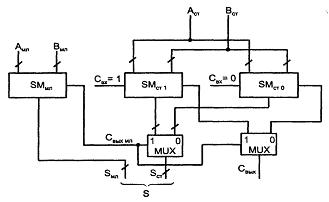

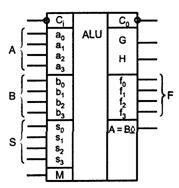

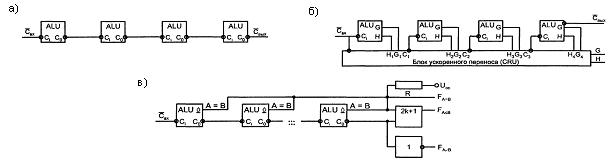

Основой АЛУ (Arithmetic-Logic Unit) служит сумматор, схема которого дополнена логикой, расширяющей функциональные возможности и обеспечивающей его перестройку с одной операции на другую. Обычно АЛУ четырехразрядные и для наращивания разрядности объединяются с формированием последовательных или параллельных переносов. Логические возможности АЛУ разных технологий (ТТЛШ, КМОП, ЭСЛ) сходны.

АЛУ (см. рисунок 6.1) имеет входы операндов А и В, входы выбора операций S, вход переноса Ci и вход М (Mode), сигнал которого задает тип выполняемых операций: логические (М = 1) или арифметико-логические (М = 0). Результат операции вырабатывается на выходах F, выходы G и Н дают функции генерации и прозрачности, используемые для организаций параллельных переносов при наращивании размерности АЛУ. Сигнал Со - выходной перенос, а выход А = В - выход сравнения на равенство с открытым коллектором.

Рисунок 6.1 – Условное обозначение АЛУ

Перечень выполняемых АЛУ операций дан в таблице 6.1. Для краткости двоичные числа S3S2S1S0 представлены их десятичными эквивалентами. Входной перенос поступает в младший разряд слова - 000Сi. Логические операции поразрядные. При арифметических операциях учитываются межразрядные переносы.

16 логических операций позволяют воспроизводить все функции двух переменных. В арифметико-логических операциях встречаются и логические и арифметические операции одновременно.

Например, ![]() - вначале поразрядно выполняются операции

инвертирования (В), логического сложения (АvВ) и умножения

(АВ), а затем полученные указанным образом два четырехразрядных числа

складываются арифметически.

- вначале поразрядно выполняются операции

инвертирования (В), логического сложения (АvВ) и умножения

(АВ), а затем полученные указанным образом два четырехразрядных числа

складываются арифметически.

При операциях над словами большой размерности АЛУ соединяются друг с другом с организацией последовательных (см. рисунок 6.2,а) или параллельных (см. рисунок 6.3,б) переносов. В последнем случае совместно с АЛУ применяют микросхемы - блоки ускоренного переноса (CRU, Carry Unit), получающие от отдельных АЛУ функции генерации и прозрачности, а также входной перенос и вырабатывающие сигналы переноса по известным формулам.

Таблица 6.1 – Перечень операций АЛУ

|

S |

Логические функции (М=1) |

Арифметико-логические функции (М=0) |

|

0 1 2 3 |

0000 |

A + Ci

1111 +Ci |

|

4 5 6 7 |

|

|

|

8 9 10 11 |

В АВ |

A + AB + Ci A + B + Ci

AB + 1111 + Ci |

|

12 13 14 15 |

1111

А |

A + A + Ci A v B + A + Ci

A + 1111 + Ci |

Блок CRU вырабатывает также функции генерации и прозрачности для всей группы обслуживаемых им АЛУ, что при необходимости позволяет организовать параллельный перенос на следующем уровне (между несколькими группами из четырех АЛУ).

Рисунок 6.2 - Схемы наращивания АЛУ при последовательном (а) и параллельном (б) переносах и реализация функций компаратора для группы (в)

На рисунке 6.2,в показаны способы выработки сигналов сравнения слов для группы АЛУ. Выход сравнения на равенство выполняется по схеме монтажной логики для выходов типа ОК. Комбинируя сигнал равенства слов с сигналом переноса на выходе группы при работе АЛУ в режиме вычитания, легко получить функции Fa≥b и Fa≤b. Если А<В, то при вычитании возникает заем из старшего разряда и Fa≤b = 1. Если заем отсутствует (А>В), то получим Fa≥b = 1.

6.2 Матричные умножители

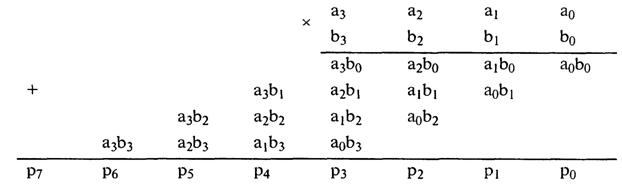

Структура матричных умножителей тесно связана со структурой математических выражений, описывающих операцию умножения.

Пусть имеются два целых двоичных числа без знаков Am = am-1...ao и

Bn=bn-1...bo. Их перемножение выполняется по известной схеме "умножения столбиком". Если числа четырехразрядные, т. е. m = n = 4, то

Члены вида aibj, где i = 0... (m - 1) и j = 0... (n - 1) вырабатываются параллельно во времени конъюнкторами. Их сложение в столбцах, которое можно выполнять разными способами, составляет основную операцию для умножителя и определяет почти целиком время перемножения.

Матричные перемножители могут быть просто множительными блоками (МБ) или множительно-суммирующими (МСБ), последние обеспечивают удобство наращивания размерности умножителя.

МСБ реализует операцию Р = Аm х Вn + Сm + Dn, т. е. добавляет к произведению два слагаемых: одно разрядности m, совпадающей с разрядностью множимого, другое разрядности n, совпадающей с разрядностью множителя.

6.2.1 Множительно-суммирующие блоки.

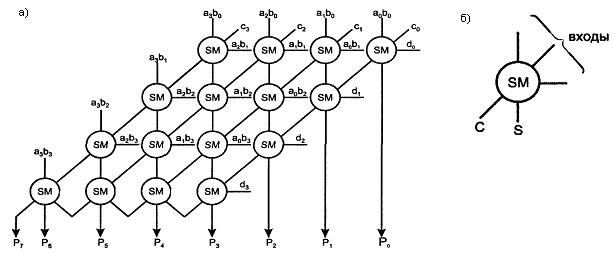

Множительно-суммирующий блок для четырехразрядных операндов без набора конъюнкторов, вырабатывающих члены вида аibj, показан на рисунке 6.3, а, где для одноразрядного сумматора принято обозначение (см. рисунок 6.3,б).

Рисунок 6.3 – Схема МСБ для четырехразрядных сомножителей (а) и обозначение одноразрядного сумматора для данной схемы (б)

Для построения МСБ чисел равной разрядности требуется n2 конъюнкторов и n2 одноразрядных сумматоров.

6.2.2 Схемы ускоренного умножения.

Рассмотрим процесс умножения по модифицированному алгоритму Бута -умножение сразу на два разряда. Уменьшение суммирований частичных произведений существенно сокращает время произведения. К этому приводит алгоритм, основанный на следующих рассуждениях.

Пусть требуется вычислить произведение

![]() . (6.1)

. (6.1)

Непосредственное воспроизведение соотношения (6.1) связано с выработкой частичных произведений вида

Abi2i (i = 0...n - 1). (6.2)

Число таких произведений равно разрядности множителя n.

Выражение (6.1) можно видоизменить с помощью соотношения

![]() . (6.3)

. (6.3)

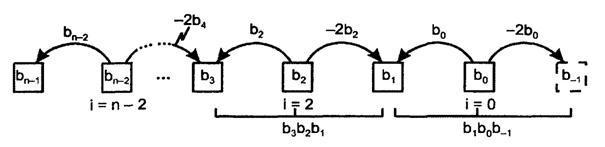

Это соотношение позволяет разреживать последовательность степеней в сумме частичных произведений. Можно, например, исключить четные степени, как показано на рисунке 6.4.

Рисунок 6.4 – Исключение четных степеней множителя

Исключение четных (или нечетных) степеней не только изменяет значения оставшихся частичных произведений, но и сокращает их число примерно вдвое, что ускоряет выработку произведения. По формуле (6.3) для расширения разрядной сетки "разносят по соседям" члены с четными степенями b222,bo2o,

b-22-2 в выражении (6.1) для множителя В.

После чего оставшиеся частичные произведения для любого i-го разряда имеют вид

![]() .

(6.4)

.

(6.4)

Если сравнить (6.1) и (6.4), то частичных произведений уменьшилось примерно вдвое. При применении этого алгоритма говорят об умножении сразу на два разряда (левые i+1 и правые i-1 коэффициенты от четного разряда i).

Используя (6.4) для всех возможных сочетаний bi+1, bi, bi-1, можно составить таблицу 6.2 частичных произведений.

Таблица 6.2

|

bi+1 |

bi |

bi-1 |

Значение скобки |

Ri/2i |

Операция для получения Ri/2i |

|

0 |

0 |

0 |

0 |

0 |

Замена А нулем |

|

0 |

0 |

1 |

1 |

А |

Скопировать А |

|

0 |

1 |

0 |

1 |

А |

Скопировать А |

|

0 |

1 |

1 |

2 |

2А |

Сдвиг А влево |

|

1 |

0 |

0 |

-2 |

-2А |

Сдвиг А влево и перевод в доп.код |

|

1 |

0 |

1 |

-1 |

-А |

Перевод А в доп.код |

|

1 |

1 |

0 |

-1 |

-А |

Перевод А в доп.код |

|

1 |

1 |

1 |

0 |

0 |

Замена А нулем |

Пример.

Пусть требуется умножить 1010 на 0111, т. е. 10∙7 = 70. При разреживании частичных произведений оставим только нечетные (см. рисунок 6.4).

Тогда по формуле (6.4) получим

![]() .

.

Из полученного выражения видно, что необходимо расширить разрядную сетку множителя В влево на 1 разряд и вправо на 2 разряда, т.е.

В = b4b3b2b1bob-1b-2 = 0011100.

Первому частичному произведению соответствует тройка bob-1b-2 = 100. Из таблицы 6.2 получаем, что этой тройке соответствует частичное произведение

R-1 = -2А∙2-1 = -А,

для получения которого требуется перевести А в дополнительный код. Сама величина А в пределах разрядной сетки произведения должна быть записана как 0001010, ее обратный код 1110101 и дополнительный код 1110110.

Второму частичному произведению соответствует тройка b2b1bo = 111, следовательно, второе частичное произведение равно R1 = 0 (см. таблицу 6.2).

Третьему частичному произведению соответствует тройка b4b3b2 = 001, следовательно, оно имеет вид R3 = А∙23 = 1010000 (сдвиг А на 3 разряда влево).

Для получения результата заданного умножения требуется сложить частичные произведения:

1110110

1010000

-----------

1000110 = 26 + 22 + 21 = 64 + 4 + 2 =70.

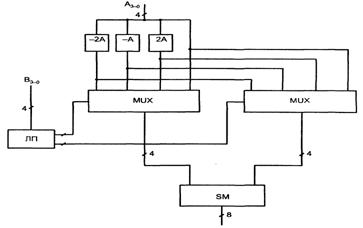

Схема, реализующая алгоритм быстрого умножения, показана на рисунке 6.5.

Рисунок 6.5 – Схема быстрого умножения

Множимое А поступает на ряд преобразователей, заготавливающих все возможные варианты частичных произведений (-2А, -А, 2А), кроме самого А и нуля, которые не требуют схемной реализации. Множитель В поступает на логический преобразователь ЛП, который анализирует тройки разрядов, декодирует их и дает мультиплексорам (MUX) сигналы выбора того или иного варианта частичных произведений (см. таблицу 6.2). Окончательный результат получается путем суммирования частичных произведений с учетом их взаимного сдвига в разрядной сетке. Размерность умножителя «4х4».

7 Лекция. Триггеры и регистры

7.1 Триггеры

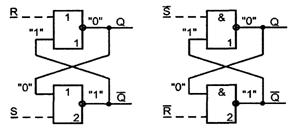

Триггеры - элементарные автоматы, содержащие элемент памяти (фиксатор) и схему управления. Фиксатор строится на двух инверторах, связанных друг с другом "накрест", так что выход одного соединен с входом другого. Такое соединение дает цепь с двумя устойчивыми состояниями (см. рисунок 7.1.). Если на выходе инвертора 1 имеется логический ноль, то он обеспечивает на выходе инвертора 2 логическую единицу и наоборот.

Рисунок 7.1 – Варианты схем асинхронного RS-триггера

Установочные сигналы показаны на рисунке 7.1

штриховыми линиями. Буквой R латинского алфавита (от Reset) обозначен сигнал

установки триггера в 0 (сброса), а буквой S (от Set) - сигнал установки в

состояние логической 1 (установки). Состояние триггера считывается по значению

прямого выхода, обозначаемого как Q или второго выхода с инверсным сигналом ![]() . Для

RS-триггера

на элементах ИЛИ-НЕ установочным сигналом является 1, поскольку только он

приводит логический элемент в 0 независимо от сигналов на других входах

элемента (см. рисунок 7.1,а). Для RS-триггера на элементах И-НЕ

установочным сигналом является нулевой (см. рисунок 7.1,б).

. Для

RS-триггера

на элементах ИЛИ-НЕ установочным сигналом является 1, поскольку только он

приводит логический элемент в 0 независимо от сигналов на других входах

элемента (см. рисунок 7.1,а). Для RS-триггера на элементах И-НЕ

установочным сигналом является нулевой (см. рисунок 7.1,б).

7.1.1 Классификация триггеров.

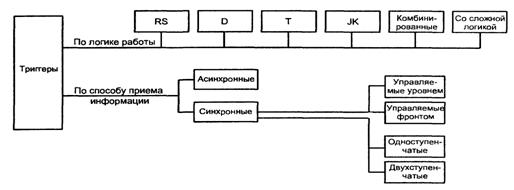

Классификация триггеров проводится по признакам логического функционирования и способу записи информации (см. рисунок 7.2).

Рисунок 7.2 – Классификация триггеров

По логическому функционированию различают триггеры типов RS, D, T, JK и др. Кроме того, используются комбинированные триггеры, в которых совмещаются одновременно несколько типов, и триггеры со сложной входной логикой (группами входов, связанных между собой логическими зависимостями).

Триггер типа RS имеет два входа - установки в единицу (S) и установки в ноль (R). Одновременная подача сигналов установки S и сброса R не допускается (эта комбинация сигналов называется запрещенной).

Триггер типа D (от слова Delay - задержка) имеет один вход. Его состояние повторяет входной сигнал, но с задержкой, определяемой тактовым сигналом.

Триггер типа Т изменяет свое состояние каждый раз при поступлении входного сигнала. Имеет один вход, называется триггером со счетным входом или счетным триггером.

Триггер типа JK универсален, имеет входы установки (J) и сброса (К), подобные входам триггера RS. В отличие от последнего, допускает ситуацию с одновременной подачей сигналов на оба входа (J = К = 1). В этом режиме работает как счетный триггер относительно третьего (тактового) входа.

В комбинированных триггерах совмещаются несколько режимов. Например, триггер типа RST - счетный триггер, имеющий также входы установки и сброса.

Примером триггера со сложной входной логикой служит JK-триггер с группами входов J1J2J3 и К1К2К3, соединенными операцией конъюнкции:

![]() .

.

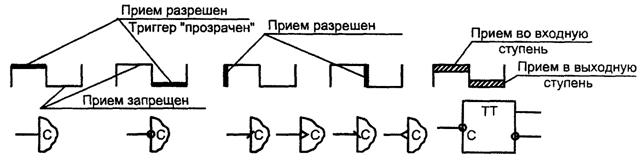

По способу записи информации различают асинхронные (нетактируемые) и синхронные (тактируемые) триггеры. В нетактируемых переход в новое состояние вызывается непосредственно изменениями входных информационных сигналов. В тактируемых, имеющих специальный вход С(от слова Clock), переход происходит только при подаче на этот вход тактовых сигналов. Тактовые сигналы называют также синхронизирующими, исполнительными, командными и т. д.

По способу восприятия тактовых сигналов триггеры делятся на управляемые уровнем и управляемые фронтом. Управление уровнем означает, что при одном

уровне тактового сигнала триггер воспринимает входные сигналы и реагирует на них, а при другом не воспринимает и остается в неизменном состоянии. При управлении фронтом разрешение на переключение дается только в момент перепада тактового сигнала (на его фронте или спаде).

Триггеры, управляемые фронтом, называют также триггерами с динамическим управлением. Динамический вход может быть прямым или инверсным. Прямое динамическое управление означает разрешение на переключение при изменении тактового сигнала с нулевого значения на единичное, инверсное - при изменении тактового сигнала с единичного значения на нулевое.

По характеру процесса переключения триггеры делятся на одноступенчатые и двухступенчатые.

В одноступенчатом триггере переключение в новое состояние происходит сразу, в двухступенчатом - по этапам. Двухступенчатые триггеры состоят из входной и выходной ступеней. Переход в новое состояние происходит в обеих ступенях поочередно. Один из уровней тактового сигнала разрешает прием информации во входную ступень при неизменном состоянии выходной ступени. Другой уровень тактового сигнала разрешает передачу нового состояния из входной ступени в выходную.

На рисунке 7.3 показаны процессы, происходящие в синхронных (тактируемых) триггерах. На диаграммах тактовых импульсов отмечено содержание процессов на отдельных этапах, под диаграммами даны обозначения входов для соответствующих триггеров.

Рисунок 7.3 - Временные диаграммы, поясняющие работу синхронных триггеров, и условные обозначения тактирующих входов

В схемах буферных регистров используется термин "триггер-защелка" (Latch). Под этим понимается триггер, который прозрачен при одном уровне тактового сигнала и переходит в режим хранения при другом. Двухступенчатый триггер обозначается двумя буквами ТТ. Двухступенчатые триггеры часто называют также триггерами типа MS (англ. Master-Slave, т. е. хозяин - раб): входная ступень вырабатывает новое значение выходной переменной Q, а выходная его копирует.

С синхронизацией (тактированием) триггера связаны два параметра - время предустановки tSU (Set-Up Time) и время выдержки tH (Hold Time).

Время tSU - это интервал до поступления синхросигнала, в течение которого информационный сигнал должен оставаться неизменным (см. рисунок 7.4).

Рисунок 7.4 – Время нарастания переднего фронта синхроимпульса

Время выдержки tH - это время после поступления синхросигнала, в течение которого информационный сигнал должен оставаться неизменным. Соблюдение времен предустановки и выдержки обеспечивает правильное восприятие триггером входной информации.

7.1.2 Схемотехника триггеров.

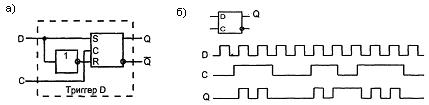

Между триггерами RS и D с одной стороны и Т, JK с другой имеется существенная разница. RS, D-триггеры имеют разомкнутую структуру, а Т, JK-триггеры замкнутую с обратной связью, т.е. используют выходные сигналы для воздействия на свои входы.

D-триггер получается из триггера RS, если подавать на вход S значение D, а на вход R его инверсию (см. рисунок.7.5,а). Информационный сигнал D запоминается только в момент синхроимпульса С (см. рисунок 7.5,б).

Рисунок 7.5 – Схема D-триггера (а) и временная диаграмма (б)

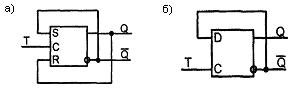

Т-триггер образуется на основе триггера RS по схеме (см. рисунок 7.6,а). В этом случае роль счетного входа играет тактирующий вход С.

Рисунок 7.7 – Схема Т-триггера

При каждом разрешении приема информации по входу тактирования С Т-триггер по обратным связям принимает состояние, противоположное текущему, т. е. переключается. Т-триггер аналогичным способом можно получить и на основе D-триггера (см. рисунок 7.6, б).

Работоспособность счетного Т-триггера обеспечивается применением в рассматриваемой структуре непрозрачных триггеров (двухступенчатых или с динамическим управлением) или внутренних задержек.

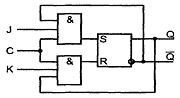

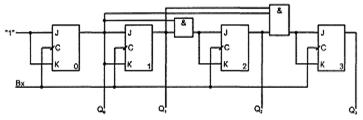

Схема JK-триггера (см. рисунок 7.7) зависит от таблицы 7.1.

Рисунок 7.7 – Схема JK-триггера

Таблица 7.1 – Таблица истинности JK-триггера

|

J |

K |

Qн |

|

0 |

0 |

Q |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

|

Во избежание режима генерации, как и для счетного Т-триггера, здесь требуется применять RS-триггер двухступенчатого типа или с динамическим управлением.

7.2 Регистры

7.2.1 Классификация регистров.

Регистры оперируют с множеством связанных переменных, составляющих слово. Над словами выполняется ряд операций: прием, выдача, хранение, сдвиг в разрядной сетке, поразрядные логические операции.

Регистры состоят из разрядных схем, в которых имеются триггеры и логические элементы.

По количеству линий передачи переменных регистры делятся на однофазные и парафазные, по системе синхронизации на однотактные, двухтактные и многотактные.

Однако главным классификационным признаком является способ приема и выдачи данных. По этому признаку различают параллельные (статические) регистры, последовательные (сдвигающие) и параллельно-последовательные.

В параллельных регистрах прием и выдача слов производятся по всем разрядам одновременно. В них хранятся слова, которые могут быть подвергнуты поразрядным логическим преобразованиям.

В последовательных регистрах слова принимаются и выдаются разряд за разрядом. Их называют сдвигающими, т. к. тактирующие сигналы при вводе и выводе слов перемещают их в разрядной сетке. Сдвигающий регистр может быть нереверсивным (с однонаправленным сдвигом) или реверсивным (с возможностью сдвига в обоих направлениях).

Последовательно-параллельные регистры имеют входы-выходы одновременно последовательного и параллельного типа. Имеются варианты с последовательным входом и параллельным выходом (SIPO, Serial Input - Parallel Output), параллельным входом и последовательным выходом (PISO).

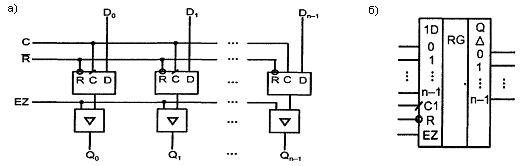

В параллельных (статических) регистрах схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи тактирования, сброса/установки, разрешения выхода или приема, т. е. цепи управления. Пример схемы статического регистра, построенного на D- триггерах с прямыми динамическими входами, имеющего входы сброса R и выходы с третьим состоянием, управляемые сигналом EZ, показан на рисунке 7.8.

Для современной схемотехники характерно построение регистров именно на D-триггерах, преимущественно с динамическим управлением. Многие имеют выходы с третьим состоянием, некоторые регистры относятся к числу буферных, т. е. рассчитаны на работу с большими емкостными или низкоомными активными нагрузками. Это обеспечивает их работу непосредственно на магистраль (без дополнительных схем интерфейса).

Рисунок 7.8 – Схема статического регистра (а) и его условное обозначение (б)

7.2.2 Сдвигающие регистры.

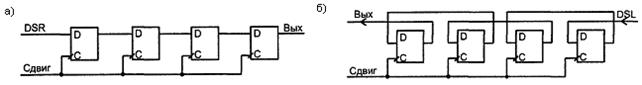

Последовательные (сдвигающие) регистры представляют собою цепочку разрядных схем, связанных цепями переноса.

В однотактных регистрах со сдвигом на один разряд вправо (см. рисунок 7.9,а) слово сдвигается при поступлении синхросигнала. Вход и выход последовательные (DSR- Data Serial Right). На рисунке 7.9,б показана схема регистра со сдвигом влево (вход данных DSL - Data Serial Left).

Рисунок 7.9 – Схема регистра сдвига вправо (а) и влево (б)

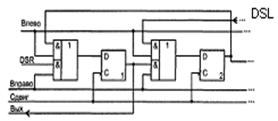

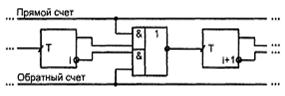

На рисунке 7.10 иллюстрируется принцип построения реверсивного регистра, в котором имеются связи триггеров с обоими соседними разрядами, но соответствующими сигналами разрешается работа только одних из этих связей.

Рисунок 7.10 – Схема реверсивного регистра

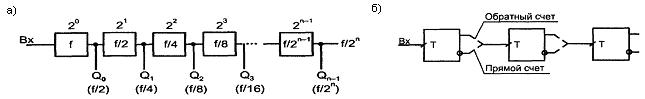

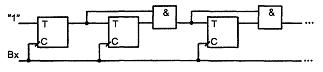

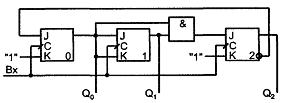

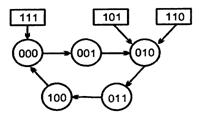

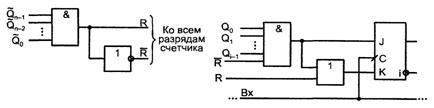

8 Лекция. Двоичные счетчики

К счетчикам относят автоматы, которые под действием входных импульсов переходят из одного состояния в другое, фиксируя тем самым число поступивших на их вход импульсов в том или ином коде. Основной операцией является изменение содержимого счетчика на единицу. Прибавление такой единицы соответствует операции инкрементации (INR), вычитание - операции декрементации (DCR).

Счетчик характеризуется модулем счета М, который определяет число возможных состояний. После поступления на счетчик М входных сигналов начинается новый цикл, повторяющий предыдущий.

8.1 Классификация счетчиков

По способу кодирования внутренних состояний различают двоичные счетчики, счетчики Джонсона, счетчики с кодом «1 из N» и др.

По направлению счета счетчики делятся на суммирующие (прямого счета), вычитающие (обратного счета) и реверсивные (с изменением направления счета).

По принадлежности к тому или иному классу автоматов говорят о синхронных или асинхронных счетчиках.

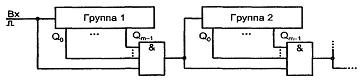

Счетчики строятся из разрядных схем, имеющих межразрядные связи. Соответственно организации этих связей различают счетчики с последовательным, параллельным и комбинированными переносами.

Возможные режимы работы счетчика:

- регистрация числа поступивших на счетчик сигналов;

- деление частоты.

В первом режиме результат - содержимое счетчика, во втором режиме выходными сигналами являются импульсы переполнения счетчика.

Быстродействие счетчика характеризуется временем установления в нем нового состояния (первый режим), а также максимальной частотой входных сигналов fmax.

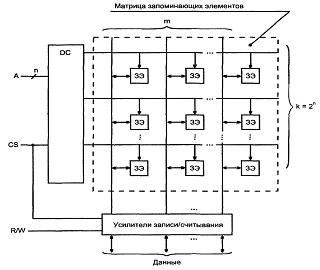

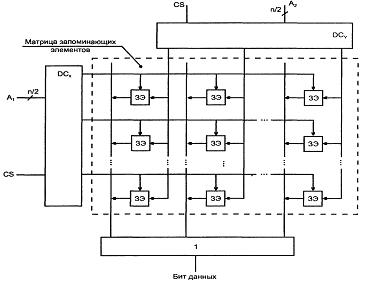

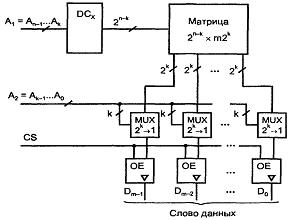

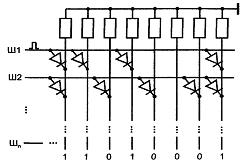

Как и любой автомат, счетчик можно строить на триггерах любого типа, однако удобнее всего использовать для этого триггеры типа Т (счетные) и JK, имеющие при J = К = 1 счетный режим.