Коммериялық емес акционерлық қоғам

АЛМАТЫ ЭНЕРГЕТИКА ЖӘНЕ БАЙЛАНЫС УНИВЕРСИТЕТІ

Электроника кафедрасы

СХЕМОТЕХНИКА 1

5В070400 – Есептеу техникасы мен бағдарламалық камту, 5В070300- Ақпараттық жұйелері мамандықтары бойынша барлық оқу түрінің студенттері үшін зертханалық жұмыстарға арналған әдістемелік нұсқау

Алматы 2011

ҚҰРАСТЫРУШЫ: Ұ.Қ.Дегембаева. Электроника. 5В070400 – Есептеу техникасы мен бағдарламалық камту, 5В070300- Ақпараттық жұйелері мамандықтары бойынша барлық оқу түрінің студенттері үшін зертханалық жұмыстарға арналған әдістемелік нұсқау – Алматы: АЭжБУ, 2011. – 30 б.

Әдістемелік жазба Ақпараттық технология факультетінің студенттері үшін «Схемотехника 1» пәні бойынша зертханалық жұмыстарды орындауға көмекші құралы болып табылады. Оқу құралында қысқаша анықтамалар қарастырылып, зерттеулерді орындауға тапсырмалары бар зертханалық жұмыстардың жазбалары мазмұндалған. Орындалатын жұмыс оның көлемі мен тізбектілігі оқылатын курс ерекшеліктеріне байланысты оқытушымен реттеледі.

Әдістемелік нұсқаулар радиотехника және байланыс факультеті мамандықтарының барлық оқу түріндегі студенттеріне арналған.

Без.17, кесте. 14, әдеб. көрсеткіші. – 16 атау.

Пікір беруші: тех.ғыл.канд., Байкенов Б.С.

«Алматы энергетика және байланыс университетінің» коммерциялық емес акционерлік қоғамының 2011 ж. баспалық жоспары бойынша басылады.

© «Алматы энергетика және байланыс университетінің» КЕАҚ, 2011 ж. ъ

Мазмұны

|

DS зертханалық стендін және ewb бағдарламасын сипаттау |

4 |

|

1 Зертханалық жұмыс. DTL NAND логикалық элементтері |

5 |

|

2 Зертханалық жұмыс. ТТЛ сериялы инвертордың логикалық элеметтерін зерттеу |

7 |

|

3 Зертханалық жұмыс. ESL NOR логикалық сериясының Схемасын зерттеу |

10 |

|

4 Зертханалық жұмыс. МОП-құрылымды комплиментарлы логикалық элементтер |

18 |

|

5 Зертханалық жұмыс. Логикалық элементтер серияларының әртүрлі комбинацияларын зерттеу |

23 |

|

6 Зертханалық жұмыс. 220 платасында зақымдануларды табу |

25 |

|

7 Зертханалық жұмыс. Шмит триггері. Шмит триггерлеріндегі электронды күзет |

31 |

|

Әдебиеттер тізімі |

37 |

DEGEM SISTEMS зертханалық стендінің сипаттамасы

Курс ЕВ-220 «Сандық электроника» сериясынан эксперименттер жүргізуге арналған бірінші жұмыс панелі болып табылады. Ол түрлі сериялы логикалық элементтермен жұмыс істеуге арналған, сондай-ақ ол түрлі технологияларды қолданумен құрылған. Стенд мынадай 6 схемалардан тұрады:

- DTL NAND логикалық элементтер;

- комплиментарлы МОП-құрылымы;

- HCT INV GATE интегралдық инвертор;

- ТТЛ сериялы инвертор;

- TSL NOR логикалық элементтер сериясы;

- түрлі сериялар комбинациясы, сондай-ақ ЕВ-220 платасында зақымдануларды табу мүмкіндігі берілген.

ЕВ-220 панелінде түпшелер мен қосу тораптарының көп саны кездеседі. Тұрақты ток көздері сапасында +5 кернеуімен РS-1, PS-2 қолданылады, ал айналмалы ток көздері сапасында сыртқы немесе ішкі генераторларды қолдануға болады.

ЕВ-220 панелін және EWB бағдарламасын қолданудың мақсаты құру дағдыларын меңгеру және түрлі сериялы логикалық элемент параметрлері компоненттерін жасау болып табылады. Сондай-ақ, CMOS, NAND және NOR инверторлы логикалық элементтерін құру.

Жабдықтар: DEGEM SISTEMS ақпаратты кешені және IBM- Windows операциялық жүйесімен үйлескен дербес компьютер.

Сандық құрылғыларда және есептеуіш техника құрылғыларында екі сигнал қолданылады: логикалық нөл және логикалық бірлік. Соның ішінде әр логикалық сигналға кернеудің анықталған абсолютті мәні сәйкес келеді. Бұл кернеулер оң және теріс логикалы элементтер үшін әр түрлі болып келеді. Одан басқа, логикалық бірлік және логикалық нөл кернеуі түрлі технологиялармен дайындалған элементтер (ТТЛ-, КМОП-, И2Л, ЭСЛ-элементтері) үшін де әр түрлі болады.

Микросхеманың әр сериясында базалық элементтер бар, олар көбіне осы серияның барлық микросхемаларының құрауыштарын сипаттайды.

Бұл жұмыста шығыс кернеулерінің ТТЛ және КМОП базалы логикалық элементтерде берілетін кіріс кернеулерінен тәуелділілігінің қалай өзгеретіні зерттелген.

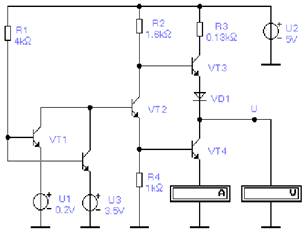

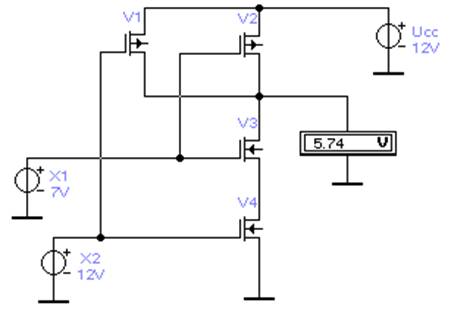

U1 және U3 кернеу көздері кіріс сигналдарын имитациялайды, сондай-ақ төмен кернеулер логикалық нөлге, ал айтарлықтай жоғарылары – логикалық бірлікке сәйкес келеді. VT1 таңбасымен таңбаланған екі транзисторлар екіэмиттерлі транзисторды имитациялайды (өкінішке орай, мұндай транзисторлар EWB элементті кітапханаларында жоқ).

Х1 және Х2 көздері аналогтық қызметтерді орындайды: кіріс сигналдарын имитациялайды.

Қарастырылған элементтер ЖӘНЕ-ТЕРІСТЕУ логикалық қызметтерін орындайды, сондықтан кіріске жоғары деңгейлі екі кернеуді жіберу кернеу шығысында жақын деңгей бойынша нөл вольтының пайда болуына алып келеді.

Кіріс кернеуінің жатық өзгерісі шығыс кернеуінің сызықсыз өзгерісіне алып келеді (жіберу сипатты кейбір бөлімдерде сызықты бөлімдер бақыланады).

№ 1 Зертханалық жұмыс. DTL NAND логикалық элементтері

Жұмыстың мақсаты: NAND Схемасы жұмысын зерттеу және ДТЛ сериясының сипаттамасын алу.

1 Үй жұмысы

1.1.1 Ұсынылған әдебиет бойынша (5,17,18) теориялық сұрақтарға алдын ала жауап беру.

1.1.2 Зертханалық жұмысқа әдістемелік көрсеткіштерді оқу.

1.2 ДТЛ сериясы элементтерінің сипаты

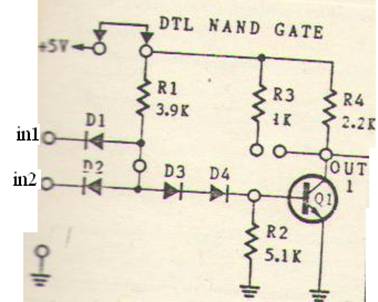

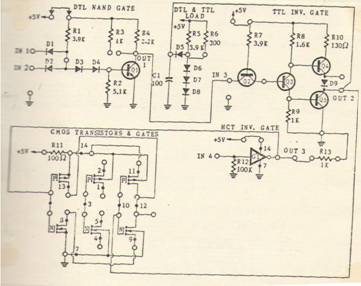

Жоғары сол бұрышта жұмыс панелінде DTL NAND сериялы логикалық элементтің экспериментті контуры Схемасын табу.

1 сурет

1.3 Бақылау сұрақтары

1) Базалы логикалық элементтің негізгі электрлік параметрлерін атап шығыңыз.

2) Логикалық элементтің беріліс сипатына анықтама беріңіз.

3) Логикалық схемалардың тағайыны қандай?

4) ЖӘНЕ схемасы қандай операцияны орындайды?

5) Қай схема логикалық операцияны модельдейді:

а) 1*1=1;

б) 1+1=1.

6) Байланыс арнасы дегеніміз не?

7) Модуляция дегеніміз не?

8) Импульсты модуляцияның қандай түрі болмайды?

9) Параметрлері тұрақты элементтерден тұратын және электрлік әсерлерден де, уақыттан да тәуелді болмайтын тізбектер қалай аталады?

10) Параметрлері тұрақты элементтерден тұратын және электрлік әсерлерге (токқа немесе кернеуге) тәуелді, бірақ уақытқа тәуелсіз тізбектер қалай аталады?

1.4 Жұмыстық тапсырмалар

1.4.1 Ube=0,5 B Uvdiode=0,6 B

Ube,sat=0,7 B Ud,on=0.7 B

Uce,sat=0,2 B βtyp=70 тең деп алып,

in1 және in2-де төрт комбинация мүмкіндігі үшін in1 шығысында кернеуді есептеңіз. Схеманың, шын мәнінде, NAND логикалық функциясын жүзеге асыратынын көрсетіңіз.

1.4.2 Логикалық 1 немесе логикалық 0 шығысында қоректендіру көздерінен схемамен тұтынылған токты есептеңіз.

1.4.3 Ашық R3 кезінде 0 және 1 шығысы үшін жұмыстық Uсе кернеуін және Іс тогын табыңыз.

1.4.4 Шығысқа қосылған идентивті каскадтар үшін шығыс бойынша тармақталу коэффициентін есептеңіз.

1.5 Зертхана жұмысын орындауға арналған әдістемелік

көрсеткіштер

1.5.1 Схеманы 1-суретте көрсетілгендей етіп құрастырыңыз. Кіріске 5В кернеуін беріңіз, сондай-ақ, кернеуді А және В логикалық ауыстырып-қосқыштың in1 және in2 кірістерінде өлшеңіз.

1.5.2 Мүмкін болатын барлық А және В комбинациясы үшін шығыс кернеулерін өлшеңіз. Шыққан нәтижелерді 1.1 –кестеге толтырыңыз.

1.1 к е с т е

|

in1 |

in2 |

Шығыс |

|

|

(volts) |

Logic level |

||

|

0 |

0 |

|

|

|

0 |

1 |

|

|

|

1 |

0 |

|

|

|

1 |

1 |

|

|

1.5.3 Шығыста логикалық 1 немесе логикалық 0 үшін қоректендіру көздерінен Схемамен тұтынылған токты өлшеңіз. in1=0 және in2=1 үшін Д1 арқылы көшетін токты өлшеңіз.

1.5.4 Шығыста (R3 резисторы ашық) логикалық 1 немесе логикалық 0 үшін Uсе кернеуін өлшеңіз.

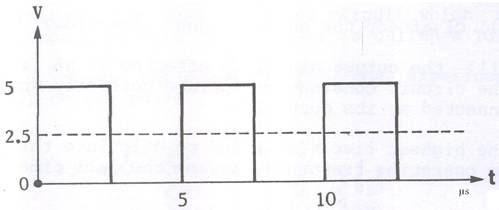

1.5.5 in1-ге логикалық 1 мәнін беріңіз. Толқынның тікбұрышты формасын 200 кГц жиілікпен және 5В қос импульсты амплитудамен in2-ге 2.3-суретте көрсетілгендей етіп, жалғаңыз. in1-ді осциллографпен жалғаңыз және ұлғаю уақытын өлшеңіз. Енді R3-ті R4 -ке параллель етіп жалғаңыз және олардың шығыс сигналдарына қалай әсер ететіндігін тексеріңіз.

1.2 сурет

1.5.6 out1-ді жүктеме тізбегіне (DTL§TTL LOAD) R6 ашық резисторымен жалғаңыз. Біздің схеманы идентивті өз өзіне каскадпен жүктейтіндігімізге назар аударыңыз.

а) жүктеме тізбегінде out1-ден in1=1 және in2=0 немесе 1 үшін ағымдағы токты өлшеңіз және жазып алыңыз.

б) in2-ні шығыс тікбұрышты сигналға жалғаңыз және жүктеме жоқ кездегі шығыс нәтижелерін салыстырыңыз.

в) R6 және R5 жалғаңыз. Бұл 14-ші идентивті каскадты жүктемеге эквивалентті. Шығыс токтарын өлшеңіз және жазып алыңыз. Жүктеменің шығыс сигналдарына қалай әсер ететіндігін жазып алыңыз.

1.5.7 Кернеуді схеманың екі, содан кейін үш кірісіне жіберіңіз және шыққан нәтижелерін 3-кестеге толтырыңыз, кестені дәл етіп толтыруды ұмытпаңыз.

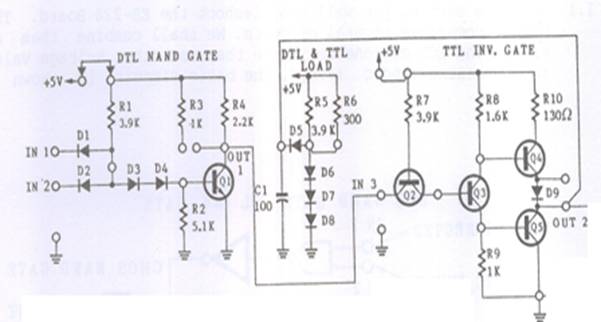

1.3 сурет

1.5.8 Инвертор схемасын жалғаңыз. Содан кейін логикалық 0 немесе логикалық 1 бар кездегі ток схемасына қоректендіруден бөлінген токты өлшеңіз. Бұны орындау үшін кернеуді резисторда (100 Ом) өлшеңіз және сәйкесті токты есептеңіз.

1.5.9 Резисторлы жүктемені қолдануда бір контакт жерлендірілуі қажет.

2 зертханалық жұмыс. ТТЛ сериялы инвертордың логикалық элеметтерін зерттеу

Жұмыстың мақсаты: түрлі серияларға жататын логикалық элементтердің қалай құрамдастырыла алатынын оқу.

2.1 Алдын ала дайындалу

2.1.1 Зертханалық жұмысты орындамас бұрын, алдын ала ұсынылған әдебиеттер бойынша ТТЛ сериялы логикалық элементтер туралы теориялық мағлұматтарды оқып үйрену.

2.1.2 Зертхана жұмысына берілген тапсырмаларды және оған берілген әдістемелік көрсеткіштерді оқу.

2.1.3 Анықтама бойынша паспортты деректерді жазу және түрлі логикалық элементтердің зерттелген түрлерінің сипаттарын салу.

Қолданылған құралдар мен элементтер:

- PU-2000 орталық процессоры;

- ЕВ-220 баспа платасы;

- сандық әмбебап құралы;

- осциллограф.

2.2 Бақылау сұрақтары

1) Егер Q2-ні көпэмиттерлі транзисторға ауыстырса, онда логикалық элементтің қай Схемасы И-НЕ немесе НЕ-И болады?

2) R8 және R10 арқылы ағымдағы ток неге айтарлықтай аз болуы мүмкін?

3) 14 каскадтар шығыста параллельді жалғанып тұрған кезде 0 логикалық деңгейге сәйкесетін кернеу неге артады?

4) 1кОм резисторлы жүктемесі жалғанып тұрған кезде 1 логикалық деңгейге сәйкес келетін кернеу неге артты?

5) ТТЛ элементінің Схемалық әртүрлілігін атаңыз және келтіріңіз.

6) Базалы логикалық элементтер құруда қолданылатын негізгі Схематехникалық шешімдерді атаңыз; оларды техникалық параметрлер бойынша салыстырыңыз.

7) Схематехнологияны қолданумен нақты типті есептей отырып, кірістің «артық» режімі туралы мәселе қалай шешіледі?

8) Логикалық элементтердің кіріс сандарын өсіру қалай іске асырылады?

9) ДТЛ элементтерімен салыстыру бойынша ТТЛ элементтерінің артықшылықтарын атаңыз.

2.3 Зертханалық жұмысқа арналған тапсырмалар

2.3.1 Схеманың қалай жұмыс істеп жатқанын тексеріңіз және оның шын мәнінде инвертор екенін дәлелдеңіз. Сіз Q2 шығысының жүктеме Схемасына (DTL§TTL) жалғанатынын көре аласыз.

2.3.2 Қоректендіру көздерінен тұтынылған токты өлшеңіз.

2.3.3 1-кестеге ток мәнін кіріс логикалық деңгей функциясы сияқты толтырыңыз.

2.3.4 Жүктеме Схемасында R6-ны R5-ке параллель жалғаңыз. Бұның шығыста кернеу деңгейіне қалай әсер ететінін анықтаңыз.

2.3.5 С1-ден тұратын жүктеме Схемасын ажыратыңыз және шығысты R12 резисторына жалғаңыз. Резистордың екінші жағын жерлендіру қажет. Бұл жүктеме шығыс сигналына қалай әсер етеді?

2.4 Есептік тапсырмалар

2.4.1 Қоректендіру көздерінен тұтынылатын токты есептеңіз және өлшенген мәнмен салыстырыңыз. Егер айырмашылық көп болса, онда қалай екенін бағалап көріңіз.

2.4.2 Тұтынатын орта қуатты Схемамен есептеңіз. Кірісте жарты уақытта Схема логикалық 0-ге ие, ал қалған уақытта – логикалық 1-ге ие болады. Бұл нәтижені CMOS логикалық элементімен тұтынылатын қуатпен салыстырыңыз.

2.4.3 Нәтижені ДТЛ логикалық элементімен тұтынылатын қуатпен салыстырыңыз.

2.5 Жұмысты орындауға арналған әдістемелік көрсеткіштер

2.5.1 PU-2000 жүйесіне ЕВ-220 баспа платасын қою.

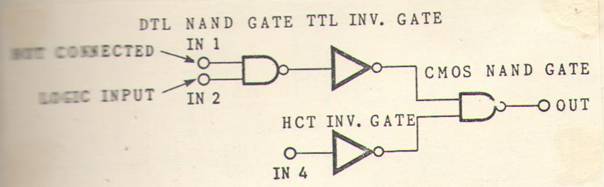

2.5.2 1 суреті бойынша Схема құрастырыңыз.

1 сурет – ТТЛ инвертор сериясы

2.1 к е с т е

|

Uвх, В |

Uвых, В |

|

|

|

2.6 ТТЛ-элементінің беріліс сипаттамасын зерттеудің - зертханалық жұмыстың виртуалды бөлігін орындауға арналған тапсырмалар мен әдістемелік көрсеткіштер қою

2.6.1 2.1-суретте көрсетілген Схеманы құрастырыңыз.

2.6.2 1.1-кестеден қажетті деректерді ала отырып, нұсқа нөмеріне сәйкес резисторлар номиналын құрыңыз. Барлық нұсқалар үшін U2=5V.

2.6.3 VT4 транзисторы арқылы шығыс кернеуінің және токтың U1 кернеуі шамасынан (U3 кернеуін U3=3,5В тұрақты қолдау) тәуелділігін зерттеу. Зерттеу қорытындысын 2.2-кестесіне енгізу.

2 сурет

2.2 к е с т е

|

Вариант |

R1, кОм |

R2, кОм |

R3, кОм |

R4, кОм |

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

4 4 4 4 4,1 4,1 4,1 4,1 4 4 4 4 3,9 3,9 3,9 3,9 |

1,6 1,6 1,6 1,6 1,6 1,6 1,6 1,6 1,5 1,5 1,5 1,5 1,7 1,7 1,7 1,7 |

0,12 0,13 0,14 0,15 0,12 0,13 0,14 0,15 0,12 0,13 0,14 0,15 0,12 0,13 0,14 0,14 |

0,91 0,92 0,93 0,94 1,1 1,2 1,3 1,4 0,85 0,86 0,87 0,88 1,11 1,12 1,13 1,14 |

2.3 к е с т е

|

U1,В |

U,В |

I, мА |

|

3,5 2,5 1,5 1,4 1,35 1,3 1,25 1,2 0,8 0,4 0,2 |

|

|

2.6.4 Өлшеу нәтижелері бойынша графиктер құрыңыз: U=ƒ(U1) кіріс кернеуінен U шығыс кернеуінің тәуелділілігі және І=φ(U1) кіріс кернеуінен токтың тәуелділілігі.

2.6.5 График бойынша логикалық бірлікке және логикалық нөлге сәйкесетін кернеуді анықтаңыз. Бұл мәндерді есепке енгізіңіз.

2.7 ТТЛ-элементінің дәл кестесін оң логикамен зерттеу.

2.7.1 ТТЛ-элементінің кіріс кернеуінен U шығыс кернеуінің тәуелділілігін зерттеңіз (2 суретті қара). Ол үшін 2.4 кестесін толтырыңыз.

2.4 к е с т е

|

U1, В |

U3, В |

U, В |

|

0,2 0,2 3,5 3,5 |

0,2 3,5 0,2 3,5 |

|

3 зертханалық жұмыс. ESL NOR логикалық сериясының cхемасын зерттеу

Жұмыстың мақсаты:

–ECL NOR логикалық серияның эксперименталды cхемасын түсіру және талдау;

–10102 жеке нөмері бойынша NOR логикалық элементтердің санын анықтау;

–ECL NOR сериялы логикалық элементтер бойынша анықтамалық әдебиеттермен жұмыс дағдыларын алу.

Бақылау сұрақтары

1) Қандай факторлар ЭСЛ элементтерінің жоғары

жылдамәрекеттерін қамтамасыз етеді?

2) Схема жұмысы келесі тәуелділіктермен сипатталады: хвх.=0 және хвх.=1 кезінде хвых =1-ге тең. Бұл қандай cхема?

3) Сигналды дискреттеу немен қорытындыланады?

4) Кванттау деңгейінің санын қалай анықтауға болады?

5) ЭЕМ жылдамәрекетті өлшем бірлігін атаңыз.

3.1 Алдын ала дайындалу

3.1.1 Зертханалық жұмысты орындамас бұрын, алдын ала ұсынылған әдебиеттер бойынша ECL NOR сериялы логикалық элементтер туралы теориялық мағлұматтарды оқып үйрену.

3.1.2 Зертхана жұмысына берілген тапсырмаларды және оған берілген әдістемелік көрсеткіштерді оқу.

3.2 Қолданылатын құралдар мен элементтер:

- РU–2000 орталық процессоры;

- ЕВ-220 баспа платасы;

- сандық әмбебап құралы;

- осциллограф.

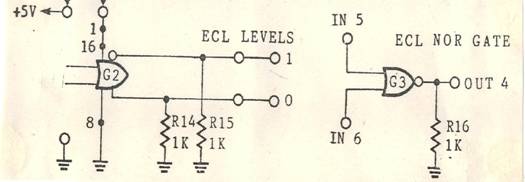

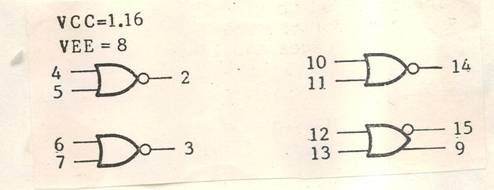

ECL экспериментті cхемасы (эмиттерлі байланысты логикалық cхема) – ECL-ді қолданумен құрылған және 10102 жеке нөмірі бар cхеманың біртұтас бөлігі. Бұл компонент NOR -мен 4 логикалық элементтен тұрады, әрқайсысы екі кіріспен. Қадауыштар суретте көрсетілгендей етіп нөмірленеді, біз 0 және 1 логикалық деңгейлеріне нақты кернеуді алу үшін әрқайсысына екі шығыспен логикалық элементтерді қолданатын боламыз. Бұл логикалық элемент платада G2 болып маркерленеді. Логикалық деңгейлер G2-ден шығуда G3 болып маркерленген NOR логикалық элементін талдау үшін қолданылатын болады. Ол сондай-ақ, ECL-дің логикалық элементі болып табылады.

3.3 Жұмыстық тапсырмалар

3.3.1 Ажыратылған С2 кірісінде cхеманы құрастырыңыз және OUT15 -та логикалық деңгейді анықтаңыз.

3.2 10102 нөмірлі элемент үшін кернеу көздерін анықтаңыз.

3.3.3 R14,R15,R16 резисторларын ИЛИ НЕ ЭСЛ вентилі шығысына жалғаңыз, олардың тағайынын анықтаңыз.

3.3.4 Қосылған С2-де cхеманы құрастырыңыз, шығыс кернеулерінің мәнін «1» және «0» логикалықта жазыңыз.

3.3.5 Т=250C температурада типтілік мән үшін түсу уақытын және өсу уақытын анықтаңыз.

3.3.6 ECL NOR сериялы логикалық элементтің беріліс сипаттамасын анықтаңыз.

3.3.7 Ток көздерінен барлығы «0» шығыс логикалық деңгейге ие болған кезде, төрт логикалық элементтерді (вентильдерді) активациялау үшін токты өлшеңіз.

3.3.8 Схемамен тұтынылған қуатты, сондай-ақ бір ИЛИ НЕ вентилімен тұтынылған қуатты есептеңіз.

3.4 Жұмысты орындауға арналған әдістемелік көрсеткіштер

3.4.1 1-суретте көрсетілген, ECL NOR сериялы логикалық элементтердің экспериментті cхемасын құрастырыңыз.

3.1 сурет

3.4.2 +5В кернеулі көзге cхеманы жалғаңыз, «1» және «0» логикалықтар үшін кернеу деңгейін жазыңыз.

3.4.2 UCC1 және UCC2, сондай-ақ UEE –де кернеу мәнділігін жазыңыз.

3.2 сурет

3.4.3 ЭСЛ логикалық cхема үшін түсу уақыты өсу уақытына, осыған көз жеткізіңіз.

3.4.4 Шығыс кернеуіннің кіріс кернеуінен тәуелділігін алып тастаңыз, деректерді 3.1-кестесіне енгізіңіз.

3.1 к е с т е – НЕМЕСЕ-ЖӘНЕ ЭБЛ вентилі

|

In5 |

In6 |

Out4 |

|||

|

кернеу |

Логикалық деңгей |

кернеу |

Логикалық деңгей |

кернеу |

Логикалық деңгей |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3.4.5 Тұтынылған қуатты мәнділікті өлшеу және қоректендіру көздерінің кернеуі, сондай-ақ бір вентилмен тұтынылатын қуат бойынша есептеңіз.

3.4.7 Схеманың шын мәнінде ИЛИ НЕ вентилі болып табылатындығын анықтаңыз.

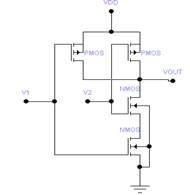

4 Зертханалық жұмыс. МОП-құрылымды комплиментарлы логикалық элементтер

Жұмыстың мақсаты: СМОS логикалық сериялардың сипаттарын зертеу (МОП-құрылымды комплиментарлы).

4.1 Үй жұмысы

4.1.1 Ұсынылған әдебиет (5, 17, 18) бойынша теоретикалық сұрақтарға алдын ала жауап беру.

4.1.2 Лабораториялық жұмыстың әдістемелік көрсеткішін оқу.

4.2 СМОS сериясының элементтерін сипаттау

4.1, 4.2, 4.3 суреттеріндегі стенд үш схемадан тұрады қоректендіруші тізбек пен зерттеу контуры арасында жүйелі қосылған R=100 Ом резисторы құрылды (ол схема жұмысы үшін қажетті болып табылмайды). Ол қоректендіру көзіндегі токты өлшеу үшін орналасқан.

4.3 Бақылау сұрақтары

1) Логикалық элементтердің маңызды статистикалық және динамикалық параметрлерін есептеңіз.

2) ЛЭ инверторының амплитудалық беріліс сипаттамасын көрсетіңіз.

3) Логикалық элементтердің жылдамәрекеті немен анықталады?

4) Базалық логикалық элементтер түсінігінде не тұспалданады?

5) КМОП құрылымдарындағы логикалық элементтер қуатының аз тұтынылуының себебі неде?

4.4 Жұмыстық тапсырма

4.4.1 4.1-суретіне сәйкес эксперименталды Схеманы құрастырыңыз.

Кірісте логикалық 1 және 0 берілгендегі шығысты тексеріңіз, қорытындыны 1-кестеге жазыңыз.

4.4.2 0-ден 5В-ға дейінгі кірісте кернеуді өзгерте отырып, функционалдық генераторға Схеманы қосып шыққан нәтижені 4.2-кестесіне жазыңыз.

4.4.3 4.2-суретіне сәйкес эксперименталды Схеманы құрастырыңыз Кіріс сигналдарының мүмкіндігі әртүрлі комбинациялары үшін алынған шығыстарды тексеріңіз, және қорытындыларды 4.3-кестесіне енгізіңіз.

4.4.4 R13 –ті қосып, резисторлы жүктемені тексеріңіз, әрбір логикалық деңгей үшін шығыста кернеудің қандай болатынын анықтаңыз.

4.4.5 Қосымша инверторды қоса отырып, CMOS жүктемесін тексеріңіз.

4.4.6 Логикалық 1 немесе логикалық 0 шығысы кезіндегі қоректендіру көзінен Схемамен тұтынылатын токты есептеңіз.

4.5 Зертханалық жұмысты орындауға арналған әдістемелік көрсеткіштер

4.5.1 Кіріске 5В кернеуін беріңіз және шығыстағы кернеуді анықтаңыз. Шығыста не болатынын жазыңыз.

1 к е с т е

|

Uкір, В |

Uшығ, В |

|

0 |

|

|

1 |

|

4.5.2 PS-1 кірісіндегі кернеуді азайтыңыз, шығыс сигналын өлшеңіз.

4.1 сурет

4.5.3 Айналмалы генераторды пайдалана отырып, 4.4.2-тармағын орындаңыз, 4.2 кестесін толтырыңыз және беріліс сипаттамасын құрыңыз.

4.2 сурет

4.2 к е с т е

|

Uкір, В |

Uшығ, В |

|

0 |

|

|

1 |

|

|

1,5 |

|

|

2 |

|

|

2,2 |

|

|

2,5 |

|

|

3 |

|

|

4 |

|

|

5 |

|

4.5.4 Схеманың екі, одан кейін үш кірісіне кернеуді беріңіз және қорытындыны 3 кестеге жазыңыз, ақиқат кестесін толтыруды ұмытпаңыз.

4.2– сурет

4.3 к е с т е

|

U1 (В) |

U2 (B) |

U3(В) |

Uшығ .(В) |

|

|

|

|

|

|

|

|

|

|

4.5.5 Инвертор Схемасын жалғаңыз. Содан кейін не логикалық 0, не логикалық 1-і бар кезіндегі токтың қоректендіруші схемасынан бөлінген токты өлшеңіз. Бұны орындау үшін кернеуді резисторда (100 Ом) өлшеңіз және сәйкесті токты есептеңіз.

4.5.6 Резисторлы жүктемені қолдануда бір контакт жерлендірілген болуы керек.

4.5.6 CMOS жүктемесін қолдануда, CMOS транзисторларының жұбын пайдалана отырып, қосымша инверторды қосыңыз. Инверторды CMOS Схемасына емес қандай да бір басқа +5 В қадауышына қосыңыз. Бұл инвертормен берілген қуаттылықты ғана өлшейтініне кепілдік береді. Кіріс сигналдары екі деңгейдің бірі болып табылғанда, CMOS жүктемесінің көмегімен қоректендіруден бөлінген токты өлшеңіз. Нәтижелерді пайдалана отырып, әр жағдайдағы қуатты есептеңіз.

4.5.7 Бөлімде көрсетілген қысқа тұйықталған бөлімнің орнына 13 және 3 қадауыштарының арасына амперметрді қосып құйма тогын өлшеңіз, Токты тікелей өлшеңіз. І инвертор кірісіне логикалық 0 түскенде, ток шығыстан келген бағытқа қарай ағады (қоректендіру көзінің тогы). Бұл ток қоректендіру көзінен І инверторы (PMOS) арқылы 2-инверторға және жерге ағады. Қоректендіру көзі тогын немесе қозғалмалы токты тікелей өлшеңіз.

4.5.8 Әмбебап өлшеу құралын ажыратыңыз және 3-қадауышты 13-қадауышпен қысқартыңыз. ТТЛ деңгейінің сигналын 200 кГц генераторындағы жиілікпен кіріске қосыңыз, енді біріншілікті сигналмен салыстыру бойынша өсу және түсу уақыттарының ұлғаюын тексеріңіз.

4.5.9 R11 резисторындағы кернеуді өлшеңіз және шыққан қорытындыны инвертор шығысына түсетін айналмалы ток қуатын өлшеу үшін пайдаланыңыз.

4.6 КМОП элементінің біріліс сипаттамасының зертханалық жұмыс-зерттеуінің виртуалды бөлігін орындауға арналған тапсырмалар мен әдістемелік көрсеткіштер

4.6.1 4.3 суретінде көрсетілген cхеманы құрастырыңыз.

Шығыс кернеуінің Х1 кернеуі кеңдігінен тәуелділігін зерттеу (Х2 кернеуін тұрақты Х2 = 12 B-пен қолдау). Зерттеу нәтижелерін 4.4 кестесіне енгізіңіз.

4.3 сурет

4.4 к е с т е

|

Х1,В |

U,В |

|

0 1 2 … 11 12 |

|

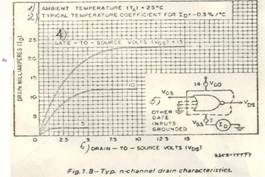

PMOS және NMOS типті транзисторлар үшін анықтамалық спецификациясы

а) б)

4.4 сурет – Құйманың типтік сипаттамалары

а) n-типті арнасымен типтік сипаттамасы

б) p-типті арнасымен типтік сипаттамасы

1) Көз құймасы, Вольт (Uds);

2) Құйма тогы, мА;

3) Логикалық элементтің (вентилдің) басқа кірістері жерлендірілген;

4) Қоршаған орта температурасы;

5) ТД=-0,3 %0С үшін типті температуралы коэффициент.

5 Зертханалық жұмыс. Логикалық элементтер серияларының әртүрлі комбинацияларын зерттеу

Жұмыстың мақсаты: түрлі серияларға жататын логикалық элементтердің қалай құрамдастырыла алатынын оқу.

5.1 Алдын ала дайындалу

5.1.1 Зертханалық жұмысты орындамас бұрын, алдын ала ұсынылған әдебиеттер бойынша логикалық элементтер туралы теориялық мағлұматтарды оқып үйрену.

5.1.2 Зертхана жұмысына берілген тапсырмаларды және оған берілген әдістемелік көрсеткіштерді оқу.

5.1.3 Анықтама бойынша паспортты деректерді жазу және түрлі логикалық элементтердің зерттелген түрлерінің сипаттарын салу.

Қолданылған құралдар мен элементтер:

- PU-2000 орталық процессоры;

- ЕВ-220 баспа платасы;

- сандық әмбебап құралы;

- осциллограф.

2.2 Бақылау сұрақтары:

1) Егер Q2-ні көпэмиттерлі транзисторға ауыстырса, онда логикалық элементтің қай cхемасы И-НЕ немесе НЕ-И болады?

2) R8 және R10 арқылы ағымдағы ток неге айтарлықтай аз болуы мүмкін?

3) И2Л элементтерінің ерекшелігі неде?

5.2 Зертханалық жұмысқа арналған тапсырмалар

5.2.1 Схеманың қалай жұмыс істеп жатқанын тексеріңіз және оның шын мәнінде инвертор екенін дәлелдеңіз.

5.2.2 Қоректендіру көздерінен тұтынылған токты өлшеңіз.

5.2.3 2 кестеге ток мәнін кіріс логикалық деңгей функциясы сияқты толтырыңыз.

5.2.4 ТТЛ элементінің МОП-құрылымды комплиментарлы логикалық элементпен жүктелген схеманы көз алдыңызға елестетіңіз; ол дұрыс жұмыс істей ала ма?

5.2.5 МОП-құрылымды комплиментарлы каскадтағы кіріс тогын өлшеңіз.

5.3 Есептік тапсырмалар

5.3.1 Қоректендіру көздерінен тұтынылатын токты есептеңіз және өлшенген мәнмен салыстырыңыз. Егер айырмашылық көп болса, онда қалай екенін бағалап көріңіз.

5.3.2 Тұтынатын орта қуатты CMOS және ТТL логикалық элементтер схемасымен есептеңіз. Кірісте жарты уақытта схема логикалық 0-ге ие, ал қалған уақытта – логикалық 1-ге ие болады. Бұл нәтижені CMOS логикалық элементімен тұтынылатын қуатпен салыстырыңыз.

5.4 Зертханалық жұмысқа арналған әдістемелік көрсеткіштер

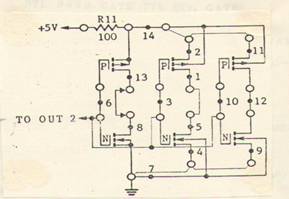

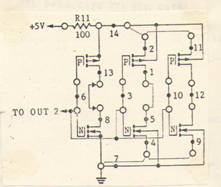

5.4.1 МОП-құрылымды комплиментарлы инвертор кірісін ТТЛ инверторы шығысына қосыңыз. Енді МОП-құрылымды комплиментарлы инвертор шығысы ТТЛ инверторы кірісіне ілесетін болады. Содан кейін шығыстағы кернеу деңгейін өлшеңіз. Схеманы 1 суреттегідей жалғаңыз, онда ТТЛ-инверторы МОП-құрылымды комплиментарлы инвертордың үш логикалық элементімен жүктелуі тиіс.

а) 2,11 қадауыштарын +5 В-ға жалғаңыз.

б) 4,9 қадауыштарын 7-ге жалғаңыз (жер).

в) 1 және 5 қадауыштарын қосыңыз.

г) 13 және 8 қадауыштарын қосыңыз.

5.4.2 Екі логикалық деңгейлер үшін біреуінің шығысында МОП-құрылымды комплиментарлы логикалық элементтен 0 және 1 кіріс шамасы үшін кернеуді табыңыз.

5.4.3 С1-ден тұратын жүктемелік схеманы ажыратыңыз және шығысты R12 резисторына (оның қарсылықтарын алдын ала өлшеп) қосыңыз. Резистордың екінші жағын жерлендіру қажет. Бұл жүктеме шығыс сигналына қалай әсер ететін болады?

5.1 сурет – Логикалық элементтер серияларының комбинациясы

5.1 к е с т е

|

Uкір, В |

Uшығ, В |

|

|

|

6 Зертханалық жұмыс. 220 платасында зақымдануларды табу

Жұмыстың мақсаты: түрлі серияларға жататын логикалық элементтердің қалай құрамдастырыла алатынын оқу.

6.1 Алдын ала дайындалу

6.1.1 Зертханалық жұмысты орындамас бұрын, алдын ала ұсынылған әдебиеттер бойынша эмиттерлі байланысты схема компоненттерінен басқа, ТТЛ сериялы логикалық элементтер туралы теориялық мағлұматтарды оқып үйрену.

6.1.2 Зертхана жұмысына берілген тапсырмаларды және оған берілген әдістемелік көрсеткіштерді оқу.

6.1.3 Анықтама бойынша паспортты деректерді жазу және түрлі логикалық элементтердің зерттелген түрлерінің сипаттарын салу.

Қолданылған құралдар мен элементтер:

- PU-2000 орталық процессоры;

- ЕВ-220 баспа платасы;

- сандық әмбебап құралы;

- осциллограф.

6.2 Жұмыстық тапсырмалар

6.2.1 Схеманың қалай жұмыс істеп жатқанын тексеріңіз және оның шын мәнінде инвертор екенін дәлелдеңіз. Сіз Q2 шығысының жүктеме схемасына (DTL§TTL) жалғанатынын көре аласыз.

6.2.2 Қоректендіру көздерінен тұтынылған токты өлшеңіз.

6.2.3 6.1-кестеге ток мәнін кіріс логикалық деңгей функциясы сияқты толтырыңыз.

6.2.4 Жүктеме схемасында R6-ны R5-ке параллель жалғаңыз. Бұның шығыста кернеу деңгейіне қалай әсер ететінін анықтаңыз.

6.2.5 С1-ден тұратын жүктеме схемасын ажыратыңыз және шығысты R12 резисторына жалғаңыз. Резистордың екінші жағын жерлендіру қажет. Бұл жүктеме шығыс сигналына қалай әсер етеді?

6.3 Есептік тапсырмалар

6.3.1 Қоректендіру көздерінен тұтынылатын токты есептеңіз және өлшенген мәнмен салыстырыңыз. Егер айырмашылық көп болса, онда неге екенін бағалап көріңіз.

6.3.2 Тұтынатын орта қуатты схемамен есептеңіз. Кірісте жарты уақытта схема логикалық 0-ге ие, ал қалған уақытта – логикалық 1-ге ие болады. Бұл нәтижені CMOS логикалық элементімен тұтынылатын қуатпен салыстырыңыз.

6.4 Зертханалық жұмысты орындауға арналған әдістемелік көрсеткіштер

6.4.1 Схеманы платада 3-суретте көрсетілгендей етіп қосыңыз.

6.4.2 NAND, ДТЛ, НСТ, ДТЛ схемаларын және II торабын +5 В-ға қосыңыз.

6.4.3 R13 резисторының бір жағын жерлендіріңіз.

6.4.4 OUT1 және IN3 жалғаңыз.

6.4.5 OUT2 –ты жалпы Д5/СI нүктесіне жалғаңыз. R6 және R5–ті 10-ға параллелді жалғаңыз.

6.4.6 8 және 9; 12 және 13 нүктелерін қосыңыз.

6.4.7 OUT3-ты 6-нүктеге және R13-тің басқа келесі жағына жалғаңыз. Жиналған схема енді 6.2-схемасы сияқты болуы керек.

6.2 сурет – Зақымдалуды табу үшін пайдаланылған детальді көрсетілген схеманың қосылысы

6.4.8 Логикалық кірістерді ІN2, IN4-ке (IN1 бос қалады; ашық кірістің жоғары логикалық деңгейге сәйкес келетінін есіңізге түсіріңіз) жалғаңыз. 6.3 кестесін толтырыңыз.

6.3 к е с т е

|

IN2 |

IN4 |

OUT1 |

|

0 |

0 |

|

|

0 |

1 |

|

|

1 |

0 |

|

|

1 |

1 |

|

6.4.9 Егер cхема дұрыс жұмыс істесе, онда 6.4 кестеде көрсетілген нүктелердегі кернеу деңгейін өлшеңіз.

6.4 к е с т е

|

IN2 |

IN4 |

OUT шарттары |

OUT3 |

CMOS |

OUT2 |

OUT1 |

Негізгі қосылыстар |

|||

|

Q1 |

D1 |

D2 |

D3 |

|||||||

|

0 |

0 |

ОК Fault (зақымдану)1 Fault8 |

|

|

|

|

|

|

|

|

|

0 |

1 |

ОК Fault1 Fault8 |

|

|

|

|

|

|

|

|

|

1 |

0 |

ОК Fault1 Fault8 |

|

|

|

|

|

|

|

|

|

1 |

1 |

ОК Fault1 Fault8 |

|

|

|

|

|

|

|

|

6.4.10 200 кГц жиілікті комплиментарлы МОП-құрылымды ТТЛ сигналын IN2-ге жалғаңыз. Логикалық 0 және логикалық 1-ді кезекпен IN4-ке жалғаңыз. Осы екі жағдайда OUT және OUT2 толқын қалыптарын бақылаңыз және олардың уақытша диаграммасын құрыңыз.

6.3 сурет – Зақымдануды табу үшін қолданылатын тексеріс схемасы

6.4.11 Зақымдануды табу әдістемесі.

6.5 және 6.6 кестелерінде РИ-2000 – пуск блогында (модулінде) жұмыс істеудегі жұмыс режімін анықтаудың қажетті негізгі қадамдары сипатталған. Төменде ЕВ-220 платасы үшін кодтың келесі қадамдары берілген:

6.5 к е с т е

|

|

РС1 |

РС2 |

|

ЕВ-220 |

805 |

658 |

6.6 к е с т е

|

STEP 1 |

KEY IN 2 |

DISPLAY 3 |

COMMENTS 4 |

|

1 |

|

PCb/PC1 |

PCb displayed for one second, followed by PC1. 5 |

|

2 |

805 |

805 |

Key in first 3 digits of board code (таблица 5) 6 |

|

3 |

* |

PCb/PC2 |

PCb displayed for one second, followed by PC2. 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

658 |

658 |

Key in last 3 digits of board code (таблица 5) 8 |

|

5 |

* |

EB-220 |

Board number displayed in alternating parts 9 |

|

6 7 |

* * |

Idl Id2 |

Omits student number update. If laboratory is connected to computer, key in student number in 3 parts, striking the * after each part. 10 |

|

8 |

* |

Id3 |

|

|

9 |

* |

Fn |

Selects operational mode (function) 11 |

|

10 |

2 |

Fn2 |

Sets Practice Mode 12 |

|

11 |

* |

P.00 |

Practice mode – intsert fault number 13 |

1 – қадам;

2 – пернені қосу;

3 – дисплейге жазу;

4 – түсіндірмелер;

5 – РС1-ден кейін 1 секунд ішінде РСв жарықтанады;

6 – Плата кодының алғашқы 3 санын қосыңыз (1-кесте);

7 – РСв 1 секунд ішінде, содан кейін РС2 жарықтанады;

8 – Плата кодының соңғы 3 санын қосыңыз (1-кесте)

9 – Плата нөмірі кезекпен жарықтанады;

10– Егер зертхана компьютермен қосылған болса, сәулелену нөмірін бөліңіз;

11–Жұмыс режімін таңдау (функциялар);

12 – Practice Mode сериялары;

13 – Практикалық режім –зақымдалу күнін қойыңыз.

Кейбір істен шығуларды енгізу үшін Practice Mode режімінде 6.7 кестесінде көрсетілген қадамдарға сәйкес жұмыс істеңіз.

6.7 к е с т е

|

STEP 1 |

KEY IN 2 |

DISPLAY 3 |

COMMENTS 4 |

|

1 |

|

P.00 |

Practice Mode. 00 is the fault number 5 |

|

2 |

XX |

P.XX |

Selecting fault number XX (XX = 0…12 6 |

|

3 |

* |

P.XX |

The display will blink one second; 7 Then the faule will be introduced |

6.4.12 Зақымдалуларды нәтижелер бланкінде сипаттаңыз.

а) 8 зақымдалуларын енгізу.

б) 6.8 кестесінде көрсетілген өлшеулерді орындаңыз.

6.8 к е с т е

|

IN2

1 |

IN4

2 |

Cтатус

3 |

OUT

|

OUT3

|

Terminal 9 on the CMOS circuit 4 |

OUT2

|

OUT1 |

|

0 |

0 |

5 Correct 6 Fault 1 Fault 8 |

|

|

0V Undefined 0mV |

|

|

|

0 |

1 |

Correct Fault 1 Fault 8 |

|

|

Undefined Undefined Undefined |

|

|

|

1 |

0 |

Correct Fault 1 Fault 8 |

|

|

0V Undefined 0V |

|

|

|

1 |

1 |

Correct Fault 1- Fault 8 |

|

|

|

|

|

1 – 2 кіріс

2 - статус

3- шығыс

4- КМОП тізбегіндегі 9 соңғы құрылғылар

5-түзетулер

6- істен шығулар

7 Зертханалық жұмыс. Шмит тригері

Жұмыстың мақсаты

– Шмитт триггерінің классикалық схемасында шығыс кернеуінің кіріс кернеуінен тәуелділігін алу және талдау;

– EWB бағдарламасында эмиттарлы байланысты екі транзисторда Шмитт триггерінің классикалық схемасымен жұмыс істеудегі жұмыс дағдыларын игеру;

– Анықтамалық әдебиеттермен Шмитт триггері бойынша жұмыс дағдыларын игеру.

7.1 Алдын ала дайындалу

7.1.1 Зертханалық жұмысты орындамас бұрын, ұсынылған әдебиеттер бойынша Шмитт триггері туралы теориялық мағлұматтарды оқып үйрену.

7.1.2 Зертхана жұмысына берілген тапсырмаларды және оған берілген әдістемелік көрсеткіштерді оқу.

7.1.3 Анықтама бойынша паспортты деректерді жазу және триггерлердің зерттелген типтері сипаттамаларын салу.

Регенеративті компаратор (Шмидт триггері) компьютерлік құрылғылар мен сандық схемалардағы бөгеуілдер салдарынан қате ауыстырып-қосуларды болдырмау үшін пайдаланылады. Бұндай түрдегі компаратор оң кері байланыстарды қолданады.

Қолданылған құралдар мен элементтер:

- PU-2000 орталық процессоры;

- ЕВ-220 баспа платасы;

- сандық әмбебап құралы;

- осциллограф.

7.2 Жұмыстық тапсырмалар

7.2.1 EWB бағдарламасында эмиттерлі байланыспен екі транзистордағы (VT1и VT2) Шмитт триггерінің классикалық cхемасы жұмысын жинау.

7.2.2 FG функционалдық генератордан кіріс сигналдарын зерттеу.

7.2.3 Триггердің қайта беріліс сипаттамасын алу.

7.2.4 Үшбұрышты формалы сигналдарын триггер кірісіне берудегі сипатты гистерезисті зерттеу.

7.2.5 Генераторды синусоидты тербеліс режіміне терістемеуші Шмитт триггерін іске асыра отырып, ауыстыру.

7.2.6 ШТ-ны жоғарыжиілікті бөгеуден қорғану үшін қолдану.

7.2.7 EWB бағдарламасын пайдалана отырып, МАСТЕР КИТ NS011 электронды күзет құрылғысында ШТ-ны қолдану мысалын көрсету.

7.2.8 Электронды блок cхемасын құру.

7.3 Жұмысты орындауға арналған әдістемелік көрсеткіштер

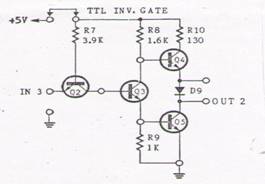

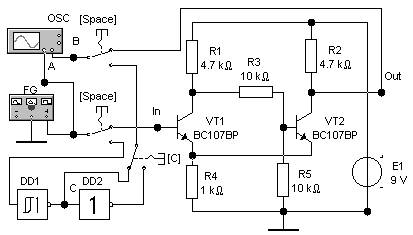

7.3.1 EWB бағдарламасында эмиттерлі байланыспен екі транзистордағы (VT1и VT2) Шмитт триггерінің классикалық Схемасы жұмысын 1-суреті бойынша құру (7.1 суретті қара).

7.1 суреті – Шмитт триггерінің классикалық схемасы

7.3.2 FG функционалды генератордан келетін кіріс сигналы In (база VT1) кірісіне және OSC осциллографтың А арнасына беріледі, ал шығысы Оut (коллектор VT2) шығысынан алынады және В арнасына беріледі.

7.3.3 Триггердің қайтаберіліс сипаттамасын алу үшін 7.2-суретте көрсетілген параметрлермен үшбұрышты формалы сигналдарын генерациялау режіміне қоямыз.

7.2 сурет

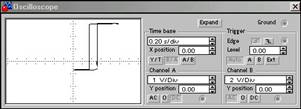

Осциллоскопта кірістен шығыс кернеуінің тәуелділігін алу үшін В/A типінің жайма режімін таңдаймыз (7.3 сурет).

7.3 сурет – B/A жаймасы режімін таңдау

Бұдан кейін салыстыру үшін типтік базалық логикалық элементтерде (DD1 және DD2) ШТ-ны модельдеу орындалатын болса, онда cхема [Space] және [C] кілттерімен құралдар коммутациясын қарастырады. Дәл осы жағдайда [Space] кілттері жоғарғы жағдайларда, ал [C] кілттері кез келген жағдайларда болуы қажет. Моделдеуді қосу арқылы экраннан сипатты гистерезис тұзағын көреміз (7.1 суретін қараңыз).

Әдебиет тізімі

1. Жолшараева Т.М., Рахимжанова З.М. Микроэлектроника. Шала өткізгішті аспаптар. Оқу құралы. 050704 – Есептеу техникасы және бағдарламалық қамту, 050702 – Автоматтандыру және басқару мамандықтары бойынша оқитын студенттерге арналған. 2009

2. Жолшараева Т.М., Схемотехника. Учебное пособие для студентов по специальности 5В0704 ВТиПО и для специальности 5В0719 РЭТ. 2010 .

3. Жолшараева Т.М., Электроника. Учебное пособие для студентов обучающихся по специаьности 5В0702 – Автоматизация и управение, 5В0719 – РЭТ, 5В0704 ВТиПО. 2010.

4. Шанаев О.Т.Цифрлық құрылғылар және микропроцессорлар. Оқу құралы 2009.

5. Шанаев О.Т. Микропроцессорлық жүйелер. Оқу құралы. 2009.

6. Шанаев О.Т. Бағдарламалы құрылымдар. Оқу құралы. 2011 .

7. Дегембаева У.К., Шайхин Б.М. Электроника және аналогтық құрылғылардың схемотехникасы. Оқу құралы 5В0719 – Радиотехника, электроника және телекоммуникация мамандықтары бойынша оқудың барлық түріндегі студенттер үшін. 2009 .

8. Дегембаева У.К., Шайхин Б.М. Электроника. Оқу құралы 5В0719 – Радиотехника, электроника және телекоммуникация және 5В0702 – Автоматтандыру және басқару мамандықтары бойынша оқудың барлық түріндегі студенттер үшін. 2009 .

9. Дегембаева У.К., Шайхин Б.М. Микроэлектроника. Жартылай өткізгішті аспаптар мен интегралдық микросұлбалар. 050704 – Есептеу техникасы және бағдарламалық қамту, 5В0719 - Радиотехника, электроника және телекоммуникация және 050702 – Автоматтандыру және басқару мамандықтары бойынша оқудың барлық түріндегі студенттер үшін. 2009.

10. Берикулы Әлімжан Техникалық электроника: Жоғарғы техникалық оқу орындары студенттеріне арналған оқулық. – Алматы: Білім, 1995. – 196 бет.

11. Берикулы Ә. ЭВМ және электроника. – Алматы, 1995. – 150 с.

12. Алексеев А.Н., Шайхин Б.М. “Электроника мен фотониканың физикалық негіздері”. Оқу құралы, АЭИ, Алматы, 1992 .

13. Лачин В.И., Савелов Н.С. Электроника: Учеб. пособие –

Ростов

н/Д: Феникс, 2009. – 704 с.

14. Опадчий Ю.Ф., Глудкин О.П., Гуров А.И. Аналоговая и цифровая электроника: Учебник для вузов. Под ред. О.П.Глудкина. – М.: Горячая линия‑Телеком. 2005, – 768 с.

15. Гусев В. Г., Гусев Ю. М. Электроника и микропроцессорная техника: Учеб.для вузов – М.: Высш. шк., 2006, – 800 с.

16. Гершунский Б.С. Основы электроники и микроэлектроники: Учебник для вузов – Киев: Высща школа, 1989. – 424 с.

17. Пейтон А.Дж, Волш.В. Аналоговая электроника на операционных усилителях. – М..: Бином, 1994. – 352 с.

18. Аналоговые и цифровые интегральные микросхемы. Справочное пособие /Под ред. С.В.Якубовского. – М.: Радио и связь, 1985. – 432с.

19. Павлов В.Н., Ногин В.Н. Схемотехника аналоговых электронных устройств. – М.: Радио и связь, 2005. – 320 с.

20. Фолкенберри Л. Применение операционных усилителей и линейных ИС. – М.: Мир, 1985. – 572 с.

21. Алексенко А.Г. Основы микросхемотехники. ‑3-е изд. – БИНОМ.Лаб.знаний, 2004. – 448 с.

22. Прянишников В.А. Электроника: Полный курс лекций. – СПб.: КОРОНА принт, Бином Пресс, 2006. – 416 с.

23. Жолшараева Т.М. Микроэлектроника. Полупроводниковые приборы: Учебное пособие. Алматы: АИЭС, 2006. – 79 с.

24. Жолшараева Т.М. Микроэлектроника. Интегральные микросхемы: Учебное пособие. Алматы: АИЭС, 2007. – 81 с.

25. Жолшараева Т.М. Электроника: Учебное пособие. Алматы: АИЭС, 2010.− 80 с.

26. Т.М.Жолшараева. Электроника. Методические указания к выполнению расчетно-графических работ для студентов всех форм обучения специальности 050702 – Автоматизация и управление. – Алматы: АИЭС, 2008. – 22 с.

27. Шанаев О.Т. Система моделирования Electronic Workbench / на казахском и русском языках. – Алматы: АИЭС, 2003.

28. Нефедов А.В. Транзисторы для бытовой, промышленной и спе-циальной аппаратуры: Справочное пособие. – М.: Солон-Пресс, 2006. – 600 с.

29. Транзисторы для аппаратуры широкого применения: Справочник. /Под редакцией Б.Л.Перельмана. – М.: Радио и связь, 1982. – 656 с.

2011 ж. негізгі жоспар, реті ___