Некоммерческое акционерное общество

АЛМАТИНСКИЙ УНИВЕРСИТЕТ ЭНЕРГЕТИКИ И СВЯЗИ

Кафедра электроники

СИГНАЛЬНЫЕ ПРОЦЕССОРЫ

Конспект лекций

для бакалавров специальности 5В071900 – Радиотехника, электроника и телекоммуникации

.

Алматы 2012

СОСТАВИТЕЛЬ: С.Н.Петрищенко. Сигнальные процессоры. Конспект лекций для бакалавров специальности 5В071900 – Радиотехника, электроника и телекоммуникации. - Алматы: АУЭС, 2012. – 38 с.

Приведены основные понятия и математические соотношения цифровой обработки сигналов, дана краткая характеристика цифровых фильтров, излагаются вопросы преобразования Фурье и квантования в цифровых системах, рассмотрены классификация и особенности сигнальных процессоров и их использование для решения типовых задач цифровой обработки сигналов, представлена архитектура сигнального процессора TMS320C50, проанализированы режимы его адресации, форматы представления данных, правила работы с симулятором, приведены состав и назначение платы обучающего комплекса, а также структура и назначение сигнальных процессоров подсерии TMS320C54x.

Курс лекций предназначен для бакалавров специальности 5В071900 – Радиотехника, электроника и телекоммуникации.

Ил. 13, табл. 1 , библиогр. 12 назв.

Рецензент: канд.тех.наук, проф. С.В.Коньшин.

Печатается по плану издания некоммерческого акционерного общества «Алматинский университет энергетики и связи» на 2012 г.

© НАО «Алматинский университет энергетики и связи» , 2012 г.

Лекция №1. Основные понятия и математические соотношения цифровой обработки сигналов

Содержание лекции: цифровая обработка сигналов и сигнальные процессоры, дискретные сигналы, нормирование, z – преобразование, его основные свойства, спектр дискретных сигналов.

Цель лекции: ознакомиться с направлением развития цифровой обработки сигналов, изучить типовые дискретные сигналы, приемы нормирования дискретных сигналов, методы z – преобразования и преобразования Фурье.

Цифровая обработка сигналов (ЦОС) в основном базируется на применении сигнальных процессоров (СП) для обработки типовых задач в реальном масштабе времени, применяемых в системах телекоммуникаций (включая глобальную сеть Internet), управления, мультимедиа, медицины и многих других.

Цифровые системы по сравнению с аналоговыми обладают рядом таких преимуществ, как высокая степень микроминиатюризации аппаратуры, высокая точность, помехозащищенность и стабильность характеристик.

ЦОС имеет дело с цифровыми сигналами, происходящими из

дискретных сигналов, которые дискретны по времени и непрерывны по состоянию.

Они описываются решетчатой функцией ![]() , где

, где ![]() - номер отсчета 0,1,2,3…, интервал Т

– период дискретизации, а обратная величина Т - частота дискретизации

- номер отсчета 0,1,2,3…, интервал Т

– период дискретизации, а обратная величина Т - частота дискретизации ![]() Цифровые сигналы в

отличии от дискретных сигналов дискретны не только по времени, но и по

состоянию, они могут принимать только конечное число значений из некоторого

конечного интервала. Эти значения называются уровнями квантования, а

соответствующие функции – квантованными.

Цифровые сигналы в

отличии от дискретных сигналов дискретны не только по времени, но и по

состоянию, они могут принимать только конечное число значений из некоторого

конечного интервала. Эти значения называются уровнями квантования, а

соответствующие функции – квантованными.

При анализе дискретных сигналов удобно пользоваться

нормированным временем ![]() Таким образом, номер отсчета

Таким образом, номер отсчета ![]() дискретного сигнала

может интерпретироваться как нормированное время.

дискретного сигнала

может интерпретироваться как нормированное время.

При изучении цифровых цепей в качестве испытательных воздействий чаще других используются два дискретных сигнала:

1) цифровой единичный импульс, который показан на рисунке 1,а и математически представлен соотношением

где ![]()

2) цифровой единичный скачок, показан на рисунке 1,б и представлен математическим соотношением

где

![]()

![]()

![]()

![]()

Рисунок 1

К типовым дискретным сигналам относятся также экспонента, гармонический сигнал и комплексный гармонический сигнал [ 1 ].

По теореме Котельникова максимальная частота

аналогового сигнала ![]() не

должна превышать половины частоты дискретизации

не

должна превышать половины частоты дискретизации ![]() , поэтому в частотной области все

дискретные сигналы целесообразно рассматривать в диапазоне

, поэтому в частотной области все

дискретные сигналы целесообразно рассматривать в диапазоне ![]() , где

, где ![]() - частота Найквиста. Это позволяет

ввести понятие нормированной частоты

- частота Найквиста. Это позволяет

ввести понятие нормированной частоты ![]() где

где ![]() - текущая частота. Тогда на частоте

Найквиста

- текущая частота. Тогда на частоте

Найквиста ![]() . Таким

образом, дискретный сигнал можно рассматривать в основном частотном диапазоне

. Таким

образом, дискретный сигнал можно рассматривать в основном частотном диапазоне ![]() .

.

Для нормированной круговой частоты ![]() , то есть основная

полоса частот соответствует области

, то есть основная

полоса частот соответствует области ![]()

Полезным методом описания дискретных систем является ![]() - преобразование,

которое оказывается наглядной и удобной формой представления процессов,

протекающих при цифровой обработке.

- преобразование,

которое оказывается наглядной и удобной формой представления процессов,

протекающих при цифровой обработке.

Прямое ![]() - преобразование определяет

- преобразование определяет ![]() - образ дискретной

последовательности

- образ дискретной

последовательности ![]() следующим

соотношением

следующим

соотношением

![]() .

(1.1)

.

(1.1)

Дискретный сигнал ![]() называется оригиналом, а функция

называется оригиналом, а функция ![]() - изображением (Z–образ).

Аргумент

- изображением (Z–образ).

Аргумент ![]() функции

функции

![]() является

комплексной величиной

является

комплексной величиной ![]() или

в полярных координатах

или

в полярных координатах ![]() где

где ![]() а

а ![]() . Комплексная функция

F(z)

определена лишь для тех значений

. Комплексная функция

F(z)

определена лишь для тех значений ![]() , при которых ряд (1.1)

сходится. Условием сходимости ряда (1.1) является

, при которых ряд (1.1)

сходится. Условием сходимости ряда (1.1) является

![]() < ∞. (1.2)

< ∞. (1.2)

Обратное Z–преобразование решает задачу восстановления оригинала по известному изображению, используя следующее соотношение

![]() (1.3)

(1.3)

где С – контур сходимости ![]() охватывающий начало координат

охватывающий начало координат ![]() - плоскости.

- плоскости.

Такой интеграл решить сложно, поэтому существуют более

простые способы нахождения обратного ![]() - преобразования: с использованием таблицы

соответствия, на основании теоремы Коши о вычетах или разложением изображения

на простые дроби [ 1 ].

- преобразования: с использованием таблицы

соответствия, на основании теоремы Коши о вычетах или разложением изображения

на простые дроби [ 1 ].

Основные свойства ![]() - преобразования сводятся к следующему:

- преобразования сводятся к следующему:

1)

Линейность. Если ![]() и

и ![]() - решетчатые функции, а

- решетчатые функции, а ![]() и

и ![]() - постоянные действительные коэффициенты,

то

- постоянные действительные коэффициенты,

то

![]() (1.4)

(1.4)

2) Сдвиг последовательности (задержка). Если

последовательность ![]() имеет

имеет

![]() -

преобразование

-

преобразование ![]() ,

то задержанная на

,

то задержанная на ![]() интервалов

последовательность

интервалов

последовательность ![]()

![]() , имеет

, имеет ![]() - преобразование

- преобразование

![]()

![]() (1.5)

(1.5)

3) Свертка последовательностей. Если

последовательности ![]() и

и

![]() имеют

имеют ![]() - преобразования

- преобразования ![]() и

и ![]() , то последовательность

, то последовательность ![]() , представляющая собой

свертку исходных последовательностей

, представляющая собой

свертку исходных последовательностей ![]() , имеет

, имеет ![]() - преобразование

- преобразование ![]()

Для описания дискретных сигналов в частотной области

используется спектр, который связан с дискретным сигналом парой преобразований

Фурье. Спектром ![]() или

фурье-изображением дискретного сигнала называют прямое преобразование Фурье

дискретной последовательности

или

фурье-изображением дискретного сигнала называют прямое преобразование Фурье

дискретной последовательности ![]()

, (1.6)

, (1.6)

где ![]() - оригинал (дискретная последовательность).

- оригинал (дискретная последовательность).

Обратное преобразование Фурье для дискретной последовательности

. (1.7)

. (1.7)

При сравнении формул (1.6) и (1.1) можно увидеть, что преобразование Фурье представляет собой частный случай z – преобразования:

![]() .

.

Свойства спектра дискретного сигнала следуют из свойств z-преобразования [ 2 ].

Лекция №2. Анализ основных направлений цифровой обработки сигналов

Содержание лекции: классификация цифровых фильтров, их математическое описание, спектральный анализ.

Цель лекции: ознакомиться с классификацией и математическим описанием рекурсивных и нерекурсивных цифровых фильтров и методами спектрального анализа.

К одному из основных направлений цифровой обработки сигналов (ЦОС) относится цифровая фильтрация. Цифровая фильтрация – это процесс преобразования цифровых сигналов с целью выделения и/или подавления определенных частот этих сигналов, а устройство, выполняющее фильтрацию, называется фильтром. На рисунке 2 представлены классы и типы цифровых фильтров (ЦФ).

Рисунок 2

Из рисунка 2 видно, что в области цифровой фильтрации разработчик систем ЦОС имеет дело с реализацией двух классов фильтров:

- фильтры с бесконечной импульсной характеристикой (БИХ-фильтры), то есть с импульсной характеристикой, имеющей бесконечную длину во временной области; такой фильтр называют еще рекурсивным из-за наличия обратной связи;

- фильтры с конечной импульсной характеристикой (КИХ-фильтр), то

есть с импульсной характеристикой, ограниченной по времени ( с какого-то момента времени она становится равной нулю); из-за отсутствия обратной связи такие фильтры называют нерекурсивными.

Из рисунка 2 видно, что фильтры могут быть фильтрами низкой частоты (НЧ), высокой частоты (ВЧ), полосовыми фильтрами (ПФ), режекторными фильтрами, а из нерекурсивных фильтров (НРФ) можно также построить амплитудные корректоры (АК), преобразователи Гильберта и дифференциаторы.

Оба

класса фильтров относятся к классу линейных систем с постоянными параметрами, в

которых входная![]() и выходная

и выходная ![]() последовательности связаны отношениями типа

свертки. Если обозначить через

последовательности связаны отношениями типа

свертки. Если обозначить через ![]() отклик системы на единичный импульс, то получим

свертку вида:

отклик системы на единичный импульс, то получим

свертку вида:

(2.1)

(2.1)

где

![]() - отсчеты входного и выходного сигналов;

- отсчеты входного и выходного сигналов;

h(k) – импульсная характеристика;

x(n - k) - входной отсчет, задержанный на k интервалов дискретизации.

Цифровые фильтры полностью описываются во временной области разностными уравнениями, а в z-области – передаточными функциями.

Рекурсивные фильтры представляют собой системы с обратной связью и описываются разностными уравнениями вида

(2.2)

(2.2)

где bi и ak – вещественные коэффициенты, причем хотя бы один ak ≠ 0;

x(n-i) - входные отсчеты, задержанные на ![]() периодов дискретизации

периодов дискретизации ![]() ;

;

y(n-k)-выходные отсчеты, задержанные на ![]() периодов дискретизации

T;

периодов дискретизации

T;

N и M – постоянные целые числа, причем М ≥ N.

Нерекурсивные фильтры представляют собой системы без обратной связи и описываются разностными уравнениями вида

![]() ,

(2.3)

,

(2.3)

где N - число коэффициентов;

N-1 – порядок фильтра.

Необходимо отметить, что коэффициенты ak передаточной функции рекурсивного фильтра по абсолютной величине равны коэффициентам разностного уравнения, но противоположны по знаку, а коэффициенты bi разностного уравнения и передаточной функции нерекурсивного фильтра полностью совпадают и представляют собой отсчеты его импульсной характеристики.

Таким образом, для построения систем цифровой фильтрации требуется эффективная реализация соотношения типа дискретной свертки (2.1), которая раскладывается на операции умножения и накапливающего суммирования, а также операции задержки, что учитывается в архитектуре сигнальных процессоров при реализации процессов цифровой фильтрации.

В ряде задач цифровой обработки необходимо оценить

параметры спектра сигнала, то есть выполнить спектральный анализ. Исходными

данными для обработки являются ![]() отсчетов сигнала

отсчетов сигнала ![]() . Для исследования частотного

состава этой последовательности ее нужно преобразовать, используя Фурье-анализ.

С аналитической точки зрения Фурье-анализ позволяет установить связь между

сигналом во временной области и его спектром в частотной области. При этом

вычисляются компоненты спектра на основе дискретного преобразования Фурье

(ДПФ).

. Для исследования частотного

состава этой последовательности ее нужно преобразовать, используя Фурье-анализ.

С аналитической точки зрения Фурье-анализ позволяет установить связь между

сигналом во временной области и его спектром в частотной области. При этом

вычисляются компоненты спектра на основе дискретного преобразования Фурье

(ДПФ).

ДПФ – это пара взаимно однозначных преобразований, которые в компактном виде выглядят следующим образом:

1)

прямое![]()

; (2.4)

; (2.4)

2)

обратное  , (2.5)

, (2.5)

где ![]() - длина исходной последовательности;

- длина исходной последовательности;

![]() - количество частотных отсчетов;

- количество частотных отсчетов;

![]() - количество временных отсчетов;

- количество временных отсчетов;

![]() - поворачивающий множитель (весовая,

периодическая функция), получивший свое название потому, что аргумент экспоненты

- поворачивающий множитель (весовая,

периодическая функция), получивший свое название потому, что аргумент экспоненты

![]() отображает

угол поворота на единичной окружности комплексной

z-плоскости.

отображает

угол поворота на единичной окружности комплексной

z-плоскости.

Используя свойство периодичности поворачивающего

множителя ![]() ,

можно уменьшить количество арифметических операций для вычисления ДПФ.

Существует целый набор алгоритмов для быстрого ДПФ: с основанием 2, с

основанием 4, Виноградова и другие.

,

можно уменьшить количество арифметических операций для вычисления ДПФ.

Существует целый набор алгоритмов для быстрого ДПФ: с основанием 2, с

основанием 4, Виноградова и другие.

Первый алгоритм был опубликован в 1965 году в США и назван по имени его создателей Кули-Тьюки. Существуют две версии этого алгоритма:

1)

с прореживанием по времени, при

реализации которого требуется перестановка (прореживание) отсчетов ![]() входной

последовательности;

входной

последовательности;

2)

с прореживанием по частоте, при

реализации которого требуется перестановка (прореживание) отсчетов ![]() выходной

последовательности.

выходной

последовательности.

Лекция №3. Квантование в цифровых системах

Содержание лекции: способы квантования чисел, источники ошибок квантования, шум квантования входного сигнала, собственный и полный выходной шум системы, шумовые характеристики.

Цель лекции: изучить способы квантования чисел, уметь оценивать шум квантования входного сигнала, собственный и полный шум цифровой системы и ее характеристики.

В цифровых

системах обработки сигналов отсчеты обрабатываемого сигнала

![]() ,

,![]() ,

коэффициенты разностного уравнения или передаточных функций, а также результаты

выполнения арифметических операций в сумматорах и умножителях представляются

b-разрядными двоичными числами в

соответствии с разрядностью регистров, ячеек памяти и операционных устройств.

Такое приближенное представление чисел называют квантованием. Квантование –

нелинейная операция, поэтому при ее введении в алгоритм обработки сигнала,

который описывается линейным дискретным уравнением, возникают ошибки в

реализации алгоритма. Такие ошибки называются ошибками квантования.

,

коэффициенты разностного уравнения или передаточных функций, а также результаты

выполнения арифметических операций в сумматорах и умножителях представляются

b-разрядными двоичными числами в

соответствии с разрядностью регистров, ячеек памяти и операционных устройств.

Такое приближенное представление чисел называют квантованием. Квантование –

нелинейная операция, поэтому при ее введении в алгоритм обработки сигнала,

который описывается линейным дискретным уравнением, возникают ошибки в

реализации алгоритма. Такие ошибки называются ошибками квантования.

Квантование

числа – это его представление с помощью конечного количества (b) значащих разрядов. С учетом

знакового разряда разрядность числа определяется как ![]() . Нелинейность операции

квантования вносит в представление квантуемого числа А ошибку

. Нелинейность операции

квантования вносит в представление квантуемого числа А ошибку

![]() , (3.1)

, (3.1)

где А – двоичное число до квантования;

F(A) – число после квантования.

Шагом квантования

![]() называется расстояние между двумя соседними

уровнями квантования при

называется расстояние между двумя соседними

уровнями квантования при

![]() Шаг квантования определяется весом младшего значащего

разряда:

Шаг квантования определяется весом младшего значащего

разряда: ![]() .

.

В цифровой обработке рассматриваются только числа, по модулю не превосходящие единицу

![]() . (3.2)

. (3.2)

При квантовании используются два способа приближения чисел: округление и

усечение.

В случае

округления выбирается ближайший уровень квантования, при этом исходное

k-разрядное число (

k >

b ) заменяется

до ближайшего

b-разрядного и

ошибка округления

![]() не превосходит половины шага

квантования

не превосходит половины шага

квантования

.

(3.3)

.

(3.3)

При усечении

k-разрядного числа до

b значащих разрядов (k >

b) младшие (k

-

b) разряды

исходного числа отбрасываются. Ошибка усечения

![]() меньше шага квантования, но больше ошибки

округления

меньше шага квантования, но больше ошибки

округления

![]() <

<![]() .

(3.4)

.

(3.4)

В связи с этим в аналого-цифровых преобразователях и в цифровых процессорах обработки сигналов обычно применяется округление.

Источниками ошибок квантования являются:

а) аналого-цифровое преобразование (АЦП), при котором квантуются дискретные сигналы;

б)

арифметические

операции с цифровым сигналом

![]() ;

;

в) квантование коэффициентов цифровой системы.

В дальнейшем вместо термина «ошибка квантования» будет использоваться термин «шум квантования».

Линейные модели

процессов аналого-цифрового преобразования и умножения (с конечным числом

разрядов) и шумом ![]() идентичны, их свойства

описываются одинаковыми выражениями для математического ожидания и

дисперсии ошибок квантования,

поэтому

идентичны, их свойства

описываются одинаковыми выражениями для математического ожидания и

дисперсии ошибок квантования,

поэтому

![]() ;

;

, (3.5)

, (3.5)

где

![]() и

и

![]() - шумы АЦП и умножителя

соответственно.

- шумы АЦП и умножителя

соответственно.

Для оценки влияния квантования входного сигнала (шум АЦП) на выходной шум цифровой цепи полагаем, что коэффициенты и арифметические операции реализуются точно. Выходной шум, как реакция дискретной цепи, имеющей импульсную характеристику h( к ), на шум АЦП определяется по формуле

.

(3.6)

.

(3.6)

Дисперсия составляющей выходного шума, обусловленной АЦП

(3.7)

(3.7)

Шум на выходе цифровой цепи имеет еще одну составляющую, обусловленную квантованием результатов умножения (собственный шум).

Дисперсия шума квантования на выходе цифровой цепи первого порядка определяются с учетом этой составляющей

(3.8)

(3.8)

где

![]() -

максимальное значение ошибки составляющей выходного

собственного шума;

-

максимальное значение ошибки составляющей выходного

собственного шума;

![]() - дисперсия

составляющей выходного собственного шума;

- дисперсия

составляющей выходного собственного шума;

h(k)- импульсная характеристика цепи первого порядка;

L - количество умножителей.

Дисперсия выходного шума звена второго порядка для всех i = 1,2,…,L определяется следующей формулой

(3.9)

(3.9)

где ![]() - импульсная характеристика цепи второго

порядка.

- импульсная характеристика цепи второго

порядка.

![]() - импульсная характеристика от

выхода

i – го умножителя до выхода цепи.

- импульсная характеристика от

выхода

i – го умножителя до выхода цепи.

Важными шумовыми характеристиками цифровой системы являются отношение сигнал/шум и ее динамический диапазон.

Отношение сигнал/шум

![]() – это отношение мощности выходного сигнала системы

– это отношение мощности выходного сигнала системы

![]() к мощности шума на выходе системы

к мощности шума на выходе системы

![]()

![]() [дБ].

(3.10)

[дБ].

(3.10)

Динамический

диапазон ![]() – это отношение максимальной

амплитуды

– это отношение максимальной

амплитуды ![]() к минимальной амплитуде

к минимальной амплитуде ![]() входного сигнала, при

которой обеспечивается определенное отношение

входного сигнала, при

которой обеспечивается определенное отношение ![]() сигнала на выходе системы

сигнала на выходе системы

![]() [дБ],

(3.11)

[дБ],

(3.11)

при

![]() [дБ],

(3.12)

[дБ],

(3.12)

где

![]() - мощность выходного сигнала на нижней

границе динамического диапазона (при амплитуде входного сигнала

- мощность выходного сигнала на нижней

границе динамического диапазона (при амплитуде входного сигнала ![]() ).

).

Динамический диапазон следует контролировать введением коэффициентов масштабирования.

Лекция №4. Архитектурные особенности сигнальных процессоров

Содержание лекции: назначение и типы сигнальных процессоров, особенности их архитектуры , методы параллельной обработки.

Цель лекции: изучить типы цифровых сигнальных процессоров, научиться понимать и правильно использовать ключевые архитектурные особенности, а также современные методы параллельной обработки сигналов.

Сигнальные процессоры (СП) – это устройства, предназначенные для формирования, преобразования и обработки сигналов информационных и связных систем и сетей в реальном времени. Главная их особенность – обработка больших массивов данных.

Сигнальные процессоры могут выполняться в виде специализированных (непрограммируемых) сверхбольших интегральных схем (СБИС) или как универсальные СБИС. К специализированным процессорам относятся, например, процессор быстрого преобразования Фурье (БПФ), синтезатор частот, кодер и т.д. К универсальным процессорам относятся:

1) логические схемы (ПЛИС – программируемые логические интегральные схемы);

2) программируемые цифровые сигнальные процессоры, иностранная аббревиатура которых DSP ( Digital Signal Processor), а отечественная – СП;

3) транспьютеры.

Преимуществом универсальных процессоров перед специализированными является возможность реализации на них разнообразных устройств при относительно невысокой цене кристалла.

К СП по архитектуре и производительности наиболее близки транспьютеры, позволяющие производить обработку больших информационных массивов. Транспьютер имеет процессор с архитектурой RISC ( Reduced Instruction Set Computer), т.е. ядро с сокращенным набором команд, быстродействием более миллиона команд в секунду (MIPS) и аппаратными средствами, обеспечивающими параллельные вычисления. Транспьютер содержит четыре высокоскоростных канала связи, которые служат для обмена сообщениями с другими транспьютерами. Эти четыре канала позволяют соединять транспьютеры между собой, организуя различные транспьютерные сети со сложными соединениями.

ПЛИС проще и дешевле СП и транспьютеров, но требуют много периферийных устройств и устройств ввода-вывода.

Наибольшее распространение получили программируемые СП, которые явились результатом развития микропроцессоров, но отличаются от них архитектурой, приспособленной для решения задач цифровой обработки сигналов. Основные требования, предъявляемые к СП:

1) высокое быстродействие;

2) высокая производительность при реализации алгоритмов с большим объемом вычислений в реальном времени.

Эти требования выполняются, благодаря использованию следующих архитектурных особенностей СП:

1) применение гарвардской архитектуры;

2) использование конвейерного режима работы;

3) наличие специального устройства умножения;

4) введение спецкоманд;

5) организация короткого командного цикла.

Гарвардская архитектура позволяет поднять быстродействие и гибкость использования. В классическом варианте она предполагает хранение программ и данных в разных запоминающих устройствах, что позволяет совмещать во времени выборку и исполнение команд. Модифицированная гарвардская архитектура допускает обмен между памятью программ и памятью данных, что расширяет возможности процессора, при этом отпадает необходимость в отдельном постоянном запоминающем устройстве (ПЗУ) для хранения коэффициентов.

Традиционные микропроцессоры имеют неймановскую архитектуру, при которой происходит пошаговое, потактно-последовательное выполнение команд, при этом данные и команды передаются по одной шине.

Примеры гарвардской и неймановской архитектур представлены на рисунке 4.

|

|||

|

|||

Рисунок 4

Конвейерный режим используется для сокращения длительности командного цикла. На рисунке 5 показан пример 3-х каскадного конвейерного режима.

N N+1 N+2

Рисунок 5

Из рисунка 5 видно, что в ходе N-го цикла процессор может одновременно извлекать из памяти N-ю команду, декодировать (N - 1)-ю команду и в то же время выполнять (N - 2)-ю команду.

Операция умножения реализуется в СП аппаратным умножителем-накопителем. Аппаратный умножитель позволяет выполнять операцию умножения за один командный цикл. Например, в процессоре с фиксированной запятой такой умножитель за один такт (обычно 25 нс) принимает два 16-битовых дробных числа, представленных в форме дополнения до двух, и вычисляет их 32-битное произведение.

За счет применения спецкоманд число командных циклов можно резко сократить. Например, команда LTD позволяет выполнить за один цикл три команды: загрузки (LT), задержки (DMOV) и сложения (APAC), а команда MACD позволяет за один командный цикл выполнить четыре команды: загрузки (LT), задержки (DMOV), сложения (APAC) и умножения (MPY).

В таблице 1 представлены временные циклы некоторых СП, выпускаемых американской фирмой Texas Instruments серии TMS320.

Т а б л и ц а 1

|

Процессор |

Время цикла, нс |

|

TMS320C10 |

200 |

|

TMS320C25 |

125 |

|

TMS320C30 |

75 |

|

TMS320C541 |

25 |

|

TMS320C67* |

6 |

|

TMS320C6202 |

4 |

Малость командного цикла делает СП удобным средством решения многих прикладных задач, например, в системах обработки телевизионных изображений. Для повышения вычислительной эффективности СП используются следующие их новейшие архитектуры:

1) SIMD (single instruction, multiple data – одна команда, много данных); в процессорах с такой архитектурой имеется несколько трактов передачи данных и операционных блоков, поэтому команда может передаваться нескольким операционным блокам для обработки блоков данных одновременно, увеличивая число операций, выполняемых за один такт;

2) VLIW (very large instruction word – командные слова сверхбольшой длины); эти слова состоят из нескольких коротких команд, для выполнения которых за один такт требуется несколько операционных блоков, функционирующих параллельно;

3) суперскалярная обработка позволяет выполнять несколько команд за один такт при использовании параллелизма на уровне команд.

Лекция №5. Классификация и особенности цифровых сигнальных процессоров с фиксированной точкой

Содержание лекции: поколения сигнальных процессоров с фиксированной точкой фирмы Texas Instruments, их особенности.

Цель лекции: изучить особенности архитектуры четырех поколений цифровых сигнальных процессоров, оценить их возможности в различных областях применения.

В современных сигнальных процессорах арифметические операции выполняются с использованием арифметики с фиксированной или плавающей точками.

В цифровой обработке сигналов более распространена арифметика с фиксированной точкой, так как ей сопутствует быстрая и недорогая реализация. Однако, при такой форме представления чисел их диапазон ограничен, а итоговая система подвержена проблемам переполнения, поэтому необходимо вводить масштабирование обрабатываемых данных.

Процессоры с плавающей точкой работают в более широком динамическом диапазоне при более точном представлении данных, но их архитектура значительно сложнее, поэтому они имеют большие размеры кристалла и стоимость.

Рассмотрим архитектуру четырех поколений типовых цифровых сигнальных процессоров с фиксированной запятой семейства TMS320, производимых фирмой Texas Instruments (TI). Такое деление процессоров на четыре поколения основано на исторических причинах, архитектурных особенностях и вычислительной эффективности [ 4 ].

К первому поколению ЦСП относится семейство TMS320C1x. Характерным представителем этого семейства является 16-разрядный процессор TMS320C10, который способен выполнять 5 млн.операций в секунду при длительности командного цикла не более 200 нс. В процессоре реализована арифметика с фиксированной запятой в двоичном дополнительном коде. Процессор адресует восемь 16-разрядных портов ввода и восемь 16-разрядных портов вывода данных [ 9 ].

Для достижения высокого быстродействия и гибкости в основу процессора положена модифицированная гарвардская архитектура, что позволяет не только полностью совмещать во времени процессы выборки и выполнения команд, но и осуществлять передачи между программной памятью и памятью данных.

Память программ реализуется на масочном постоянном запоминающем устройстве (ПЗУ) объемом 1536×16 разрядов и может размещаться как внутри кристалла (процессор TMS320C10), так и вне его (процессор TMS32010). Имеется возможность расширения внешней памяти до общего объема 4096×16 разрядов с сохранением максимального быстродействия.

АЛУ процессора предназначено для выполнения операций сложения, вычитания и логических операций над 32-разрядными словами. Один из операндов берется из аккумулятора, второй поступает либо из регистра (Р) произведения умножителя, либо с внутренней шины данных с возможностью последовательного сдвига влево на 0-15 разрядов. Результат операции заносится в аккумулятор. Параллельное сдвигающее устройство (сдвигатель (0,1,4) используется при записи старших разрядов аккумулятора в память данных для масштабирования разультата произведения.

Через мультиплексор процессор может использовать один из двух способов адресации: прямой или косвенный. При первом способе адрес ячейки памяти формируется из семи младших разрядов слова команды и одного разряда, выдаваемого указателем страницы (DP). При этом память данных делится на станицу 0 (DP = 0) и страницу 1 (DP = 1). В первом случае обслуживаются ячейки от 0 до 127, во втором – от 128 до 144.

В режиме косвенной адресации в качестве адреса памяти данных используются восемь младших разрядов одного из вспомогательных регистров (ARO или AR1). Текущий вспомогательный регистр выбирается с помощью указателя вспомогательного регистра (ARP).

В состав блока управления процессором входят устройство управления, программный счетчик и стековая память с глубиной вложения не более четырех. Программный счетчик и стек предоставляют пользователю организовать переходы, вызовы подпрограмм и прерывания.

Типичным представителем процессоров ЦОС второго поколения является семейство TMS320C5х со временем цикла не более 25 нс. Процессоры ЦОС первого и второго поколений совместимы по системе команд и имеют много общего архитектурно, однако процессоры второго поколения обладают большими функциональными возможностями и меньшим энергопотреблением. Кроме того, они имеют больший объем встроенной памяти и много специальных команд для поддержки эффективного выполнения алгоритмов ЦОС. Например, в число специальных команд входит команда умножения и накопления со сдвигом данных (MACD), которая при объединении ее с командой повтора (RPT) позволяет реализовать КИХ-фильтр со значительной экономией времени. Возможность адресации с инвертированием битов полезна при быстром преобразовании Фурье (БПФ). В результате вычислительная производительность процессоров второго поколения в 4-6 раз выше производительности процессоров первого поколения.

Процессоры ЦОС с фиксированной запятой третьего поколения , которые характеризуются семейством TMS320C54х, являются улучшением процессоров предыдущего поколения в сторону увеличения их производительности (66 млн. команд в секунду) за счет более эффективного использования встроенных ресурсов. По сравнению с процессорами второго поколения, процессоры третьего поколения отличаются тремя внутренними шинами данных и одной шиной программ. Такая внутренняя организация процессора позволяет ему обеспечить высокую степень параллельности выполнения команд. Этому семейству свойственна высокоспециализированная система команд и увеличенный объем памяти.

На рисунке 6 показана упрощенная архитектура процессора ЦОС с фиксированной запятой третьего поколения семейства TMS320C54х.

|

Рисунок 6

Большинство ЦСП с фиксированной запятой третьего поколения применяют в цифровой связи и цифровом аудио. За счет использования специальных команд такие процессоры можно применять для реализации алгоритмов адаптивной фильтрации и для поддержки декодирования Витерби. Кроме того, эти процессоры имеют низкий расход энергии.

Процессоры ЦОС с фиксированной запятой четвертого поколения (семейство TMS320C62х) основаны на архитектуре VLIW.

Процессор ядра имеет два независимых арифметических тракта, в каждом из которых четыре операционных блока: логическое устройство, схема сдвига/логическое устройство, умножитель и устройство адреса данных. Обычно процессор извлекает из памяти восемь 32-битовых команд за один раз, поэтому длина слова получается равной 256 бит (сверхбольшая длина). При наличии в сумме восьми операционных блоков, по четыре в каждом тракте, процессор может выполнять до восьми команд параллельно в одном такте. Кроме значительной программной памяти, процессор имеет двухуровневую кэш-память: 4 Кбайт уровня 1 и 64 Кбайт уровня 2.

Высокая производительность процессоров семейства TMS320C62х (1,6 млрд.операций в секунду) и наличие широкого набора инструментальных средств позволяют использовать их для экономичного решения задач, требующих высокопроизводительной обработки сигналов. Области применения процессоров: медицинская диагностика, цифровые абонентские линии, модемы удаленного доступа и другие приложения [ 6 ].

Лекция №6. Архитектура сигнального процессора TMS320C50

Содержание лекции: краткая характеристика архитектуры сигнального процессора TMS320C50.

Цель лекции: изучить особенности архитектуры сигнального процессора TMS320С50.

TMS320С5х - сигнальные процессоры, которые базируются на модифицированной Гарвардской архитектуре. В этой архитектуре используются два пространства памяти - для программ и для данных со своими шинами адреса и данных. По шине данных памяти программ из программной памяти пересылаются коды команд и непосредственные операнды. По шине данных памяти данных пересылаются данные от разнообразных модулей процессора в память данных и наоборот. Имеются команды обмена данными между памятью программ и памятью данных.

В процессорах TMS320C5х поддерживается высокий уровень параллелизма. Так, пока данные обрабатываются в арифметико-логическом устройстве (ALU), в арифметическом устройстве вспомогательных регистров может производиться инкремент или декремент содержимого этих регистров.

Структурная схема процессора TMS320C50 представлена на рисунке 7, из которой видно, что процессор выполняет арифметические команды, используя 32-х разрядные ALU и аккумулятор (ACC). ALU - универсальный арифметический модуль, который оперирует 16-ти разрядными операндами (непосредственными или из памяти) или/и 32-х разрядными из умножителя или аккумулятора. Аккумулятор используется для хранения результатов, поступающих из ALU, а также для ввода второго операнда в ALU. 32-х разрядный ACC разделен на старшее слово (ACCH) - биты 31:16 и младшее – (ACCL) c битами 15:0. Для быстрого временного сохранения содержимого аккумулятора имеется 32-х разрядный буфер аккумулятора (ACCB).

В дополнение к основному ALU имеется параллельный логический модуль (PLU), который выполняет логические операции над данными, не оказывая влияния на содержимое аккумулятора. PLU упрощает поразрядную установку, очистку и тестирование, требуемое при управлении и при операциях над регистрами состояния.

Аппаратный умножитель выполняет перемножение двух 16-ти разрядных слов с получением 32-х разрядного результата за один командный цикл. Умножитель состоит из трех элементов: собственно умножителя (multiplaer), регистра результата PREG (product register) и временного регистра TREG0. 16-ти разрядный TREG0 хранит множитель, 32-х разрядный PREG содержит результат умножения. В зависимости от используемых команд значение множителя может быть загружено из памяти данных, памяти программ, или непосредственно из команды.

Рисунок 7

Масштабирующий сдвигатель (Prescaler) имеет 16-ти разрядный вход, соединенный с шиной данных, и 32-х разрядный выход, соединенный со входом ALU. Prescaler производит левый сдвиг входных данных от 0 до 16 бит. Сдвиг может задаваться в команде или с помощью указателя динамического сдвига (регистра ТREG1). Младшие разряды при сдвиге заполняются нулями, а старшие - в зависимости от состояния бита SXM в регистре состояния ST1, или нулями (SXM=0), или расширением знака.

Процессор имеет и другие сдвигатели: сдвигатель масштабирования результата (Post – Scaler) для левого сдвига от 0 до 7 бит результата из CALU и сдвигатель результата ((P – Scaler) для сдвига влево на 0, 1 или 4 бита или сдвига вправо на 6 разрядов для предотвращения переполнения.

Регистровый файл (AUXREGS), состоящий из восьми вспомогательных регистров (8x16) и индексного регистра (INDR), используется для формирования адреса при косвенной адресации. Для адресации к вспомогательным регистрам служит указатель вспомогательных регистров (ARP). Арифметическое устройство (ARAU) вместе с регистровым файлом предназначено для генерации адреса. Обычно вспомогательные регистры используются для хранения адреса, а INDR содержит смещение.

Восьмиуровневый аппаратный стек (stack) служит для хранения содержимого программного счетчика (PC) при выполнении процедур и подпрограмм обработки прерываний. При прерываниях регистры (ACC, ARCR, INDX, PMST, PREG, ST0, ST1, TREGs) помещаются в одноуровневый стек и извлекаются из него при возврате из прерывания.

Встроенная в кристалл процессора TMS320C50 память (Program Memory) состоит из трех видов:

1) масочно – программируемая память программ ROM, для изменения режима работы которой предусмотрен бит управления (MP/MC);

2) память данных или программ/данных SARAM, которая предусматривает выполнение одной операции чтения/записи в полном машинном цикле, состоит из независимых блоков по 2К или по 1К слов; конфигурация памяти изменяется битами OVLY и RAM в регистре PMST;

3) память данных DARAM предусматривает выполнение одной операции чтения или записи в полном машинном цикле без конфликтов на внутренней шине данных; конфигурация памяти изменяется с помощью бита конфигурации (CNF) в регистре состояния (ST1).

В качестве периферийного устройства в кристалл процессора встроен таймер/счетчик T/C, который представляет собой 16 – разрядный вычитающий счетчик. При достижении нулевого значения генерируется прерывание TINT и формируется импульс на выходе TOUT. Таймер управляется программно и может быть остановлен, перезапущен, сброшен или запрещен.

Лекция №7. Режимы адресации памяти сигнального процессора TMS320C50

Содержание лекции: основные режимы адресации памяти в процессорах семейства TMS320C5x.

Цель лекции: изучить четыре основных режима адресации памяти, используемые в процессоре TMS320C50.

В процессорах семейства TMS320C5x возможны четыре основных режима адресации памяти данных:

1) Прямая адресация.

2) Косвенная адресация.

3) Непосредственная адресация.

4) Циклическая адресация.

1. Прямая адресация.

Вся область памяти данных процессора объёмом 64К разделена на 512 страниц размером 128 16-ти разрядных слов каждая. В режиме прямой адресации, команда содержит только младшие 7 бит адреса ячейки памяти. Это поле при обработке адреса дополняется 9 битами регистра указателя страницы (DP) до полного 16-ти разрядного адреса. Таким образом, регистр DP указывает на одну из 512 возможных страниц памяти размером 128 слов, а 7-ми битовый адрес в слове команды указывает на определённую ячейку памяти на данной странице памяти. Регистр DP может быть загружен при помощи команд LDP (load data memory page pointer) или LST #0 (load status register STO).

2. Косвенная адресация.

Восемь вспомогательных регистров (AR0 - AR7) обеспечивают гибкую и удобную косвенную адресацию в процессорах TMS320C5х. В случае косвенной адресации адрес операнда находится в текущем вспомогательном регистре. Для выбора текущего вспомогательного регистра необходимо загрузить в регистр указателя вспомогательного регистра (ARP) значение в диапазоне от 0 до 7.

Над содержимым вспомогательных регистров можно производить ряд арифметических операций с помощью арифметического устройства вспомогательных регистров - ARAU (Auxiliary Register Arithmetic Unit), которое выполняет арифметические операции над содержимом вспомогательных регистров в фазе декодирования команды. Это позволяет сформировать адрес перед фазой декодирования следующей команды. Использование ARAU позволяет модифицировать содержимое ARn после использования его содержимого в текущей команде, например, регистр может быть инкрементирован или декрементирован.

С помощью косвенной адресации, может быть адресована любая ячейка памяти в пределах 64К при помощи полного 16-ти разрядного значения содержащегося во вспомогательном регистре.

Существует два основных вида модификации адреса при косвенной адресации:

- косвенная адресация с инкрементом и декрементом на 1;

- косвенная адресация с индексацией (изменением) на величину, содержащуюся в регистре INDX.

Во втором случае возможно в свою очередь два варианта:

- добавление или вычитание содержимого регистра INDX;

- добавление или вычитание содержимого регистра INDX по правилам бит реверсивной арифметики (обычно используется для реализации быстрых алгоритмов преобразования Фурье).

Во всех случаях содержимое вспомогательного регистра, указанного регистром ARP, используется как адрес операнда в памяти данных. ARAU осуществляет математические операции над содержимым указанного вспомогательного регистра.

После выполнения любой команды с косвенной адресацией в ARP может быть загружено новое значение. Если в ARP загружается новая величина, то старая величина загружается в буфер вспомогательного регистра состояния ST1.

Косвенная адресация может быть использована во всех командах, кроме команд с непосредственными операндами или без операндов.

3. Непосредственная адресация

В случае непосредственной адресации операнд содержится непосредственно в слове команды. В процессорах `C5x имеются однословные команды с непосредственной адресацией (8-битовые, 9-битовые и 13-битовые константы) и двухсловные (16-битные константы) длинные команды с непосредственной адресацией. В коротких командах непосредственный операнд находится прямо в слове. В длинных командах непосредственный операнд содержится во втором слове.

4. Циклическая адресация

Циклическая адресация представляет метод адресации, при котором происходит циклическое обращение к ячейкам некоторой области памяти (к ячейкам буфера), т.е. при достижении конца буфера автоматически происходит переход к его началу и наоборот [ 6 ]. В пределах буфера для указания адреса используется вспомогательный регистр (т.е. косвенный принцип адресации). При инкременте содержимого регистра (увеличении адреса) при достижении последней ячейки буфера в этот регистр автоматически заносится начальный адрес буфера.

На рисунке 8 приведен алгоритм циклической адресации. Рисунок показывает, как будет распределяться последовательность отсчетов входного сигнала в буфере длиной 6 ячеек. В таком буфере, например, можно организовать линию задержки на 5T, где T – интервал дискретизации. Для этого надо последовательно считывать отсчеты x(0) и x(5), x(1) и x(6) и т.д.

Рисунок 8

В процессорах семейства TMS320C5x имеется аппаратный механизм реализации циклических буферов, которые позволяют организовать два одновременно действующих циклических буфера, управляемых с помощью вспомогательных регистров. Существует 5 регистров, с помощью которых осуществляется управление циклическими буферами:

- CBSR1 - регистр начального адреса первого циклического буфера;

- CBSR2 - регистр начального адреса второго циклического буфера;

- CBER1 - регистр конечного адреса первого циклического буфера;

- CBER2 - регистр конечного адреса второго циклического буфера;

- CBCR - регистр управления циклическими буферами.

Чтобы задать циклический буфер, необходимо вначале загрузить адреса начала и конца в соответствующие регистры циклического буфера, затем определить вспомогательный регистр, который будет работать указателем на ячейку памяти внутри циклического буфера. И в завершение установить бит разрешения работы соответствующего циклического буфера в регистре CBCR.

Лекция №8. Представление данных в процессорах с фиксированной точкой

Содержание лекции: форматы представления данных в процессоре TMS320C50.

Цель лекции: изучить форматы представления целых, дробных, положительных и отрицательных чисел в сигнальном процессоре TMS320C50.

Система команд процессора с фиксированной запятой TMS320С50 ориентирована на обработку двоичных чисел, представленных в дополнительном коде, который позволяет представлять как положительные, так и отрицательные числа при знаковом старшем бите.

При представлении чисел с фиксированной точкой в зависимости от ее положения используют целые или дробные числа. Максимальный диапазон представления целых чисел определяется количеством используемых разрядов при абсолютной погрешности, равной единице, а дробных – плюс-минус единица ( ± 1), абсолютная погрешность которых определяется количеством используемых разрядов в дробной части.

В 16-разрядных процессорах TMS320С5x шина данных 16-ти разрядная, а аккумулятор (АСС) - 32-х разрядный. Целочисленная арифметика позволяет представлять большие числа, но создает проблемы с сохранением результата в 16-ти разрядной ячейке памяти. При использовании дробной арифметики 32-х разрядный аккумулятор позволяет увеличить точность вычислений и уменьшить накопление ошибки. Для сохранения результата в 16-ти разрядной ячейке памяти используются старшие разряды аккумулятора. При этом потеря точности несущественна, так как младшие разряды аккумулятора содержат шум округлений.

На рисунке 9 показано соответствие исходных дробных чисел и двоичных чисел в процессоре в дополнительном коде.

|

Рисунок 9

Формат представления дробных чисел определяется как формат Q15 (15 — число значащих разрядов справа от разделительной точки). Промежуточные значения вычисляемых дробных величин на выходе умножителя и АЛУ могут быть представлены в других форматах, в частности, Q31 или Q30.

Чтобы записать исходное дробное число в формате Q15 процессора его необходимо умножить на 32768, отбросить дробную часть и перевести в 16-ричную систему (в дополнительном коде, если исходная дробь отрицательна). Ассемблер позволяет производить эти вычисления при выполнении трансляции программы.

Для перевода результата вычислений, произведенных в процессоре, из формата Q15 в обычный вид необходимо проделать обратные преобразования:

1) Перевести число из 16-ричной системы в десятичную.

2) Разделить полученное число на 32768.

Операции алгебраического сложения/вычитания чисел в дополнительном коде как беззнаковых чисел выполняются в АЛУ по правилам обычной двоичной арифметики.

Операция умножения выполняется в аппаратно реализованном специализированном узле — умножителе. Умножитель реализует алгоритм умножения двоичных чисел в дополнительном коде.

При умножении целых чисел результат содержится во всех 32 разрядах. Если необходимо ограничиться при умножении целых чисел одним словом (например, для запоминания в ячейке ЗУ), то умножать нужно числа, величина которых не превышает 28, и результат будет находиться в младшем слове регистра P.

При умножении дробных чисел в формате Q15 старшее слово 32- разрядного регистра P, в котором находится результат, является его округленным значением в формате Q14 (с двумя знаковыми разрядами) с отброшенными младшими значащими разрядами.

Таким образом, в зависимости от того, какие числа перемножаются, результат может находиться или в старшем, или в младшем слове регистра P.

Возможны два варианта решения ликвидации «лишних» знаковых разрядов:

1) сдвигом на один бит влево содержимого аккумулятора, если необходимо сохранить в памяти его старшее слово;

2) путем сдвига содержимого регистра P влево.

Второй вариант сдвига можно осуществить сдвигателем P-регистра, который управляется 2-х разрядным регистром РМ, расположенным в регистре управления ST1. Содержимое РМ можно менять командой SPM c указанием величины сдвига влево на 1 или 4 разряда или вправо на 6 разрядов. РМ устанавливается в 0 после общего сброса или командой SPM 0.

Если установить режим сдвига на 1 бит влево, то при сохранении в аккумуляторе содержимого Р- регистра формат представления чисел в аккумуляторе будет Q31 (при умножении чисел в формате Q15).

Режим расширения знака процессора определяется состоянием бита SXM (Sign Extension Mode), который расположен в регистре состояния процессора. Он показывает: использовать расширение знака или нет.

Установка бита выполняется командами:

SETC SXM ; SXM =1 - установка бита (АЛУ оперирует с числами в дополнительном коде).

CLRC SXM ; SXM = 0 - сброс бита (АЛУ оперирует с беззнаковыми числами).

После общего сброса процессора бит SXM установлен в 1.

Двоичное представление дробных чисел в дополнительном коде имеет следующие особенности: если к (+1) в двоичном коде прибавить 1/32767, получится –1, т. е. число кардинально изменяется: вместо большого положительного становится большим отрицательным.

В процессоре TMS320C50 бит контроля переполнения OV (Overflow) располагается в регистре состояния и устанавливается в случае, когда величина в аккумуляторе переходит границу между большими положительными и отрицательными числами, а также в случае, если осуществлен перенос в 33-ий, несуществующий бит.

В процессорах TMS320 с фиксированной запятой предусмотрен режим работы с переполнением. В этом режиме при выходе положительного числа за пределы разрядной сетки устанавливается наибольшее возможное положительное число, а при выходе отрицательного числа за пределы разрядной сетки устанавливается наибольшее по модулю отрицательное число.

Режим работы с переполнением или без определяется значением бита OVM регистра состояния ST1. При значении 1 происходит работа в режиме с переполнением, при значении 0 — без переполнения.

Значение бита OVM, равное 0, может быть установлено командой ROVM или CLRC OVM, значение 1 — командой SOVM или SETC OVM.

Ниже приведен пример стандартной конфигурации регистров состояния процессора для организации процедуры его инициализации.

SETC SXM ; разрешить использовать дополнительный код

CLRC OVM ; разрешить переполнение

SPM 1 ; осуществить сдвиг на 1 бит влево при копировании

; Р – регистра в аккумулятор

Лекция №9. Изучение симулятора процессора TMS320C50

Содержание лекции: правила работы с симулятором процессора TMS320C50.

Цель лекции: изучить пользовательский интерфейс и основные приемы работы с симулятором сигнального процессора TMS320C50.

Симулятор (имитатор) предназначен для программной имитации работы процессора TMS320C50 и отладки программ, предназначенных для выполнения на данном процессоре. Имитатор выполняет программы не в реальном масштабе времени. При выполнении программы в нем возможен контроль, а также модификация (изменение) состояния основных регистров процессора и содержимого памяти при тех или иных операциях.

Безусловным достоинством работы с симулятором является возможность имитировать работу цифрового сигнального процессора на любой IBM PC машине. Однако при реализации операций, при которых требуется обрабатывать большие объемы информации или анализировать изменения динамических процессов, происходящих в реальном масштабе времени, работа с симулятором становиться крайне сложной и неэффективной. Подключение реальных внешних устройств к нему вообще невозможно.

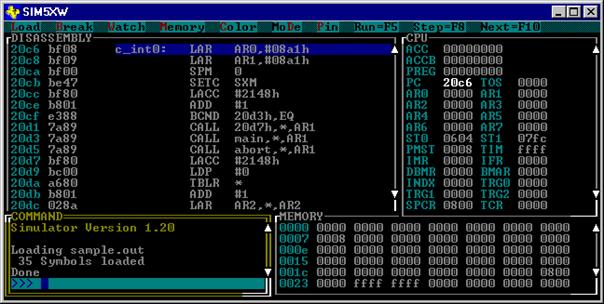

Программа симулятора SIM5X обладает дружественным интерфейсом и позволяет вводить основные команды, управляющие работой как в командной строке, так и посредством манипулятора “мышь”, используя экранное меню. Симулятор позволяет загружать и выполнять файлы, полученные в результате трансляции и компоновки программы, написанной на языке ассемблера, а также отлаживать программы на уровне языка С.

Графическая панель, формируемая программой, организована по оконному типу и дает возможность:

- загружать исполняемые программы и просматривать их дизассемблерную версию в окне DISASSEBLY;

- выделять, перемещать и менять размеры окон;

- выполнять программы в пошаговом режиме и контролировать их выполнение, следя за изменениями, происходящими с содержимым регистров (окно СРU) и областей памяти процессора (окно MEMORY);

- задавать точки останова при непрерывном выполнении программы;

- сохранять содержимое различных областей памяти в отдельном файле, что позволяет сохранять и использовать для анализа данные, полученные в результате выполнения программ при работе с симулятором;

- вводить различные команды через командное меню, посредством клавиатуры (окно COMMAND), или “мышью”;

- контролировать время выполнения программ.

После запуска программы симулятора, на экране монитора появляется графическая панель, вид которой приведен на рисунке 10 . Панель отражает состояние всех регистров и памяти процессора, а также текст дизассемблированной программы.

Рисунок 10

Процесс подготовки исполняемых программ для сигнального процессора TMS320C50 можно разделить на три этапа:

1) создание модуля-файла, например, sim.asm с исходным текстом программы, написанным на языке ассемблера;

2) трансляция полученного файла для создания объектного файла, например, sim.obj , а также листинга sim.lst, производится в режиме MS DOS путем набора в командной строке следующей команды:

dspa.exe - lcs sim.asm

3) если в программе sim нет ошибок, то нужно произвести операцию компоновки и получить выходной файл, например, sim.out и файл sim.map, набрав команду вида:

dsplnk.exe sim.cmd

Для компоновки программы используется командный файл sim.cmd, в котором задается одно из возможных распределений памяти, используемое в работе по изучению симулятора.

Таким образом, на основе объектного файла sim.obj, полученного после трансляции, и под управлением sim.cmd, программой компоновщика dsplnk.exe формируется выходной файл sim.out, который будет использоваться при работе с программой симулятора. Программа компоновщика формирует также таблицу реально полученного распределения памяти sim.map. Этот файл позволяет контролировать инициализацию начальных адресов и количество ячеек памяти, используемых для хранения программы и данных в процессоре, а также правильность расположения и соединения секций программы.

После запуска программы симулятора на экране монитора должны появиться четыре окна графического интерфейса, отражающих состояние основных элементов архитектуры процессора:

1) окно DISASSEBLY - для отлаживания текста дизассемблированной программы;

2) окно СРU - для отражения состояния аккумулятора процессора (ACC) и его буфера (ACCB), регистра результата умножения (PREG), программного счетчика (PC), регистрового файла, состоящего из восьми вспомогательных регистров (AR1 – AR0) и индексного регистра (INDX), регистров состояния (ST0, ST1 и PMST) и других регистров;

3) окно MEMORY – для отражения памяти процессора;

4) окно COMMAND – для введения разных команд процессора.

Для загрузки исполняемой программы в меню LOAD выбирается команда LOAD. В открывшимся окне нужно набрать имя файла исполняемой программы с расширением и нажать на клавиши Enter и F8.

Для вывода на экран в окно MEMORY содержимое ячеек памяти, где хранятся переменные, начиная, например, с адреса 0800, нужно набрать в командном окне команду:

mem 0x0800@data

Для запуска программы в автоматическом режиме используется команда RUN или клавиша F5. При этом программа будет выполняться до тех пор, пока не будет остановлена нажатием клавиши Esc.

Для установки точки останова в нужном месте программы нужно поместить на нее курсор и нажать левую кнопку мыши. При этом выбранная строка программы в окне DISSASEMBLE будет подсвечена. Выполнение программы между точками останова происходит при нажатии на клавишу F5. Для снятия точки останова нужно снова установить курсор в нужном месте программы и нажать левую кнопку мыши. Для снятия точек останова и возврата в начало программы используется команда RESTART.

Для выполнения программы в пошаговом режиме используется пункт меню STEP или F8.

Для возврата к состоянию с исходным содержимым программы необходимо выйти из программы командой QUIT и загрузиться вновь.

Лекция №10. Обучающий комплекс TMS320C50 DSP Starter Kit

Содержание лекции: состав платы обучающего комплекса, назначение его составных частей.

Цель лекции: изучить структурную схему платы DSK.

Плата TMS320C50 DSP Starter Kit (в дальнейшем для краткости DSK) представляет собой обучающий комплект, ориентированный на начальное изучение процессора. Возможно также использование этой платы в качестве встраиваемого модуля с цифровым сигнальным процессором для сравнительно несложных применений с обработкой сигналов, частоты которых лежат в звуковом диапазоне.

Плата – дешевый, простой учебный инструмент, который позволяет производить эксперименты с использованием TMS320C50 для обработки сигналов в реальном времени, не вкладывая дополнительных средств на создание испытательного стенда; быстро и просто организовать учебное место студента и производить эксперименты по изучению устройств различного назначения таких, как системы контроля, различные аудио и речевые устройства и др., сигналы которых расположены в области частот звукового диапазона до 9,6 кГц. Плата работает под управлением персонального компьютера.

Плата DSK включает:

- цифровой сигнальный процессор с фиксированной точкой TMS320C50. Входная тактовая частота CLKIN – 40 мГц, тактовая частота работы процессора CLKOUT1 – 20 мГц, время командного цикла - 50 нс;

- 32Кб PROM (программируемое ПЗУ), в котором зашиты служебные программы загрузки и отладчика;

- устройства ввода/вывода аналоговых сигналов на базе схемы АЦП/ЦАП TLC32040;

- стандартные RCA соединители для подключения аналоговых сигналов, в частности подключать микрофон и динамик;

- XDS510 разъем эмулятора для организации управления работой процессора в режимах отладки с помощью персонального компьютера;

- разъем для подключения к последовательному порту ПЭВМ RS232, через который организуется связь с компьютером: загрузка программ и управление работой.

На рисунке 11 изображена упрощенная структурная схема DSK.

Связь схемы АЦП/ЦАП TLC32040 с процессором TMS320C5x осуществляется через последовательный порт этого процессора.

Рисунок 11

Карта памяти DSK приведена на рисунке 12. В распоряжении пользователя для размещения программ и данных находится блок внутренней памяти типа SARAM размером 9К слов. Этот блок является памятью программ и памятью данных. Статус блока определяется битами RAM, OVLY регистра PMST, которые не могут быть модифицированы. Часть этого блока отводится под запись таблицы векторов прерывания (адреса 0800h – 083fh), часть - под ядро программы монитора. Указатель на таблицу векторов IPTR в регистре PMST, а также биты RAM, OVLY не могут быть модифицированы. В регистре PMST может быть модифицирован только младший байт содержимого.

В распоряжении пользователя остаётся область с адресами 0980h – 2bffh. Кроме того, в распоряжении пользователя находятся блоки памяти данных типа DARAM B0 и B1, один из которых (В0) может быть сконфигурирован как память программ.

Блок B2 DARAM зарезервирован как буфер для хранения содержания регистров состояния. Если программа - монитор (из области с адресами 0840h – 097fh) затерта при записи других программ или данных в эту область, требуется сигнал сброса для перезагрузки монитора

Схема АЦП/ЦАП подключена к последовательному порту процессора C50. Опорная частота работы схемы АЦП/ЦАП TLC32040, значение которой может быть равным 5Мгц или 10 Мгц, задается таймером процессора C50. Вход сброса АЦП/ЦАП подключен к контакту BR\ TMS320C50. В АЦП/ЦАП можно изменять частоту дискретизации и параметры фильтров. Описание схемы содержится в приложении Е.

Рисунок 12

Плата TMS320C50 DSK имеет свою собственную программу монитора, позволяющую контролировать состояние распределения памяти и регистров процессора, а также управлять их работой.

В качестве программного обеспечения вместе с платой DSK поставляется:

- собственный ассемблер для DSK, отличающийся от стандартного ассемблера процессора ‘С5Х некоторым упрощением и программированием только в абсолютных адресах;

- отладчик, программа-монитор.

В качестве выходного файла ассемблер формирует файл для непосредственного запуска на DSK из программы - монитора (ассемблер включает в себя определенные функции компоновщика). В то же время программа - монитор (отладчик DSK) позволяет запускать на DSK как входные файлы DSK, так и файлы формата COFF, полученные с помощью стандартного языка.

Лекция №11. Малопотребляемые сигнальные процессоры серии TMS320С5000

Содержание лекции: структура сигнального процессора подсерии TMS320C54x.

Цель лекции: изучить структуру процессора подсерии TMS320C54x.

Рассмотрим сигнальный процессор (СП) серии TMS320C5000 на примере процессоров подсерии TMS320C54x, которые отличает комбинирование модифицированной гарвардской архитектуры с тремя внутренними шинами данных и одной шиной команд [ 6 ]. Такая внутренняя организация процессора обеспечивает высокую степень параллельности выполнения команд. Эту серию характеризует высокоспециализированная система инструкций, наличие на кристалле дополнительных периферийных устройств и увеличенный объем внутренней памяти. Все это обеспечивает известную гибкость и производительность систем, проектируемых на основе данных сигнального процессора.

Три шины данных используются для чтения операндов и записи результата операции одновременно с выборкой инструкции в одном процессорном цикле. Общий объем адресуемой процессором памяти, составляющий 192 16-разрядных слов, разбит на 3 специализированных сегмента: команд, данных и ввода/вывода ― каждый из которых может иметь размер до 64 Кслов. Внутри процессора может быть расположена ROM объемом до 48 16-разрядных и до 10 Кслов двухвходовой RAM. В сигнальном процессоре предусмотрена опция защиты данных во внутренней памяти от сканирования. При установке режима защиты ни одна из команд не сможет получить доступ к содержимому внутрикристальной памяти.

Для ускорения выполнения типовых операций сигнальной обработки помимо «стандартных» для СП блоков барабанного сдвига и адресной арифметики процессор содержит ряд дополнительных функциональных модулей, повышающих его гибкость и производительность. Блок умножения с накоплением (MAC) выполняет над 17 битовыми операндами операции вида S = S + a • b за один процессорный такт. Подобные операции характерны для алгоритмов фильтрации, свертки, вычисления корреляционной функции.

Для быстрого вычисления значений функции у = ехр(х) микропроцессор содержит блок перекодировки значения аккумулятора (EXP Encoder), интерпретируемое как значение аргумента функции. Данный блок вычисляет соответствующее значение за один такт.

Эффективную реализацию оператора Витерби обеспечивает блок (CMPS Operation), выполняющий за один цикл операцию сравнения-выбора с накоплением (Add/Compare Selection).

Арифметико-логическое устройство (АЛУ) способно выполнять арифметические или булевы операции над комплексными числами (используя два регистра аккумулятора АССА и АССВ) или может функционировать как два 16-разрядных АЛУ, выполняющих одновременно две 16-разрядных операции. АЛУ и MAC могут выполнять операции в цикле одновременно.

Устройство барабанного сдвига осуществляет сдвиг данных на 0—31 разряд влево или 0—16 разрядов вправо за один такт, а также совместно с блоком вычисления экспоненциальной функции обеспечивает нормализацию содержимого аккумулятора за один такт. Дополнительные возможности сдвига позволяют процессору масштабировать данные, выделять разряды числа, предотвращать возникновение переполнения и потери значимости.

Все сигнальные процессоры подсерии TMS320C54x имеют одинаковую структуру, однако отличаются друг от друга расположенной на кристалле периферией, соединенной с ЦПУ. Из рисунка 13 видно, что в состав периферийных устройств входят:

- программно-управляемый генератор тактов ожидания;

- программный переключатель банков памяти;

- параллельные порты ввода/вывода;

- аппаратный таймер и генератор тактовых импульсов.

Рисунок 13

Генератор тактов ожидания позволяет увеличить число тактов внешней шины для работы с медленной внешней памятью и внешними устройствами.

Переключатель банков памяти позволяет автоматически добавлять один такт при пересечении границ банка памяти внутри программного адресного пространства или при переходе от пространства адресов команд к пространству адресов данных. Этот дополнительный такт позволяет устройству памяти освободить шину раньше, чем другое устройство получит доступ к ней, избегая тем самым конфликтной ситуации при обращении к памяти.

Микропроцессоры семейства имеют 64К портов ввода/вывода. Эти порты предназначены для связи с внешними устройствами с использованием минимума дополнительных внешних декодирующих схем.

Интерфейс главного порта (HPI) — 8-разрядный параллельный порт, предназначенный для связи СП и хост-процессора системы. Обмен данными между хост-процессором и процессором осуществляется через внутрикристальную HPI-память объемом 2К 16-разрядных слов, которая может также использоваться как память команд или данных общего назначения. Скорость обмена по HPI составляет до 160 Мбайт/с.

Сигнальные процессоры данной подсерии содержат высокоскоростные дуплексные последовательные порты, позволяющие связываться с другими процессорами, кодеками и т.д. В процессоре реализованы следующие разновидности последовательных портов:

- универсальный;

- мультиплексный с временным уплотнением;

- с автобуферизацией.

Универсальный последовательный порт использует два отображаемых в память регистра: передачи данных и приема данных. Передача и прием данных сопровождается генерацией маскируемого прерывания, которое может быть обработало программно.

Буферизированный последовательный порт позволяет осуществлять непосредственный обмен между устройством и памятью, не используя при этом ресурсов процессора. Максимальная скорость обмена по последовательному порту может составлять до 40 Мбайт/с.

В сигнальных процессорах TMS320C54x реализована эффективная трехуровневая система управления энергопотреблением. Низкое, управляемое энергопотребление, высокая производительность (до 66 MIPS) и широкие функциональные возможности при невысокой цене предопределили востребованность TMS320C54x в следующих областях: сотовые и радиотелефоны, персональные системы радиовызова, «персональные цифровые ассистенты» (PDA), техника беспроводной передачи данных (радиосети) и т.д.

Список литературы

1. Солонина А.И. и др. Алгоритмы и процессоры цифровой обработки сигналов – СПб.: БХВ - Петербург, 2001. - 464 с.

2. Бойко В.И. и др. Схемотехника электронных систем. Микропроцессоры и микроконтроллеры. – СПб.: БХВ – Петербург, 2004. – 464 с.

3. Сперанский В.С. Сигнальные микропроцессоры и их применение в системах телекоммуникаций и электроники: учебное пособие. – М.: Горячая линия - Телеком, 2008. – 168 с.

4. Айфичер Эммануил, Джервис Барри. Цифровая обработка сигналов: практический подход. - М.: Издательский дом «Вильямс», 2004.- 992 с.

5. Куприянов М.С., Матюшкин Б.Д. Цифровая обработка сигналов: процессоры, алгоритмы, средства проектирования. – СПб.: Политехника, 1999.- 592 с.

6. Круг П.Г. Процессоры цифровой обработки сигналов: Учебное пособие. - М.: Издательство МЭИ, 2001. – 128 с.

7. Солонина А.И. и др. Основы цифровой обработки сигналов: курс лекций. – СПб.: БХВ - Петербург, 2005. - 768 с.

8. Корнеев В.В., Киселев А.В. Современные микропроцессоры. – М.: НОЛИДЖ, 1998. – 240 с.

9. Гольденберг Л.М. и др. Цифровые устройства и микропроцессорные системы. Задачи и упражнения: учебное пособие. - М.: Радио и связь, 1992. -256 с.

10. Петрищенко С.Н. Цифровая обработка сигналов: конспект лекций для магистрантов специальности 6N0719 – Радиотехника, электроника и телекоммуникации. - Алматы: АИЭС, 2009. – 36 с.

11. Петрищенко С.Н., Мусапирова Г.Д. Сигнальные процессоры. Методические указания к выполнению лабораторных работ для студентов специальности 5В071900 – Радиотехника, электроника и телекоммуникации. – Алматы: АУЭС, 2011. – 37 с.

12. Петрищенко С.Н., Мусапирова Г.Д. Сигнальные процессоры. Методические указания на выполнение курсовой работы для бакалавров специальности 5В071900 – Радиотехника, электроника и телекоммуникации. – Алматы: АУЭС, 2011. – 11 с.

Содержание

1 Лекция №1. Основные понятия и математические соотношения цифровой обработки сигналов

2 Лекция №2. Анализ основных направлений цифровой обработки сигналов

3 Лекция №3. Квантование в цифровых системах

4 Лекция №4. Архитектурные особенности сигнальных процессоров

5 Лекция №5. Классификация и особенности цифровых сигнальных процессоров с фиксированной точкой

6 Лекция №6. Архитектура сигнального процессора TMS320C50

7 Лекция №7. Режимы адресации памяти сигнального процессора TMS320C50

8 Лекция №8. Представление данных в процессорах с фиксированной точкой

9 Лекция №9.Изучение симулятора процессора TMS320C50

10Лекция №10.Обучающий комплекс TMS320C50 DSP Starter Kit

11Лекция №11.Малопотребляемые сигнальные процессоры серии TMS320C5000

Список литературы

Св.план 2012 г.поз.343