Некоммерческое акционерное общество

АЛМАТИНСКИЙ УНИВЕРСИТЕТ ЭНЕРГЕТИКИ И СВЯЗИ

Кафедра «Электроника»

ОСНОВЫ МИКРОПРОЦЕССОРНОЙ ТЕХНИКИ

Часть 2

Методические указания к выполнению лабораторных работ

для студентов всех форм обучения специальности

5B070300 – Информационные системы

Алматы 2011

СОСТАВИТЕЛЬ: У.Т. Шанаев. Основы микропроцессорной техники. Часть 2. Методические указания к выполнению лабораторных работ по курсу “Основы микропроцессорной техники” для студентов всех форм обучения специальности 5B070300 – Информационные системы. – Алматы: АУЭС, 2011. – 19 с.

Предлагаемые в методической разработке работы посвящены моделированию структуры микропроцессорных систем, т.е. изучению общих принципов построения микропроцессорных систем и обеспечения взаимодействия работы их структурных и функциональных блоков по реализации поставленных практических задач. Тем самым, эти лабораторные работы нацелены на формирование знаний студентов как по структурным основам микропроцессорных систем, так и по основам программирования их работы.

Выполнение этих работ, организованных в виде виртуальных экспериментов, осуществляемых на разработанной автором модели микропроцессорной системы в программной среде Electronics Workbench, предоставит студентам широкие возможности как для освоения принципов их построения, так и для приобретения практических навыков по программированию их работы.

Методические указания к лабораторным работам предназначены для студентов всех форм обучения по специальности 5B070300 – Информационные системы. Они могут быть использованы и для организации лабораторных занятий по идентичным темам аналогичных дисциплин, запланированных для других специальностей.

Ил. 8, табл. 2, библиогр. – 7 назв.

Рецензент: докт. физ-мат. наук, проф. С. Б. Бимурзаев

Печатается по плану издания Некоммерческого акционерного общества “Алматинский университет энергетики и связи” на 2011 г.

© НАО “Алматинский университет энергетики и связи”, 2011 г.

Введение

Курс “Основы микропроцессорной техники”, посвященный изучению структурных принципов построения микропроцессорных систем и их функциональных основ, состоит из двух взаимосвязанных и взаимообусловленных частей: аппаратная часть (hardware) и программная часть (software). Ясно, что для наиболее полного освоения дисциплины необходимо обеспечить формирования знания как по аппаратной, так и по программной частям курса.

В предущей методической разработке [1] были представлены лабораторные работы, предназначенные для изучения принципов построения структурных компонентов (устройств ввода данных, системы памяти, интерфейсов) микропроцессорной системы и их функционирования (организации параллельной, последовательной и помехоустойчивой передач).

Предлагаемые в методической разработке лабораторные работы, посвящены моделированию структуры микропроцессорной системы, т.е. принципов их построения и обеспечения взаимодействия структурных и функциональных блоков системы. Следовательно, эти работы нацелены на формирование знаний студентов как по основам построения микропроцессорных систем, так и по программированию их работы.

Выполнение рабочих заданий лабораторных занятий осуществляется на разработанной автором модели микропроцессорной системы. Основу этой модели составляет микропроцессор, обладающий уникальными (т.е. не типовыми) функциональными возможностями. В качестве остальных структурных блоков системы были использованы рассматривавшиеся ранее устройства (системы ввода и памяти). Использованная методика построения системы нацелена на обеспечение преемственности формирования знаний студентов и приобретению ими навыков построения цифровых систем, что необходимо им в будущей профессиональной деятельности.

Предлагаемая методика организации лабораторных занятий проверена многолетней практикой преподавания автора и испытана временем. Разнообразие форм организации учебного исследования обеспечивает более глубокие знания студентов по теории изучаемых элементов и устройств цифровых систем и способствуют формированию у них практических навыков по проведению как моделирующих, так и практических экспериментов, что, в конечном счете, обеспечивает достижение целей лабораторных занятий.

1 Практические сведения и методические рекомендации

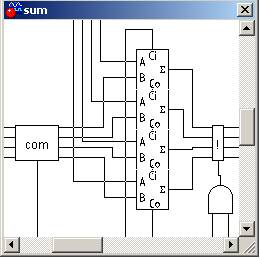

Модель 4-разрядной микропроцессорной системы, содержащий в своем составе микропроцессор (MP4M), устройство ввода данных (In), система памяти (Mem) и блок выбора режима работы системы (Regime), приведен на рисунке 1.1.

Рисунок 1.1

В качестве основы построения модели были приняты следующие общие принципы построения микропроцессорных систем:

- магистральность;

- модульность;

- микропрограммное управление.

Принцип магистральности определяет характер связей между функциональными блоками МПС, заключающейся в том, что все блоки соединяются между собой общей системной магистралью и через него обмениваются информацией. В состав системной магистрали входят шина данных (DB, Data Bus), Шина адреса (AB, Address Bus) и шина управления (CB, Control Bus). Шины данных и адреса в учебной модели – четырехразрядные, а число линий в шине управления определяется числом блоков системы, числом их внутренних структурных компонентов и числом их режимов работы.

Принцип модульности состоит в том, система строится на основе отдельных конструктивно и функционально завершенных модулей. Составными модулями учебной модели являются:: микропроцессор (MP4M, Microprocessor 4-bit, Modified), устройство ввода данных (In, Input) и система памяти (Mem, Memory). Внутренние структуры этих блоков также определены по тем же принципам магистральности и модульности.

Принцип микропрограммного управления состоит в возможности выполнения команд с помощью элементарных операций – микрокоманд (пересылок информации, арифметических и логических операций, приращений).

Рассмотрим внутренюю структуру модулей системы.

1.1 Микропроцессор

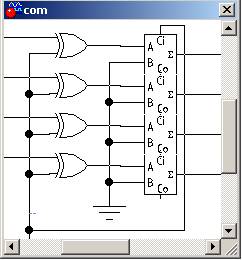

В состав микропроцессора входят следующие блоки (см. рисунок 1.2):

- набор специализированных регистров (RGs, Registers);

- арифметико-логическое устройство (ALU, Arithmetic-Logic Unit);

- регистр команды (IR, Instruction Register);

- дешифратор команд (DC_16, Decoder 16-bit);

- таймер (CLK, Clock);

- микропрограммное устройство (Combi, Combinational Circuit.

Рисунок 1.2

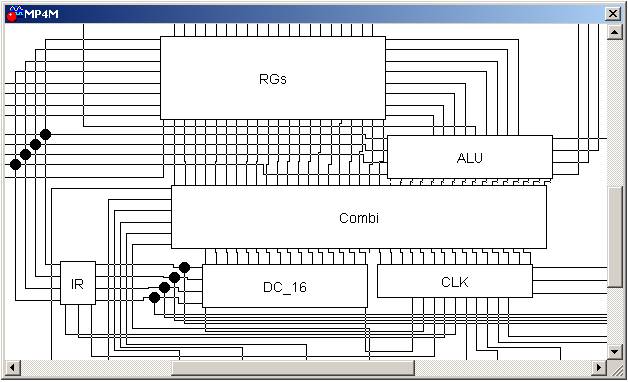

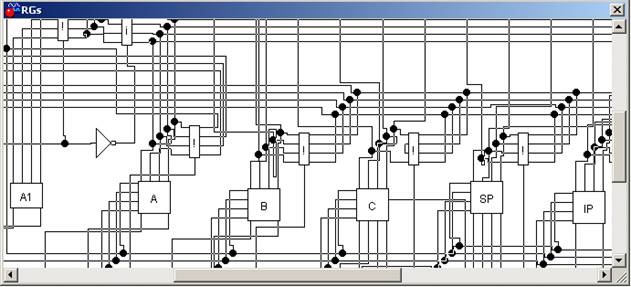

Набор регистров (RGs) содержит в своем составе следующие регистры, каждый из которых предназначен для выполнения определенных функций (см. рисунок 1.3):

Рисунок 1.3

- регистр A, построенный на основе микросхемы 74169, выполняет функцию аккумулятора (Accumulator), где хранится один из операндов, участвующих в выполнении арифметических и логических операций или результат выполнения операции. Загрузка аккумулятора осуществляется из памяти (команда LD A) или из ALU (после выполнения арифметической или логической операции);

- регистр A1, построенный на основе микросхемы 7493, предназначен для накопления переносов при организации циклического суммирования. Он обнуляется при запуске программы и при загрузке аккумулятора (регистра A) командой LD A. Вывод его содержимого на индикаторы (аккумулятора) осуществляется кратковременным нажатием клавиши Space;

- регистр B, построенный на основе микросхемы 74169, выполняет функцию адресного регистра для команд пересылок между памятью и внутренними регистрами микропроцессора (команды LD C, LD IP, LD SP, LD A). После выполнения команд LD C, LD SP, LD A происходит приращение содержимого регистра B (т.е. увеличение на единицу). Загрузка этого регистра осуществляется командой LD B, в качестве адресного регистра для которого используется регистр C. Он обнуляется при запуске программы;

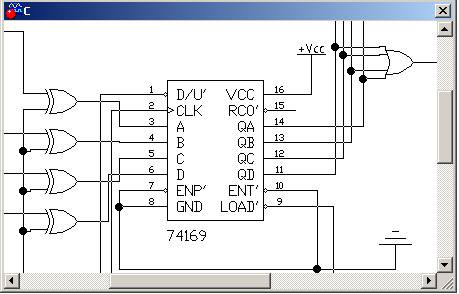

- регистр C, построенный на основе микросхемы 74169 (см. рисунок 1.4), выполняет функцию адресного регистра для второго операнда, участвующего в выполнении арифметических и логических операций. После выполнения соответствующих команд происходит приращение содержимого регистра C, но в отличие от регистра B знак приращения регистра C может быть изменен, он устанавливается клавишей I. Ее состояние показывает индикатор (I) - Dcr/Inr: при I=0 – положительное (Increment), а при I=1 – отрицательное (Decrement) приращение. Его содержимое может быть оставлено и в неизменном состоянии, о котором будет рассказано при описании режимов работы системы. Загрузка этого регистра осуществляется командой LD C.

При запуске программы этот регистр устанавливается в состояние 1111 (с помощью элементов XOR). Ввиду того, что любая программа содержит в своем составе команды пересылок, первой команды программы должна быть загрузка регистра B (команда LD B) данным, содержащимся в ячейке памяти данных с адресом 1111.

Четырехвходовый элемент OR в схеме регистра C предназначен для определения нулевого состояния регистра, по которому осуществляется условный переход при организации циклических операций;

Рисунок 1.4

- регистр SP, построенный на основе микросхемы 74169, выполняет функцию указателя стека (Stack Pointer), т.е. он выполняет функцию адресного регистра при выполнении команд PUSH и POP: перед выполнением команды PUSH происходит отрицательное приращение (Predecrement) его содержимого и после выполнения команды POP – положительное приращение (Postincrement). Загрузка этого регистра осуществляется командой LD SP. При запуске программы этот регистр устанавливается в состояние 1111;

- регистр IP, построенный на основе микросхемы 74169, выполняет функцию указателя команды (Instuction Pointer). После выборки кода текущей команды и сохранения его в регистре команды происходит приращение его содержимого. Загрузка этого регистра осуществляется командой LD IP. Его содержимое изменяется и при выполнении условий перехода, определяемых в некоторых альтернативных режимах работы системы. Он обнуляется при запуске программы.

Входы всех регистров соединены к внутренней шине данных, а выходы – к шине данных или к шине адреса (через буферные элементы с тремя состояниями) соответственно выполняемыми ими функциями.

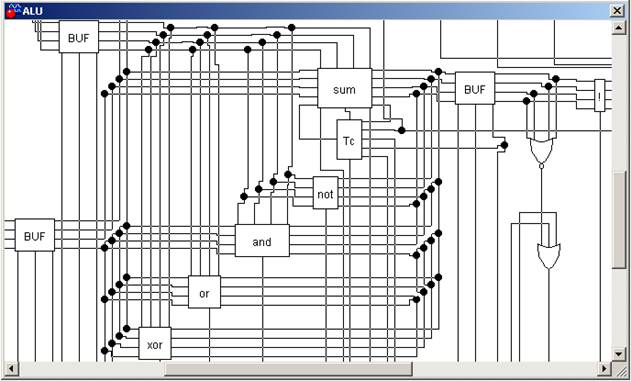

Арифметико-логическое устройство (ALU, Arithmetic-Logic Unit) осуществляет выполнение арифметических и логических операций и содержит в своем составе различные подблоки (sum, not, and, or, xor), предназначенные для реализации соответствующих операций и буферные регистры для временного хранения операндов и результата выполненной операции (см. рисунок 1.5).

Рисунок 1.5

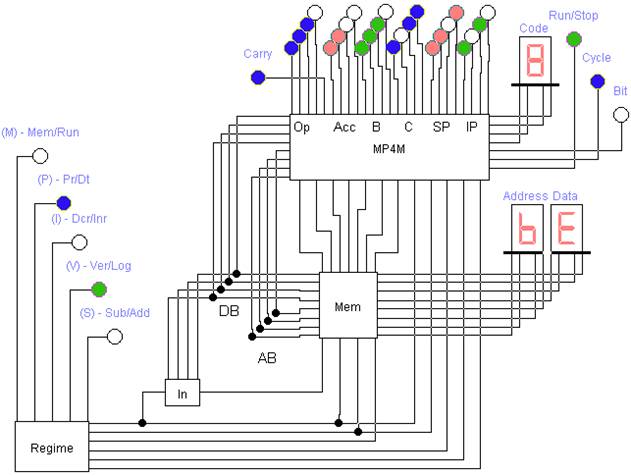

Подблок sum (summation), построенный на основе одноразрядных сумматоров (см. рисунок 1.6, a), содержит блок com (complement), предназначенный для получения дополнительного кода вычитаемого при выполнении операции вычитания (см. рисунок 1.6, b). Таким образом, в блоке sum может выполняться операции как суммирования, так и вычитания. Характер операции определяется состоянием переключателя (S) - Sub/Add: при S=0 – суммирование (Addition), а при S=1 – вычитание (Subtraction).

Подблок Tc, построенный на основе D-триггеров, обеспечивает хранение переноса и передачу ее в сумматор в зависимости от типа команды суммирования/вычитания – ADS или ACS (без переноса или с переносом).

Логические элементы в последней части схемы обеспечивают реализацию битовой операции по поиску единичного бита в определенном разряде данных. Обнаружение единичного бита в искомом разряде данных позволяет осуществить условный переход при организации циклических операций.

В регистр команды (IR), построенный на основе микросхемы 74194, записывается код текущей команды и сохраняется там до в течение всего процессе ее выполнения.

|

|

|

|

a |

b |

Рисунок 1.6

Дешифратор команды (DC_16) в зависимости от кода команды включает соответствующую микропрограмму управления выполнением текущей команды, т.е. определяет линию выработки сигналов, управляющих работой устройств, участвующих в ее выполнении.

Таймер (CLK) определяет временное распределение сигналов управления, передаваемых к устройствам, участвующим в выполнении команд.

Микропрограммное устройство комбинационного типа (Combi, Combinational Circuit), формирует пространственные и временные сигналы управления, обеспечивающие выполнение текущей команды.

1.2 Устройство ввода данных

Устройство ввода (In), предназначенное для ввода в память системы необходимых для ее работы данных (кодов команд и данных), состоит из двух подблоков (см. рисунок 1.7):

- клавишное устройство (0_F);

- кодирующее устройство (CD).

Клавишное устройство (0_F), построенное на основе клавиш, поименованных шестнадцатеричными символами, обеспечивают формирование отрицательных импульсов при их нажатии.

Кодирующее устройство (CD), составленное на основе приоритетных шифраторов, вырабатывает двоичный код, соответствующий нажатой клавише.

Рисунок 1.7

1.3 Система памяти

Основными структурными компонентами системы памяти (Mem, Memory) являются (см. рисунок 1.8):

- блоки памяти (mem, memory);

- блок управления памяти (MCon, Memory Control);

- регистр адреса (Add_4);

- буферные элементы.

Рисунок 1.8

Два идентичных блока памяти (mem) предназначены для раздельного хранения кодов команд и данных.

Блок управления памяти (MCon) обеспечивает выбор одного из блоков памяти (кодов или данных) и режим его работы (ввода, записи, считывания) в зависимости от управляющих сигналов, поступающих от устройства ввода или микропроцессора.

Общий для двух блоков памяти регистр адреса (Add_4) предназначен для хранения адреса активизируемой ячейки памяти во время записи или считывания информации.

Буферные элементы (!и i) с тремя состояниями определяют направление передачи данных в зависимости от типа выполняемой команды.

1.4 Режимы работы системы

Система может работать в нескольких режимах, которые определяются в зависимости от состояний клавиш в блоке выбора режима ее работы (Regime). Состояние этих клавиш показывают соответствующие индикаторы (см. рисунок 1.1). Опишем эти режимы.

Загрузка памяти от устройства ввода осуществляется при M=1. Если при этом P=1, то запись происходит в программную память (программа должна завершаться командой остановки с кодом F), а при P=0 – в память данных. Проверка содержимого памяти осуществляется изменением адреса ячейки памяти путем кратковременного нажатия клавиши Space. При переключении клавиши P происходит обнуление адреса памяти.

Запуск программы к работе осуществляется переключением клавиши M в состояние M=0. Если при этом P=1, то при выполнении арифметических и логических команд происходит изменение содержимого регистра C (соответственно значению I), а при P=0 его содержимое остается неизменным.

При S=0 по командам ADS и ACS выполняются операции сложения, а при S=1 – операции вычитания.

При V=0 по команде AND выполняется обычная операция логического умножения между двумя операндами, а при V=1 – реализуется битовая операция по поиску единичного бита в определенном разряде данных, для чего в аккумулятор должно быть загружено число, содержащее единицу только в искомом разряде. Описанная битовая операция имитирует поиск сигнала запроса от внешнего устройства или квитирования в реальных прикладных системах.

Перевод системы в один из описанных режимов осуществляется перед запуском программы к работе, но может быть осуществлен и в процессе работы программы, что расширяет программные возможности системы. Например, в процессе работы можно операции сложения изменять на вычитание и наоборот. Аналогично конъюнкцию можно изменять на битовую операцию.

1.5 Команды микропроцессора MP4M

Команды микропроцессора MP4M и их характеристики приведены в таблице 1.1, а порядок установки режимов работы системы – в таблице 1.2.

Т а б л и ц а 1.1 – Команды микропроцессора MP4M

|

Мн-ка |

Коды |

Операции |

|||

|

Hex |

V=0 |

P |

S |

V=1; I=1 |

|

|

LD B |

0 |

B←[(C)]; C←(C)+1 |

|

|

|

|

LD C |

1 |

C←[(B)]; B←(B)+1 |

|

|

|

|

LD IP |

2 |

IP←[(B)] |

|

|

|

|

LD SP |

3 |

SP←[(B)]; B←(B)+1 |

|

|

|

|

LD A |

4 |

A←[(B)]; B←(B)+1 |

|

|

|

|

ST |

5 |

[(B)]←(A);B←(B)+1 |

|

|

|

|

INR |

6 |

A←(A)+1 |

|

|

|

|

NOT |

7 |

A← |

|

|

|

|

ADS |

8 |

A←(A)±[(C)]; TC |

P=1: C←var(I) P=0: C = invar |

S=1: SUB (–) S=0:ADD,ADC (+) |

Zc = 0: IP←IP+1 |

|

ACS |

9 |

A←(A)±[(C)±TC; TC |

|

|

|

|

AND |

A |

A←(A)۸[(C)] |

|

|

Zc۸Za=0: IP←IP+1 |

|

OR |

B |

A←(A)۷[(C)] |

|

|

|

|

XOR |

C |

A←(A) |

|

|

|

|

PUSH |

D |

SP←(SP)–1; (SP)]←(A) |

|

|

|

|

POP |

E |

A←(SP)]; SP←(SP)+1 |

|

|

|

|

HLT |

F |

IP = invar |

|

|

|

Т а б л и ц а 1.2 – Установка режимов работы микропроцессора MP4M

|

Ключи и инд-ры |

M/R = 1 |

M/R → 0: Running: A,B,IP ← 0; C,SP ← F |

||

|

P=1: C←var(I); P=0: C = invar |

||||

|

S = 0 |

P/D = 1: MemPr←IN |

P/D = 0: MemD←IN |

Addition (+) |

A ← (A) + [(C)] |

|

S = 1 |

Subtraction (–) |

A ← (A) – [(C)] |

||

|

I = 1 |

PostDecrement C←(C) –1 |

C←(C)–1; (C)=0: Zc ← 0 |

||

|

I = 0 |

PostIncrement C←(C) +1 |

C ← (C) + 1 |

||

|

V = 0 |

Logical Operation |

A

← (A)

{۸ /

۷ / |

||

|

V = 1 |

Verifying of Byte |

(A)=0010…bi = 1: Za ← 0 |

||

1.6 Оборудование рабочего места:

- компьютер;

- программа Electronics Workbench Professional (C:\EWB5PRO);

- папка BMPT(Bases of the Microprocessor Technology);

- файл MP4M.ewb.

2 Лабораторная работа. Модель MP4M

Цель работы:

- знакомство со структурой модели микропроцессорной системы;

- освоение порядка работы с моделью МПС;

- изучение действия команд пересылок;

- освоение принципов построения МПС и ее функционирования.

2.1 Рабочее задание

2.1.1 Открыть программу EWB5PRO и выбрать файл MP4M.ewb. Раскрывая подсхемы основных блоков системы (см. рисунок 1.1) и их внутренних компонентов и изучая практические сведения о системе, представленные в 1.2, ознакомиться с их структурой и принципами функционирования.

2.1.2 Активизировать программу EWB5PRO кнопкой

![]() и в дальнейшем не выключать

ее до конца работы во избежание потери записанной в память информации.

и в дальнейшем не выключать

ее до конца работы во избежание потери записанной в память информации.

2.1.3 Подготовить систему к режиму загрузки программы установкой клавиш M и P в состояние M=1 и P=1. Загрузить в память коды команд представленной ниже программы.

|

Адрес |

Команды |

Коды |

Адрес |

Команды |

Коды |

|

0 |

LD B |

0 |

5 |

POP |

E |

|

1 |

LD A |

4 |

6 |

ST |

5 |

|

2 |

LD SP |

3 |

7 |

PUSH |

D |

|

3 |

LD C |

1 |

8 |

PUSH |

D |

|

4 |

POP |

E |

9 |

HLT |

F |

2.1.4 Перевести систему в режим загрузки данных установкой клавиши P в состояние P=0. Загрузить в память данные (например, последовательные значения чисел, начиная с какого-то конкретного значения) и записать их в рабочую тетрадь.

2.1.5 Проверить правильность введенной в память информации (программы и данных), выбрав необходимый тип памяти клавишей P и кратковременно нажимая клавишу Space.

2.1.6 Запустить работу загруженной

программы, установив клавишу P в состояние P=1 и переключив клавишу M в состояние M=0. Наблюдая за состояниями

индикаторов, проверить работу программы. При необходимости работу программы

можно приостановить кнопкой ![]() или

перезапустить программу двойным нажатием клавиши M (не

очень быстро).

или

перезапустить программу двойным нажатием клавиши M (не

очень быстро).

2.1.7 После остановки работы программы перевести систему в режим ввода и проверить содержимое ячеек памяти данных. Объяснить причину происшедших изменений.

2.1.8 Восстановив введенные ранее данные и изменив содержимое ячейки памяти данных с адресом F, запустить работу программы и проверить ее работу.

2.2 Контрольные вопросы

1. Объяснить структуру модели микропроцессорной системы и ее функциональных блоков.

2. Объяснить внутреннюю структуру микропроцессора и функции ее составляющих компонентов.

3. Объяснить действия команд пересылок, использованных в исследованной программе.

3 Лабораторная работа. Арифметические операции

Цель работы:

- освоение порядка работы с моделью МПС;

- изучение действия арифметических команд при выполнении операций сложения;

- изучение действия арифметических команд при выполнении операций вычитания.

3.1 Рабочее задание

3.2.1 Открыть программу EWB5PRO, выбрать файл MP4M.ewb и активизировать программу EWB5PRO кнопкой ![]() .

.

3.2.2 Подготовить систему к режиму загрузки программы (M=1, P=1) и загрузить в память коды команд представленной ниже программы суммирования.

|

Адрес |

Команды |

Коды |

Адрес |

Команды |

Коды |

|

0 |

LD B |

0 |

6 |

ADS |

8 |

|

1 |

LD C |

1 |

7 |

ADS |

8 |

|

2 |

LD A |

4 |

8 |

ACS |

9 |

|

3 |

INR |

6 |

9 |

ACS |

9 |

|

4 |

INR |

6 |

A |

ACS |

9 |

|

5 |

ADS |

8 |

B |

HLT |

F |

3.2.3 Перевести систему в режим загрузки данных (M=1, P=0). Загрузить в память данные (например, последовательные значения чисел, начиная с какого-то конкретного значения) и записать их в рабочую тетрадь.

3.2.4 Проверить клавишей Space правильность введенной в память информации (программы и данных).

3.2.5 Запустить работу загруженной

программы (P=1, затем M=0). Наблюдая

за состояниями индикаторов, проверить работу программы. При необходимости можно

воспользоваться кнопкой приостановки ![]() .

.

3.2.6 После остановки работы программы проверить содержимое регистра A1 кратковременным нажатием клавиши Space (эту можно делать и процессе работы программы). Объясните полученный результат. При возникновении затруднения в этом, перезапустить программу (двойным нажатием клавиши M) и более внимательно наблюдать за возникающими переносами в операциях сложения.

3.2.7 Перевести систему в режим загрузки программы, изменить состояние клавиши S в S=1, в результате чего программа суммирования превращается в программу вычитания, т.е. при выполнении команд ADC и ACS выполняются операции вычитания (соответственно – без переноса и с переносом).

3.2.8 Запустить работу загруженной программы. Наблюдая за состояниями индикаторов, проверить работу программы. При необходимости перезапустить работу программы.

3.2.9 Учитывая, что арифметические операции выполнятся в дополнительном коде, выполните вручную в двоичном коде все выполненные в программе операции вычитания и сравните их поэтапно с результатами, получаемыми в системе.

3.2 Контрольные вопросы

1. Объяснить действия команд суммирования в программе.

2. В чем заключается различия действий команд ADS и ACS?

3. В каких случаях происходит накопление переноса в регистре A1?

4. Объяснить порядок выполнения операций вычитания и продемонстрировать его на примерах.

4 Лабораторная работа. Логические операции

Цель работы:

- освоение порядка работы с моделью МПС;

- изучение действия логических команд;

- освоение методики определения единичного бита в определенном разряде данных.

4.1 Рабочее задание

4.1.1 Открыть программу EWB5PRO, выбрать файл MP4M.ewb и активизировать программу EWB5PRO.

4.1.2 Подготовить систему к режиму загрузки программы и загрузить в память коды команд представленной ниже программы.

|

Адрес |

Команды |

Коды |

Адрес |

Команды |

Коды |

|

0 |

LD B |

0 |

6 |

XOR |

C |

|

1 |

LD C |

1 |

7 |

LD A |

4 |

|

2 |

LD A |

4 |

8 |

AND |

A |

|

3 |

NOT |

7 |

9 |

OR |

B |

|

4 |

AND |

A |

A |

XOR |

C |

|

5 |

OR |

B |

B |

HLT |

F |

4.1.3 Перевести систему в режим загрузки данных. Загрузить в память данные и записать их в рабочую тетрадь.

4.1.4 Запустить работу загруженной программы. Наблюдая за состояниями индикаторов, проверить работу программы и действия команд в ней. При необходимости приостановить работу программы или перезапустить ее.

4.1.5 Перевести систему в режим загрузки программы, изменить состояние клавиши V в V=1 и загрузить в память коды команд представленной ниже программы определения единичного бита в определенном разряде данных.

|

Адрес |

Команды |

Коды |

Адрес |

Команды |

Коды |

|

0 |

LD B |

0 |

5 |

AND |

A |

|

1 |

LD C |

1 |

6 |

AND |

A |

|

2 |

LD A |

4 |

7 |

AND |

A |

|

3 |

AND |

A |

8 |

AND |

A |

|

4 |

AND |

A |

9 |

HLT |

F |

4.1.6 Перевести систему в режим загрузки данных. Загрузить в ячейку памяти данных с адресом F число 7, в ячейку с адресом 8 – число 2, а в остальные ячейки – любые числа. Записать эти данные в рабочую тетрадь.

4.1.7 Запустить работу загруженной программы. Наблюдая за состояниями индикаторов, проверить работу программы. Обнаружение единицы во втором разряде данных оповещается высвечиванием индикатора Bit.

4.1.8 Перевести систему в режим загрузки данных и, изменив число в ячейке с адресом 8 на число 4, снова запустить работу программы и пронаблюдать за работой программы.

4.2 Контрольные вопросы

1. Объяснить действия логических команд, использованных в программе. Объяснить порядок выполнения соответствующих операций на примерах.

2. Объяснить порядок обнаружения единицы в определенном разряде данных на примерах.

3. Как можно было бы осуществить обнаружение нуля в определенном разряде данных?

5 Лабораторная работа. Циклические программные структуры

Цель работы:

- освоение принципов организации циклической программной структуры на модели МПС;

- освоение методики работы с массивом данных;

- изучение программы вычисления суммы нескольких чисел;

- освоение методики поиска единичного бита в определенном разряде данных.

5.1 Рабочее задание

5.1.1 Открыть программу EWB5PRO, выбрать файл MP4M.ewb и активизировать программу EWB5PRO.

5.1.2 Подготовить систему к режиму загрузки и загрузить в память коды команд представленной ниже программы и данные для программы для определения суммы N чисел (в данном случае N=5).

|

Адрес |

Команды |

Коды |

Адрес |

Данные |

Адрес |

Данные |

|

0 |

LD B |

0 |

0 |

6 |

… |

… |

|

1 |

LD C |

1 |

1 |

8 |

7 |

5 |

|

2 |

ADS |

8 |

2 |

D |

8 |

2 |

|

3 |

LD IP |

2 |

3 |

A |

… |

… |

|

4 |

HLT |

F |

4 |

9 |

|

|

|

|

|

|

5 |

B |

F |

7 |

5.1.3 Запустить работу загруженной программы при P=1, S=0, I=1. После завершения работы программы младшая тетрада результата суммирования окажется в аккумуляторе (регистре A), а старшую тетраду, которая находится в регистре A1, можно выяснить кратковременным нажатием клавиши Space.

5.1.4 Определите вручную сумму чисел, размещенных в ячейках с адресами 1…5, и сравнить ее с результатом, полученным в системе.

5.1.5 Перевести систему в режим загрузки, загрузить в память коды команд представленной ниже программы обнаружения единичного бита в третьем разряде среди данных, размещенных в ячейках с адресами 1…5 (в данном конкретном случае – число D, размещенное в ячейке с адресом 2).

|

Адрес |

Команды |

Коды |

Адрес |

Данные |

Адрес |

Данные |

|

0 |

LD B |

0 |

0 |

6 |

… |

… |

|

1 |

LD C |

1 |

1 |

8 |

7 |

5 |

|

2 |

LD A |

4 |

2 |

D |

8 |

4 |

|

3 |

AND |

A |

3 |

A |

9 |

3 |

|

4 |

LD IP |

2 |

4 |

9 |

… |

… |

|

5 |

HLT |

F |

5 |

B |

F |

7 |

5.1.6 Запустить работу загруженной программы. Наблюдая за состояниями индикаторов, проверить работу программы. При обнаружении искомого числа высвечивается индикатор Bit и программа завершит свою работу.

5.1.7 Перевести систему в режим загрузки изменить значение D, размещенное в ячейке с адресом 2, на 3 и перезапустить работу программы. В данном случае программа проверит данные в ячейках с адресами 1…5 и, не обнаружив среди них искомое число, завершит свою работу.

5.2 Контрольные вопросы

1. Объяснить принципы организации циклической программной структуры на учебной модели;

2. Объяснить принципы организации работы с массивом данных;

3. Объяснить структуру программы вычисления суммы чисел;

4. Объяснить структуру программы обнаружения единицы в определенном разряде среди массива данных.

Список литературы

1. Шанаев О.Т. Основы микропроцессорной техники. Методические указания к выполнению лабораторных работ по первой части курса. – Алматы: АИЭС, 2003.

2. Шанаев О.Т. Система моделирования Electronic Workbench / на казахском и русском языках. – Алматы: АИЭС, 2003.

3. Угрюмов Е. П. Цифровая схемотехника. – СПб.: БХВ-Петербург, 2004.

4. Токхайм Р. Микропроцессоры. Курс и упражнеия: Пер. с. англ. – М.: Мир, 1988.

5. Уэйкерли Дж. Ф. Проектирование цифровых устройств: Пер. с. англ. – М.: Постмаркет, 2002.

6. Хамахер К. И др. Организация ЭВМ. Пер. с. англ. – СПб.: Питер, 2003.

7. Сугано Т. Дж., Уидмер Н. С. Цифровые системы. Теория и практика: Пер. с англ. – М.: Издательский дом “Вильямс”, 2004.

Содержание

1 Практические сведения и методические рекомендации

2 Лабораторная работа. Модель MP4M

3 Лабораторная работа. Арифметические операции

4 Лабораторная работа. Логические операции

5 Лабораторная работа. Циклические программные структуры

Сводный план 2011 г., поз. 204