Некоммерческое акционерное общество

АЛМАТИНСКИЙ УНИВЕРСИТЕТ ЭНЕРГЕТИКИ И СВЯЗИ

Кафедра электроники

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ

Конспект лекций

для бакалавров специальности

5В100200 – Системы информационной безопасности

Алматы 2013

СОСТАВИТЕЛЬ: С.Н.Петрищенко. Цифровые устройства и микропроцессоры. Конспект лекций для бакалавров специальности 5В100200 – Системы информационной безопасности. - Алматы: АУЭС, 2013. – 49 с.

Приведены арифметические и логические основы цифровой техники, рассмотрены вопросы синтеза комбинационных и последовательностных устройств, а также принципы функционирования типовых микросхем комбинационных устройств, конечных автоматов и микросхем памяти. Описаны структура и система команд типового 8-разрядного микропроцессора, представлены принципы организации микропроцессорной системы, состав и принцип действия стандартного периферийного оборудования для организации параллельного и последовательного интерфейсов и таймера.

Ил. 12, табл. 5, библиогр. - 8 назв.

Рецензент: канд.тех.наук, проф. А.С.Байкенов

Печатается по дополнительному плану издания некоммерческого акционерного общества «Алматинский университет энергетики и связи» на 2012 г.

© НАО «Алматинский университет энергетики и связи» , 2013 г.

Введение

Обмен информацией в электронных системах происходит при помощи аналоговых и дискретных сигналов. Дискретные сигналы проще сохранять и обрабатывать, они меньше поддаются искажению под воздействием помехи. Кроме того, эти искажения легче обнаружить и исправить. В связи с этим, дискретные (цифровые) сигналы находят более широкое применение, чем аналоговые.

На современном этапе развития цифровая техника занимает все более монопольное положение на рынке электронных систем и устройств. Персональные компьютеры, контроллеры практически вытеснили аналоговые вычислительные машины. То же самое происходит с аппаратурой радиосвязи, радиовещания и телевидения. Однако полностью вытеснить аналоговую технику цифровая в принципе не может, так как физические процессы, от которых электронная система получает информацию, имеют аналоговую природу. В этом случае необходимы на входе и выходе цифроаналоговые и аналого-цифровые устройства.

Элементную базу цифровых устройств составляют интегральные схемы разной степени интеграции. Малые интегральные схемы (МИС) реализуют простейшие логические преобразования. На средних интегральных схемах (СИС) строят регистры, счетчики, дешифраторы, сумматоры и так далее. Появление больших и сверхбольших интегральных схем (БИС и СБИС) привело к появлению микропроцессоров (МП).

Микропроцессор способен выполнять команды, входящие в его систему команд. Меняя программу, можно решать различные задачи на одном МП. Таким образом, структура аппаратных средств не связана с характером решаемой задачи, что обеспечивает микропроцессору массовое производство.

В конспекте лекций излагаются арифметические и логические основы построения цифровых устройств, рассматриваются этапы синтеза комбинационных устройств и конечных автоматов на логических элементах и триггерах, а также принципы работы их типовых микросхем.

Рассмотрены вопросы, связанные с организацией запоминающих устройств на полупроводниковых микросхемах статического типа.

Приведены архитектура типового восьмиразрядного МП и принципы организации микропроцессорной системы с использованием разнообразного периферийного оборудования.

Лекция №1. Арифметические и логические основы цифровой техники

Содержание лекции: введение основных понятий и определений цифровой техники, арифметика и кодирование двоичных чисел, основы алгебры логики.

Цели лекции: ознакомиться с основными понятиями и определениями цифровой техники, освоить правила перевода чисел из одной системы счисления в другую и двоичной арифметики, способы кодирования двоичных чисел, а также изучить аксиомы, основные законы и правила алгебры логики.

Информация, воплощенная в некоторой материальной форме, называется сообщением или сигналом. Сигналы могут носить аналоговый (непрерывный), либо дискретный (цифровой) характер, когда изменяемая величина (функция) может иметь место только при конкретных значениях времени. Цифровые сигналы состоят только из последовательности двух цифр 1 и 0, которые называют логическими, поскольку существует раздел математики, называемый алгеброй логики, задающей правила работы с такими двоичными сигналами. Методы обработки цифровых сигналов и соответствующие устройства и системы называются цифровыми или логическими. Существуют две формы представления цифровых сигналов: потенциальная и импульсная. В первом случае наибольшей физической величине, например, напряжению соответствует логическая 1, наименьшему – логический 0 (положительная логика), если все наоборот, то имеет место отрицательная логика. Во втором случае появление импульса в определенный момент времени соответствует логической 1, его отсутствие – логическому 0. Наибольшее распространение получили цифровые устройства, реализованные в виде цифровых микросхем, использующих потенциальную форму представления цифровых сигналов, в частности, положительную логику.

Цифровая техника использует двоичную систему счисления, так как обрабатывает числа, представленные только в двоичной форме. Однако, для сокращенной формы записи двоичных чисел в микропроцессорной технике применяют восьмеричную и шестнадцатеричную системы счисления.

Система счисления – это способ записи чисел цифровыми символами. Системы счисления делят на непозиционные и позиционные. В непозиционной системе счисления значение символа не зависит от его положения в числе, а в позиционных – зависит.

Любое число в любой системе счисления можно записать в виде следующего полинома

,

,

где

q – основание системы счисления; ![]() - коэффициенты при степенях

основания (

- коэффициенты при степенях

основания (![]() );

);

![]() - веса

разрядов числа.

- веса

разрядов числа.

В двоичной системе счисления

q

= 2 и используются два коэффициента (1 и 0). Двоичное число 101101,101 можно

представить в виде следующего полинома: ![]() .

.

Двоичная арифметика очень проста. Основной арифметической операцией, которая используется в цифровых устройствах, является сложение, так как вычитание легко свести к сложению путем изменения на обратный знак вычитаемого, а умножение и деление - к операциям сложения и некоторых логических действий. Для арифметического сложения или вычитания двоичных чисел необходимо помнить, что две логические 1 не могут находиться в одном разряде, то есть они переходят в соседний старший разряд в качестве одной логической 1.

В восьмеричной системе счисления счисления

q

= 8 и используются восемь коэффициентов (0,1,2,3,4,5,6,7). Восьмеричное число ![]() можно представить в

виде следующего полинома

можно представить в

виде следующего полинома ![]() .

.

В шестнадцатеричной системе счисления

q

= 16 и используются шестнадцать коэффициентов (цифры от 0 до 9 и буквы начала

латинского алфавита A,B,C,D,E,F). Шестнадцатеричное число ![]() можно представить полиномом

можно представить полиномом ![]() .

.

Перевод дробного числа из десятичной в другую систему счисления осуществляется в два этапа:

1) переводится целая часть числа делением ее на основание системы счисления до остатка, меньшего этого основания, при этом полученное число записывается справа налево;

2) переводится дробная часть числа умножением ее на основание системы счисления до получения либо нулевого остатка после запятой, либо до заданной степени точности, при этом полученное число записывается слева от запятой сверху вниз. На рисунке 1 приведен пример перевода десятичного числа 45,75 в двоичное.

Рисунок 1 – Пример перевода десятичного числа в двоичное

Для обратного перевода достаточно сложить веса

единичных разрядов двоичного числа: ![]() .

.

В таблице 1 представлен натуральный ряд десятичных чисел в порядке возрастания, которым соответствует свой двоичный эквивалент.

Т а б л и ц а 1

|

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

|

0 |

1 |

10 |

11 |

100 |

101 |

110 |

111 |

1000 |

Продолжение таблицы 1

|

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

∙∙∙ |

|

1001 |

1010 |

1011 |

1100 |

1101 |

1110 |

1111 |

11110 |

∙∙∙ |

Недостатки данного способа кодирования десятичных чисел:

а) для увеличения диапазона однозначности десятичных чисел нужно увеличивать разрядность устройств;

б) технически трудно реализовать переход от натурального кода к десятичной системе.

Этих недостатков лишена двоично-десятичная система кодирования, которая присваивает каждой десятичной цифре от 0 до 9 свой двоичный эквивалент в виде тетрады, то есть четырехразрядного двоичного числа. При таком способе кодирования, например, десятичное число 37 можно представить, согласно таблице 1, как 0011 0111. Таким образом, при двоично-десятичном кодировании сохраняется десятичная система счисления при двоичном форме представления десятичных чисел.

Математической базой для анализа и синтеза работы цифровых устройств служит алгебра логики, в основе которой лежат три логические функции: логическое сложение (дизъюнкция), логическое умножение (конъюнкция) и логическое отрицание (инверсия). На рисунке 2 представлены логические элементы ИЛИ,И,НЕ соответственно реализующие эти функции.

При логическом сложении входных двоичных переменных выход всегда будет равен логической 1, если хотя бы на один вход логического элемента ИЛИ поступает логическая 1. На выходе будет логический 0, если на все входы поступают логические 0. При логическом умножении входных двоичных переменных выход всегда будет равен логическому 0, если хотя бы на один вход логического элемента И поступает логический 0. На выходе будет логическая 1, если на все входы поступают логические 1. При логическом отрицании выход логического элемента НЕ всегда инвертирует двоичное значение его входа. На практике большим применением пользуются комбинированные логические элементы ИЛИ-НЕ, И-НЕ, которые выполняют две логические функции: логическое сложение с отрицанием результата и логическое умножение с отрицанием результата соответственно. Логичесие элементы И,ИЛИ,НЕ составляют основной базис при построении логических устройств, а комбинированные логические элементы - универсальный базис.

Логическую функцию можно задать структурной формулой, то есть равенством, в левой части которого записана буква, обозначаюшая логическую функцию, а в правой – логическое выражение

Существуют две формы записи логических выражений: совершенная дизъюнктивная нормальная форма (СДНФ) и совершенная конъюнктивная нормальная форма (СКНФ).

СДНФ – это логическая сумма минтермов, на которых логическая функция равна единице. Минтерм – это логическое произведение входных переменных, преставленных с отрицанием или без него.

СКНФ – это логическое произведение макстермов, на которых логическая функция равна нулю. Макстерм – это логическая сумма входных преременных, представленных с отрицанием или без него.

При проектировании цифровых устройств часто требуется преобразовать структурные формулы. Для этого используют соотношения, вытекающие из аксиом и законов алгебры логики.

Рассмотрим аксиомы, справедливость которых можно подтвердить, используя правила логического сложения, умножения и инверсии.

Пусть ![]() - некоторая логическая переменная, тогда

- некоторая логическая переменная, тогда

![]()

Для логических операций сложения и умножения справедливы переместительный и сочетательный законы. У распределительного закона только первая его часть ( правило раскрытия скобок) соответствует обычной алгебре, а вторая часть ( правило взятия в скобки) имеет место только в алгебре логики.

Рассмотрим некоторые правила алгебры логики, имеющие

наибольшее практическое использование для преобразования структурных формул.

Правило де Моргана ![]() и

и

![]() Это правило

позволяет заменить логическое умножение сложением и наоборот. Правило склеивания

Это правило

позволяет заменить логическое умножение сложением и наоборот. Правило склеивания

![]() и

и ![]() На правиле склеивания

основаны графические методы карт Карно или диаграмм Вейча для минимизации

логических функций.

На правиле склеивания

основаны графические методы карт Карно или диаграмм Вейча для минимизации

логических функций.

Лекция №2. Анализ и синтез комбинационных устройств

Содержание лекции: этапы синтеза комбинационного устройства, анализ работы типовых комбинационных схем.

Цели лекции: изучить формы представления логических функций, освоить методы их минимизации и построения структурных схем, получить навыки анализа работы типовых комбинационных микросхем.

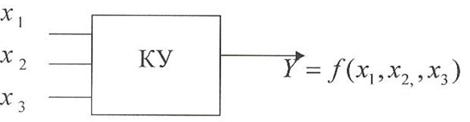

Комбинационное устройство (КУ) – это логическое устройство, выход которого определяется только состоянием его входа, то есть зависит от того, какой набор из входных переменных подается в данный момент времени. На рисунке 3 представлено КУ с тремя входами и одним выходом.

Рисунок 3 – Пример комбинационного устройства с тремя входами

Логическую функцию

![]() можно задать таблицей

истинности, которая для трех входных переменных представлена в таблице 2.

можно задать таблицей

истинности, которая для трех входных переменных представлена в таблице 2.

Т а б л и ц а 2

|

N |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

В столбцах таблицы 2 записаны возможные наборы значений входных переменных и соответствующие им заданные значения логической функции.

Логическую функцию

![]() можно

также задать структурной формулой, то есть равенством, в левой части которого

записана буква, обозначающая логическую функцию, а в правой – логическое

выражение. Запись, содержащая двоичные переменные, соединенные знаками

логического сложения, умножения и инверсии, называется логическим выражением.

можно

также задать структурной формулой, то есть равенством, в левой части которого

записана буква, обозначающая логическую функцию, а в правой – логическое

выражение. Запись, содержащая двоичные переменные, соединенные знаками

логического сложения, умножения и инверсии, называется логическим выражением.

Существуют две формы записи структурной формулы: совершенная дизъюнктивная нормальная форма (СДНФ) и совершенная конъюнктивная нормальная форма (СКНФ).

СДНФ – это логическая сумма минтермов, на которых логическая функция равна 1. Минтерм – это логическое произведение входных переменных, представленных с отрицанием и без него. По данным таблицы 2, запишем структурную формулу в виде СДНФ, причем знаки инверсии ставим над теми входными переменными, которые равны 0:

![]() .

.

Поскольку каждому набору входных переменных

соответствует свой десятичный эквивалент, то структурную формулу можно

представить в сокращенном виде ![]() .

.

СКНФ – это логическое произведение макстермов, на

которых логическая функция равна 0. Макстерм – это логическая сумма входных

переменных, представленных с отрицанием и без него. По данным таблицы 2,

запишем структурную формулу в виде СКНФ, учитывая, что знак инверсии ставится

над теми входными переменными, которые равны 1:![]()

![]() .

.

Структурная формула в сокращенном виде имеет вид ![]() .

.

Для минимизации структурных формул используются следующие методы: а) графический метод карт Карно или диаграмм Вейча при числе аргументов Х ≤ 5 ; б) при Х > 5 - метод Мак-Класки [ 6 ].

Приведем пример минимизации вышеприведенных

структурных формул методом карт Карно. Количество клеток карты определяется по

формуле ![]() , где

n – число входов.

, где

n – число входов.

На рисунке 4 приведена заполненная по таблице 2 карта Карно. Из рисунка 4 видно, что каждому набору из входных переменных Х3Х2Х1 соответствует свое значение логической функции в сооветствующей клетке.

Рисунок 4 – Карта Карно на восемь клеток

Объединять в карте можно клетки в количестве по модулю два (2,4,8,16), по горизонтали или вертикали, рядом находящиеся или на противоположных сторонах. При объединении двух клеток пропадает одна переменная, при объединении четырех клеток – две переменные, при объединении восьми клеток – три переменные, если в объединенном пространстве эти переменные принимают противоположные значения 1 и 0.

Применяя эти правила к нашему примеру, получим следующие минимизированные структурные формулы:

ДНФ : ![]() ; КНФ:

; КНФ: ![]() .

.

Анализируя полученные выражения делаем вывод, что для их схемной реализации в основном базисе (И,ИЛИ,НЕ) понадобится одинаковое число логических элементов ( пять штук). Для реализации в универсальных базисах И-НЕ или в ИЛИ-НЕ над выражениями надо поставить две инверсии и применить правило де Моргана:

![]() ,

,

![]() .

.

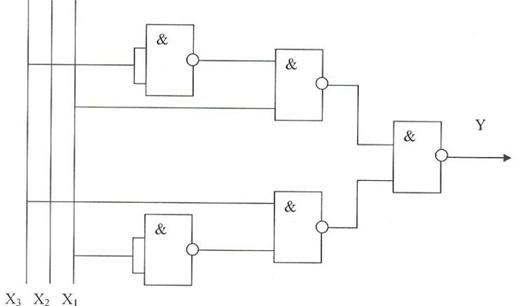

Из полученных выражений видно, что число логических операций, а значит, и логических элементов, в обоих случаях выросло до шести, однако однотипность использования логических элементов делает такую схемную реализацию более привлекательной. На рисунке 5 показан пример структурной схемы в базисе И-НЕ.

Рисунок 5 – Схема комбинационного устройства в базисе И-НЕ

Исходя из приведенного примера можно сделать вывод, что синтез КУ целесообразно разбить на ряд этапов:

1) запись условий функционирования КУ, которые задаются как логическая функция словесно, таблицей истинности или готовой структурной формулой;

2) запись и минимизация структурной формулы;

3) запись минимизированной структурной формулы в заданном базисе; 4) составление структурной схемы.

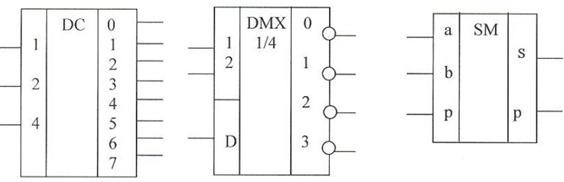

В цифровой технике при построении сложных устройств широко применяются не только отдельные логические элементы, но и их комбинации в виде типовых структур, выполняемых как единое целое в виде интегральных микросхем. На рисунке 6 представлены условные обозначения таких типовых комбинационных устройств, как дешифратор с организацией 3 на 8 и прямыми выходами, демультиплексор с организацией ¼, информационным входом D, инверсными выходами и адресными входами 1,2 и полный сумматор.

Дешифратор (DC-decoder) предназначен для распознавания кодовых комбинаций, каждой

из которых соответствует свой выход, на котором, в случае прямых выходов

фомируется логическая 1, а в случае инверсных – логический 0. Количество

выходов дешифратора определяется из соотношения ![]() , где

n – число

входов. Шифратор (CD-coder) выполняет операцию, противоположную дешифратору, то

есть кодирует поступающую на его входы информацию. Демультиплексор (DMS) используется

для передачи информации с одного информационного входа на один из выходов в

желаемом порядке. Выбор того или иного выхода осуществляется двоичным кодом,

поступающим на адресные входы. Число выходов определяется из соотношения

, где

n – число

входов. Шифратор (CD-coder) выполняет операцию, противоположную дешифратору, то

есть кодирует поступающую на его входы информацию. Демультиплексор (DMS) используется

для передачи информации с одного информационного входа на один из выходов в

желаемом порядке. Выбор того или иного выхода осуществляется двоичным кодом,

поступающим на адресные входы. Число выходов определяется из соотношения ![]() , где

, где ![]() - число адресных входов.

Мультиплексор (MS) выполняет задачу, обратную демультиплексору, то есть

передает информацию в желаемом порядке c

нескольких входов,на один выход, для чего на его

адресные входы подается соответствующий двоичный код. Сумматор (SM) –

это устройство, предназначенное для арифметического сложения двоичных или

двоично-десятичных чисел. Простейшим сумматором является сумматор по модулю

2, который выпускается под названием ИСКЛЮЧАЮЩЕЕ ИЛИ. Он имеет два

входа и один выход и способен выдавать логическую 1 только при поступлении на

его входы двух неравнозначных сигналов (1 и 0). Применяется для проверки

цифровых схем на четность или нечетность. Полный сумматор предназначен

для арифметического сложения двух одноразрядных двоичных чисел, для чего он

имеет два входа, а третий вход является входом переноса и нужен для сложения

многоразрядных чисел. Два выхода сумматора участвуют в формировании суммы и

переноса.

- число адресных входов.

Мультиплексор (MS) выполняет задачу, обратную демультиплексору, то есть

передает информацию в желаемом порядке c

нескольких входов,на один выход, для чего на его

адресные входы подается соответствующий двоичный код. Сумматор (SM) –

это устройство, предназначенное для арифметического сложения двоичных или

двоично-десятичных чисел. Простейшим сумматором является сумматор по модулю

2, который выпускается под названием ИСКЛЮЧАЮЩЕЕ ИЛИ. Он имеет два

входа и один выход и способен выдавать логическую 1 только при поступлении на

его входы двух неравнозначных сигналов (1 и 0). Применяется для проверки

цифровых схем на четность или нечетность. Полный сумматор предназначен

для арифметического сложения двух одноразрядных двоичных чисел, для чего он

имеет два входа, а третий вход является входом переноса и нужен для сложения

многоразрядных чисел. Два выхода сумматора участвуют в формировании суммы и

переноса.

Рисунок 6 – Примеры условных обозначений типовых комбинационных устройств

Лекция №3. Анализ и синтез последовательностных устройств

Содержание лекции: анализ работы типовых последовательностных схем, этапы синтеза последовательностного устройства.

Цели лекции: изучить работу триггеров, получить навыки анализа работы типовых последовательностных схем, освоить методику синтеза конечных автоматов.

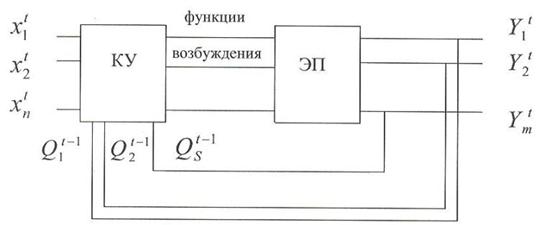

Последовательностное устройство или конечный автомат – это устройство, выход которого определяется не только состоянием его входа, но и тем состоянием, в котором оно находилось в предшествующий момент времени. На рисунке 7 представлена одна из разновидностей конечного автомата, называемого автоматом Мура.

Рисунок 7 – Схема автомата Мура

Как видно из рисунка 7, конечный автомат состоит из комбинационного устройства и элементов памяти (ЭП), в качестве которых применяют триггеры. Аналитически работу автомата можно записать как

![]() .

.

Синтез конечного автомата сводится к определению типа и количества элементов памяти, а также схемы комбинационного устройства в выбранном базисе.

Триггер – это простейший автомат, который обладает двумя устойчивыми состояниями (1 и 0) и способен переходить из одного состояния в другое под воздействием входных сигналов. При определенной комбинации входных сигналов триггер не изменяет своего состояния, то есть он способен хранить один бит информации, поэтому он является элементарной ячейкой памяти и часто используется для организации триггерных структур памяти.

По способу управления триггеры подразделяют на асинхронные, переключение которых непосредственно зависит от входных сигналов, и синхронные, переключение которых возможно только с поступлением синхроимпульса на специальный вход С, который может иметь как статическое, так и динамическое управление. В первом случае триггеры реагируют на информационные сигналы при подаче на вход С уровня логической 1 (прямой вход) или логического 0 (инверсный вход). Во втором случае триггеры воспринимают информационные сигналы при изменении сигнала на вход С от 0 до 1 (прямой динамический вход) или от 1 до 0 (инверсный динамический вход). Синхронные триггеры со статическим управлением могут иметь двухступенчатую структуру, поэтому они всегда срабатывают по заднему фронту синхроимпульса.

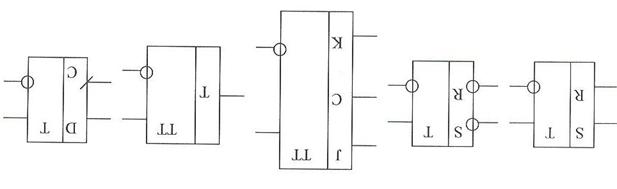

По функциональным возможностям триггеры подразделяют на асинхронные RS-триггеры с прямыми или инверсными входами, универсальный синхронный JK-триггер, Т-триггер (счетный триггер) и D-триггер (триггер задержки). На рисунке 8 соответственно представлены графические обозначения этих триггеров.

Рисунок 8 – Графические обозначения разных типов триггеров

Как видно из рисунка 8, у всех триггеров для удобства

использования предусмотрено два выхода: прямой и инверсный. Выходы триггеров

принято обозначать: буквой ![]() - прямой выход и

- прямой выход и ![]() - инверсный выход.

- инверсный выход.

Переключение RS-триггера с прямыми входами в состояние логической 1 происходит при S=1,R=0, а в состояние логического 0 при S=0, R=1, при этом вход S называется входом установки, а вход R – сбросом. При S=R=0, триггер хранит 1 бит информации, а комбинация S=R=1 – запрещена в силу неопределенности состояния триггера. RS-триггер с инверсными входами делает все наоборот.

JK-триггер реагирует на входные информационные сигналы только при поступлении прямоугольного импульса на вход синхронизации С. Переключение JK-триггера происходит так же, как у RS-триггера с прямыми входами, принимая, что J=S а K=R, за исключением одной комбинации J=R=1, при которой триггер будет переключаться в противоположное состояние при поступлении очередного синхроимпульса, а так работает Т-триггер. Отсюда вытекает способ построения Т-тиггера из JK-триггера.

D-триггер

способен задерживать прохождение информационного сигнала

cо

входа D на

выход ![]() до

поступления очередного синхроимульса, подаваемого на вход синхронизации С.

до

поступления очередного синхроимульса, подаваемого на вход синхронизации С.

Путем последовательного соединения триггеров можно построить такие типовые последовательностные устройства, как регистры и двоичные счетчики. В первом случае используют D-триггеры, во втором – T-триггеры.

Регистры предназначены для записи, хранения и выдачи информации в виде двоичного кода числа. Занесение новой информации в регистр называется записью, ее вывод – считыванием, а установка в нулевое состояние – сбросом. Если запись и считывание производятся параллельно, то есть всеми разрядами одновременно, то регистр называется параллельным. Достоинство таких регистров – высокое быстродействие. Регистр , в котором код записывается и считывается последовательно во времени, то есть разряд за разрядом, называется последовательным. Достоинство таких регистров – возможность сдвигать двоичную информацию вправо или влево.

Цифровой счетчик называется двоичным, если его

коэффициент счета (![]() )

будет равен по модулю два, то есть 2,4,8 и т.д. Коэффициент счета – это то

количество счетных импульсов, которые надо подать на вход счетчика, чтобы он

вернулся в исходное состояние. Если

)

будет равен по модулю два, то есть 2,4,8 и т.д. Коэффициент счета – это то

количество счетных импульсов, которые надо подать на вход счетчика, чтобы он

вернулся в исходное состояние. Если ![]() , где

n – целое

положительное число, то счетчик называется недвоичным. У суммирующего счетчика

исходное состояние равно нулю, а с приходом очередного счетного импульса его

состояние будет увеличиваться на 1. У вычитающего счетчика исходное состояние

равно

, где

n – целое

положительное число, то счетчик называется недвоичным. У суммирующего счетчика

исходное состояние равно нулю, а с приходом очередного счетного импульса его

состояние будет увеличиваться на 1. У вычитающего счетчика исходное состояние

равно ![]() , а с

приходом очередного счетного импульса его состояние будет уменьшаться на 1. Реверсивные

счетчики могут работать как в режиме сложения, так и вычитания.

, а с

приходом очередного счетного импульса его состояние будет уменьшаться на 1. Реверсивные

счетчики могут работать как в режиме сложения, так и вычитания.

Типовые разновидности регистров и счетчиков обычно

выпускают в виде цифровых микросхем. ![]() Нетиповые регистры или счетчики можно

синтезировать на базе логических элементов и триггеров. В качестве примера

рассмотрим синтез синхронного счетчика на базе

JK-триггеров с

Нетиповые регистры или счетчики можно

синтезировать на базе логических элементов и триггеров. В качестве примера

рассмотрим синтез синхронного счетчика на базе

JK-триггеров с ![]() = 3.

= 3.

1. Синхронный счетчик с ![]() =

3 строится на основе двоичного счетчика, состоящего из двух JK-триггеров, так

как

=

3 строится на основе двоичного счетчика, состоящего из двух JK-триггеров, так

как

n = ] log ![]() [ = ] log

3 [ » 2

,

[ = ] log

3 [ » 2

,

где n – число триггеров в счетчике;

]log![]() [

- двоичный логарифм, округленный до большого целого числа.

[

- двоичный логарифм, округленный до большого целого числа.

2. Число избыточных

состояний счетчика равно М =22 –![]() = 4 – 3 = 1,

= 4 – 3 = 1,

где: 22 – число устойчивых состояний двоичного счетчика.

3. Граф переходов счетчика и матрица переходов JK-триггера имеют вид, представленный на рисунке 9.

Вид перехода Входные сигналы

![]()

![]()

![]()

0 0 0 Ф

0 1 1 Ф

11 - избыточное состояние (*) 1 0 Ф 1

Ф – факультативное состояние 1 1 Ф 0

Рисунок 9 – Граф переходов счетчика и матрица переходов JK - триггера

4. На основании графа и матрицы строим таблицу 3.

Т а б л и ц а 3

|

Q2 |

Q1 |

J2 |

K2 |

J1 |

K1 |

||

|

|

0 |

0 |

Ф |

1 |

Ф |

||

|

0 |

1 |

1 |

Ф |

Ф |

1 |

||

|

1 |

0 |

Ф |

1 |

0 |

Ф |

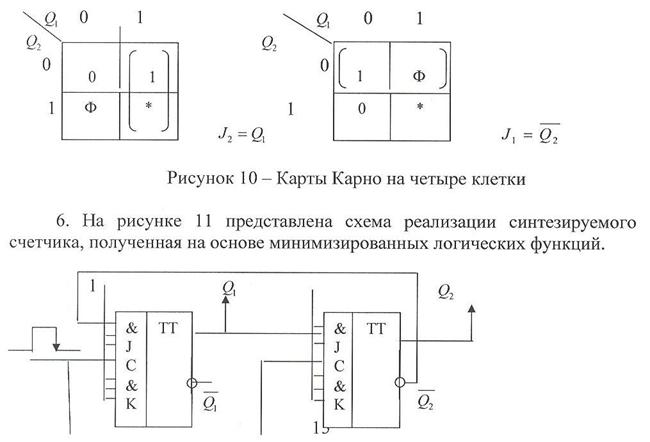

5. Полученные в таблице 3 функции возбуждения минимизируем с помощью двух карт Карно, представленных на рисунке 10.

Рисунок 11 – Схема недвоичного счетчика

Лекция №4. Полупроводниковые запоминающие устройства

Содержание лекции: виды запоминающих устройств, их параметры, структура и принцип действия оперативных и постоянных запоминающих устройств, приемы объединения микросхем памяти.

Цели лекции: изучить типы полупроводниковой памяти, ее основные параметры, структуру и принцип действия оперативных и постоянных запоминающих устройств, освоить построение памяти заданной структуры.

Для продолжительного хранения или хранения больших объемов двоичной информации используется память, состоящая из полупроводниковых микросхем, выполненных на основе биполярных или МОП-транзисторов. Память состоит из ячеек, которые имеют один или несколько элементов памяти (ЭП), каждый из которых способен запоминать 1 бит информации. Каждая ячейка памяти имеет свой адрес (номер), который должен быть указан при обращении к ней.

По способу хранения информации в ЭП различают статические и динамические запоминающие устройства (ЗУ). В статических используются бистабильные ЭП, в динамических хранение информации осуществляется за счет заряда конденсаторов, которые для обеспечения режима хранения должны периодически подзаряжаться (режим регенерации).

По виду доступа к информации различают ЗУ с произвольным или последовательным доступом. В первом случае возможно произвольное обращение к любой ячейке памяти, во втором – только в порядке возрастания или убывания их адресов, что характерно для внешней памяти.

По выполняемой функции ЗУ можно классифицировать на оперативные запоминающие устройства (ОЗУ) и постоянные запоминающие устройства (ПЗУ). ОЗУ (обозначение микросхем RAM – random access memory) используются для хранения информации, получаемой в процессе работы устройства. Они могут работать в режимах записи и считывания информации и являются энергозависимыми, так как при отключении источника питания информация в них пропадает. ПЗУ хранят информацию, которая не должна изменяться в ходе работы. Они работают только в режиме считывания и энергонезависимы. По способу программирования микросхемы ПЗУ подразделяют на четыре группы:

1) масочные (ROM), однократно программируемые изготовителем по способу заказанного фотошаблона (маски);

2) с возможностью однократного электрического программирования (PROM) по способу пережигания плавких перемычек на кристалле;

3) с возможностью многократного электрического программирования (EEPROM);

4) с электрической записью и ультрафиолетовым стиранием (EPROM), для чего в крышке корпуса микросхемы имеется окошко.

Основные параметры ЗУ делят на три группы:

1) классификационные: а) N – число ячеек памяти; б) n – разрядность, определяется числом разрядов двоичного числа, хранимого в ячейке; 3) М = N∙n – информационная емкость, измеряемая в байтах (1байт – 8 бит), килобайтах (1Кбайт = 1024 байт),мегабайтах (1Мбайт = 1024 Кбайт), гегабайтах (1Гбайт = 1024 Мбайт) и т.д.;

2) статические: а) напряжение источника питания ; б) напряжение логической единицы; 3) напряжение логического нуля;

3) динамические: а) время выборки – интервал времени между подачей входного сигнала и получением на выходе данных; б) период следования тактовых импульсов.

|

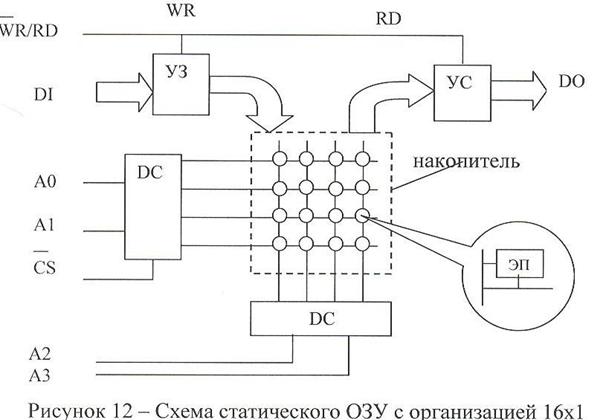

Для обращения к микросхеме требуется ко входам дешифраторов столбцов и строк подвести четырехразрядный код адреса (А3,А2,А1,А0) выбранного ЭП, а также инверсный сигнал «Выборка кристалла» (CS), разрешающий обращение к накопителю. Режим микросхемы устанавливается сигналом «Запись – считывание» (WR/RD ). При WR/RD = 0 открывается устройство записи (УЗ) и через информационный вход DI (data input) происходит запись двоичного числа в выбранный ЭП. При WR/RD = 1 открывается устройство считывания (УС) и двоичное число считывается из активизированного ЭП через информационный выход DO (data output).

На рисунке 13 изображена структура типового восьмиразрядного ПЗУ емкостью 29=512 байт =4096 бит, которая хорошо иллюстрирует принципы построения и функционирования ПЗУ. В узлах матрицы 64х64 размещается полупроводниковый прибор (диод, транзистор) с плавкой вставкой (PROM) или без нее (ROM).

Рисунок 13 - Структура восьмиразрядного ПЗУ емкостью

29=512 байт

В каждом угле контакт между адресной и разрядной шинами может быть нарушен посредством разрушения полупроводникового прибора и вставки.

У ПЗУ типа PROM в узлах матрицы наносится слой нитрида кремния, который хорошо хранит электрический заряд. Время обращения зависит от технологии изготовления БИС запоминающих устройств и для биполярных ПЗУ составляет 20….50 нс, для биполярных - 200….600 нс.

В таблице 4 приведены основные параметры некоторых микросхем ОЗУ (обозначение РУ) и репрограммируемых ПЗУ ( обозначения РР при электрическом стирании и РФ – при ультрафиолетовом).

Т а б л и ц а 4

|

Обозна-чения микросхем |

Органи- зация |

Время цикла, нс |

Время хранения, Час |

Число циклов

|

Удель- ная Рпот, мВт/бит |

Техно-логия |

|

К500РУ415 |

1Кх1 |

25 |

|

|

0,8 |

ЭСЛ |

|

К541РУ3 |

16Кх1 |

150 |

|

|

0,03 |

И2Л |

|

К573РУ9А |

2Кх8 |

400 |

|

|

0,0005 |

К-МОП |

|

К565РУ5Б |

64Кх1 |

230 |

|

|

0,0003 |

n-МОП |

|

К573РР2 |

2Кх8 |

|

15000 |

10000 |

0,02 |

n-МОП |

|

К573РФ2 |

2Кх8 |

|

25000 |

100 |

0,012 |

n-МОП |

|

К573РФ6А |

8Кх8 |

|

5 лет |

25 |

0,004 |

n-МОП |

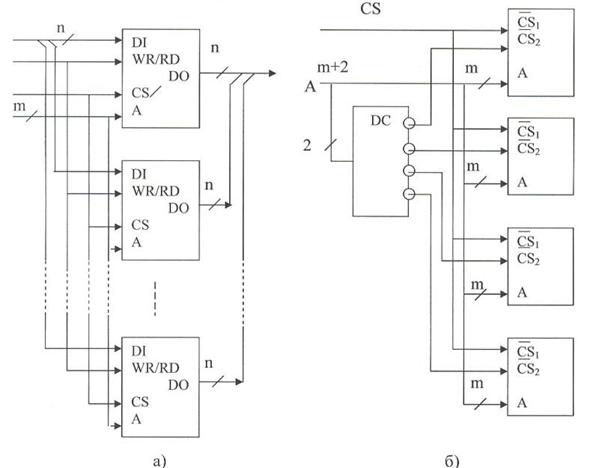

Создание запоминающего устройства может потребовать объединения однотипных микросхем для увеличения разрядности чисел или общей емкости их хранения. В первом случае на адресные шины всех микросхем параллельно подаются группы кодов адресов этой части микросхем, а на входы управления также параллельно требуемые сигналы управления. Как видно из рисунка 14а, информационные входы и выходы объединяются в соответствующие информационные шины, причем разрядности объединяемых микросхем суммируются.

Рисунок 14 – Схемы объединения однотипных микросхем

На рисунке 14б показан один из вариантов объединения для четырех микросхем с целью увеличения общей емкости хранимых чисел. В данном случае значения двух старших разрядов (m+2) – разрядной шины адреса А обеспечивают обращение к одной из микросхем. Остальные m разрядов подаются параллельно на адресные входы всех микросхем. Благодаря такому включению любой m – разрядный код, поданный на эти входы, будет адресовать по одной ячейке памяти в каждой микросхеме, а выбираться будет та из них, которая находится в микросхеме с разрешающим значением сигнала CS2.

Лекция №5. Структура и принцип действия типового однокристального микропроцессора

Содержание лекции: состав, структура и принцип действия 8-разрядного однокристального микропроцессора, назначение основных узлов.

Цели лекции: изучить основной состав типового микропроцессора, его структуру и принцип действия, освоить назначение основных узлов.

Развитие микроэлектронной технологии привело к появлению микросхем большой и сверхбольшой степени интеграции (БИС и СБИС), которые стали основой для создания микропроцессоров (МП). МП – это программно-управляемое устройство, предназначенное для обработки цифровой информации и управления процессом этой обработки, реализованное в виде одной (однокристальный МП) или нескольких БИС или СБИС (модульный МП). Под обработкой цифровой информации понимается выполнение некоторых арифметических и логических операций. Исходя из определения, данному МП, он должен состоять из арифметико-логического устройства (АЛУ) и устройства управления процессором (УУП). Кроме того, ему необходима внутренняя память, реализованная на регистрах общего назначения (РОН), для хранения кодов и адресов команд и операндов (двоичные слова, участвующие в операциях). На рисунке 15 представлен основной состав МП и внешнее оборудование, необходимое для его нормального функционирования.

|

|

Рисунок 15 – Упрощенная схема типовой микропроцессорной системы

Как видно из рисунка 15, в качестве внешнего оборудования используются:

а) память (ОЗУ и ПЗУ) для хранения программ и данных;

б) внешние запоминающие устройства (ВЗУ) для увеличения объема памяти (накопители на магнитных лентах, дисках);

в) специальные устройства, предназначенные для ввода в МП или вывода из него информации (УВВ);

г) блок управления для координации управления всех вышеперечисленных узлов.

Функционирование процессора происходит в следующем порядке:

1) выборка из памяти команды;

2) анализ кода операции и определение ее типа, количества операндов;

3) вычисление адресов и выборка из памяти операндов;

4) выполнение команды;

5) переход к адресу следующей команды и повторение цикла.

Для изучения основных принципов работы МП выберем наиболее простую его модель фирмы Intel i8080А (аналог - К580ВМ80А) или i8085 (аналог – К1821ВМ85А). Несмотря на свой многолетний возраст, эти МП до сих пор встречаются в каталогах фирм и применяются в системах управления различной аппаратурой, где возможностей микропроцессора хватает.

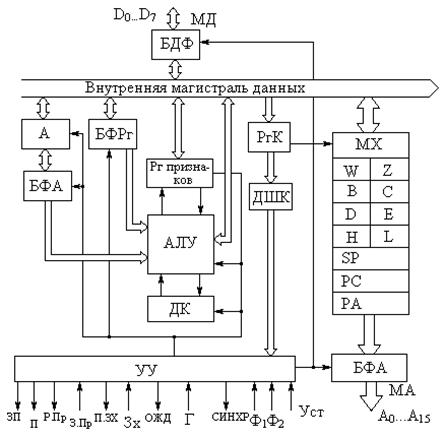

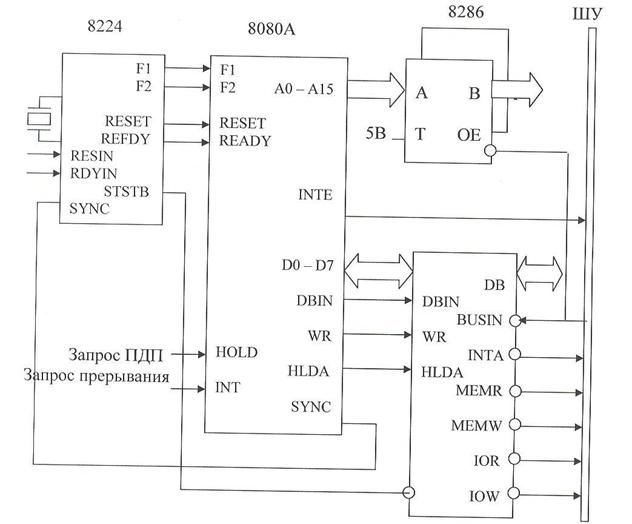

На рисунке 16 представлена структурная схема однокристального восьмиразрядного МП i8080A, из которой видно, что МП связан с внешним оборудованием через магистральную систему шин: однонаправленной 16-разрядной магистралью адреса (МА), двунаправленной 8-разрядной магистралью данных (МД) и 12 сигналами управления по шине управления (6 входных и 6 выходных).

Данный МП рассчитан на выполнение логических и арифметических операций с 8-разрядными числами в двоичной и двоично-десятичной системах счисления, а также операций с двойной разрядностью.

Функциональное назначение внешних выводов МП следующее:

А0...А15 - адресная магистраль, обеспечивающая адресацию любой из 216 8-разрядных ячеек памяти или внешнего устройства (ВУ);

Д0...Д7 - двунаправленная магистраль данных, используемая для обмена информацией с памятью или ВУ;

СИНХР (SYNC) - выход сигнала СИНХРОНИЗАЦИЯ появляется в начале каждого машинного цикла для временного согласования МП с ВУ;

П (DBIN) – выход сигнала ПРИЕМ указывает на готовность к приему данных, выданных из памяти или ВУ;

ОЖД – выход сигнала ОЖИДАНИЕ указывает на то, что МП находится в режиме ожидания готовности ВУ к работе;

ЗП (WR) - выход сигнала ЗАПИСЬ указывает, что данные выданы МП и установлены на МД, т.е. могут быть записаны в память или переданы в ВУ;

Зх (HOLD) - вход сигнала ЗАХВАТ указывает на запрос ВУ на управление МА и МД;

П.ЗХ.(HLDA) - выход сигнала ПОДТВЕРЖДЕНИЕ ЗАХВАТА указывает на перевод МД и MA в состояние высокого сопротивления, используется при режиме прямого доступа к памяти;

З.Пр.(INT) - вход сигнала ЗАПРОС ПРЕРЫВАНИЯ, поступает от внешнего устройства с требованием прерывания основной программы и перехода на выполнение подпрограммы обслуживания прерывания;

Р.Пр.(INTE) - выход сигнала РАЗРЕШЕНИЕ ПРЕРЫВАНИЯ указывает на состояние внутреннего триггера разрешения прерывания МП;

Г (READY) - сигнал ГОТОВ информирует о готовности ВУ к обмену информацией с МП. При Г = 0 МП будет находиться в состоянии ОЖД;

УСТ (RESET) – вход СБРОС, для сбрасывания в 0 счетчика команд и передачи в регистр адреса нулевого адреса первой команды;

Ф1 и Ф2 - входы для подачи тактовых противофазных сигналов Ф1 и Ф2 , которые определяют тактовую частоту работы МП (2,08; 2,63; 3,125).

|

|

Рисунок 16 - Структурная схема однокристального МП i8080A

Микропроцессор i8080A состоит из следующих функциональных блоков:

1) блока регистров общего назначения PОH;

2) арифметико-логического блока АЛБ;

3) регистра команд РгК;

4) устройства управления УУ;

5) буферов магистрали данных - БФД и магистрали адреса - БФА.

Блок PОH включает в себя шесть программно-доступных регистров: В, С, D, Е, Н, L. Их можно использовать как отдельные 8-разрядные регистры или как три 16-разрядных регистра ВС, DЕ, HL. Регистры W и Z не доступны программисту и используются для выполнения команд внутри МП.

Программный счетчик PC содержит текущий адрес памяти. Содержимое PC автоматически изменяется в течение каждого цикла команды. Указатель стека SP содержит адрес последней записанной в стек информации. PA - регистр для хранения адреса памяти. MX - двунаправленный мультиплексор для связи РОН с магистралью данных.

АЛБ включает в себя 8-разрядное АЛУ, схему десятичной коррекции ДК, 5-разрядный регистр признаков, аккумулятор А, буфер аккумулятора БФА и буферный регистр БФРг. АЛБ осуществляет арифметические операции сложения и вычитания, логические операции И, ИЛИ, ИСКЛЮЧАЮЩИЕ ИЛИ и сдвиги. При проведении операций одно число всегда берется из БФА, а другое - из БФРг.

По результату выполнения арифметическо-логических операции АЛБ устанавливает в регистре признаков один из пяти разрядов:

1) бит переноса C устанавливается в состояние логической 1 при переносе из старшего разряда числа при выполнении арифметических операций, а при операциях сдвига – в состояние, соответствующее содержимому выдвигаемого из аккумулятора разряда;

2) ополнительный признак переноса (при обработке двоично-десятичных чисел) хранит при выполнении операции перенос из 4-го разряда;

3) бит знака устанавливается в состояние, соответствующее значению старшего разряда операции АЛУ;

4) бит нулевого признака устанавливается в состояние логической 1, если результат операции АЛУ равен нулю;

5) разряд признака четности устанавливается в состояние логической 1, если число единиц в разрядах результата четное.

Регистр команд РгК и дешифратор команд ДШК используются в МП для получения и дешифрации кода команды.

Устройство управления совместно с дешифратором формирует управляющие сигналы для всех внутренних блоков микропроцессора, а также его выходные сигналы управления и состояния.

Буферы МД и МА обеспечивают хранение соответственно данных и адресов на время, необходимое для их обработки.

Выполнение каждой команды производится МП в строгой последовательности, определяемой кодом команды, и синхронизируется во времени сигналами Ф1 и Ф2 тактового генератора. Период синхросигналов Ф1 и Ф2 называется машинным тактом. Машинный цикл - время, требуемое для извлечения одного байта информации из памяти или выполнения команды, определяемой одним машинным словом. Машинный цикл может состоять из 3...5 машинных тактов. Время выполнения команды - время получения, декодирования и выполнения команды. В зависимости от вида команды оно может состоять из I...5 машинных циклов.

Лекция №6. Типовые схемы сопряжения микропроцессорной системы

Содержание лекции: структура, принцип действия и характеристики вспомогательных схем сопряжения центрального процессора..

Цели лекции: - изучить структуру и работу вспомогательных микросхем, предназначенных для сопряжения МП с внешним оборудованием, получить навыки составления структуры процессора на их основе.

МП через систему шин подключается к внешнему оборудованию, образуя микропроцессорную систему (МПС), как показано на рисунке 15. Обработкой информации, управлением потока и интерпретации команд, а также управлением работы шин занимается МП. Функции хранения информации выполняет постоянная и оперативная память. Связь с внешними устройствами осуществляют модули, называемые портами «ввода-вывода».

Для стандартного подключения к МП портов внешних устройств и памяти служат схемы сопряжения МП с внешним оборудованием.

Нагрузочная способность МП i8080A по шинной магистрали данных для сигнала логического нуля составляет всего 1,8 мА, а для логической единицы – 0,15 мА. Если суммарная нагрузка по МД или МА будет превышать эти величины, то для электрического сопряжения в микропроцессорной системе необходимо использовать шинные усилители-формирователи, которые позволяют:

а) обеспечить заданную нагрузочную способность шин при одно- и двунапрвленной передаче информации;

б) подключить к МПС удаленные элементы без существенного ухудшения характеристик;

в) согласовывать уровни сигналов между элементами, выполненными на базе различных технологий (ТТЛ, КМОП, n-МОП и т.д.).

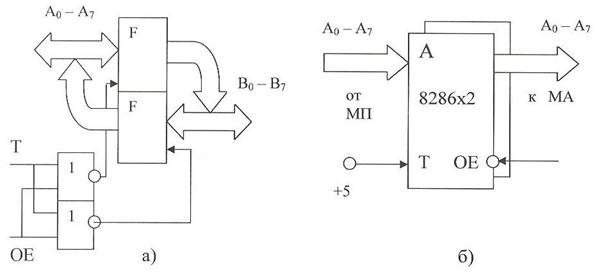

В микропроцессорном комплекте i8080A имеются БИС 8286 и 8287 (ВА86 и ВА87 – аналоги), которые представляют собой восьмиразрядные двунаправленные шинные формирователи (ШФ), имеющие два канала А (входы) и В (выходы), один из которых подключается к МП, а другой – к системной магистрали, причем выходы с тремя состояниями у первой микросхемы – прямые, а второй – инверсные.

Из рисунка 17а, на котором показана функциональная схема ШФ 8286, видно, что управление направлением передачи и ее отключением осуществляется управляющими сигналами T (Transmitter) и OE (Output Enable), подаваемыми на входы усилителей F, соответственно. Передача информации разрешена при OE = 0, причем, если T = 1, то направление передачи от МП к МД. При OE = 1 выходы обоих каналов переводятся в третье состояние, когда выходные усилители отключены. ШФ имеют малую нагрузку по входам (0,2 мА при низком входном уровне) и высокую нагрузочную способность выходов (12 мА для выходов А и 32 мА для выходов В при низком уровне выходного сигнала). На рисунке 17б показан пример организации адресной магистрали на двух микросхемах ШФ.

Рисунок 17 - Организации адресной магистрали на шинных формирователях

В МПС для подключения к магистрали часто используют буферные регистры (БР), которые представляют собой универсальные восьмиразрядные регистры на D – триггерах с тремя состояниями на выходе. В отличие от ШФ буферные регистры способны хранить данные. Благодаря этому они могут выполнять временную буферизацию данных, что составляет важнейшую функцию портов. БФ с тремя состояниями на выходах регистра обеспечивают портам возможность отключения от магистрали по действием управляющих сигналов, а также необходимую нагрузочную способность.

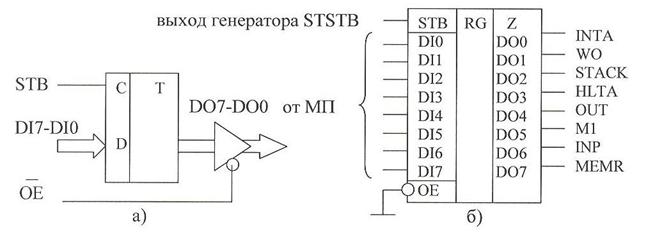

В микропроцессорном комплекте i8080A имеются восьмиразрядные буферные регистры 8282 и 8283 (инвертирующий), которые имеют аналоги ИР82 и ИР83 в серии КР580. На рисунке 18 представлены структурная схема (а) и условное обозначение регистра 8282 (б).

Рисунок 18 – Структура буферного регистра и его условное обозначение

Из рисунка 18 видно, что БР имеет информационные входы DI0…DI7, выходы усилителей с тремя состояниями DO0…DO7, разрешающий вход строба STB (Strobe), по которому происходит запись информации в регистр (при STB = 0 – режим хранения), и вход ОЕ, низкий уровень сигнала на который разрешает чтение информации по выходам, а высокий уровень сигнала переводит выходы в состояние «отключено».

МП в первом такте каждого машинного цикла выставляет на МА байт своего состояния, который сигналом SYNC записывается в регистр состояния для дальнейшего использования при формировании управляющих сигналов, обращения к ОЗУ и организации различных режимов работы МПС.

На рисунке 18б показана схема включения БР в качестве регистра состояния, на выходе которого формируются десять битов состояния: INTA – подтверждение прерывания; WO – запись – вывод; STACK – стек; HLTA – подтверждение останова; OUT – вывод; M1 – цикл М1; INP – ввод; MEMR – считывание из памяти.

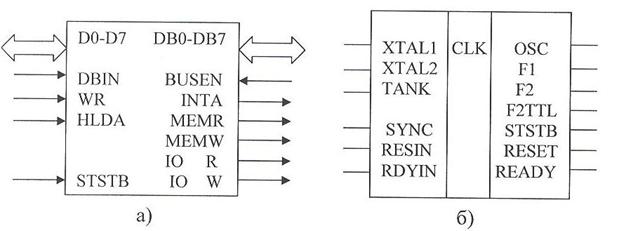

Для упрощения интерфейса центрального процессора разработаны специальные БИС системного контроллера (СК) 8226/28/38 (аналоги: КР580ВК26/28/38), которые осуществляют формирование выходных сигналов МД и сигналов управления ОЗУ и усройств ввода-вывода.

На рисунке 19а показана схема подключения СК 8226. Микросхема содержит двунаправленный магистральный формирователь, регистр состояния и схему формирования управляющих сигналов. Формирователь управляется сигналами, подаваемыми на входы DBIN, HLDA с соответствующих выходов МП, и внешним сигналом размещения магистрали, подаваемым на вход BUSEN (bas enable) с системы прямого доступа памяти (ПДП). Сигнал высокого уровня на входе BUSEN устанавливает все входы контроллера в высокоимпедансное состояние. Байт состояния запоминается по стробу, подаваемому на вход STSTB с одноименного выхода генератора тактовых импульсов (ГТИ), реализованного на микросхеме 8224 (аналог – КР580ГФ24), условное обозначение которого показано на рисунке 19б.

Рисунок 19 – Схемы системного контроллера и генератора импульсов

ГТИ предназначен для синхронизации микропроцессорной системы на основе соответствующего комплекта. Генератор формирует тактовые импульсы частотой до 2,5 МГц с амплитудой 12В, Назначение выводов микросхемы генератора следующее:

SYNC – вход синхронизации начала цикла от МП;

RESIN – входной сигнал сброса;

RDYIN – вход сигнала готовности ВУ для работы с МП;

OSC – выход гармонического сигнала;

F1,F2 – выходы тактовых импульсов;

STSTB – строб состояния (для фиксации байта состояния МП);

RESET – выходной сигнал сброса;

READY – выходной сигнал готовности.

На рисунке 20 показан один из вариантов построения структуры центрального процессора 8080А на базе вспомогательных БИС соответствующего комплекта.

Рисунок 20 - Структура модуля центрального процессора 8080А

Лекция №7. Система команд однокристального микропроцессора

Содержание лекции: форматы команд, способы адресации, система команд, форма написания программы на языке ассемблера.

Цели лекции: изучить форматы команд, основные способы их адресации, разобраться с механизмом действия команд.

Для того чтобы МП выполнил серию последовательных операций нужна программа. Если она написана на языке высокого уровня, например, на PL/M или СИ, то необходимо знать только язык программирования. При написании программы на языке ассемблера необходимо знать систему команд, то есть знать, какие операции выполняются МП.

Восьмиразрядный МП 8080А имеет вполне определенное количество команд, равное 78, поэтому его называют МП с жесткой системой команд, наращивать и изменять которые нельзя.

Каждая команда имеет определенную структуру (формат), в которой можно выделить поле кода операции (КОП) и поле операнда, определяющее числа (операнды), участвующие в операции в соответствии с КОП. Для команд используются три вида формата:

1) однобайтный, в котором несколько старших разрядов отводится под КОП, а остальные под адресацию операндов;

2) двухбайтный, в котором первый байт отводится под КОП, а второй – под восьмиразрядный операнд или номер устройства ввода-вывода;

3) трехбайтный, в котором первый байт отводится под КОП, а второй и третий – под шестнадцатиразрядный операнд или адрес ячейки памяти.

Способ определения операнда на основе структуры команды называется способом адресации. Использование нескольких способов адресации расширяет возможности при составлении программы. Выбор того или иного способа адресации определяется:

- минимальным объемом памяти для хранения программы;

- наименьшим временем выполнения программы;

- набором команд, которыми располагает данный МП.

Поскольку техника адресации редко удовлетворяет сразу обоим первым требованиям, находят компромиссное решение.

Наибольшее распространение получили следующие способы адресации:

а) прямая адресация. При этом способе адресации за КОП должен следовать адрес данных, участвующих в операции. Этим адресом может быть адрес памяти (трехбайтная команда), имя регистра (однобайтная команда), номер порта ввода или вывода (двухбайтная команда);

б) непосредственная адресация. При этом способе адресации операнд сразу следует за КОП., то есть его не надо искать, он находится в «теле» команды. Операнды хранятся в памяти непосредственно за ячейкой, содержащей КОП. Команды с непосредственной адресацией бывают двухбайтные (КОП – восьмиразрядный операнд) и трехбайтные (КОП – шестнадцатиразрядный операнд);

в) косвенная адресация. При этом способе адресации фактически используются два адреса. Первый трехразрядный адрес находится в «теле» команды и является символическим именем одного из регистров регистровой пары, в которой находится второй шестнадцатиразрядный адрес операнда, хранимого в ячейке памяти. Команды косвенной адресации обычно имеют однобайтный характер. Косвенная адресация часто сочетается с другими видами адресации, например, непосредственная косвенно-регистровая адресация.

Условно систему команд можно разбить на пять групп:

1) команды пересылок;

2) команды арифметических операций;

3) команды логических операций;

4) команды перехода;

5) специальные команды.

В дальнейшем, при написании команд используется символический язык и приняты следующие обозначения: R – один из РОН (B,C,D,E,H,L) или аккумулятор; RP – одна из регистровых пар (BC,DE,HL,SP): D8 – восьмиразрядный операнд; D16 – шестнадцатиразрядный операнд. В таблице 5 представлены трехразрядные коды, соответствующие именам регистров общего назначения и ячейке памяти М (memory), адрес которой определяется содержимым регистровой пары HL.

Т а б л и ц а 5

|

РОН и М |

B |

C |

D |

E |

H |

L |

M |

A |

|

Коды |

000 |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

Команды пересылок осуществляют передачу данных из одного блока в другой, при этом сначала определяют приемник, а потом источник данных. Если работают с ячейкой памяти, то ее адрес определяется содержимым регистровой пары HL (старший байт в H, а младший – в L). Рассмотрим действие некоторых команд пересылок:

![]() MOV Rd,Rs;

Rd Rs – отправка содержимого регистра источника (Rs) в

регистр приемник (Rd);

MOV Rd,Rs;

Rd Rs – отправка содержимого регистра источника (Rs) в

регистр приемник (Rd);

![]() MVI R,D8;

R D8 – отправка

восьмиразрядного операнда в регистр R;

MVI R,D8;

R D8 – отправка

восьмиразрядного операнда в регистр R;

![]() LDA D16;

A M (D16); - загрузка в аккумулятор содержимого ячейки

памяти, адрес которой определяется числом

D16;

LDA D16;

A M (D16); - загрузка в аккумулятор содержимого ячейки

памяти, адрес которой определяется числом

D16;

![]() LXI RP,D16;

RP

D16 – загрузка регистровой пары

RP числом

D16;

LXI RP,D16;

RP

D16 – загрузка регистровой пары

RP числом

D16;

![]() OUT D8; ПОРТ(D8)

A – содержимое аккумулятора

передается в порт с номером D8;

OUT D8; ПОРТ(D8)

A – содержимое аккумулятора

передается в порт с номером D8;

![]() IN D8;

A ПОРТ(D8) – содержимое

порта с номером D8 передается в аккумулятор.

IN D8;

A ПОРТ(D8) – содержимое

порта с номером D8 передается в аккумулятор.

![]()

![]()

![]() PUSH RP;

SP – 1

Rh;

SP – 2

Rl;

SP

SP – 2 – содержимое старшего регистра (Rh) регистровой

пары отправляется в ячейку памяти по адресу, который на единицу меньше содержимого

указателя стека SP, а содержимое младшего регистра (Rl) –

в ячейку памяти, адрес которой меньше содержимого

SP на два.

PUSH RP;

SP – 1

Rh;

SP – 2

Rl;

SP

SP – 2 – содержимое старшего регистра (Rh) регистровой

пары отправляется в ячейку памяти по адресу, который на единицу меньше содержимого

указателя стека SP, а содержимое младшего регистра (Rl) –

в ячейку памяти, адрес которой меньше содержимого

SP на два.

![]()

![]()

![]() POP RP;

Rl

SP;

Rh

SP +

1; SP

SP + 2 - содержимое ячейки памяти, адрес которой

определяется содержимым SP, засылается в

Rl, а содержимое

ячейки памяти, адрес которой на единицу меньше содержимого

SP

засылается в Rh. Содержимое регистра

SP

увеличивается на два.

POP RP;

Rl

SP;

Rh

SP +

1; SP

SP + 2 - содержимое ячейки памяти, адрес которой

определяется содержимым SP, засылается в

Rl, а содержимое

ячейки памяти, адрес которой на единицу меньше содержимого

SP

засылается в Rh. Содержимое регистра

SP

увеличивается на два.

Команды арифметических операций выполняются в АЛУ МП. К ним относятся операции сложения и вычитания. Один из операндов при этих операциях всегда помещается в аккумулятор, а второй операнд помещается в регистр или ячейку памяти. Результат операции помещается в аккумулятор, стирая операнд, который раньше там хранился. К командам арифметического сложения относятся:

![]() ADD R;

A

A +

R - сложение содержимого аккумулятора с содержимым

заданного регистра;

ADD R;

A

A +

R - сложение содержимого аккумулятора с содержимым

заданного регистра;

![]() ADI D8;

A

D8 +

A – сложение числа

D8 с содержимым

аккумулятора;

ADI D8;

A

D8 +

A – сложение числа

D8 с содержимым

аккумулятора;

![]() ADC R;

A

A +

R +

CY – сложение операндов с учетом признака переноса СY;

ADC R;

A

A +

R +

CY – сложение операндов с учетом признака переноса СY;

![]() INR R;

R R + 1 – инкремент, или увеличение на единицу

содержимого регистра или ячейки памяти.

INR R;

R R + 1 – инкремент, или увеличение на единицу

содержимого регистра или ячейки памяти.

К командам вычитания относятся:

![]() SUB R;

A

A –

R – вычесть

из содержимого аккумулятора содержимое регистра или ячейки памяти;

SUB R;

A

A –

R – вычесть

из содержимого аккумулятора содержимое регистра или ячейки памяти;

![]() SUI D8;

A

A –

D8 - вычесть из содержимого аккумулятора

восьмиразрядное двоичное число;

SUI D8;

A

A –

D8 - вычесть из содержимого аккумулятора

восьмиразрядное двоичное число;

![]() SBB R;

A

A –

R –

CY – вычитание операндов с учетом признака переноса

CY

(заем);

SBB R;

A

A –

R –

CY – вычитание операндов с учетом признака переноса

CY

(заем);

![]() DCR R;

R

R – 1 – декремент или уменьшение на единицу содержимого

регистра или ячейки памяти.

DCR R;

R

R – 1 – декремент или уменьшение на единицу содержимого

регистра или ячейки памяти.

Команды логических операций позволяют выполнять следующие действия:

![]() ANA R;

A

A

ANA R;

A

A ![]() R – логическое умножение И;

R – логическое умножение И;

![]() ORA R;

A

A

ORA R;

A

A ![]() R – логическое

сложение ИЛИ;

R – логическое

сложение ИЛИ;

![]() XRA R;

A

A

XRA R;

A

A ![]() R - исключающее

ИЛИ;

R - исключающее

ИЛИ;

![]()

![]() CMA –

А А – обратный код

содержимого аккумулятора;

CMA –

А А – обратный код

содержимого аккумулятора;

CMP R; A – R – сравнение двух чисел;

RLC – циклический сдвиг влево на один разряд, причем старший разряд замещает младший и одновременно разряд триггера переноса;

RRC - циклический сдвиг вправо на один разряд, причем младший разряд замещает старший и одновременно разряд триггера переноса.

Команды передачи управления предназначены для изменения нормального последовательного хода программы путем ее прерывания подачей одной из команд передачи управления. Рассмотрим два типа команд:

1) безусловные, по которым переход в программе осуществляется по адресу, который указывается в команде. Например, команда JMP D16 отправляет по адресу D16;

2) условные, по которым переход осуществляется только при появлении какого-либо условия, формируемого регистром признаков: NZ – не нуль, Z – нуль, NC – нет переноса, C – перенос, PO – нечетность, PE – четность, P – плюс, M – минус. Прибавляя символ условного перехода J к обозначению того или иного признака получаем команду условного перехода. Например, команда JNZ D16 выполняется при ненулевом результате предыдущей операции и отправляет по адресу D16.

Специальные команды не передают и не обрабатывают информацию, а используются для управления МП. Команда HLT позволяет остановить выполнение программы, а команда NOP не задает выполнение операции, а позволяет перейти к очередной команде с задержкой на четыре такта Т. Команды EI и DI обеспечивают программное разрешение или запрет режима прерывания соответственно.

Достоинством языка ассемблера является то, что все элементы программы представлены в символической форме, отражающей их содержательный смысл. Преобразование символических имен команд в двоичные коды возлагается на специальную программу – ассемблер. При наличии в программе синтаксических ошибок ассемблер в процессе трансляции выдает сообщения об ошибках.

Каждая строка ассемблера соответствует одной команде или директиве и может содержать четыре поля:

МЕТКА КОД ОПЕРАНД КОММЕНТАРИЙ

STORE: STA 8000H Запомнить содержимое

аккумулятора в ячейке памяти с адресом 8000

MVI С,ОАН Загрузить в регистр С число A

MASK EQU 0FH Директива эквивалентность

Метка используется для символического обозначения адреса перехода команд передачи управления. Поле КОД содержит символическое имя выполняемой команды или директивы. Поле ОПЕРАНД определяется в зависимости от поля КОД и может содержать один или несколько операндов, разделенных запятой, в качестве которых используются данные и символические обозначения внутренних регистров МП. Поле КОММЕНТАРИЙ содержит пояснение тех действий, которые производятся командой. Содержание этого поля ассемблером игнорируется.

Лекция №8. Принципы организации микропроцессорной системы

Содержание лекции: модульный принцип построения микропроцессорной системы, интерфейс, варианты шинной организации, способы программно-управляемого обмена, адаптеры программируемых параллельного и последовательного ввода-вывода.

Цели лекции: изучить основные понятия и приемы, используемые при организации МПС, познакомиться с тремя способами программно-управляемого обмена, оценить работу параллельного и последовательного интерфейсов.

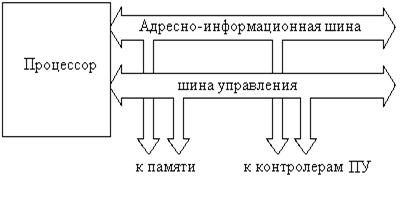

При реализации современных МПС широко используется модульный принцип, в соответствии с которым МПС строится из набора устройств и блоков - модулей, реализующих законченные функции и обладающих свойством независимости от других модулей. Для соединения модулей между собой служат проводники для передачи сигналов - шины. Шины, объединенные по функциональному признаку, называются магистралью. Совокупность шин, связывающих два модуля и алгоритм, определяющий порядок обмена информацией между ними, называется интерфейсом. Интерфейс характеризуют его ширина (максимальная разрядность передаваемых по нему данных) и скорость (бит/с).

На рисунке 21 показано использование единого (системного) интерфейса, к которому подключаются все устройства, входящие в состав МПС. Периферийные устройства (ПУ) подключаются к единому интерфейсу через контроллер, предназначенным для управления ПУ. Каждый тип ПУ требует применения специфичного контроллера. ПУ подключается к контроллеру с помощью интерфейса устройства.

|

|

Рисунок 21 – Схема использования единого интерфейса

Применение единого интерфейса обуславливает следующие правила обмена информацией:

1) информация передается словами, ширина интерфейса обычно равна длине слова памяти;

2) в каждый момент времени обменивается информацией одна пара устройств - источник и приемник;

3) прямой обмен информацией между двумя ПУ невозможен: источником или приемником информации всегда является процессор или память.

Для шинной организации МПС используются двухшинная или трехшинная структуры. На рисунке 22 показана двухшинная структура. Сокращение количества шин достигается за счет объединения адресной шины и шины данных. При этом возникает так называемая мультиплексируемая шина, по которой в одни моменты времени передаются адреса, а в другие - данные. Это позволяет значительно сократить количество выводов МП БИС.

|

Рисунок 22 – Двухшинная организация микропроцессорной системы

Во всех МПС применяется программно-управляемый обмен данными с ПУ. При этом обмен идет под управлением программы через регистры процессора одним из трех способов - синхронным, асинхронным и по прерыванию.

При синхронном обмене синхронизирующие сигналы МП задают временной интервал, в течение которого производится обмен с ПУ.

При асинхронном обмене интервал между командами передачи данных задается самим внешним устройством. При этом МП тратит время на ожидание готовности ПУ к обмену и во время этого ожидания не производит никакой другой работы по обработке данных.

Обмен по прерыванию программы отличается от асинхронного обмена тем, что готовность ПУ к обмену проверяется при помощи аппаратных средств МПС. При этом МП выполняет какую-либо из программ (основную, фоновую), не связанную с обменом. Когда ПУ готово к приему или выдаче информации, оно посылает сигнал готовности, воспринимаемый контроллером прерываний (КП). КП прерывает исполнение основной программы и передает управление подпрограмме, организующей нужный вид обмена данными. Когда выполнение подпрограммы завершается, возобновляется работа МПС по основной программе.

Обмен большими массивами данных с. памятью осуществляется в режиме прямого доступа к памяти (ПДП) под управлением контроллера прямого доступа в память. В этом режиме шины данных и адресов отдаются в распоряжение ПУ и МП в операциях обмена участия не принимает.

Для обеспечения связи МП с различными внешними устройствами разработаны контроллеры (адаптеры), обеспечивающие связь с ПУ по стандартному параллельному каналу передачи данных и связь с ПУ по стандартному последовательному каналу передачи данных.

На рисунке 23 представлен программируемый параллельный адаптер (ППИ), который обеспечивает подключение ПУ к шине данных системного интерфейса МПС через три независимых двунаправленных канала (порта) ввода-вывода: А, В и С. Управляющие сигналы определяют режим работы (синхронный, асинхронный, чтение, запись) и используемые для обмена каналы.

|

Рисунок 23 – Схема программируемого параллельного адаптера

Программирование ППИ осуществляется подачей в его регистр (РУС) управляющего слова, с помощью которого, при первом его формате задается направление передачи каждого из портов и один из трех режимов работы:

1) режим 0 – простой ввод-вывод данных в синхронном режиме побайтно через порты А,В, и С или дополнительно через порт С- потетрадно;

2) режим 1 – стробируемый ввод-вывод, при котором происходит обмен данными с ПУ через порты А и В в асинхронном режиме и режиме прерывания программы, сопровождаемая управляющими сигналами, проходящими через порт С;

3) режим 2 – двунаправленная магистраль обмена данными с ПУ через порт А в режиме прерывания программы, при этом пять разрядов порта С используются для передачи и приема управляющих сигналов. Порт В можно запрограммировать на работу в режимах 0 и 1.

Второй формат управляющего слова используется для установки или сброса произвольного разряда порта С.

|

|

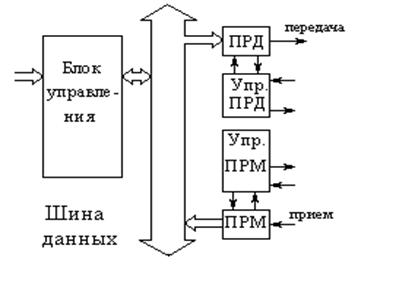

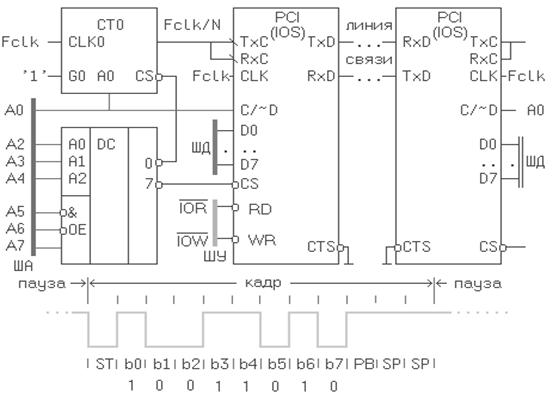

Рисунок 24 – Схема приемно-передающего устройства

На рисунке 24 представлено приемно-передающее устройство, предназначенное для преобразования информации, снимаемой с МД МПС из параллельной формы в последовательную и обратно. Другое название устройства - универсальный синхронно-асинхронный приемопередатчик. Устройство имеет в своем составе два независимых последовательных интерфейса: ввода (приемник) и вывода (передатчик). Связь приемника и передатчика БИС с системным интерфейсом МПС осуществляется через двунаправленный буфер данных по шине данных.

Схема управления адаптера служит для формирования внутренних управляющих сигналов из сигналов системного интерфейса. Она содержит регистры слова приказа и слова режима, содержимое которых определяет режим работы устройства: синхронный или асинхронный . В слове режима также задается скорость передачи, длина передаваемого символа, количество стоп-битов, наличие проверки на четность.

Для организации работы микропроцессорной системы в режиме реального времени можно использовать программируемый таймер, который позволяет формировать сигналы с разными временными интервалами и частотными характеристиками.

Важной архитектурной особенностью МПС являются прерывания, которые позволяют эффективно организовать работу МП при наличии нескольких параллельных процессов. Для технической реализации прерываний используют программируемые контроллеры прерываний.

Лекция №9. Программируемый параллельный интерфейс

Содержание лекции: схема включения программируемого параллельного интерфейса в микропроцессорную систему, его адресация, коды выбора одного из портов, порядок выполнения инструкций IN и OUT, режимы работы.

Цели лекции: изучить назначение входов и выходов программируемого параллельного интерфейса, способы его инициализации, режимы работы.

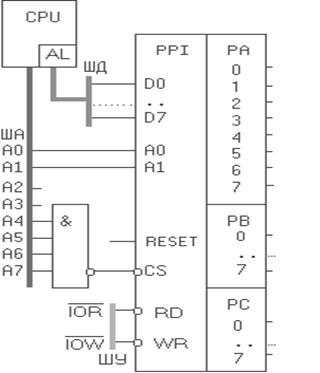

На рисунке 25 приведены условное обозначение программируемого параллельного интерфейса (ППИ или PPI-Programmable Peripheral Interface) и одна из возможных схем его включения в микропроцессорную систему. ППИ имеет три двунаправленных 8-ми битных канала связи с внешними устройствами, называемых обычно портами - PA,PB,PC.

Рисунок 25 – Схема включения ППИ в микропроцессорную систему

Порт PC отличается от остальных тем, что его можно "расчленить" на два независимых 4-х битных порта: старшую половину D7..D4 и младшую D3..D0. Как видно из рисунка 25, ППИ подключается к шине данных с помощью двунаправленных тристабильных выводов D7..D0. Входы A1,A0 осуществляют выбор одного из четырех каналов обмена данными: трех портов PA,PB,PC или внутреннего регистра управления/состояния (РУС или CSR - Control and Status Register).

Т а б л и ц а 6

|

A1 |

A0 |

КАНАЛ |

|

0 |

0 |

PA |

|

0 |

1 |

PB |

|

1 |

0 |

PC |

|

1 |

1 |

CSR |

ППИ переводится в рабочее состояние активным значением сигнала на инверсном входе "выбор микросхемы" (Chip Select, Crystall Select, CS) ~CS = 0, снимаемым с выхода дешифратора адреса (на рисунке 25 приведен неполный дешифратор - элемент И-НЕ). Логический ноль на выходе элемента И-НЕ появится, если все сигналы на его входах равны "1" (A7=A6=A5=A4=1). Так как выбор того или иного канала производится с помощью входов A1,A0, подключенных к аналогичным линиям шины адреса (ША), то с учетом входов дешифратора возможны следующие комбинации сигналов на ША, представленные в таблице 7.

Т а б л и ц а 7

|

ЛИНИИ ШИНЫ АДРЕСА |

КАНАЛ/ ПОРТ |

АДРЕС (HEX) |

|||||||

|

|

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

||

|

1 |

1 |

1 |

1 |

x |

x |

0 |

0 |

PA |

F0 |

|

1 |

1 |

1 |

1 |

x |

x |

0 |

1 |

PB |

F1 |

|

1 |

1 |

1 |

1 |

x |

x |

1 |

0 |

PC |

F2 |

|

1 |

1 |

1 |

1 |

x |

x |

1 |

1 |

CSR |

|

Линии A3,A2 шины адреса в схеме не задействованы, поэтому их значения в таблице обозначены (x - Don't Care Bits). При вычислении 16-ного адреса программист в качестве значения этих бит может подставлять любые значения, в том числе нули, как это и сделано в таблице. Например, для порта PB двоичный код 1111xx01 = 11110001(BIN) = F1(HEX).

Обмен байтами данных между МП (CPU) и внешними устройствами (ВУ), подключенными к портам ППИ, может производиться по командам ассемблера IN А, Адрес порта или OUT Адрес порта, А.

Выполнение команд IN и OUT производится в два этапа (без учета тактов и циклов, зависящих от конкретной архитектуры микропроцессора). Например, рассмотрим выполнение инструкций IN A,0F1h и OUT 0F1h,A, где A – аккумулятор, F1 – адрес порта PB.

1 этап. Микропроцессор помещает адрес (например F1) на ША, где он дешифрируется (в нашем примере элемент И-НЕ). С выхода дешифратора активный уровень (0) поступает на инверсный вход ~CS и переводит ППИ в рабочее состояние.

2 этап..

а) команда OUT. В следующий момент времени МП помещает байт, находящийся в аккумуляторе на шину данных и одновременно вырабатывает строб записи ~IOW поступающий на вход управления записью ~WR. Импульс ~IOW защелкивает байт данных в выходном регистре соответствующего порта ( в нашем примере в порте PB);

б) команда IN. Микропроцессор посылает на вход управления чтением ~RD строб чтения ~IOR , которым считывается в аккумулятор по ШД байт данных из порта PB.

ППИ имеет три основных режима работы:

0 – простой ввод-вывод (для передачи информации работают все порты РА,РВ и РС).;

1 – стробируемый ввод-вывод (для передачи информации работают два порта РА и РВ, а порт РС используют для управления передачей информации, то есть для ее квитирования);

2 - двунаправленная магистраль (в этом режиме работает только порт РА, а порт РВ можно использовать в режиме 0).

Тип операций выполняемых ППИ (режим работы) зависит от управляющего слова (УС), записанного в его регистр управляющего слова (РУС).

При программировании используют два формата УС:

1) первый - для задания режима работы и направления включения портов;

2) второй – для установки или сброса произвольного разряда порта С.

Управляющее слово первого формата определяют по таблице 8.

Т а б л и ц а 8

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

1 |

х |

х |

PA |

PCh |

РВ или РС1 |

PB |

PCl |

где D7 = 1 – установка формата 1;

![]() D6 =

D5 = 0 – режим 0

D6 =

D5 = 0 – режим 0

D6 =0, D5 = 1 – режим 1 для портов РА и РСh (старшая тетрада);

D6 = 1, D5 = х – режим 2

D4 = 1 – ввод, D4 = 0 – вывод порта РА;

D3 = 1 – ввод, D3 = 0 – вывод порта РСh;

D2 = 0 – режим 0, D2 = 1 – режим 1 портов РВ и РСl;

D1 = 1 – ввод, D1 = 0 – вывод порта РВ;

D0 = 1 – ввод, D0 = 1 – вывод порта РСl (младшая тетрада).

Разряды УС во втором формате имеют следующие значения:

D7 = 0 – установка формата 2; D6,D5,D4 – не используются;

D3,D2,D1 – определяют двоичный код номера разряда;

D0 = 1 - установка разряда, D0 = 0 – сброс разряда порта С.

При каждом изменении режима работы (новое УС первого формата) все выходные регистры и триггеры состояния сбрасываются.

Как было сказано выше, в режиме 0 базового ввода-вывода могут работать все три порта, причем порт С разделяется на два независимых 4-битных порта (РСh и РCl). Всего, таким образом, получается два 8-битных и два 4-битных порта параллельного ввода или вывода, что обеспечивает 16 возможных конфигураций адаптера в режиме 0. Выводимые данные фиксируются в регистрах-защелках, входящих в состав всех портов, а вводимые данные не запоминаются.

Режим 0 применяется в программно-управляемом вводе-выводе с медленнодействующими периферийными устройствами.

Режим 1 предназначен для однонаправленных передач данных, инициируемых прерываниями. Собственно передача слов данных осуществляется через порты А и В, а шесть линий порта С используются для управления обменом.

Например, если порт РВ установлен на ввод, то параллельно с передачей данных из периферийного устройства (ПУ) в порт РВ подается через разряд 2 порта РС логический 0, сигнализируя о выдаче информации из ПУ, а через разряд 1 порта РС ПУ получает логический 0 подтверждения приема данных. Если порт РВ установлен на вывод информации, то параллельно с выдачей информации в ПУ через разряд 1 порта РС идет сигнал логического 0, а через разряд 2 порта РС осуществляется прием от ПУ логического 0 подтверждения записи данных в ПУ.

Аналогично работает порт РА, только при вводе информации он использует разряды 4 и 5, а при выводе – разряды 6 и 7 порта РС.

Данный режим предоставляет пользователю следующие возможности: запрограммировать один или два параллельных порта с линиями квитирования и прерывания, каждый из которых может работать на ввод или вывод. При использовании только одного порта остальные 13 линий можно запрограммировать в режиме 0. При определении двух портов в режим 1 оставшиеся 2 линии можно использовать для ввода или вывода.