АЛМАТЫ ЭНЕРГЕТИКА ЖӘНЕ БАЙЛАНЫС ИНСТИТУТЫ

Электроника және компьютерлік технологиялар кафедрасы

ЦИФРЛЫҚ ҚҰРЫЛҒЫЛАР ЖӘНЕ МИКРОПРОЦЕССОРЛАР

050704 – Есептеу техникасы және бағдарламалық камтамасыздандыру,

050719 – Радиотехника, электроника және телекоммуникациялар

мамандықтарының студенттері үшін зертханалық жұмыстарды орындауға арналған әдістемелік нұсқаулар

Алматы 2009

ҚҰРАСТЫРУШЫ: О.Т.Шанаев. Микропроцессорлық жүйелер. 050704 – Есептеу техникасы және бағдарламалық қамтамасыздандыру, 050719 – Радиотехника, электроника және телекоммуникациялар мамандықтарының студенттері үшін “Цифрлық құрылғылар және микропроцессорлар” пәнінің екінші бөлімінен зертханалық жұмыстарды орындауға арналған әдістемелік нұсқаулар. – Алматы: АЭжБИ, 2009. – 31 б.

Әдістемелік нұсқауларда микропроцессорлық жүйелердің негізгі құрылғыларының құрылым принциптерін зерттеуге арналған зертханалық жұмыстар келтірілген. Бұл жұмыстардың орындалуы арқылы студенттердің “Цифрлық құрылғылар және микропроцессорлар” пәнінің екінші бөлімінен алар білімінің түпнегізі қаланады. Келтірілген жұмыстар мамандардың квалификациялық сипаттамасы мен Мемлекеттік стандарттардың талаптарына және зертханалық жұмыстардың ұйымдастырылуы мен жүргізілуінің педагогика-психологиялық негіздеріне сай құрылған. Ұсынылған зертханалық жұмыстар Electronics Workbench моделдеу жүйесіндегі жүзеге асырылатын виртуалды тәжірибе түрінде орындалады.

Зертханалық жұмыстарға берілген әдістемелік нұсқаулар 050704 – Есептеу техникасы және бағдарламалық қамтамасыздандыру, 050719 – Радиотехника, электроника және телекоммуникациялар мамандықтарының барлық оқу түрінің студенттеріне арналған. Бұл нұсқауларды өзге мамандықтарға жоспарланған осы сияқты пәндердің сәйкесті тақырыптарынан зертханалық жұмыстар ұйымдастыру үшін де пайдалануға болады.

Кіріспе

“Цифрлық құрылғылар және микропроцессорлар” пәнінің, микропроцессорларға арналған екінші бөлімі өзара байланысты және өзара толтырымды екі бөліктен тұрады: аппараттық бөлігі (hardware) және бағдарламалық бөлігі (software). Техникалық пәндердің игерілуінде оның түп негіздік тақырыптары бойынша орындалатын зертханалық жұмыстардың орны үлкен екені белгілі. Таралған дәстүр бойынша бұл пәннің зертханалық жұмыстарының тапсырмалары негізінде ассемблер тіліндегі бағдарламалау негіздерін үйретуге арналған, ал пәннің аппараттық бөлігіне онша көңіл бөлінбейді. Оны сәйкесті зертханалық жұмыстардың қойылым күрделілігімен түсіндіруге болады. Бірақ, жүйенің регистрлік моделіне негізделген, ассемблер тілінде бағдарлама құру үшін жүйенің аппараттық бөліктері туралы, бағдарламаның нақтылы командаларының орындалуы кезіндегі оларда жүретін процестер туралы және информация мен басқару сигналдарының жүру жолдары туралы толық түсінік қажет болады. Демек, пәнді толық игеру үшін оның аппараттық бөлігін де, бағдарламалық бөлігін де игеру керек болады.

Ұсынылған әдістемелік нұсқауларда “Цифрлық құрылғылар және микропроцессорлар” пәнінің аппараттық бөлігі бойынша қойылған зертханалық жұмыстардың суреттемесі мен сәйкесті жұмыс тапсырмалары келтірілген. Әдістемелік нұсқауларда келтірілген жұмыс тапсырмаларының орындалуы Electronics Workbench бағдарлама жүйесінде моделдеу арқылы жүргізілетін виртуалды тәжірибе түрінде ұйымдастырылған. Тапсырмалардың кейбірін студенттердің өздік жұмысының (СӨЖ) тапсырмасы ретінде бөліп шығаруға болады. Зертханалық сабақтардың ұсынылған ұйымдастырылу әдістемесі автордың көптеген жылдық сабақ жүргізу барысында тексеріліп, уақыт тәжірибесінен өткен. Оқу зерттелімінің бұндай ұйымдастырылу әдістемесі студенттердің оқылатын құрылғылар жөнінде тереңірек білім алуын және олардың іс жүзіндегі және моделдік тәжірибелер жүргізу жолдарын игеруіне мүмкіндік береді.

Әдістемелік нұсқауларда ұсынылған Electronics Workbench бағдарлама жүйесі арқылы жүргізілетін виртуалды зерттелімдерді орындауға арналған тапсырмалар зертханалық сабақтарға қойылған мақсаттарға жетуге толық мүмкіндік береді және студенттерге оқу барысының қажеттігінде (мысалы, курстық және бакалаврлық шығарым жұмыстарын орындау кезінде) немесе мамандығы бойынша болашақтағы жұмысында өздік қолдануына жағдай жасалады .

Орындалған оқу зерттемесі жөнінде студенттер сәйкесті жұмыс есептесімін дайындауы керек. Онда зерттеу сұлбалары, өлшенген және есептелген шамалар, тәжірибеден шығарылған және қосалқы сызбалар, зерттелуші элементтің немесе құрылғының анықталған (өлшенген және есептелген) параметрлері, орындалған тәжірибелердің нәтижелері жөнінде қорытындылар, СӨЖ тапсырмаларының орындалу нәтижелері және сұрақтарға қысқаша жауаптар болу керек.

Келесі қарастырылатын мәселе ұсынылған зертханалық жұмыстардың тақырыбтары мен жұмыс тапсырмаларының мазмұнына байланысты. Бұл мәселені анықтау үшін пәннің теориялық мазмұнына қысқаша тоқталамыз.

Микропроцессорных жүйелердің (МПЖ) құрылу негізіне үш принцип алынған:

- магистралдік;

- модулдік;

- микробағдарламалы басқару.

Магистралдік принцип МПЖ-нің қызмет блоктарының арасындағы байланыс сипатын анықтайды; жүйенің барлық блогы өзара жүйелік магистраль (жүйе желісі) арқылы жалғанады және сол арқылы информация алмасады.

Модулдік принцип жүйенің, қызметі жағынан толықтай бітірілген, жеке блоктар негізінде құрылатындығын сипаттайды. Әрбір модулдің, оны іске қосатын, рұқсат кірісі болады; ондағы сигнал деңгейі модулдің үшінші (жоғарғыкедергілі) жағдайын, яғни оның жүйе желісіне қосылуын басқарады.

Микробағдарламалы басқару принципі қарапайым операциялардың – микрокомандалардың (информация жіберілімінің, арифметикалық операциялардың, ығыстырымдардың және т.б.) жүзеге асырылу мүмкіндіктерін сипаттайды.

Жүйелік магистралға негізгі үш информиацалық желі кіреді: адрес желісі, дерек желісі және басқарым желісі.

Дерек желісі – жүйе модулдерінің арасында дерек алмастырылатын, негізгі желі. Дерек желісі, оның деректерді екі бағытта да жіберуді қамтамасыз етуі керек болғандықтан, әрқашан екібағытты.

Адрес желісі – жадыға (немесе сыртқы құрылғыларға) байланысымды қамтамасыз етуші желі.

Магистралдың байланыс жолдарының толық санын кеміту үшін көбіне адрес желісі мен дерек желісін кезектестіру тәсілі қолданылады, яғни байланыс жолдары әр уақыт мезетінде адрес пен деректі кезектеп жіберіледі (цикл басында – адрес, цикл аяғында – деректер).

Басқару желісінің жолдарындағы сигналдар кезекті цикл түрін анықтайды және оның әртүрлі бөліктеріне немесе кезеңдеріне сәйкесті уақыт мезеттерін бекітеді. Сонымен қатар, басқару сигналдары процессор (немесе магистралдың өзге қожасының, бастаушының, master) жұмысын жадының немесе енгізу/шығару құрылғыларының (орындаушы құрылғының, slave) жұмысымен келістіреді.

Негізгі басқару сигналдары – алмастыру стробтары, яғни жазу (шығару) стробы мен оқу (енгізу) стробы. Бұл сигналдарды процессор қалыптастырады, олар деректердің желі арқылы сәйкесті бағытта жіберілу мезеттерін анықтайды.

Микропроцессорлық жүйенің құрамы:

- орталық процессор;

- тұрақты жады құрылғысы;

- қызмет жадысының құрылғысы;

- енгізу/шығару құрылғысы;

- үзіліс жүйесі;

- таймер.

Бұл құрылғылардың барлығы да жүйе магистралына қосылған және олардың өзара информация алмасуы да осы магистраль арқылы жүзеге асырылады.

Енгізу/шығару құрылғыларын немесе сыртқы құрылғыларды (ЕШҚ немесе СҚ) жүйе магистралына қосу үшін олардың сигналдары, енгізу/шығару интерфейстері арқылы жүзеге асырылатын нақтылы стандарттарға сәйкес болу керек.

Процессордың деректерді жазу және оқу операцияларын орындауы бағдарламалы-басқарылымды алмасу, үзіліс және жадыға тура шығу режимдерінде жүзеге асырылуы мүмкін, олардың ішіндегі ең бастысы – біріншісі.

МПЖ құрылымы жөнінде жоғарыда айтылғанға байланысты зертханалық жұмыстардың тақырыптары мен олардың құрамындағы жұмыс тапсырмаларының мазмұны анықталды.

Бастапқы үш жұмыс әртүрлі жады жүйелеріне және олардың әртүрлі құрылым принциптеріне арналды.

Төртінші жұмыс информация енгізу құрылғысына және оларды әртүрлі тәсілмен сақтаудың жүзеге асырылуына арналды.

Бесінші жұмыс микропроцессорлық жүйеде бағдарламалы-басқарылымды алмасудың жүзеге асырылуына арналды.

Соңғы екі жұмыс интерфейстерге (параллель және тізбекті) арналды.

Жұмыс тасырмаларының орындалу сипаты жұмыстан жұмысқа дамытылған әлпетте қойылды: егер бастапқы жұмыстардың тапсырмалары құрылғы сұлбаларын жеке модулдер түрінде жиналатын болса, келесі жұмыстардың сұлбалары алдыңғы жұмыстарда дайындалған моделдерді пайдалану арқылы жиналады, ал соңғы жұмыстардың орындалуы толықтай дайын моделдерде жүзеге асырылады. Информация алмастыруға арналған бірнеше жұмыста ортақ магистралдың қолданылуына аса көңіл бөлінген, ал шығыстары үш жағдайлы құрылғылар жұмыстардың бәрінде дерлік пайдаланылады.

Ұсынылған зетханалық жұмыстардың тақырыптарының, жұмыс тапсырмаларының мазмұны мен олардың орындалу сипатының (әдістемесінің) студенттердің оқу дәрістерінен және сәйкесті әдебиетті оқу нәтижесінде алған теориялық білімдерін тиянақтай түсетіндігі және Electronics Workbench сияқты заман талабына сай жаңа бағдарламалық құралдар арқылы моделдеу тәжірибелерін жүргізіп үйренетіндігі сөзсіз.

1 №1 зертханалық жұмыс. ROM түрлі жадылық құрылғылар

1.1 Жұмыстың мақсаты:

- ROM түрлі ЖҚ-дың құрылым принциптерін игеру;

- тәжірибелер жүргізуге қажетті қосалқы құралдарды құру жолдарын игеру.

1.2 Теориялық мәліметтер

ROM (Read Only Memory) түрлі жадылық құрылғылардың кейбіріндегі информация (ROM(M) және PROM түрлі ЖҚ-да) ешқашан өзгермейді, ал кейбірінде (в ЗУ типов EPROM и EEPROM) өзгереді, бірақ жұмыс кезінде емес.

Тұрақты жадыны бағдарламалау – жады элементтерінің матрицасының горизонталь және вертикаль жолдарының арасында байланыс элементтерінің орналастырылуы арқылы жүзеге асырылады.

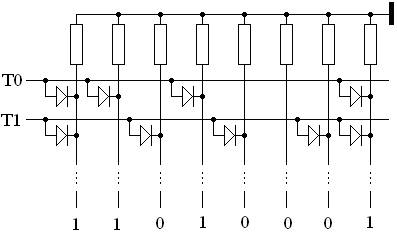

Диодты ROM(M) матрицасында (1.1-сурет) горизонталь жолдар – сөз таңдам жолдары, ал вертикаль жолдар – оқылым жолдары. Оқылатын сөз диодтардың координат торының түйіндеріндегі орналасысымымен анықталады. Диодтың тұрған кезінде таңдалған горизонталь жолдың жоғарғы потенциалы сәйкесті вертикаль жолға жіберіледі де, сөздің осы разрядында логикалық бір сигналы шығады. Диодтың жоқ кезінде, вертикаль жол резистор арқылы жерге жалғанғандықтан, потенциал нөлге жуық болады. Көрсетілген матрицадағы таңдам жолы Т0 жандандырылғанда 11010001 сөзі оқылады (номері ноль ұяшықта осы сөз сақталған). Т1 жолы жандандырылғанда 10101011 сөзі оқылады (ол номері 1 ұяшықта сақталған). Таңдам жолдары – адрес дешифраторының шығыстары, әрбір адрес қиыстырымы дешифратордың сәйкесті шығысын жандандырады да, сілтенген ұяшықтағы сөз оқылады.

1.1 Сурет

1.3 Жұмыстың тапсырмасы

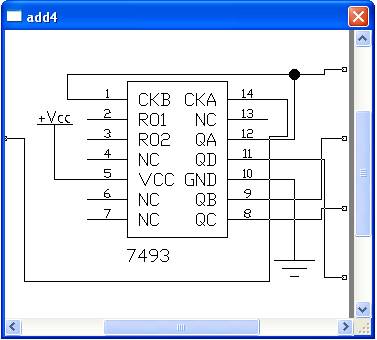

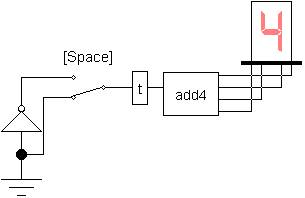

1.3.1 Жеке импульс қалыптастырғышының (1.2-сурет) және төрт разрядты адрес қалыптастырғышының (1.3-сурет) сұлбаларын блок түрінде дайында.

1.2 Сурет

1.3 Сурет

1.3.2 Адрес қалыптастыру сұлбасын жинап, оның жұмысын тексер (1.4-сурет).

1.4 Сурет

1.3.3 C:\EWB5PRO\MPS_Lab\ROM_base файлын шығарып, онда келтірілген және келесі (негізгі) сұлбаны жинауға қажетті блоктарды ашып, олардың ішкі құрылымымен таныс. ROM_16x7 блогының құрамына шығысты дешифратор (dc16 блогы) мен он алтылық символдардың 7-сегментті индикаторының коды тұрған жады элементтерінің матрицасы (16x7 блогы) кіреді. Матрицадағы байланыс элементтері ретінде, блок түрінде безендірілген, өзі ашылатын үш жағдайлы буферлік сұлба пайдаланылады.

1.3.4 ROM ЖҚ-сын басқару сұлбасын (1.5-сурет) жинап, жады ұяшықтарының әрбіреуіндегі информацияны оқу арқылы оның жұмысын зертте.

1.5 Сурет

1.3.5 Матрицалық блока сұлбасын L, J, H, P, S, U, –, _, e, n, q, r символдарының екеуінің (оқытушының көрсетуі бойынша) суреттемесі шығатындай етіп өзгерт.

1.3.6 Өзгертілген сұлбаның жұмысын тексеріп, оны өзіңнің жеке папкаңда, өзің туралы нақтылы мәлімет бар аталыммен, мысалы, ROM_ВТ04-Алмат-1аталымымен сақта.

1.4 Бақылау сұрақтары

1. ROM құрылымы қандай қызмет атқарады?

2. ROM құрылымының сұлбалары қалай ұйымдастырылған?

3. ROM(M) құрылымдары қалай бағдарламаланады?

4. PROM құрылымдары қалай бағдарламаланады?

5. EPROM және EEPROM құрылымдарының ерекшелігі қандай?

2 №2 зертханалық жұмыс. ЖҚ-дың түпнегіздік құрылымдары

2.1 Жұмыстың мақсаты:

- жадылық құрылғылардың түпнегіздік құрылым принциптерін игеру;

- жадылық құрылғылардың өлшемін кеңейту жолдарын үйрену.

2.2 Теориялық мәліметтер

2.2.1 2D құрылымы

Қарапайым цифрлық құрылғылардың (RAM түрінің де, ROM түрінің де) жады жүйесін 2D құрылымымен құруға болады.

2D құрылымында (2.1сурет) n-разрядты жады ұяшықтары ЖҰ бір жол бойында орналасады (суретте – вертикаль бойында), сондықтан мұндай құрылым көбіне сызықты құрылым деп аталады.

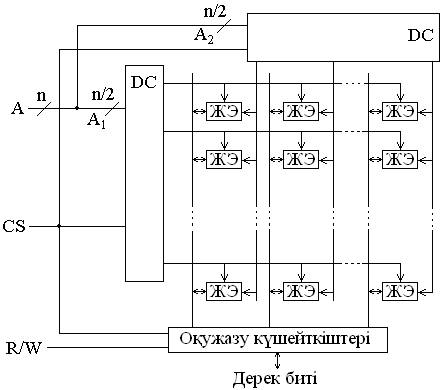

2.1 Сурет

Адрес кодының дешифраторы DC рұқсат сигналы CS (Chip Select – микросұлбаны таңдау сигналы) берілген кезде шығыс жолдарының біреуін жандандырып, таңдалған жолдағы ұяшыққа, демек, онда сақтаулы сөзге, қол жеткізеді. Матрица бағаналарының сәйкесті элементтері вертикаль жолға, яғни ішкі дерек жолына (разряд жолына, оқу/жазу жолына) жалғанған. Бағана элементтерінде сөздердің аттас биттері сақталған. Сөздің жіберілім бағыты R/W (Read – оқу, Write – жазу) сигналының әрекетіне байланысты оқу/жазу күшейткіштерімен анықталады.

2.2.2 3D құрылымы

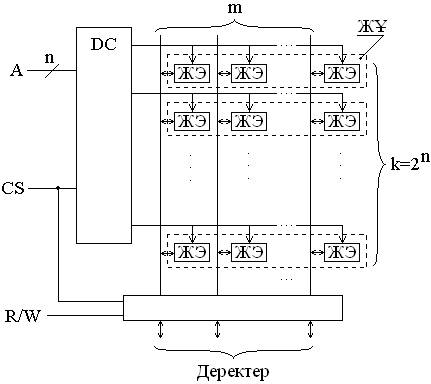

3D құрылымы (матрицалы құрылым деп те аталатын) қоскоординаталы таңдам арқылы адрес дешифраторын жеңілдетуге мүмкіндік береді (2.2-сурет).

2.2 Сурет

Мұнда n разрядты адрес коды екіге бөлінеді де, олардың әрбіреуі жеке ажыратылады. Жандандырылған жолдардың қиылысындағы жады элементі (немесе ұяшығы) таңдалады. Мұндай қиылыстар саны

2n/2 х 2n/2 = 2n.

Екі дешифратордың шығыстарының толық саны

2n/2 + 2n/2 = 2n+1

болады, ал бұл іс жүзіндегі n мәніндегі 2n санынан едәуір кем.

2.3 Жұмыстың тапсырмасы

2.3.1 2D құрылымы

2.3.1.1 C:\EWB5PRO\MPS_Lab\RAM_2D_base файлын шығарып, онда келтірілген, санауыш негізіндегі, үш разрядты адрес қалыптастырғышы (add3) мен төрт разрядты дерек көзі (data) және құрамына сегіз шығысты дешифратор (dc8) мен регистр негізіндегі 8 ұяшықтан (rg4) тұратын жады элементтерінің матрицасы (8x4) кіретін RAM_8x4 блоктарын ашып, олардың ішкі құрылымымен таныс.

2.3.1.2 Осы файлда келтірілген блоктар арқылы 2.3-суреттегі сұлбаны жина да, әрбір ұяшыққа нақтылы информация жазып, сосын олардың сақталымын тексеру арқылы оның жұмысын зертте.

2.3 Сурет

2.3.1.3 Алдымен 8х4 матрицасының негізінде 8х8 өлшемді жады элементтерінің матрицасын және сегіз разрядты дерек көзін дайындап, RAM 2D 8x8 құрылғысын және оны зерттеу сұлбасын құр.

Құрылғының жұмысын зертте.

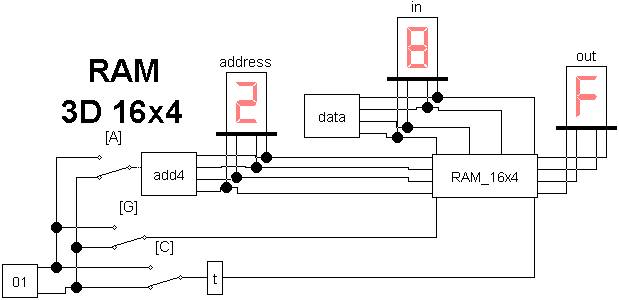

2.3.1.4 Алдымен 8х4 матрицасының негізінде 16х4 өлшемді жады элементтерінің матрицасын дайындап және алдыңғы жұмыстағы (ROM_base файлы) add4 және dc16 блоктарын пайдаланып, RAM 2D 16x4 құрылғысын және оны зерттеу сұлбасын құр.

Құрылғының жұмысын зертте.

2.3.2 Структура 3D

2.3.2.1 C:\EWB5PRO\MPS_Lab\RAM_3D_base файлын шығарып, онда келтірілген, санауыш негізіндегі, төртразрядты адрес қалыптастырғышы (add4) мен төртразрядты дерек көзі (data) және құрамына төрт шығысты қос дешифратор (2dc4) мен регистр негізіндегі 16 ұяшықтан (rg4) тұратын жады элементтерінің матрицасы (16x4) кіретін RAM_16x4 блоктарын ашып, олардың ішкі құрылымымен таныс.

2.3.2.2 Осы файлда келтірілген элементтер (блоктар) арқылы 2.4-суреттегі сұлбаны жина да, әрбір ұяшыққа нақтылы информация жазып, сосын олардың сақталымын тексеру арқылы оның жұмысын зертте.

2.4 Сурет

2.3.2.3 Жады ұяшықтарының екі 16х4 матрицасы мен сегіз разрядты дерек көзін пайдаланып, RAM 3D 16x8 құрылғысын және оны зерттеу сұлбасын құр.

Құрылғының жұмысын зертте.

2.4 Бақылау сұрақтары

1. Жадылық құрылғылардың негізгі параметрлерін келтір.

2. Жады ұяшығы деген не?

3. RAM құрылымы қандай қызмет атқарады?

4. Қандай сұлбақұралыс RAM құрылымының максималды тез әрекеттілігін қамтамасыз етеді?

5. Бір бағытты сілтемді RAM құрылымының құрылу принципі қандай?

6. Екі бағытты сілтемді RAM құрылымының құрылу принципі қандай?

7. 2D және 3D құрылымдарының артықшылықтары мен кемшіліктерін салыстыр.

8. Жады құрылымының ұяшық санын екі есе қалай ұлғайтуға болады?

9. Жады құрылымының ұяшық санын төрт есе қалай ұлғайтуға болады?

3 №3 зертханалық жұмыс. ЖҚ-дың 2DM құрылымы

3.1 Жұмыстың мақсаты:

- жадылық құрылғылардың 2DM құрылыммен құрылу принципін игеру.

3.2 Теориялық мәліметтер

Үлкен жүйелердің (мысалы, компьютерлердің) жады жүйелерін ұйымдастыруға арналған 2DM (модификацияланған 2D) түрлі құрылымдарда 2D және 3D құрылымдарының екеуінің де артықшылық жақтары қамтылған – адрес ажыратылуы жеңілдетілген және екі координаталы таңдалымды жады элементтерінің қажеттігі жоқ.

2DM құрылымының жады элементтерінің матрицасы (3.1-сурет) 2D құрылымының сипатындай: дешифратордың жандандырылған шығысы толық бір жолды таңдайды. Бірақ 2D құрылымынан ерекше, жол ұзындығы сақталушы сөздердің разряд санындай емес, одан бірнеше есе асып түседі. Жолдардың біреуін таңдауға адрес кодының An–1... Ak бөлігі пайдаланылады. Адрестің қалған разрядтары (от Ak–1... A0) жолдағы көптеген сөздердің қажеттісін мультиплексор арқылы таңдап алуға пайдаланылады. Жол ұзындығы – m2k, мұндағы m – сақталушы сөздердің разряд саны. Ұзақтығы 2k жолдың әрбір “кесіндісінен” 2k мультиплексор бір бит таңдайды. Мультиплексорлардың шығыстарында шығыс сөзі қалыптасады. Үш жағдайлы басқарылымды буферлердің ОЕ кірістеріне түсетін CS сигналының рұқсатымен шығыс сөзі сыртқы желіге жіберіледі.

3.1 Сурет

3.3 Жұмыстың тапсырмасы

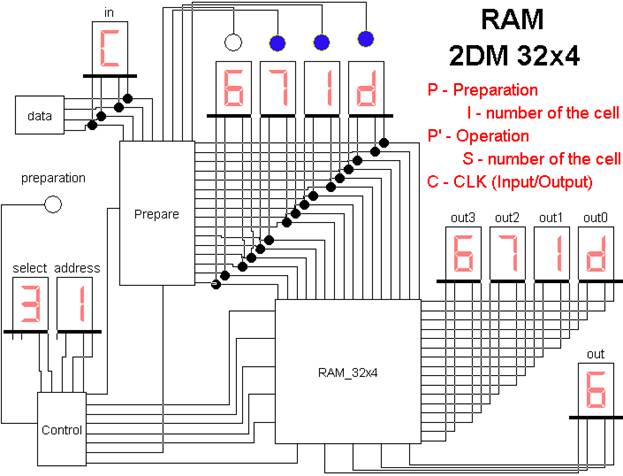

3.3.1 2DM құрылымды жады блогын зерттеу сұлбасы (3.2-сурет) келтірілген C:\EWB5PRO\MPS_Lab\RAM_2DM шығарып, келесі түсіндірме мәтінін оқи отырып және құрылғының сәйкесті блоктарын ашып қарастыру арқылы олардың ішкі құрылымымен толық таныс.

3.2 Сурет

Сұлба құрамына келесі блоктар кіреді:

- 3D құрылымды жады блогы RAM_32x4;

- дерек дайындау блогы Prepare;

- басқару блогы Control.

Жады блогы RAM_32x4 келесі блоктардан тұрады:

- жады элементтерінің матрицасы 32х4;

- жол ажырату блогы dc8;

- жолдан ұяшық таңдау блогы (оқу кезінде) mux4.

Жады матрицасы 32х4 8 жолдан тұрады (логикалық жағынан), әрбір жолда төрт 4-разрядты жады ұяшығынан rg4 құрылған cell_4x4 блогы орналасқан. Іс жүзінде жады блогы 32х4 (жалғау және қарастыру ыңғайлылығы үшін) төрт cell_4x4 блогы арқылы құрылған екі 16х4 блогының біріктірілімі түрінде жүзеге асырылған. Жады матрицасының әрбір ішкі блогы индикатормен қамтылған, олар тәжірибе кезінде жол мен ұяшық таңдалымын көрнекі бақылауға мүмкіндік береді.

Жады жолын таңдауға арналған dc8 блогы – сегіз шығысты дешифратор.

Төрт 4-кірісті мультиплексоры арқылы жиналған mux4 блогы жандандырылған жолдан қажетті ұяшық таңдау мүмкіндігін береді.

Prepare блогы жады матрицасының бір жолына қатар жазуға арналған төрт 4-разрядты сөз дайындау қызметін атқарады. Дайындау кезеңінде бұл сөздер төрт 4-разрядты жады ұяшығынан (in) құрылған ішкі in_4 блогында сақталады. Бұл ұяшықтардың біреуін таңдау дешифраторлық dc4 блогы мен оның сілтеу блогы 0_3 арқылы жүзеге асырылады.

Control блогында басқару түймелері мен құрылғының барлық жұмыс режимін қамтамасыз етуші қосалқы элементтер біріктірілген. Құрылғы үш режимде істей алады:

- жазуға арналған деректер дайындау режимі;

- жазу режимі;

- оқу режимі.

Деректер дайындау режимі келесі тәртіппен жүзеге асырылады:

- P түймесі арқылы құрылғыны деректер дайындау режиміне ауыстыру (сәйкесті индикатор жарық шығарып тұрады);

- I түймесі арқылы in_4 блогының төрт ұяшығының біреуін таңдау (сәйкесті индикатор көрсетіп тұрады);

- С (CLK) түймесі арқылы осы ұяшыққа дерек блогының (data) қалыптастырған бір сөзін жазу.

Жазу/оқу режиміне ауыстыру P түймесі арқылы жүзеге асырылады (индикатор сөнеді). Жазу режимінде:

- A түймесі арқылы жады матрицасының қажетті жолын таңдау (сәйкесті 7-сегментті индикатор көрсетеді);

- С (CLK) түймесі арқылы дайындалған деректерді жады матрицасының таңдалған жолына жазу.

Оқу режимінде:

- A түймесі арқылы жады матрицасының қажетті жолын таңдау (сәйкесті 7-сегментті индикатор көрсетеді);

- S (Select) түймесі арқылы жандандырылған жолдың нақтылы жолын таңдау (сәйкесті 7-сегментті индикатор көрсетеді).

3.3.2 RAM_2DM жады құрылғысының барлық жолына информация жазып, сосын әрбір нақтылы жады ұяшығынан оқу мүмкіндігін тексеріп, құрылғының жұмысын зертте.

3.4 Бақылау сұрақтары

1. 2DM құрылымды жадының жүзеге асырылу принциптерін түсіндір.

2. Зерттеу сұлбасының жеке блоктары қандай қызмет атқарады?

3. 2DM құрылымының өзге құрылым түрлерімен салыстырғандағы қандай артықшылығы бар?

4 №4 зертханалық жұмыс. Информация енгізу құрылғысы

4.1 Жұмыстың мақсаты:

- шифратор негізіндегі информация енгізу құрылғысын құру принциптерін игеру;

- құрылғы жұмысын жетілдіру жолдарын үйрену;

- көпрежимді құрылғыларды құру жолдарын үйрену.

4.2 Теориялық мәліметтер

Түймежинақ арқылы информация енгізу құрылғысы басылған түймеге сәйкесті код шығарып, сонымен қатар шығарылған кодты сақтауға арналған жазу импульсін қалыптастыру керек.

Құрылғының шифратор микросұлбасы (мысалы, 74148 микросұлбасы) негізінде моделдеу арқылы жүзеге асырылу кезінде (іс жүзінде де) микросұлбаның CS шықпасындағы сигнал деңгейі өзгереді, оған негіздеп жазу импульсін тудыру қызметін атқаратын жеке импульс қалыптастырғышын құруға болады. Сонымен қатар код шығарылу ұзақтығы мен жазу импульсінің қалыптастырылу мезетін уақыт жағынан келістіру керек болады. Осындай қалыптастырғыш ретінде ұзақтығы 10 ns және код қалыптасуының басынан (түйме басылу мезетінен) 20 ns кідірген теріс импульс шығаратын k аталымды блок құрылды.

Ауыстырғыш моделін тура пайдалану кезінде оны бастапқы жағдайына кері қайтару қажеттігі туады, яғни ауыстырғышқа сәйкесті түймені екі рет басуға тура келеді. Түйме басылуының ұзақтығына байланысты осындай жағдай құрылғының іс жүзіндегі жүзеге асырылуы кезінде де туады. Осы мәселені шешу үшін ұзақтығы 50 ns теріс импульс қалыптастырушы 5_ аталымды блок құрылды.

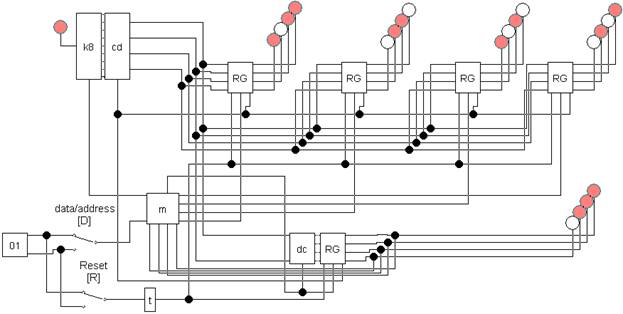

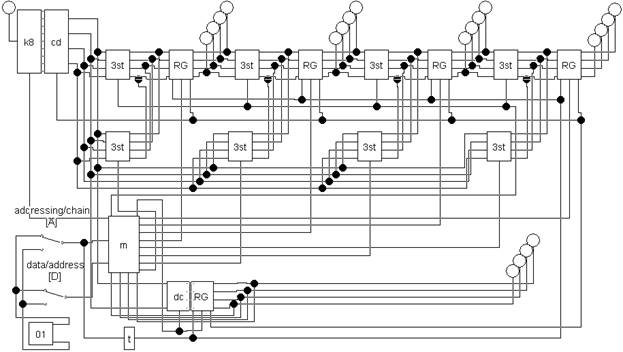

Келесі мәселе қалыптасқан кодты жазу тәсіліне байланысты: тізбелеп (chain) немесе сілтеу арқылы (addressing). Әрбір мүмкіндікті қарастыру мақсатында, зерттеуге арналған сәйкесті жеке файлдар құрылды. Ақырында, соңғы файлда, жазу режимдерінің ауыстырылу мүмкіншілігі ескеріліп, екі жағдай біріктірілді. Бұл студенттердің көпрежимді құрылғы құру жөнінде тәжірибе алуына мүмкіндік береді. Режимдердің ауыстырылуын басқару, ауыстырғыштан істейтін және сигналдардың режимге байланысты жіберілу бағытының өзгеруін қамтамасыз ететін, қиыстырма сұлба m арқылы іске асырылады.

4.3 Жұмыстың тапсырмасы

4.3.1 C:\EWB5PRO\MPS_Lab\Input_Chain файлын шығар. Онда, тудырылған кодтарды тізбелеп, яғни ығыстыру арқылы сақтаушы, шифратор негізіндегі енгізу құрылғысы келтірілген. Сұлба блоктарын ашып, олардың құрылымымен таныс.

Құрылғы жұмысын тексер.

4.1 Сурет

4.3.2 C:\EWB5PRO\MPS_Lab\Input_Addr файлын шығар. Онда, тудырылған кодтарды сілтеу арқылы сақтаушы, шифратор негізіндегі енгізу құрылғысы келтірілген. Сұлба блоктарын ашып, олардың құрылымымен таныс.

Құрылғы жұмысын тексер.

4.2 Сурет

4.3.3 C:\EWB5PRO\MPS_Lab\Input_Comb файлын шығар. Онда, тудырылған кодтардың екі түрлі жазылу тәртібі біріктірілген, шифратор негізіндегі енгізу құрылғысы келтірілген. Сұлба блоктарын ашып, олардың құрылымымен таныс.

Құрылғы жұмысын тексер.

4.3 Сурет

4.4 Бақылау сұрақтары

1. Шифратордың 74148 микросұлбасының кіріс және шығыс сигналдарының қызметін түсіндір.

2. Input_Comb сұлбасындағы 3st блогының қызметін түсіндір.

3. Input_Addr сұлбасындағы m блогының қызметін түсіндір.

4. Input_Comb сұлбасындағы m блогының қызметін түсіндір.

5 №5 зертханалық жұмыс. Деректердің бағдарламалы жіберілуі

5.1 Жұмыстың мақсаты:

- микропроцессорлық жүйеде деректердің бағдарламалы жіберілу принциптерін игеру;

- көпрежимді құрылғылардың жұмысын талдау жолдарын үйрену.

5.2 Теориялық мәліметтер

5.2.1 Асинхронды Q-bus магистралы арқылы дерек жіберу

Асинхронды, кезектесімді Q-bus магистралі арқылы бағдарламалы басқарылымды дерек жіберілімінің ұйымдастырылуы келесі тәртіппен жүзеге асырылады.

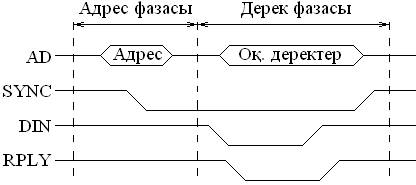

Адрес/дерек (AD) желісінде жіберім циклінің басында (адрес фазасында) процессор (бастаушы) желіге адрес кодын қояды және сонымен қатар теріс строб сигналын SYNC’ қояды. Жазу циклінің де, оқу циклінің де адрес фазасы бірдей.

Оқу циклінің дерек фазасында (5.1-сурет) процессор дерек оқылымының теріс строб сигналын DIN’ қояды. Оған жауап ретінде орындаушы құрылғы желіге өзінің дерек кодын (оқылатын деректер) қояды да, дерек жіберу операциясының орындалғанын RPLY’ сигналымен құптайды.

5.1 Сурет

Процессор, RPLY’ сигналын қабылдағаннан кейін DIN’ сигналын алып тастайды. Оған жауап ретінде орындаушы құрылғы құптаушы RPLY’ сигналын алып тастайды. Бұдан кейін процессор SYNC’ сигналын алып тастайды да, жіберім сигналын бітіреді.

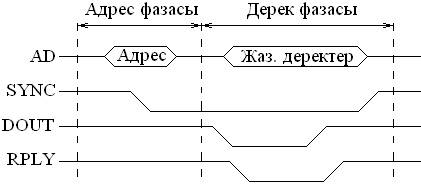

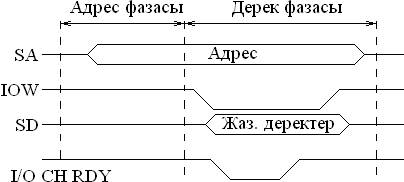

Жазу циклінің дерек фазасында (5.2-сурет) процессор AD желісіне жазылатын дерек кодын қойып, сонымен қатар дерек жазылымының теріс строб сигналын DOUT’ қояды. Оған жауап ретінде орындаушы құрылғы деректерді қабылдайды да, дерек қабылдау операциясының орындалғанын RPLY’ сигналымен құптайды. Процессор мен орындаушы құрылғының келесі әрекеттері оқу цикліндегі әрекеттер тәрізді.

Қарастырылған магистральда адрес синхронды жіберіледі (оның қабылданғандығын орындаушының құптамасынсыз), ал деректер оның жіберілгендігін немесе қабылданғандығын міндетті түрде құптауымен асинхронды жіберіледі.

5.2 Сурет

5.2.2 Синхронды ISA магистралы арқылы дерек жіберу

Синхронды, кезектесімсіз ISA магистралі арқылы бағдарламалы басқарылымды дерек жіберілімінің ұйымдастырылуы келесі тәртіппен жүзеге асырылады.

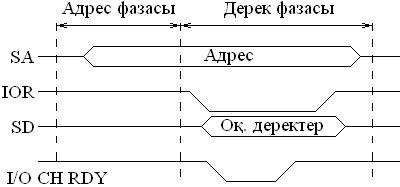

Екі цикл да процессордың (бастаушының) SA адрес желісіне адрес кодын қоюынан басталады да, онда адрес цикл аяғына дейін қалады. Екі циклге бірдей, адрес циклі дерек жіберілімінің стробының (IOR’ немесе IOW’) басымен аяқталады. Адрес фазасында өз адресін таныған орындаушы құрылғы дерек жіберіліміне дайындық жағдайына ауысады.

Оқу циклінің дерек фазасында (5.3-сурет) процессор енгізу/шығару құрылғысынан (ЕШҚ) дерек оқылымының теріс строб сигналын (IOR’) қояды. Оған жауап ретінде орындаушы құрылғы желісіне (SD) өзінің дерек кодын (оқылатын деректер) қояды. Нақтылы қойылған уақыттан кейін процессор IOR’ стробын, сосын SA желісінен адрес кодын алып тастайды.

5.3 Сурет

ISA магистралы арқылы жазу циклінің дерек фазасында (5. 4-сурет) процессор дерек желісіне (SD) жазылатын дерек кодын қойып, сонымен қатар ЕШҚ-ға дерек жазылымының теріс строб сигналын IOW’ қояды. Оған жауап ретінде орындаушы құрылғы SD желісінен жазылатын дерек кодын қабылдайды.

5.4 Сурет

5.3 Жұмыстың тапсырмасы

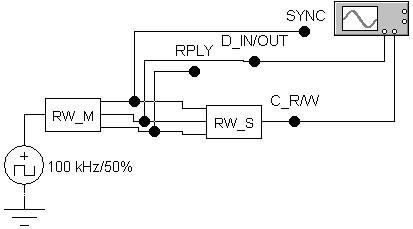

5.3.1 C:\EWB5PRO\MPS_Lab\Q-bus_1 файлын шығар. Онда асинхронды Q-bus магистралі арқылы бағдарламалы басқарылымды дерек жіберілімінің ұйымдастырылу принциптерін зерттеуге арналған құрылғының сұлбасы (5.5-сурет) келтірілген. Құрылғы екі блок түрінде жүзеге асырылған: жіберім бастаушысы RW_M (Master) және орындаушысы RW_S (Slave). Құрылғыдағы процестерді жеңілдету мақсатында, бастам сигналы ретінде құрылғының SD кірісіне қосылған генератордың сигналының теріс ауытқымасы пайдаланылады. Сұлбадағы блоктарды ашып, олардың құрылымымен таныс.

5.5 Сурет

5.3.2 Жіберімді басқару сигналдарының (SYNC, DIN/DOUT, RPLY, C_R/W) қалыптасуын осциллограф көмегімен бақылау арқылы құрылғының жұмысын зертте. Сигналдардың уақыттық диаграммаларын Paint бағдарламасында үстемелеу тәсілімен салып, олардың уақытқа байланысты параметрлерін (ұзақтығын, өзара ығысымын) анықта. Бақылауды жеңілдету мақсатында құрылғы жұмысының қарқыны арнайы баяулатылғанын ескеру керек.

5.3.3

C:\EWB5PRO\MPS_Lab\Q-bus_2

файлын шығар. Онда, жіберім процесс бастаушы

(Master) – микропроцессор (MP) мен орындаушы (Slave) – төрт перифериялық

құрылғының (Per) арасында информация жіберілуін

жүзеге асыруға мүмкіндік беретін құрылғының

сұлбасы (5.6-сурет) келтірілген. Сұлбадағы блоктарды ашып,

олардың құрылымымен таныс.

5.6 Сурет

5.3.4 Құрылғының жұмысын келесі тәртіппен зертте.

1. Деректер дайындау кезеңі:

- құрылғыны M (Mode – режим) ауыстырғышымен дайындық режиміне қой, бұл кезде сәйкесті индикатор жарық шығармау жағдайында тұрады, яғни, m = 0;

- V (Verify – проверка) ауыстырғышы да нөлдік жағдайға (v = 0) қойылу керек;

- A/D ауыстырғышын адрес енгізу режиміне (A/D = 1) қойып, перифериялық құрылғының адресін (0 – 3) енгіз;

- A/D ауыстырғышын дерек енгізу режиміне (A/D = 0) қойып, таңдалған перифериялық құрылғыға 0 – 7 түймелерінің біреуімен дерек енгізу керек. Енгізілетін санды 8– 15 арасында алу керек болса, онда 8 түймесін, сәйкесті индикатормен құпталатын, бірлік жағдайға қою керек;

- құрылғыны сілтеу режиміне (A/D = 1) қайтарып, сосын алдыңғы тәсілмен келесі перифериялық құрылғылардың адресін қойып, оларға әртүрлі деректер енгізуді жалғастыр;

- микропроцессордың (MP) буферлік регистріне де дерек енгіз, оның қойылым адресі – 5;

- микропроцессордың жұмыс кезінде дерек алмастыратын перифериялық құрылғысының адресін (мысалы, 1) қой, бұл адрес қойылым адресі – 4, адрестік регистрде сақталады.

2. Деректердің дұрыстығы мен сақталымын тексеру кезеңі:

- құрылғыны, V (Verify – тексеру) түймесін бірлік жағдайға қою арқылы, Бақылау режиміне ауыстыр;

- перифериялық құрылғының нөмерін N (Number – нөмер) түймесімен қойып, ондағы деректің дұрыстығы мен сақталымын тексер;

- N түймесін нөлдік жағдайға қайтар.

3. Дерек жіберілімін жүзеге асыру кезеңі:

- құрылғыны, M (Mode – режим) түймесін бірлік жағдайға қою арқылы жұмыс режиміне, яғни дерек жіберуді жүзеге асыру режиміне ауыстыр;

- микропроцессордың адрестік регистріне (қойылым адресі – 4) оның дерек алмастыратын перифериялық құрылғысының адресін қой. Ол үшін құрылғыны уақытша дайындық режиміне ауыстырып, адрес енгізілгеннен кейін жұмыс режиміне қайтару керек;

- R (Read) түймесін бір рет басу арқылы сілтенген перифериялық құрылғыдан (алдында қойылған 1-құрылғыдан) дерек оқылады, яғни ондағы деректің көшірмесі микропроцессордың дерек регистріне енгізіледі. Жұмыс нәтижесі сәйкесті 7-сегментті индикатормен көрсетіледі;

- басқа перифериялық құрылғының адресін (мысалы, 3) қойып, одан кейін W (Write) түймесін бір рет басу арқылы осы құрылғыға микропроцессордың дерек регистріндегі деректің көшірмесі жазылады;

- құрылғыны Бақылау режиміне ауыстырып (V түймесі), N түймесі арқылы перифериялық құрылғыларды тексеріп, орындалған жұмыс нәтижесінде микропроцессордың дерек регистріндегі және 1- мен 3-құрылғылардағы деректердің бірдейлігіне көз жеткіз;

- дерек жіберу операциясын әртүрлі нұсқада, мысалы, перифериялық құрылғылардың деректерін айналдыра ауыстыру түрінде қайтала.

5.4 Бақылау сұрақтары

1. Асинхронды, кезектесімді Q-bus магистралі арқылы бағдарламалы басқарылымды дерек жіберілімінің ұйымдастырылу принцитерін түсіндір.

2. Зертханалық жұмыста адрес жіберілуі қалай (синхронды немесе асинхронды) ұйымдастырылған? Ал деректердің?

3. Синхронды кезектесімсіз ISA магистралі арқылы бағдарламалы басқарылымды дерек жіберілімінің ұйымдастырылу принциптерін түсіндір.

4. Q-bus және ISA магистралдары арқылы асинхронды жіберілімнің ұйымдастырылуының негізгі айырмашылығы қандай?

6 №6 зертханалық жұмыс. Параллель интерфейс

6.1 Жұмыстың мақсаты:

- параллель интерфейстің құрылымының ұйымдастырылу принциптерін және оның жұмыс тәртібін игеру.

6.2 Теориялық мәліметтер

Интерфейстің негізгі элементтеріне дерек жіберу хаттамасы (тағайындалған қызметтерінің орындалу тәртібін тиянақтаушы ережелер жинағы), аппараттық бөлігі (құрылғының іс жүзіндегі құрылымы) және бағдарламалық қамтамасыз етуі жатады.

Параллель интерфейстердің қарапайым түрлеріне желілік қалыптастырғыштар (ЖҚ) мен буферлік регистрлер (БР) жатады. ЖҚ дерек көзін оның дерек жіберілуіне катыспаған кезінде, желіден ажыратады. Екі бағытты ЖҚ, басқару сигналына байланысты, информацияның жіберілу бағытын өзгертуге мүмкіндік береді. Үш жағдайлы БР, деректерді уақытша сақтаумен қатар, дерек порттарының желілерден басқару сигналдары арқылы ажыратылуын қамтамасыз етеді. Бұлардан күрделірек операциялар параллель интерфейстермен (перифериялық адаптермен) жүргізіледі.

6.3 Жұмыстың тапсырмасы

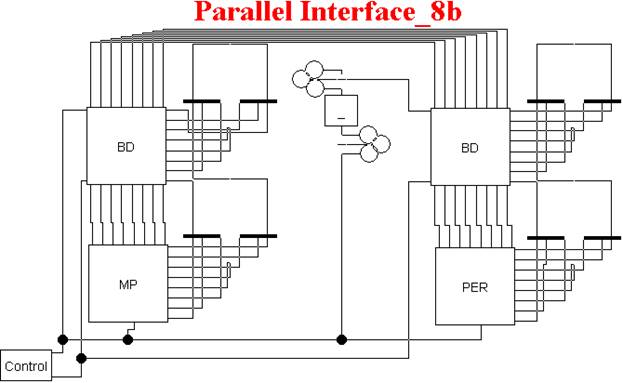

6.3.1 C:\EWB5PRO\MPS_Lab\ParInt_1 файлын шығар. Онда параллель интерфейстің құрылымы мен жұмыс тәртібін түсінуге мүмкіндік беретін, зерттеу сұлбасы (6.1-сурет) келтірілген.

6.1 Сурет

Сұлбадағы микропроцессор MP мен перифериялық құрылғы PER блоктары сырттай қарағанда іс жүзіндегі сәйкесті құрылғылардың жұмысын елестетеді. Олардың құрамына толық қызметті буферлер мен екі бағытты желілік қалыптастырғыштар енгізілген.

Құрылғылардың арасында информацияның екібағытты жіберілу принциптерін зертте. Жіберілім C (CLK) түймесін бір рет басу арқылы жүзеге асырылады, ал оның бағыты D (Direction) түймесімен басқарылады.

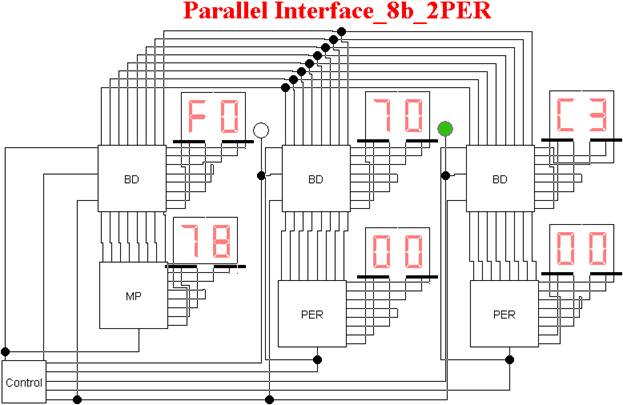

6.3.2 C:\EWB5PRO\MPS_Lab\ParInt_2файлын шығар. Онда, микропроцессордың екі портпен информация алмасуының ұйымдастырылуын елестету сұлбасы (6.2-сурет) келтірілген.

Құрылғының жұмысын зертте. Перифериялық құрылғылардың қажеттісін жандандыру P (Peripheral) түймесімен жүзеге асырылады.

Сурет 6.2

6.4 Бақылау сұрақтары

1. Желілік қалыптастырғыштар қандай қызмет атқарады?

2. Буферлік регистрлер қандай қызмет атқарады?

3. Зертханалық моделде дерек жіберілімінің екі бағыттылығы қалай жүзеге асырылады?

4. Intel 8255A (К580ВВ55А) перифериялық адаптерінің құрылымы мен жұмыс режимдерін түсіндір.

7 №7 зертханалық жұмыс. Тізбекті интерфейс

7.1 Жұмыстың мақсаты:

- тізбекті интерфейс құрылымының ұйымдастырылу принциптерін және оның жұмыс тәртібін игеру.

7.2 Теориялық мәліметтер

Дерек жіберілетін қашықтықтың ұлғайтылған кезінде деректерді жалғыз сигнал жолымен жіберу үшін оларды параллель түрінен тізбекті түрге түрлендіру қолданылады. Оған қоса, көптеген СҚ тізбекті кодпен жұмыс істейді, сондықтан олардың процессормен әрекеттесуі үшін деректерді параллель түрінен тізбекті түрге және керісінше түрлендіру қажет болады.

Тізбекті жіберілім хаттамасы екі түрде беріледі: асинхронды және синхронды.

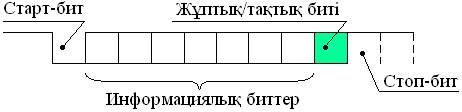

Асинхронды жіберілім кадры, яғни символды суреттеуші бит тобы, келесі форматта болады: жіберілім басы нолдік старт-битпен белгіленеді, одан кейін 5...8 информациалық биттер жіберіледі (кіші разрядынан бастап), сосын міндетті емес 2 модулімен Бақылау биті (жұптық/тақтық биті) және ақырында жіберілім кадры 1; 1,5 немесе 2 бірлік стоп-битімен бітеді (7.1-сурет). Сонымен, қабылдауыш сигналдың өзімен синхрондалады.

Сурет 7.1

Синхронды жіберілім екі түрде жүзеге асырылады – ішкі және сыртқы синхрондалымды.

Ішкі синхрондалымда дерек массивінің алдында слова – синхросимвол сөздері жіберіледі (бір немесе екі). Жіберілім жоқ кезінде таратқыш жұмысын тоқтатпайды да, жіберім жолына синхросимволдар жіберіп тұрады.

Сыртқы синхрондалымда байланыс арнасына, дерек жіберіліміне сәйкесті уақыт аралығын белгілеуші строб-сигнал жіберілетін қосымша жол енгізіледі. Строб ауытқымалары массив жіберілімінің басы мен аяғын белгілейді, бұл аралықта символдар бұрынғыдай қатар жіберіледі (старт- және стоп-биттерінсіз).

7.3 Жұмыстың тапсырмасы

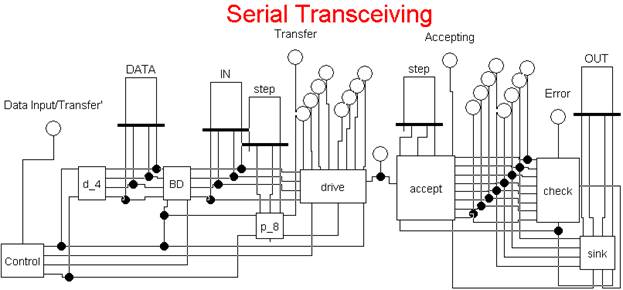

7.3.1 C:\EWB5PRO\MPS_Lab\SerInt файлын шығар. Онда, тізбекті интерфейстің құрылымының ұйымдастырылу принциптерін және жұмыс тәртібін түсінуге мүмкіндік беретін сәйкесті құрылымның сұлбасы (7.2-сурет) келтірілген.

Сурет 7. 2

Құрылғы екі блоктан тұрады: дерек таратқышынан және қабылдағышынан. Дерек көзінің (d_4) қалыптастырған жіберілімге арналған төрт разрядты сөзі данных буферінде (BD) сақталады. Бұл сөз drive (жіберу) блогында төрт қызмет битімен (старт-бит, стоп-бит, жұптық Бақылау белгісі және жұптық биті) қоршалады да, p_8 блогында қалыптастырылған сегіз тактілік импулспен жалғыз байланыс жолы арқылы жіберіледі.

accept (енгізу) блогында параллель түрге түрлендірілген деректер check (тексеру) блогында қызмет биттерінің сәйкестілігіне тексеріледі де, олардың дұрыстық жағдайында қоршалымынан босатылған төрт разрядты сөз деректердің шығыс буферіне sink (қабылдау) жіберіледі. Жіберілім қателігі табылған кезде, ол сәйкесті индикатор (Error) арқылы хабарланады да, төрт разрядты сөз бөлініп шығарылмайды.

Тізбекті интерфейстің жұмысын келесі тәртіппен тексер:

- D (Data Input/Transfer') түймесімен құрылғыны дерек таңдау (Data Input) режиміне қойып, С (CLK) түймесін бір рет басу арқылы кез келген бір санды таңдап (ұстап алып), оны дерек буферінде BD сақта;

- D түймесімен құрылғыны жіберім режиміне (Transfer) ауыстыр.

Құрылғының бұдан арғы әрекеттері автоматты түрде өздігінен жүзеге асырылады да, түрлендірімдер мен жіберілім нәтижелерін бақылау ғана керек болады. Жіберілім біткеннен кейін (жіберілімнің дұрыс кезінде де, қателік табылған кезде де) информациалық индикаторлардың көрсетімдері арқылы алынған нәтижені талда.

Осы жолмен тәжірибені бірнеше рет қайтала.

7.4 Бақылау сұрақтары

1. Тізбекті интерфейс қандай қызмет атқарады?

2. Тізбекті интерфейстің асинхронды режимдегі жұмыс тәртібін түсіндір.

3. Перифериялық Intel 8255A (К580ВВ55А) адаптерінің құрылымын және жұмыс режимдерін түсіндір.

Әдебиеттер тізімі

1. Угрюмов Е. П. Цифровая схемотехника. – СПб.: БХВ-Петербург, 2004.

2. Бойко В.И. и др. Схемотехника электронных устройств. Микропроцессоры и микроконтроллеры. – СПб.: БХВ-Петербург, 2004.

3. Уэйкерли Дж. Ф. Проектирование цифровых устройств. – М.: Постмаркет, 2002.

4. Сугано Т. Дж., Уидмер Н. С. Цифровые системы. Теория и практика: Пер. с англ. – М.: Издательский дом “Вильямс”, 2004.

5. Опадчий Ю. Ф., Глудкин О. П., Гуров А. И. Аналоговая и цифровая электроника / Под ред. О.П. Глудкина. – М.: Радио и связь, 2003.

6. Токхейм Р. Основы цифровой электроники: Пер. с. англ. – М.: Мир, 1988.

7.

Шанаев О.Т. Система моделирования Electronic Workbench / казақ және орыс тілдерінде. – Алматы, 2003.

Мазмұны

1 №1 зертханалық жұмыс. ROM түрлі жадылық құрылғылар

2 №2 зертханалық жұмыс. ЖҚ-дың түпнегіздік құрылымдары

3 №3 зертханалық жұмыс. ЖҚ-дың 2DM құрылымы

4 №4 зертханалық жұмыс. Информация енгізу құрылғысы

5 №5 зертханалық жұмыс. Деректердің бағдарламалы жіберілуі

6 №6 зертханалық жұмыс. Параллель интерфейс