Некоммерческое акционерное общество

АЛМАТИНСКИЙ УНИВЕРСИТЕТ ЭНЕРГЕТИКИ И СВЯЗИ

Кафедра «Электроника»

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ

Методические указания к выполнению лабораторных работ

для студентов всех форм обучения специальности

5B071900 – Радиотехника, электроника и телекоммуникации

Алматы 2011

СОСТАВИТЕЛЬ: У.Т.Шанаев. Цифровые устройства и микропроцессоры. Методические указания к выполнению лабораторных работ по соответствующей дисциплине для студентов всех форм обучения специальности 5В071900 – Радиотехника, электроника и телекоммуникации. – Алматы: 2011. – 48 с.

В методической разработке приведены работы, предназначенные для организации лабораторных занятий по дисциплине “Цифровые устройства и микропроцессоры” для специальности 5B071900 – Радиотехника, электроника и телекоммуникации и охватывающие по содержанию учебный материал всего курса.

Первые три работы посвящены изучению функциональных характеристик основополагающих компонентов цифровых систем и освоению порядка пользования необходимым для проведения исследований инструментарием. Выполнение этой группы работ организовывается как в виде виртуальных экспериментов, осуществляемых посредством моделирования исследуемых устройств в программной среде Electronics Workbench, так и путем практической проверки работы соответствующих устройств, установленных на стенде PU-2000 фирмы Degem Systems.

Следующие три работы посвящены изучению внутренней структуры отдельных составляющих блоков микропроцессорной системы (системы памяти, устройств ввода и микропроцессора). Выполнение этой группы лабораторных работ осуществляется путем исследования характера функционирования построенных в программной среде Electronics Workbench виртуальных моделей соответствующих устройств.

В заключительных двух работах, выполняемых как с помощью программного симулятора на основе микропроцессора Intel 8085, так и на лабораторном стенде с реальной системой на основе того же микропроцессора, изучаются различные программные структуры, составленные на языке Ассемблер.

Ил. 27, табл. 6, библиогр. – 7 назв.

Рецензент: д-р. физ-мат. наук, проф. С. Б. Бимурзаев

Печатается по плану издания Некоммерческого акционерного общества “Алматинский университет энергетики и связи” на 2011 г.

© НАО “Алматинский университет энергетики и связи”, 2011 г.

Введение

Курс “Цифровые устройства и микропроцессоры” посвящен изучению функциональных основ устройств цифровых систем и структурных принципов их построения. Для обеспечения формирования у студентов теоретических знаний по изучаемому курсу и приобретения ими практических навыков по разработке цифровых систем различного характера функционирования необходима организация выполнения лабораторных работ по основополагающим темам курса.

Первые три работы из предлагаемой методической разработки предназначены для изучения функциональных характеристик основополагающих компонентов цифровых систем (а именно: логических элементов, комбинационных и последовательностных устройств) и освоению порядка пользования необходимым для проведения исследований инструментарием. Выполнение этой группы работ организовывается как в виде виртуальных экспериментов, осуществляемых посредством моделирования исследуемых устройств в программной среде Electronics Workbench, так и путем практической проверки работы соответствующих устройств, установленных на стенде PU-2000 фирмы Degem Systems.

При разработке микропроцессорных систем учитываются два взаимосвязанных и взаимообусловленных фактора: конструирование аппаратной части системы (hardware), обеспечивающей физическую реализацию решения поставленной задачи, и определения системы команд (software), позволяющей составить программу действий и взаимодействий функциональных компонентов системы по решению задачи. Следовательно, для получения наиболее полного знания о микропроцессорной системе требуется освоение как ее аппаратной части, так и программной части. Следующие три работы в методической разработке посвящены изучению внутренней структуры отдельных составляющих блоков микропроцессорной системы (системы памяти, устройств ввода и микропроцессора) и принципов их функционирования. Выполнение этой группы лабораторных работ организовывается в виде виртуальных экспериментов, осуществляемых посредством моделирования исследуемых устройств и их функционирования в программной среде Electronics Workbench.

В остальных двух работах, выполняемых как с помощью программного симулятора на основе микропроцессора Intel 8085, так и на лабораторном стенде с реальной системой на основе того же микропроцессора (разработка фирмы Degem Systems), изучаются различные программные структуры, составленные на языке Ассемблер.

Во всех работах предлагаются задания для самостоятельной работы студентов (СРС), выполнение которых способствует закреплению как приобретенных ими теоретических знаний, так и формированию навыков по применению этих знаний для самостоятельной разработки аппаратных и программных структур.

1 Лабораторная работа. Комбинационные устройства

Цель работы:

- изучение взаимозависимости уровней входных и выходных сигналов логических элементов;

- освоение методики построения схем комбинационных устройств на основе логических элементов;

- освоение методики работы с различными инструментальными средствами, применяемыми для разработки и исследования работы цифровых устройств.

1.1 Оборудование рабочего места:

- компьютер, программная среда Electronics Workbench;

- лабораторный стенд PU-2000;

- съемные платы EB-131 и EB-132;

- соединительные провода и перемычки.

1.2 Практические сведения и методические рекомендации

Наиболее простой метод исследования характера работы логического элемента (или более сложного цифрового устройства) заключается в подаче всевозможных комбинаций логических уровней на его входы и наблюдении уровня выходного сигнала. Именно на метод рассчитаны устройства, встроенные на платах, используемых в практических экспериментах во второй части работы, реализуемых на лабораторном стенде.

Более наглядный результат можно получить путем подачи на входы элемента прямоугольные импульсы различной частоты и сопоставления наблюдаемых временных диаграмм входных и выходных сигналов элемента (или устройства) с помощью логического анализатора (Logic Analyzer). Этот метод предложен для проведения моделирующих экспериментов в первой части работы.

В программу Electronics Workbench встроен прибор под названием “логический преобразователь” (Logic Converter), с помощью которого можно реализовать все этапы синтеза схемы комбинационного устройства. Именно применение этого прибора предложено для создания схемы комбинационного устройства в соответствующем рабочем задании лабораторной работы.

Еще одно средство, которое необходимо взять в свое вооружение, – это создание подсхем. Одним из достоинств таких подсхем является возможность их повторного и многократного использования и в других экспериментах путем переноса их из одного файла в другой. Другим достоинством использования подсхем является возможность представления объемных схем в виде нескольких функциональных блоков структурной схемы, что несомненно способствует их наглядности. В этой работе, в качестве первого опыта, предлагается создать подсхему формирования одиночных импульсов от нажатия клавиши.

Перед выполнением лабораторной работы необходимо изучить методику работы с предлагаемыми инструментами и метода оформления схемных фрагментов в виде отдельных блоков в [1]. Освоение этих методов и средств закладывает основу для организации дальнейших исследований, где они будут применяться в различных сочетаниях в зависимости от типа исследуемых устройств и характера их управляющих сигналов. Их необходимо активно применять и при выполнении курсовых работ [2], что ускорит их реализацию.

Практическая часть работы проводится с помощью съемных плат ЕB-131 и EB-132, устанавливаемых на лабораторном стенде.

1.3 Рабочее задание

1.3.1 Исследовать работу логических элементов:

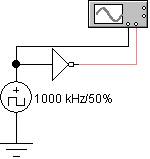

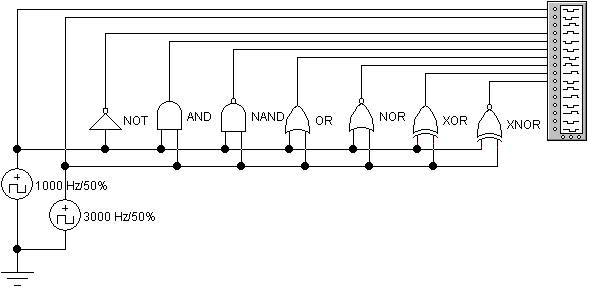

- собрать схему для совместного исследования трехвходовых логических элементов с помощью логического анализатора (см. рисунок 1.1);

- по полученным результатам проанализировать логику работы представленных в схеме элементов.

Рисунок 1.1

1.3.2 Создать блок формирования одиночных импульсов:

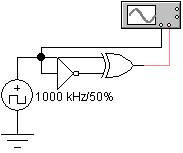

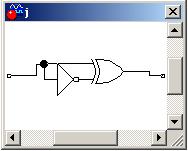

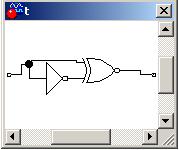

- пронаблюдать задержку сигнала на логическом элементе (см. рисунок 1.2, a) и измерить длительность этой задержки;

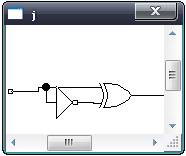

- собрать схему формирования одиночного импульса (см. рисунок 1.2, b), исследовать ее работу и оформить ее в виде отдельного блока (см. рисунок 1.2, c). В дальнейшем этот блок может быть использован для формирования одиночного импульса от нажатия клавиши.

|

|

|

|

|

a |

b |

c |

Рисунок 1.2

1.3.3 Разработать схему комбинационного устройства на основе логических элементов, реализующую таблично заданную функцию по предложенному преподавателем варианту (см. таблицу 1.1):

Т а б л и ц а 1.1

|

A |

B |

C |

F0 |

F1 |

F2 |

F3 |

F4 |

|

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

- получить минимизированное логическое выражение, соответствующее табличному представлению заданной функции;

- собрать схему устройства по полученному выражению;

- преобразовать логическое выражение к виду, предназначенному для реализации схемы на основе элементов NAND;

- собрать схему устройства по преобразованному выражению;

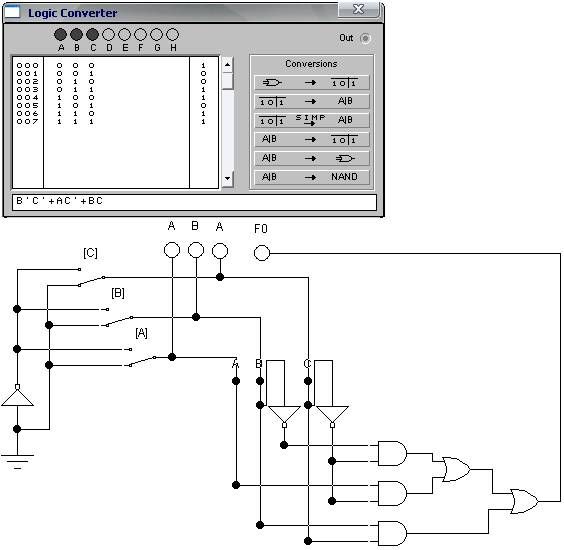

- синтезировать схему устройства с помощью логического преобразователя (Logic Converter);

- подключить к полученным схемам необходимые для проведения исследования дополнительные элементы (соответственно поименованные ключи и индикаторы);

- подавая всевозможные комбинации логических уровней на входы схем и наблюдая за уровнями выходных сигналов, проверить их работу.

В качестве иллюстрации на рисунке 1.3 представлена реализация схем по варианту F0, осуществленная с помощью логического преобразователя.

Рисунок 1.3

1.3.4 Исследовать практически логику работы предложенного преподавателем фрагмента схемы на платах EB-131 и EB-132:

- установить необходимую плату (EB-131 или EB-132) на лабораторный стенд;

- подключить входы фрагмента схемы к переключателям, размещенных на плате, с помощью соединительных проводов или перемычек;

- исследовать логику работы схемы, подавая сигналы различного уровня на ее входы с помощью переключателей и наблюдая за состояниями индикаторов на выходе;

- результаты исследования оформить в виде таблицы и по составленной таблице истинности написать соответствующее логическое выражение, характеризующее работу исследованной схемы.

1.4 Задания на СРС

1.4.1 Исследовать возможности изменения длительности одиночных импульсов, формируемых с помощью элемента XOR.

1.4.2 Исследовать возможности формирования одиночных импульсов с помощью элементов AND, NAND, OR, NOR и XNOR объяснить полученные результаты.

1.4.3 Реализовать схему предложенного в 1.3.3 схемы устройства на основе элементов NOR

1.5 Контрольные вопросы

1. Опишите логику работы исследованных в лабораторной работе элементов.

2. Как осуществляется наращивание числа входов элементов AND и OR?

3. Как можно осуществить наращивание числа входов элементов NAND и NOR?

4. Объясните возможности реализации функций элементов NAND и NOR с помощью базовых элементов.

5. Объясните порядок синтеза схем комбинационных устройств.

6. Каким образом необходимо преобразовать дизъюнктивное логическое выражение для построения схемы на основе элементов NAND?

7. Каким образом получить выражение для реализации схемы комбинационного устройства на основе элементов NOR?

8. Можно ли использовать логический преобразователь для построения схем комбинационных устройств с несколькими выходами? Если да, то как?

9. Как изменить в три раза длительность одиночных импульсов, формируемых схемой на рисунке 1.2, b?

2 Лабораторная работа. Типовые комбинационные устройства

Цель работы:

- изучение принципов работы дешифратора;

- освоение способов применения дешифратора для реализации логических функций;

- изучение принципов работы мультиплексора;

- освоение методов настройки универсального логического модуля на основе мультиплексора.

2.1 Оборудование рабочего места:

- компьютер, программная среда Electronics Workbench;

- лабораторный стенд PU-2000;

- съемные платы EB-134 и EB-132;

- соединительные провода и перемычки.

2.2 Рабочее задание

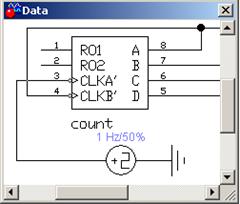

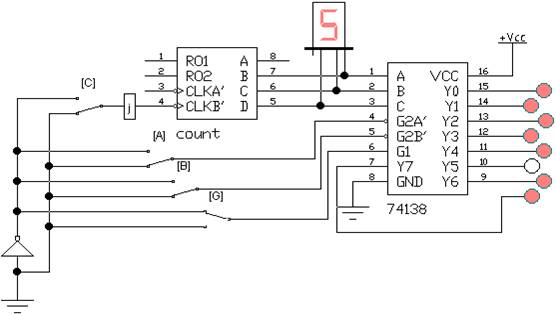

2.2.1 Исследовать работу дешифратора 74138 по схеме на рисунке 2.1. Здесь для подачи адресного кода дешифратора использован условный счетчик (count). В схеме использован формирователь одиночного импульса от нажатия клавиши (j), созданный в предыдущей работе.

Рисунок 2.1

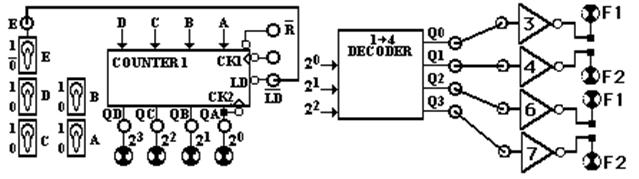

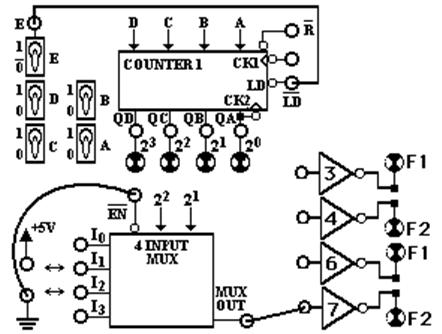

2.2.2 Исследовать работу мультиплексора 74153 с помощью логического анализатора (см. рисунок 2.2). Здесь счетчик 1 используется для подачи информационных сигналов, а счетчик 2 – для адресных кодов и разрешающего сигнала.

Рисунок 2.2

2.2.3 Исследовать практически логику работы дешифратора, размещенного на панели EB-134:

- установить съемную плату EB-134 на лабораторный стенд и выполнить соединения, необходимые для исследования работы дешифратора (см. рисунок 2.3). Счетчик 1 здесь используется в качестве регистра хранения с параллельной загрузкой и применяется для подачи на дешифратор адресного кода (22 à A1, 21 à A0) и управляющего сигнала (20 à EN). Эти соединения выполнены внутренне на самой плате;

Рисунок 2.3

- разместить плату EB-132 рядом с основным стендом и объединить ее с ним по питанию. Светодиоды, размещенные на этой плате, используются для наблюдения за уровнями выходных сигналов дешифратора;

-

изменяя

содержимое счетчика, тем самым и уровни входных сигналов (адресный код и

управляющий сигнал), составить таблицу истинности дешифратора. Двоичное

число, загружаемое в счетчик, устанавливается с помощью соответствующих

переключателей и фиксируется сигналом ![]() , подаваемого от переключателя Е.

, подаваемого от переключателя Е.

2.2.4 Исследовать практически логику работы мультиплексора, размещенного на панели EB-134:

- выполнить соединения, необходимые для исследования режимов работы мультиплексора (см. рисунок 2.4). Счетчик 1 здесь используется для подачи на мультиплексор адресного кода (22 → A1, 21 → A0). Эти соединения выполнены внутренне на самой плате. Для активизации мультиплексора, его разрешающий вход (EN) должен быть подключен к “общему проводу”;

- изменяя при каждом варианте адресного кода уровни сигнала на информационных входах мультиплексора, запишите результаты наблюдения за уровнем его выходного сигнала в виде таблицы.

Рисунок 2.4

2.3 Задания на СРС

2.3.1 Построить схему одного из таблично заданных устройств (по предложенному преподавателем варианту из таблицы 2.1) на основе дешифратора 74138. Проанализировать ее работу, дополнив схему необходимыми для проведения исследования элементами.

2.3.2 Построить схему одного из таблично заданных устройств (по предложенному преподавателем варианту из таблицы 2.1) на основе мультиплексора 74153. Проанализировать ее работу, дополнив схему необходимыми для проведения исследования элементами.

Т а б л и ц а 2.1

|

A |

B |

C |

F1 |

F2 |

F3 |

F4 |

|

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

1 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

1 |

1 |

2.4 Контрольные вопросы

1. Объясните принципы работы дешифратора.

2. Создайте схему дешифратора на основе логических элементов с указанными преподавателем характеристиками.

3. Объясните принципы работы мультиплексора.

4. Создайте схему мультиплексора на основе логических элементов и дешифратора.

5. Объясните метод настройки УЛМ, когда число переменных реализуемой функции равно числу адресных входов мультиплексора.

6. Объясните методы настройки УЛМ, когда число переменных реализуемой функции больше числа адресных входов мультиплексора.

3 Лабораторная работа. Последовательностные устройства

Цель работы:

- освоение принципов построения и режимов работы асинхронных триггеров;

- освоение принципов построения и режимов работы синхронных триггеров со статическим управлением;

- изучение режимов работы синхронных триггеров с динамическим управлением;

- освоение различных режимов ввода информации в регистры;

- освоение принципов работы и структурных различий суммирующих и вычитающих счетчиков;

- освоение структурных принципов изменения модуля счета счетчика.

3.1 Оборудование рабочего места:

- компьютер, программная среда Electronics Workbench;

- лабораторный стенд PU-2000;

- съемная плата EB-133;

- соединительные провода и перемычки.

3.2 Рабочее задание

3.2.1 Собрать схему синхронного RS-триггера на элементах NAND (см. рисунок 3.1) и исследовать режимы его работы путем изменения уровней входных сигналов. В этой и следующих работах источник логических уровней оформлен в блок под названием “0_1”.

Рисунок 3.1

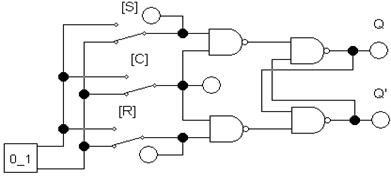

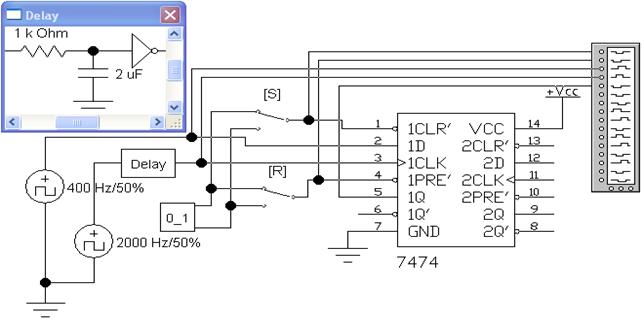

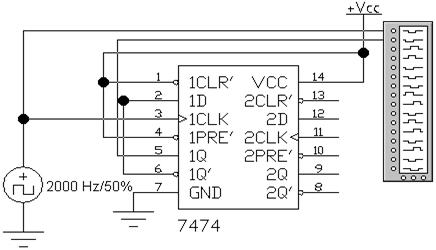

3.2.2 Исследовать режимы работы одного из D-триггеров в микросхеме 7474 (см. рисунок 3.2) с помощью логического анализатора.

В начале анализа переключатели R и S должны быть установлены в единичное состояние. В процессе анализа быстрым двойным нажатием одного из клавиш, соответствующих этим переключателям, осуществить асинронную установку или очистку триггера.

Рисунок 3.2

3.2.3 Проанализировать работу D-триггера в счетном режиме, для чего его инверсный выход необходимо замкнуть на информационный вход (см. рисунок 3.3).

Рисунок 3.3

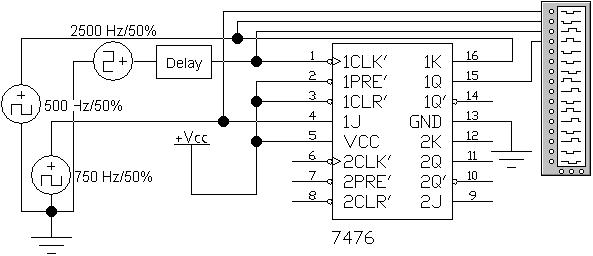

3.2.4 Исследовать режимы работы JK-триггера (см. рисунок 3.4).

Установку и очистку триггера осуществлять кратковременным изменением уровней сигнала на входах R и S в процессе анализа. (как в 3.2.2).

Рисунок 3.4

3.2.5 Для использования в дальнейших экспериментах создайте блоки (подсхемы) динамического источника данных (Data) и формирователей одиночных импульсов (j и t) соответствующей полярности (см. рисунок 3.5).

|

|

|

|

Рисунок 3.5

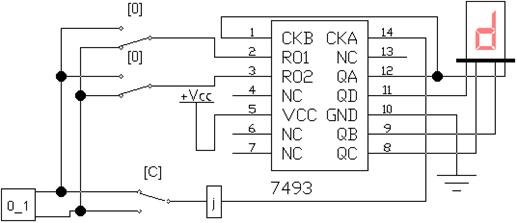

3.2.6 Собрать схему исследования счетчика 7493 (см. рисунок 3.6). Подавая тактовые сигналы с помощью клавиши С, проверить работу счетчика. Проверьте назначение сигналов на выводах R01 и R02 микросхемы триггера.

Рисунок 3.6

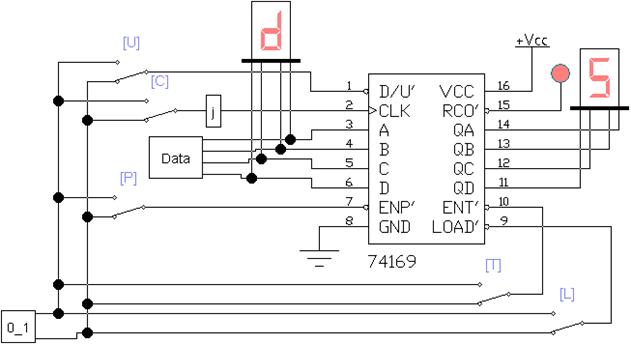

3.2.7 Собрать схему для исследования реверсивного счетчика 74169 (см. рисунок 3.7) и проанализировать режимы его работы.

Рисунок 3.7

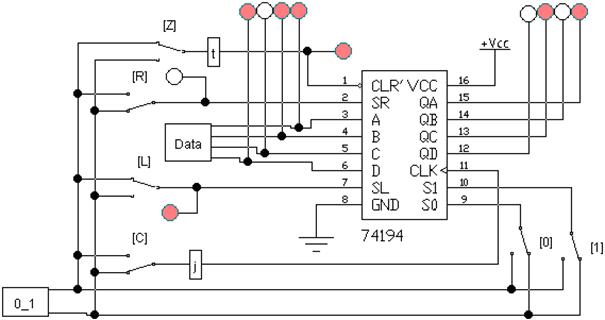

3.2.8 Собрать схему для исследования режимов работы универсального регистра 74194 (см. рисунок 3.8) и проанализировать режимы его работы.

Рисунок 3.8

3.2.9 Установить плату EB-133 на лабораторный стенд и проверить режимы работы предложенных преподавателем устройств (D- и JK-триггеров, счетчика и регистра), размещенных на плате.

3.3 Задания на СРС

3.3.1 Построить схему счетчика с возможностью предварительной установки модуля счета.

3.3.2 Построить схему восьмиразрядного регистра на основе микросхем регистров 74194. Проанализировать ее работу, дополнив схему необходимыми для проведения исследования элементами.

3.4 Контрольные вопросы

1. Объясните структуру и режимы работы асинхронного RS-триггера с прямыми и инверсными входами.

2. Объясните структуру и режимы работы синхронного RS-триггера со статическим управлением.

3. В чем состоит различие статического и динамического управления триггерами?

4. Как использовать D-триггер в качестве счетного триггера?

5. Какие функции выполняют сигналы на входах R и S микросхем D- и JK-триггеров?

6. Поясните принципы последовательного и параллельного вводов информации в регистр.

7. Как можно получить счетчик с модулем счета 13?

4 Лабораторная работа. Запоминающие устройства

Цель работы:

- изучение принципов построения ROM;

- приобретение навыков программирования PROM;

- изучение базовых структур ЗУ и освоение принципов их построения.

4.1 Оборудование рабочего места и файлы:

- компьютер, программа Electronics Workbench Professional;

- файл ROM(M) 16x7.ewb;

- файл PROM 16x7.ewb;

- файл RAM 2D_8x4.ewb;

- файл RAM_3D_16x4.ewb;

- файл RAM 2DM_32x4.ewb.

4.2 Практические сведения и методические рекомендации

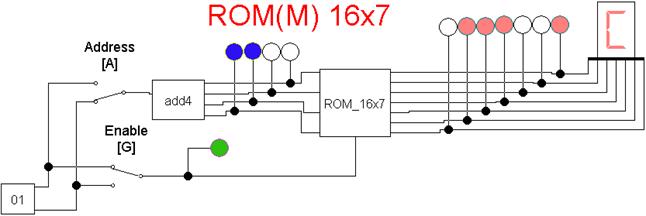

Первое задание лабораторной работы посвящено изучению структуры и принципов работы постоянного запоминающего устройства (ПЗУ) с неизменяемой информацией для отображения шестнадцатеричных символов на 7-сегментном индикаторе (см. рисунок 4.1).

Рисунок 4.1

Блок ПЗУ (подсхема ROM_16x7) cостоит из дешифратора на 16 выходов (микросхема 74154) и матрицы памяти с организацией 16x7, оформленных в виде подсхем с соответствующими наименованиями. Разрешение на работу дешифратора обеспечивается положительным уровнем сигнала от клавиши E (Enable). Адреса строк памяти (7-разрядных ячеек) формируются посредством 4-разрядного счетчика (подсхема add4).

Второе задание посвящено изучению структуры (см. рисунок 4.2) и принципов программирования (прошивки) заготовки микросхемы (в нашем случае подсхемы chip 16x7), в где исходном состоянии имеются все перемычки в пересечениях шестнадцати горизонталей (выходных линии дешифратора) и семи вертикалей (разрядных линии).

Рисунок 4.2

Программирование микросхемы осуществляется в следующем порядке:

- нажатием кнопки пуска (Activate simulation), активизировать схему;

- клавишей W (Write/Read) перевести установку в режим программирования (светится соответствующий светодиод);

- установить адрес программируемой строки матрицы памяти;

- подготовить информацию для программирования нажатием клавиш, соответствующих ликвидируемым сегментам предполагаемого к размещению на этой строке символа;

- кратковременным нажатием клавиши P (programming) обеспечить программирование строки (прошивку информации).

- восстановить исходные состояния клавиш сегментов;

- клавишей W (Write/Read) перевести установку в режим чтения информации и проверить прошитые в строках матрицы памяти информацию.

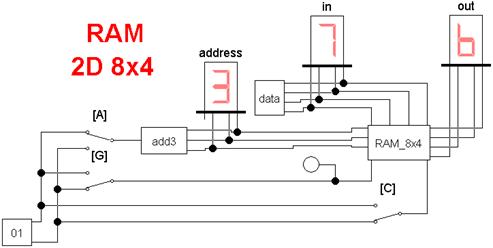

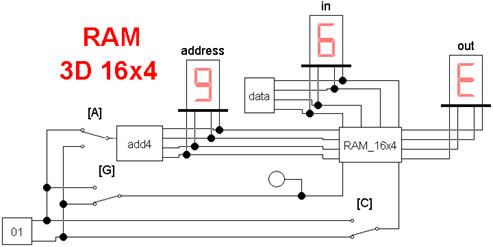

Следующие задания лабораторной работы, посвященные изучению различных структур систем памяти (2D, 3D, 2DM) и принципов их работы, выполняются на соответствующих моделях (см. рисунки 4.3-4.5).

Схема для исследования системы памяти по структуре 2D (см. рисунок 4.3) состоит из следующих блоков, оформленных в виде соответствующих подсхем:

- трехразрядный формирователь адреса (add3) на основе счетчика;

- четырехразрядный источник данных (data) на основе счетчика;

- система памяти RAM_8x4, в состав которой входят дешифратор на восемь выходов (dc8) и матрица запоминающих ячеек (8x4), содержащая 8 ячеек (rg4) на основе регистров. Каждый из ячеек матрицы памяти снабжен индикатором, что позволяет вести наблюдение за выбором ячейки памяти во время эксперимента.

Рисунок 4.3

Схема для исследования системы памяти по структуре 3D (см. рисунок 4.4) состоит из следующих блоков, оформленных в виде соответствующих подсхем:

- четырехразрядный формирователь адреса (add4) на основе счетчика;

- четырехразрядный источник данных (data) на основе счетчика;

- система памяти RAM_16x4, в состав которой входят сдвоенный дешифратор (2dc4) и матрица запоминающих ячеек (16x4), содержащая 16 ячеек (rg4) на основе регистров.

Рисунок 4.4

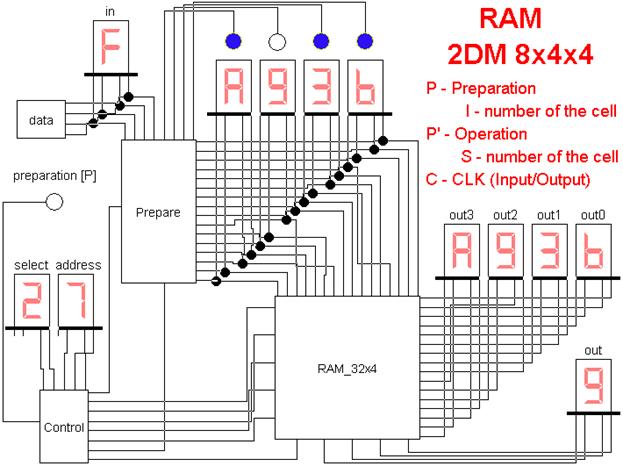

Схема для исследования системы памяти по структуре 2DM (см. рисунок 4.5) содержит в своем составе следующие блоки:

- блок памяти RAM_32x4 по структуре 2DM;

- блок подготовки данных Prepare;

- блок управления Control.

Блок памяти RAM_32x4 состоит из следующих подблоков:

- матрица элементов памяти 32х4;

- блок дешифрации строки dc8;

- блок выбора ячейки из строки (при чтении) mux4.

Матрица памяти 32х4 представляют собой (логически) 8 строк, в каждой из которых размещен блок cell_4x4, состоящая из четырех 4-разрядных ячеек памяти rg4. Физически блок памяти 32х4 реализован (с целью удобства соединения и обзора) в виде объединения двух блоков 16х4, составленных из четырех блоков cell_4x4. Каждый из внутренних блоков матрицы памяти 32х4 снабжен индикатором, что позволяет вести наблюдение за выбором строки и ячейки памяти во время эксперимента.

Блок dc8, предназначенный для выбора строки памяти, представляет собой дешифратор на восемь выходов.

Блок mux4, собранный на двух сдвоенных 4-входовых мультиплексорах, позволяет выбрать ячейку из активизированной строки.

Блок Prepare предназначен для предварительной подготовки четырех 4-разрядных слов, предполагаемых для одновременной записи в одну из строк матрицы памяти. На этапе подготовки эти слова временно сохраняются во внутреннем блоке in_4, составленного из четырех 4-разрядных ячеек памяти in. Выбор одной из этих ячеек осуществляется с помощью дешифраторного блока dc4 и блока его адресации 0_3.

В блоке Control объединены управляющие клавиши и дополнительные элементы, обеспечивающие режимы работы устройства. Устройство может работать в трех режимах – подготовки данных для записи, записи и чтения.

Рисунок 4.5

Режим подготовки данных осуществляется следующим образом:

- клавишей P (Prepare) перевести устройство в режим подготовки данных (светится соответствующий индикатор);

- клавишей I (In) выбрать одну из четырех ячеек блока in_4 (указывает соответствующий индикатор);

- клавишей С (CLK) записать в эту ячейку одну из чисел, формируемых блоком данных data.

Перевод в режим записи/чтения осуществляется повторным нажатием клавиши P (индикатор гаснет).

В режиме записи:

- клавишей A выбрать необходимую строку матрицы памяти (указывает соответствующий 7-сегментный индикатор);

- клавишей С (CLK) записать подготовленные данные в выбранную строку матрицы памяти.

В режиме чтения:

- клавишей A выбрать необходимую строку матрицы памяти (указывает соответствующий 7-сегментный индикатор);

- клавишей S (Select) выбрать определенную ячейку из активизированной строки матрицы памяти (указывает соответствующий 7-сегментный индикатор).

4.3 Рабочее задание

4.3.1 Изучить принципы построения ROM и порядок работы с ним:

- открыть файл ROM(M) 16x7.ewb, раскрыть подсхемы различных блоков (см. рисунок 4.1) и изучить их структуру;

- изменяя адреса ячеек памяти клавишей A (Address), проверить записанную в соответствующих строках памяти информацию.

4.3.2 Изучить принципы построения PROM и порядок его программирования:

- открыть файл PROM 16x7.ewb (см. рисунок 4.2), изучить структуру матрицы chip16x7 и устройство программатора (programmer), раскрыв соответствующие подсхемы;

- запрограммировать строки матрицы памяти для отображения символов из следующего списка: L, J, H, P, S, U, –, _, e, n, q, r и др.

4.3.3 Изучить принципы построения системы памяти по структуре 2D:

- открыть файл RAM 2D_8x4.ewb, где представлена схема для исследования системы памяти по структуре 2D и изучения принципа ее работы (см. рисунок 4.3). Раскрыть подсхемы блоков и изучить их структуру;

- исследовать работу представленной системы памяти, записывая в ячейки определенную информацию и проверяя затем их сохранность.

4.3.4 Изучить принципы построения системы памяти по структуре 3D:

- открыть файл RAM 3D_16x4.ewb, где представлена схема для исследования системы памяти по структуре 3D и изучения принципа ее работы (см. рисунок 4.4). Раскрыть подсхемы блоков и изучить их структуру;

- исследовать работу представленной системы памяти, записывая в ячейки определенную информацию и проверяя затем их сохранность.

4.3.5 Изучить принципы построения системы памяти по структуре 2DM:

- открыть файл RAM 2DM_32x4.ewb, где представлена схема исследования блока памяти по структуре 2DM (см. рисунок 2.3) и изучить структуру ее составных блоков, раскрывая их и изучая соответствующий пояснительный текст;

- исследовать работу устройства памяти RAM_2DM, записав информацию во все строки матрицы, а затем проверить возможность считывания из конкретной ячейки памяти.

4.4 Задания на СРС

4.4.1 Построить схему устройства памяти, работающего в стековом режиме.

4.4.2 Построить схему устройства памяти с возможностью записи в последовательные ячейки памяти, начиная с определенной ячейки.

4.5 Контрольные вопросы

1. Назовите основные параметры запоминающих устройств.

2. В чем состоит назначение ROM?

3. Какие элементы памяти используются в различных типах ROM?

4. Как и кем программируются PROM?

5. В чем состоит различие EPROM и EEPROM?

6. Какая схемотехника элементов памяти обеспечивает максимальное быстродействие RAM?

7. В чем состоит принципы построения RAM с одномерной и двумерной адресацией?

8. Сравните преимущества и недостатки структур 2D и 3D.

9. Объясните принципы осуществления структуры памяти 2DM и ее основные достоинства по сравнению с остальными структурами.

5 Лабораторная работа. Устройство ввода информации

Цель работы:

- освоение принципов построения устройств ввода информации на основе приоритетных шифраторов;

- приобретение навыков по совершенствованию работы устройства;

- приобретение навыков по созданию многорежимных устройств.

5.1 Оборудование рабочего места и файлы:

- компьютер, программа Electronics Workbench Professional;

- файл Input Unit (addressable).ewb;

- файл Input Unit (multiplexing).ewb;

- файл Input Unit (integration).ewb.

5.2 Практические сведения и методические рекомендации

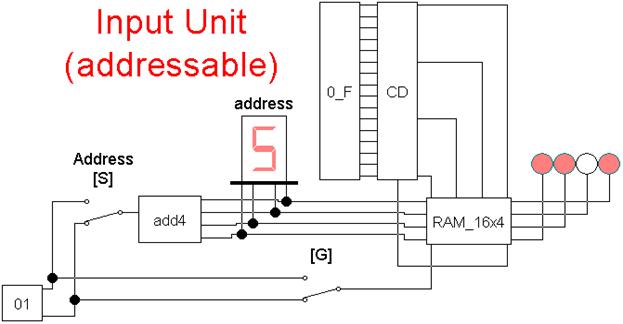

В первом задании рассматривается возможность реализации устройства ввода от шестнадцати клавиш на основе микросхем приоритетных шифраторов (см. рисунок 5.1). Сформированные коды сохраняются в ячейках памяти (подсхема RAM_16x4), исследованной в предыдущей работе. Для записи используется изменение уровня сигнала на выводе CS микросхем шифраторов. В этом устройстве адрес необходимой ячейки памяти подготавливается с помощью счетчика, как и в предыдущих работах.

Основными блоками схемы подсхемы 0_F и СD, представляющие собой набор клавиш и шифраторы соответственно. На сигнальной линии каждой клавиши в блоке 0_F установлены формирователи импульсов отрицательной полярности продолжительностью 10 ns (подсхемы, обозначенные символом l).

Основу блока CD составляет схема кодирования на двух приоритетных шифраторах 74148. Здесь же вырабатывается импульс записи длительностью 10 ns, формирующийся с задержкой 20 ns относительно начала формирования кода (момента нажатия клавиши). Параметры сформированных импульсов (относительный сдвиг сигнала записи) обеспечивают своевременное формирование кода нажатой клавиши и его запись в память.

Рисунок 5.1

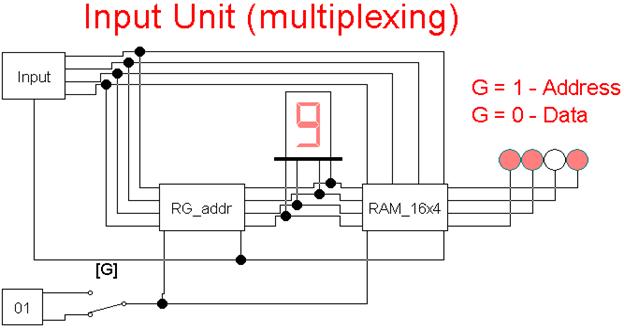

В следующей схеме (см. рисунок 5.2), рассматриваемой в данной работе, реализована возможность формирования как адреса, так и записываемой информации с помощью одних и тех же клавиш, т.е. осуществляется мультиплексирование передачи адреса и данных по одной и той же шине. Здесь блоки 0_F и СD объединены в подсхему Input.

Мультиплексирование осуществляется уровнем сигнала от клавиши G: при G=1 – передача адреса, который записывается в адресный регистр (подсхема RG_addr); при G=0 – передача записываемых в память данных.

Рисунок 5.2

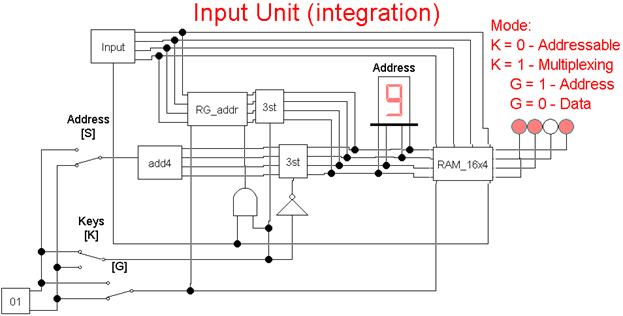

Еще более усовершенствованный вариант устройства рассматривается в следующей схеме (см. рисунок 5.3), где интегрированы оба рассмотренные ранее варианты. В этой схеме формирование адреса может быть реализовано в двух режимах: от счетчика (add4) и от блока кодирования (Inter). Переключение между этими источниками, т.е. их мультиплексирование осуществляется двумя блоками, построенными на основе элементов с тремя состояниями (подсхемы 3st), управляемых уровнем сигнала от клавиши K (при K=0 – add4 и при K=1 – Inter). В обоих случаях передача адреса осуществляется при G=1, а адреса – при G=0.

Рисунок 5.3

5.3 Рабочее задание

5.3.1 Изучить принципы построения устройства ввода на основе шифратора:

- открыть файл Input Unit (addressable).ewb, где представлена схема для исследования устройства ввода на основе шифратора (см. рисунок 5.1). Раскройте подсхемы, размещенные в схеме, и изучите их структуру;

- проверить работу устройства, устанавливая сначала адрес ячейки памяти клавишей S, а затем записывая в выбранную ячейку определенную информацию, нажимая соответствующую клавишу (0 … F).

5.3.2 Изучить принципы построения устройства ввода с мультиплексированием передачи информации:

- открыть файл Input Unit (multiplexing).ewb, где представлена схема для исследования устройства ввода с мультиплексированием передачи адреса и записываемой информации от одного источника (см. рисунок 5.2). Раскройте подсхемы, размещенные в схеме, и изучите их структуру;

- проверить работу устройства, устанавливая сначала адрес ячейки памяти (при G=1), а затем записывая в выбранную ячейку определенную информацию (при G=0), нажимая соответствующую клавишу (0 … F).

5.3.3 Изучить принципы построения устройства ввода с вариативными возможностями передачи информации:

- открыть файл 3.3.Input Unit (integration).ewb, где представлена схема, в которой объединены оба предыдущих устройства (см. рисунок 3.3). Раскройте подсхемы, размещенные в схеме, и изучите их структуру;

- проверить работу устройства в различных режимах.

5.4 Задания на СРС

5.4.1 Построить схему устройства ввода информации со сканируемой клавиатурой (на основе мультиплексоров).

5.5 Контрольные вопросы

1. Объясните работу схемы в блоке CD.

2. Объясните назначение подсхем 3st и работу их структурных элементов.

3. Объясните принципы работы устройств, исследованных в лабораторной работе.

6 Лабораторная работа. Модель MP4M

Цель работы:

- знакомство со структурой модели микропроцессорной системы;

- освоение порядка работы с моделью МПС;

- изучение действия различных команд;

- освоение принципов организации циклической программной структуры на модели МПС;

- освоение методики работы с массивом данных;

- изучение программы вычисления суммы нескольких чисел;

- освоение методики поиска единичного бита в определенном разряде данных.

6.1 Оборудование рабочего места и файлы:

- компьютер, программа Electronics Workbench Professional;

- файл MP4M.ewb.

6.2 Практические сведения и методические рекомендации

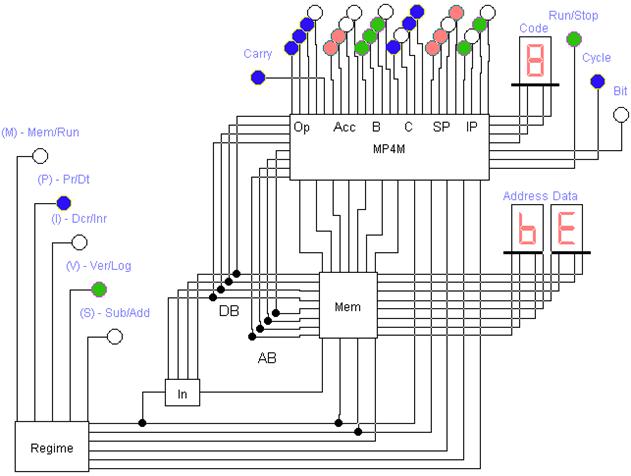

Модель 4-разрядной микропроцессорной системы, содержащая в своем составе микропроцессор (MP4M), устройство ввода данных (In), система памяти (Mem) и блок выбора режима работы системы, приведена на рисунке 6.1.

Рисунок 6.1

В состав микропроцессора входят следующие блоки:

- набор специализированных регистров (RGs, Registers);

- арифметико-логическое устройство (ALU, Arithmetic-Logic Unit);

- регистр команд (IR, Instruction Register);

- дешифратор команд (DC_16, Decoder 16-bit);

- таймер (CLK, Clock);

- микропрограммное устройство (Combi, Combinational Circuit.

Набор регистров (RGs) содержит в своем составе следующие регистры, каждый из которых предназначен для выполнения определенных функций:

- регистр A выполняет функцию аккумулятора (Accumulator), где хранится один из операндов, участвующих в выполнении арифметических и логических операций или результат выполнения операции. Загрузка аккумулятора осуществляется из памяти (команда LD A) или из ALU (после выполнения арифметической или логической операции);

- регистр A1 предназначен для накопления переносов при организации циклического суммирования. Он обнуляется при запуске программы и при загрузке аккумулятора (регистра A) командой LD A. Вывод его содержимого на индикаторы (аккумулятора) осуществляется кратковременным нажатием клавиши Space;

- регистр B выполняет функцию адресного регистра для команд пересылок между памятью и внутренними регистрами микропроцессора (команды LD C, LD IP, LD SP, LD A). После выполнения команд LD C, LD SP, LD A происходит приращение содержимого регистра B (т.е. увеличение на единицу). Загрузка этого регистра осуществляется командой LD B, в качестве адресного регистра для которого используется регистр C. Он обнуляется при запуске программы;

- регистр C выполняет функцию адресного регистра для второго операнда, участвующего в выполнении арифметических и логических операций. После выполнения соответствующих команд происходит приращение содержимого регистра C, но в отличие от регистра B знак приращения регистра C может быть изменен, он устанавливается клавишей I. Ее состояние показывает индикатор (I) - Dcr/Inr: при I=0 – положительное (Increment), а при I=1 – отрицательное (Decrement) приращение. Его содержимое может быть оставлено и в неизменном состоянии, о котором будет рассказано при описании режимов работы системы. Загрузка этого регистра осуществляется командой LD C. При запуске программы этот регистр устанавливается в состояние 1111 (с помощью элементов XOR). Ввиду того, что любая программа содержит в своем составе команды пересылок, первой команды программы должна быть загрузка регистра B (команда LD B) данным, содержащимся в ячейке памяти данных с адресом 1111. В состав регистра C включена схема, предназначенная для определения нулевого состояния регистра, по которому осуществляется условный переход при организации циклических операций;

- регистр SP выполняет функцию указателя стека (Stack Pointer), т.е. он выполняет функцию адресного регистра при выполнении команд PUSH и POP: перед выполнением команды PUSH происходит отрицательное приращение (Predecrement) его содержимого и после выполнения команды POP – положительное приращение (Postincrement). Загрузка этого регистра осуществляется командой LD SP. При запуске программы этот регистр устанавливается в состояние 1111;

- регистр IP выполняет функцию указателя команды (Instuction Pointer). После выборки кода текущей команды и сохранения его в регистре команды происходит приращение его содержимого. Загрузка этого регистра осуществляется командой LD IP. Его содержимое изменяется и при выполнении условий перехода, определяемых в некоторых альтернативных режимах работы системы. Он обнуляется при запуске программы.

Входы всех регистров соединены к внутренней шине данных, а выходы – к шине данных или к шине адреса (через буферные элементы с тремя состояниями) соответственно выполняемыми ими функциями.

Арифметико-логическое устройство (ALU, Arithmetic-Logic Unit) осуществляет выполнение арифметических и логических операций и содержит в своем составе различные подблоки (sum, not, and, or, xor), предназначенные для реализации соответствующих операций и буферные регистры для временного хранения операндов и результата выполненной операции.

Дешифратор команды (DC_16) в зависимости от кода команды включает соответствующую микропрограмму управления выполнением текущей команды, т.е. определяет линию выработки сигналов, управляющих работой устройств, участвующих в ее выполнении.

Таймер (CLK) определяет временное распределение сигналов управления, передаваемых к устройствам, участвующим в выполнении команд.

Микропрограммное устройство комбинационного типа (Combi, Combinational Circuit), формирует пространственные и временные сигналы управления, обеспечивающие выполнение текущей команды.

В качестве основы для устройства ввода и системы памяти используются рассмотренное ранее аналогичные устройства.

Блок управления памяти (MCon, Memory Control) обеспечивает выбор одного из блоков памяти (кодов или данных) и режим его работы (ввода, записи, считывания) в зависимости от управляющих сигналов, поступающих от устройства ввода или микропроцессора.

Система может работать в нескольких режимах, которые определяются в зависимости от состояний клавиш в блоке выбора режима ее работы (Regime). Состояние этих клавиш показывают соответствующие индикаторы. Опишем эти режимы.

Загрузка памяти от устройства ввода осуществляется при M=1. Если при этом P=1, то запись происходит в программную память (программа должна завершаться командой остановки с кодом F), а при P=0 – в память данных. Проверка содержимого памяти осуществляется изменением адреса ячейки памяти путем кратковременного нажатия клавиши Space. При переключении клавиши P происходит обнуление адреса памяти.

Запуск программы к работе осуществляется переключением клавиши M в состояние M=0. Если при этом P=1, то при выполнении арифметических и логических команд происходит изменение содержимого регистра C (соответственно значению I), а при P=0 его содержимое остается неизменным.

При S=0 по командам ADS и ACS выполняются операции сложения, а при S=1 – операции вычитания.

При V=0 по команде AND выполняется обычная операция логического умножения между двумя операндами, а при V=1 – реализуется битовая операция по поиску единичного бита в определенном разряде данных, для чего в аккумулятор должно быть загружено число, содержащее единицу только в искомом разряде. Описанная битовая операция имитирует поиск сигнала запроса от внешнего устройства или квитирования в реальных прикладных системах.

Перевод системы в один из описанных режимов осуществляется перед запуском программы к работе, но может быть осуществлен и в процессе работы программы, что расширяет программные возможности системы. Например, в процессе работы можно операции сложения изменять на вычитание и наоборот. Аналогично конъюнкцию можно изменять на битовую операцию.

Команды микропроцессора MP4M и их характеристики приведены в таблице 6.1, а порядок установки режимов работы системы – в таблице 6.2.

Т а б л и ц а 6.1 – Команды микропроцессора MP4M

|

Мн-ка |

Коды |

Операции |

|||

|

Hex |

V=0 |

P |

S |

V=1; I=1 |

|

|

LD B |

0 |

B←[(C)]; C←(C)+1 |

|

|

|

|

LD C |

1 |

C←[(B)]; B←(B)+1 |

|

|

|

|

LD IP |

2 |

IP←[(B)] |

|

|

|

|

LD SP |

3 |

SP←[(B)]; B←(B)+1 |

|

|

|

|

LD A |

4 |

A←[(B)]; B←(B)+1 |

|

|

|

|

ST |

5 |

[(B)]←(A);B←(B)+1 |

|

|

|

|

INR |

6 |

A←(A)+1 |

|

|

|

|

NOT |

7 |

A← |

|

|

|

|

ADS |

8 |

A←(A)±[(C)]; TC |

P=1: C←var(I) P=0: C = invar |

S=1: SUB (–) S=0:ADD,ADC (+) |

Zc = 0: IP←IP+1 |

|

ACS |

9 |

A←(A)±[(C)±TC; TC |

|

|

|

|

AND |

A |

A←(A)۸[(C)] |

|

|

Zc۸Za=0: IP←IP+1 |

|

OR |

B |

A←(A)۷[(C)] |

|

|

|

|

XOR |

C |

A←(A) |

|

|

|

|

PUSH |

D |

SP←(SP)–1; (SP)]←(A) |

|

|

|

|

POP |

E |

A←(SP)]; SP←(SP)+1 |

|

|

|

|

HLT |

F |

IP = invar |

|

|

|

Т а б л и ц а 6.2 – Установка режимов работы микропроцессора MP4M

|

Ключи и инд-ры |

M/R = 1 |

M/R → 0: Running: A,B,IP ← 0; C,SP ← F |

||

|

P=1: C←var(I); P=0: C = invar |

||||

|

S = 0 |

P/D = 1: MemPr←IN |

P/D = 0: MemD←IN |

Addition (+) |

A ← (A) + [(C)] |

|

S = 1 |

Subtraction (–) |

A ← (A) – [(C)] |

||

|

I = 1 |

PostDecrement C←(C) –1 |

C←(C)–1; (C)=0: Zc ← 0 |

||

|

I = 0 |

PostIncrement C←(C) +1 |

C ← (C) + 1 |

||

|

V = 0 |

Logical Operation |

A

← (A)

{۸ /

۷ / |

||

|

V = 1 |

Verifying of Byte |

(A)=0010…bi = 1: Za ← 0 |

||

6.3 Рабочее задание

6.3.1 Изучить действия команд пересылок:

- открыть программу EWB5PRO и выбрать файл MP4M.ewb. Раскрывая подсхемы основных блоков системы (см. рисунок 6.1) и их внутренних компонентов и изучая практические сведения о системе, приведенные выше, ознакомиться с их структурой и принципами функционирования;

-

активизировать программу EWB5PRO кнопкой ![]() и в дальнейшем ее не выключать до конца работы

во избежание потери записанной в память информации;

и в дальнейшем ее не выключать до конца работы

во избежание потери записанной в память информации;

- подготовить систему к режиму загрузки программы установкой клавиш M и P в состояние M=1 и P=1. Загрузить в память коды команд представленной ниже программы;

|

Адрес |

Команды |

Коды |

Адрес |

Команды |

Коды |

|

0 |

LD B |

0 |

5 |

POP |

E |

|

1 |

LD A |

4 |

6 |

ST |

5 |

|

2 |

LD SP |

3 |

7 |

PUSH |

D |

|

3 |

LD C |

1 |

8 |

PUSH |

D |

|

4 |

POP |

E |

9 |

HLT |

F |

- перевести систему в режим загрузки данных установкой клавиши P в состояние P=0. Загрузить в память данные (например, последовательные значения чисел, начиная с какого-то конкретного значения) и записать их в рабочую тетрадь;

- проверить правильность введенной в память информации (программы и данных), выбрав необходимый тип памяти клавишей P и кратковременно нажимая клавишу Space;

-

запустить работу загруженной программы, установив клавишу P в состояние P=1 и переключив

клавишу M в состояние M=0. Наблюдая за состояниями индикаторов, проверить работу программы.

При необходимости работу программы можно приостановить кнопкой ![]() или перезапустить программу двойным

нажатием клавиши M (не очень быстро);

или перезапустить программу двойным

нажатием клавиши M (не очень быстро);

- после завершения работы программы перевести систему в режим ввода и проверить содержимое ячеек памяти данных. Выяснить причину происшедших изменений;

- восстановив введенные ранее данные и изменив содержимое ячейки с адресом F, запустить работу программы и проверить ее работу.

6.3.2 Изучить действия арифметических и логических команд:

- подготовить систему к режиму загрузки программы (M=1, P=1) и загрузить в память коды команд представленной ниже программы;

|

Адрес |

Команды |

Коды |

Адрес |

Команды |

Коды |

|

0 |

LD B |

0 |

7 |

ADS |

8 |

|

1 |

LD C |

1 |

8 |

ACS |

9 |

|

2 |

LD A |

4 |

9 |

ACS |

9 |

|

3 |

INR |

6 |

A |

AND |

A |

|

4 |

INR |

6 |

B |

OR |

B |

|

5 |

ADS |

8 |

C |

XOR |

C |

|

6 |

ADS |

8 |

D |

HLT |

F |

- перевести систему в режим загрузки данных (M=1, P=0). Загрузить в память данные (например, последовательные значения чисел, начиная с какого-то конкретного значения) и записать их в рабочую тетрадь;

-

запустить работу загруженной программы (P=1,

затем M=0). Наблюдая за состояниями индикаторов,

проверить работу программы. При необходимости можно воспользоваться кнопкой

приостановки ![]() ;

;

- после завершения работы программы проверить содержимое регистра A1 кратковременным нажатием клавиши Space (эту можно делать и процессе работы программы). Объясните полученный результат. При возникновении затруднения в этом, перезапустить программу (двойным нажатием клавиши M) и более внимательно наблюдать за возникающими переносами в операциях сложения;

- перевести систему в режим загрузки программы, изменить состояние клавиши S в S=1, в результате чего программа суммирования перейдет в программу вычитания, т.е. при выполнении команд ADC и ACS выполняются операции вычитания (соответственно – без переноса и с переносом);

- запустить работу загруженной программы. Наблюдая за состояниями индикаторов, проверить работу программы. При необходимости перезапустить работу программы;

- учитывая, что арифметические операции выполнятся в дополнительном коде, выполните вручную в двоичном коде все осуществляемые в программе операции вычитания и сравните их поэтапно с результатами, получаемыми в системе.

6.3.3 Изучить принципы организации циклических программных структур на модели МПС:

- подготовить систему к режиму загрузки и загрузить в память коды команд представленной ниже программы и данные для программы для определения суммы N чисел (в данном случае N=5);

|

Адрес |

Команды |

Коды |

Адрес |

Данные |

Адрес |

Данные |

|

0 |

LD B |

0 |

0 |

6 |

… |

… |

|

1 |

LD C |

1 |

1 |

8 |

7 |

5 |

|

2 |

ADS |

8 |

2 |

D |

8 |

2 |

|

3 |

LD IP |

2 |

3 |

A |

… |

… |

|

4 |

HLT |

|

4 |

9 |

|

|

|

|

|

|

5 |

B |

F |

7 |

- запустить работу загруженной программы при P=1, S=0, I=1. После завершения работы программы младшая тетрада результата суммирования окажется в аккумуляторе (регистре A), а старшую тетраду, которая находится в регистре A1, можно выяснить кратковременным нажатием клавиши Space;

- определите вручную сумму чисел, размещенных в ячейках с адресами 1…5, и сравнить ее с результатом, полученным в системе;

- перевести систему в режим загрузки, загрузить в память коды команд представленной ниже программы обнаружения единичного бита в третьем разряде среди данных, размещенных в ячейках с адресами 1…5 (в данном конкретном случае – число D, размещенное в ячейке с адресом 2);

|

Адрес |

Команды |

Коды |

Адрес |

Данные |

Адрес |

Данные |

|

0 |

LD B |

0 |

0 |

6 |

… |

… |

|

1 |

LD C |

1 |

1 |

8 |

7 |

6 |

|

2 |

LD A |

4 |

2 |

D |

8 |

4 |

|

3 |

AND |

A |

3 |

A |

9 |

3 |

|

4 |

LD IP |

2 |

4 |

9 |

… |

… |

|

5 |

HLT |

F |

5 |

B |

F |

7 |

- запустить работу загруженной программы. Наблюдая за состояниями индикаторов, проверить работу программы. При обнаружении искомого числа высвечивается индикатор Bit и программа завершит свою работу

- перевести систему в режим загрузки изменить значение D, размещенное в ячейке с адресом 2, на 3 и перезапустить работу программы. В данном случае программа проверит данные в ячейках с адресами 1…5 и, не обнаружив среди них искомое число, завершит свою работу.

6.4 Задания на СРС

6.4.1 Составить программу вычисления по выражению y=(a1+a2-a3)٨4, где ٨ – символ операции нахождения единичного бита в определенном разряде данных (в данном случае – в третьем разряде) и проверить работу при различных значениях данных (a1, a2, a3).

6.5 Контрольные вопросы

1. Объясните структуру модели микропроцессорной системы и ее функциональных блоков.

2. Объясните внутреннюю структуру микропроцессора и функции ее составляющих компонентов.

3. Объясните действия команд пересылок, использованных в исследованной программе.

4. Объяснить действия арифметических и логических команд, использованных в программе. Объяснить порядок выполнения соответствующих операций на примерах.

5. Объясните принципы организации циклической программной структуры на учебной модели.

6. Объясните принципы организации работы с массивом данных.

7. Объясните структуру программы вычисления суммы чисел.

8. Объясните структуру программы обнаружения единицы в определенном разряде среди массива данных.

7 Лабораторная работа. МПС на основе микропроцессора Intel 8085

Цель работы:

- знакомство со структурой микропроцессорной системы (МПС) на основе микропроцессора Intel 8085;

- освоение порядка работы с симулятором 8085 Simulator IDE;

- изучение действий, выполняемых командами пересылки данных из состава команд микропроцессора Intel 8085, различающихся способами адресации;

- изучение действий, выполняемых арифметическими командами, различающихся способами адресации;

- изучение функциональных возможностей программного симулятора МПС на основе микропроцессора Intel 8085;

- освоение порядка работы с лабораторным стендом, предназначенным для изучения программирования на языке Ассемблер.

7.1 Оборудование рабочего места и файлы:

- компьютер, программа 8085 Simulator IDE;

- лабораторный стенд PU-2000 фирмы Degem Systems;

- съемные платы EB-151 и EB-152;

- соединительные провода и перемычки.

7.2 Практические сведения и методические рекомендации

Для выполнения виртуальной части работы на компьютере должна быть установлена программа 8085 Simulator IDE. Перед началом работы с симулятором в C:\Program Files\8085 Simulator IDE рекомендуется создать папку под именем, содержащим достаточную информацию о студенте (номер группы, фамилию и имя) и в дальнейшем сохранять все создаваемые файлы в нем. Это облегчит вам работу с этими файлами в дальнейшем.

Структура симулятора и использование его функциональных возможностей будут описаны постепенно в процессе выполнения лабораторных работ. Здесь же приведем краткое описание порядка организации работы на лабораторном стенде.

Подготовка рабочего места, т.е. системы на лабораторном стенде, осуществляется следующим образом:

- установить плату EB-151 на лабораторный стенд, а плату EB-152 слева от него. Обеспечить совместимость плат EB-151 и EB-152 по питанию (+12 V, –12 V, +5 V, GND) и возможность передачи данных между платами (RX↔TX):

- установить переключатель S1 (SIG.ANAL/KB+DISP) на плате EB-152 в положение KB+DISP (или убедится в этом). Включить источник питания стенда и удостовериться в том, что дисплей EB-152 показывает “EBHt”;

- перезапустить микрокомпьютер на плате EB-151 кратковременным нажатием кнопки “Reset” на этой плате. При правильном выполнении необходимых соединений дисплей на плате EB-152 должен показывать “Eb-151”, в противном случае необходимо проверить правильность соединений.

Для записи учебной программы (т.е. программы пользователя) в ОЗУ нажать клавишу MEM и ввести адрес первой ячейки памяти в адресное поле дисплея. Ввести необходимое значение кода в поле данных дисплея и нажать клавишу ENTER, при этом адрес ячейки памяти увеличится на единицу автоматически и можно будет ввести следующие данные (код операции или значение операнда) и т.д.

Код любой команды микропроцессора Intel 8085 можно легко определить по таблице 7.1.

Т а б л и ц а 7.1

|

|

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

A |

B |

C |

D |

E |

F |

|

|

0 |

NOP |

LXI B |

STAX B |

INX B |

INR B |

DCR B |

MVI B |

RLC |

|

DAD B |

LDAX B |

DCX B |

INR C |

DCR C |

MVI C |

RRC |

0 |

|

1 |

|

LXI D |

STAX D |

INX D |

INR D |

DCR D |

MVI D |

RAL |

|

DAD D |

LDAX D |

DCX D |

INR E |

DCR E |

MVI E |

RAR |

1 |

|

2 |

RIM |

LXI H |

SHLD |

INX H |

INR H |

DCR H |

MVI H |

DAA |

|

DAD H |

LHLD |

DCX H |

INR L |

DCR L |

MVI L |

CMA |

2 |

|

3 |

SIM |

LXI SP |

STA |

INX SP |

INR M |

DCR M |

MVI M |

STC |

|

DAD SP |

LDA |

DCX SP |

INR A |

DCR A |

MVI A |

CMC |

3 |

|

4 |

MOV B,B |

MOV B,C |

MOV B,D |

MOV B,E |

MOV B,H |

MOV B,L |

MOV B,M |

MOV B,A |

MOV C,B |

MOV C,C |

MOV C,D |

MOV C,E |

MOV C,H |

MOV C,L |

MOV C,M |

MOV C,A |

4 |

|

5 |

MOV D,B |

MOV D,C |

MOV D,D |

MOV D,E |

MOV D,H |

MOV D,L |

MOV D,M |

MOV D,A |

MOV E,B |

MOV E,C |

MOV E,D |

MOV E,E |

MOV E,H |

MOV E,L |

MOV E,M |

MOV E,A |

5 |

|

6 |

MOV H,B |

MOV H,C |

MOV H,D |

MOV H,E |

MOV H,H |

MOV H,L |

MOV H,M |

MOV H,A |

MOV L,B |

MOV L,C |

MOV L,D |

MOV L,E |

MOV L,H |

MOV L,L |

MOV L,M |

MOV L,A |

6 |

|

7 |

MOV M,B |

MOV M,C |

MOV M,D |

MOV M,E |

MOV M,H |

MOV M,L |

HLT |

MOV M,A |

MOV A,B |

MOV A,C |

MOV A,D |

MOV A,E |

MOV A,H |

MOV A,L |

MOV A,M |

MOV A,A |

7 |

|

8 |

ADD B |

ADD C |

ADD D |

ADD E |

ADD H |

ADD L |

ADD M |

ADD A |

ADC B |

ADC C |

ADC D |

ADC E |

ADC H |

ADC L |

ADC M |

ADC A |

8 |

|

9 |

SUB B |

SUB C |

SUB D |

SUB E |

SUB H |

SUB L |

SUB M |

SUB A |

SBB B |

SBB C |

SBB D |

SBB E |

SBB H |

SBB L |

SBB M |

SBB A |

9 |

|

A |

ANA B |

ANA C |

ANA D |

ANA E |

ANA H |

ANA L |

ANA M |

ANA A |

XRA B |

XRA C |

XRA D |

XRA E |

XRA H |

XRA L |

XRA M |

XRA A |

A |

|

B |

ORA B |

ORA C |

ORA D |

ORA E |

ORA H |

ORA L |

ORA M |

ORA A |

CMP B |

CMP C |

CMP D |

CMP E |

CMP H |

CMP L |

CMP M |

CMP A |

B |

|

C |

RNZ |

POP B |

JNZ |

JMP |

CNZ |

PUSH B |

ADI |

RST 0 |

RZ |

RET |

JZ |

|

CZ |

CALL |

ACI |

RST 1 |

C |

|

D |

RNC |

POP D |

JNC |

OUT |

CNC |

PUSH D |

SUI |

RST 2 |

RC |

|

JC |

IN |

CC |

|

SBI |

RST 3 |

D |

|

E |

RPO |

POP H |

JPO |

XTHL |

CPO |

PUSH H |

ANI |

RST 4 |

RPE |

PCHL |

JPE |

XCHG |

CPE |

|

XRI |

RST 5 |

E |

|

F |

RP |

POP PSW |

JP |

DI |

CP |

PUSH PSW |

ORI |

RST 6 |

RM |

SPHL |

JM |

EI |

CM |

|

CPI |

RST 7 |

F |

|

|

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

A |

B |

C |

D |

E |

F |

|

Проверка содержимого ячеек памяти осуществляется аналогично, т.е. нажатием клавиши MEM и вводом в адресное поле дисплея адреса первой проверяемой ячейки памяти. В дальнейшем, нажимая клавишу ENTER, можно последовательно изменять адреса ячеек и считывать их содержимое. При необходимости, разумеется, их можно изменить.

Для проверки содержимого регистров микропроцессора нажать клавишу REG и ввести номер регистра в адресное поле дисплея, после чего в поле данных дисплея отобразится содержимое указанного регистра. Аналогично можно просмотреть содержимое и других регистров. Номера проверяемых регистров можно изменять последовательно (см. таблицу 7.2) просто нажатием клавиши ENTER.

Т а б л и ц а 7.2

|

Номера регистров |

Регистры |

Описание регистра |

|

1 |

A |

Аккумулятор |

|

2 |

B |

Регистр B |

|

3 |

C |

Регистр C |

|

4 |

D |

Регистр D |

|

5 |

E |

Регистр E |

|

6 |

H |

Регистр H |

|

7 |

L |

Регистр L |

|

8 |

F |

Регистр флагов |

|

9 |

I |

Маска прерывания |

|

A |

PC |

Программный счетчик |

|

B |

SP |

Указатель стека |

|

C |

HL |

Указатель памяти |

|

D |

AF |

Слово состояния процессора |

|

E |

BC |

Регистровая пара BC |

|

F |

DE |

Регистровая пара DE |

Запуск программы к работе осуществляется нажатием клавиши GO и вводом начального адреса программы, затем клавиши ENTER.

7.3 Рабочее задание

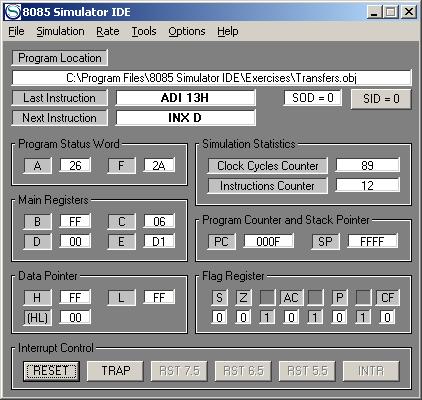

7.3.1 Освоить порядок загрузки программы в симулятор 8085 Simulator IDE и изучить действия, выполняемые командами пересылки данных:

-

запустить программу симулятора иконой ![]() . В открывшемся основном окне симулятора (см.

рисунок 7.1) выбрать Tools/Assembler

и в окне Assembler – File/New;

. В открывшемся основном окне симулятора (см.

рисунок 7.1) выбрать Tools/Assembler

и в окне Assembler – File/New;

- сдвинув курсор на табулированное расстояние (клавишей Tab), ввести первую команду представленной ниже программы и нажать Enter. Аналогично продолжить ввод остальных команд программы. Метки записываются в начале строки. В этой программе, составленной в виде нескольких блоков, осуществляются пересылки данных между процессором и памятью. В первом блоке (Single Writing-1) осуществляется одиночная пересылка в память командой с прямой адресацией. Во втором блоке (Serial Writing) реализуется передача массива данных (в виде членов арифметической прогрессии) в память командой с косвенной адресацией. Более практичный способ передачи массива данных представлен в следующем блоке (Single Writing-2). В следующих трех блоках (Data Access, Data Access and Conversion, Single Writing) осуществляются пересылки данных из одного участка памяти в другой с использованием аналогичных использованным ранее командам (только в обратном порядке). Сохранить (File/Save As) записанную программу под именем Transfers (Пересылки), в результате чего создается файл с расширением asm;

Рисунок 7.1

;WRITING to MEMORIES

SW: ;Single Writing

MVI A,0FH;Direct Loading

STA 00D0H;Direct Writing

NOP

S1: ;Serial Writing-1

MVI C,07h;Data Counter

LXI D,00D0H;Initial Address

MVI A,00H;Cleaning

T0: ADI 13H;Expansion Step

INX D;Address Increment

STAX D;Indirect Writing

DCR C;Monitoring of the Data Counter

JNZ T0;Continue

XCHG;Exchange

NOP

S2: ;Serial Writing-2

MVI C,08H;Data Counter

T1: ADI 09H;Expansion Step

INX H;Address Increment

MOV M,A;Indirect Writing

DCR C;Monitoring of the Data Counter

JNZ T1;Continue

NOP

AW: ;Data Access and Writing

LXI D,00EFH;Initial Address

MVI C,08H;Data Counter

T2: MOV A,M;Indirect Loading

STAX D;Indirect Writing

DCX H;Address Decrement

DCX D;Address Decrement

DCR C;Monitoring of the Data Counter

JNZ T2;Continue

NOP

AC: ;Data Access, Conversion and Writing

MVI C,07H;Data Counter

T3: MOV A,M;Indirect Loading

RLC;Left Shift

XCHG;Exchange

MOV M,A;Indirect Writing

DCX H;Address Decrement

DCX D;Address Decrement

XCHG;Exchange

DCR C;Monitoring of the Data Counter

JNZ T3;Continue

NOP

SA: ;Single Access and Writing

LDA 00D0H;Direct Loading

STA 00E0H;Direct Writing

HLT;Ending

- в окне Assembler выбрать Tools/Assemble&Load. Создаются файлы с расширениями hex, lst, obj;

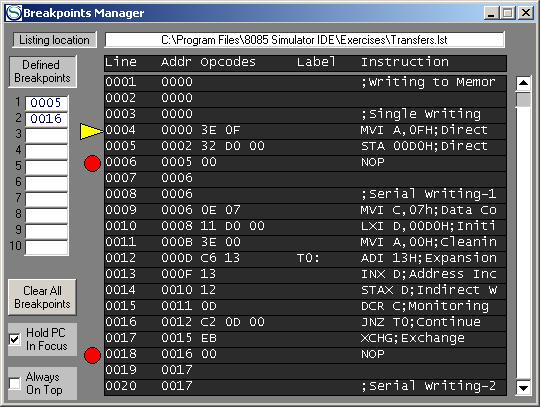

- в основном окне симулятора выбрать Tools/Breakpoints Manager и установить контрольные точки после каждого блока, т.е. в строках с командой NOP (см. рисунок 7.2);

Рисунок 7.2

- в основном окне симулятора выбрать скорость моделирования (Rate/…), например, Rate/Normal и запустить работу симулятора (Simulation/Start);

- после каждой остановки программы в контрольных точках проанализировать действия команд в выполненном блоке и полученные результаты (в регистрах микропроцессора и в соответствующих ячейках памяти);

- продолжить работу симулятора, выбрав скорость моделирования (Rate/…).

При необходимости (или по указанию преподавателя) можно осуществить раздельное выполнение отдельных блоков программы. Для этого в первую строку программы ввести команду JMP с меткой блока и заменить команду NOP в конце блока на команду HLT.

7.3.2 Изучить действия, выполняемые арифметическими командами, различающихся способами адресации:

- ввести представленную ниже программу, состоящую из следующих блоков: Data Array – осуществляет запись данных в память в виде членов арифметической прогрессии (заданные параметры n = 0AH – количество членов, a1 = 00H – первый член, d = 55H – шаг прогрессии можно изменить в процессе выполнения работы); Cumulative Summation – определяет сумму членов арифметической прогрессии, записанных в память в предыдущем блоке программы; Retention of Result – сохраняет в памяти полученный результат суммирования; Series Subtraction – осуществляет последовательное вычитание членов арифметической прогрессии из полученной ранее суммы; ALTERNATIVE of the Single-Byte Summation, состоящий из двух подблоков (Data и Cumulative Summation-A) – реализует другой способ определения суммы членов арифметической прогрессии с использованием периферийных устройств (IN, OUT). Сохранить записанную программу под именем Single-Byte Arithmetic (Однобайтная арифметика);

;SINGLE-BYTE ARITHMETIC

DA: ;Data Array (arithmetical progression)

LXI H,00E0H;Initial Address

MVI C,0AH;Data Quantity

MVI A,00H;Cleaning

MOV M,C;Writing in the Memory

SD: INX H;Address Increment

ADI 55H;Increment Step of the Linear Series

MOV M,A;Writing in the Memory

DCR C;Monitoring of the Data Counter

JNZ SD;Continue

NOP

CS: ;Cumulative Summation

;SUM=((2a1+(n-1)d)/2)n

;a1-first operand,n-quantity,d-step,

LXI H,00E0H;Initial Address

MVI A,00H;Cleaning

MOV B,A;Cleaning

MOV C,M;Installation of the Data Counter

C1: INX H;Address Increment

ADD M;Addition

JNC C2;Carry Monitoring

INR B;Carry Accumulation

C2: DCR C;Monitoring of the Data Counter

JNZ C1;Continue

NOP

RR: ;Retention of Result

INX H;

MOV M,A;Low Byte

INX H;

MOV M,B;High Byte

NOP

SS: ;Series Subtraction

LXI H,00E0H;Initial Address

MOV C,M;Installation of the Data Counter

S1: INX H;Address Increment

SUB M;Subtraction

JNC S2;Borrow Monitoring

DCR B;Borrow Subtraction

S2: DCR C;Monitoring of the Data Counter

JNZ S1;Continue

NOP

AD: ;ALTERNATIVE of the Single-Byte Summation

;Data

IN 01H;First Operand

MOV E,A

IN 01H;Data Quantity

MOV C,A

IN 02H;Step

MOV D,A

LXI H,0000H

NOP

AC ;Cumulative Summation-A

A1: MOV A,E

ADD D

MOV E,A

MOV A,L

ADD E

JNC A2

INR H

A2: MOV L,A

DCR C

JNZ A1

MOV A,L

OUT 03H

MOV A,H

OUT 04H

HLT;Ending

- в окне Assembler выбрать Tools/Assemble&Load, а затем в основном окне симулятора выбрать Tools/Breakpoints Manager и установить контрольные точки после каждого блока, т.е. в строках с командой NOP;

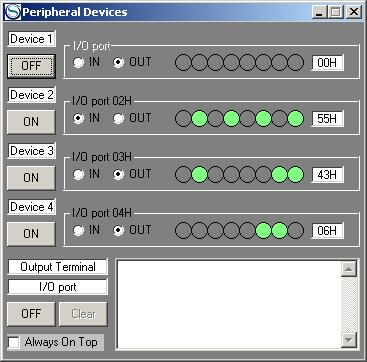

- в окне симулятора открыть окно Tools/Peripheral Devices. В открывшемся окне Peripheral Devices нажать кнопку Device 1 и определить адрес порта как 01, а затем установить этот порт на IN. Аналогично определить адрес следующего порта как 02, и установить его также на IN. Определив адреса следующих портов как 03 и 04, установить их на OUT (см. рисунок 7.3);

- в основном окне симулятора выбрать скорость моделирования (Rate/…) и запустить работу симулятора (Simulation/Start). После каждой остановки программы в контрольных точках проанализировать действия команд в выполненном блоке и полученные результаты (в регистрах микропроцессора и в соответствующих ячейках памяти);

Рисунок 7.3

- продолжить работу симулятора, выбрав скорость моделирования (Rate/…);

-

проверить соответствие полученных

результатов суммирования с вычисленным по формуле ![]() .

.

При необходимости (или по указанию преподавателя) выполнить отдельные блоки программы раздельно. Для этого в первую строку программы ввести команду JMP с меткой блока и заменить команду NOP в конце блока на команду HLT.

7.3.3 Проверить работу программы на реальной установке:

- подготовить микрокомпьютер (лабораторный стенд) к работе (см. 7.2). Ввести в ячейки памяти микрокомпьютера коды команд отдельных блоков (предложенных преподавателем) представленной выше программы.

- запустить введенную программу на выполнение нажатием клавиши GO и вводом начального адреса блока и проанализировать работу программы на микрокомпьютере, сопоставляя данные, полученные на нем с данными на симуляторе.

7.4 Задания на СРС

7.4.1 Составить программу вычисления суммы n двухбайтных чисел (например, пяти), с вводом данных с периферийного устройства.

7.4.2 Составить программу выполнения логических операций с различными способами адресации.

7.5 Контрольные вопросы

1. Объясните внутреннюю структуру микропроцессора и функции ее составляющих.

2. Объясните структуры отдельных блоков программ и действия команд в них.

3. Объясните действия команд пересылок, использованных в исследованной программе.

4. Объясните действия арифметических команд, использованных в программе.

5. Какими командами осуществляются сложение двухбайтных чисел?

6. Объясните различия действий арифметических команд с переносом и без переноса.

8 Лабораторная работа. Организация работы с подпрограммами

Цель работы:

- освоение принципов организации работы с подпрограммами;

- освоение принципов организации пересылок данных между стеком и регистрами микропроцессора.

8.1 Оборудование рабочего места и файлы:

- компьютер, программа 8085 Simulator IDE;

- лабораторный стенд PU-2000 фирмы Degem Systems;

- съемные платы EB-151 и EB-152;

- соединительные провода и перемычки.

8.2 Практические сведения и методические рекомендации

С целью рассмотрения структуры и порядка организации

работы с подпрограммами и со стеком в работе рассматривается программа вычисления

по выражению y = a1*a2 + a3*a4 + ![]() . Для решения

поставленной задачи необходимо предварительно составить подпрограммы умножения

и кумулятивного суммирования.

. Для решения

поставленной задачи необходимо предварительно составить подпрограммы умножения

и кумулятивного суммирования.

В микропроцессоре Intel 8085 отсутствует команда умножения, поэтому для операции умножения приходится составлять соответствующую программу. Определим алгоритм умножения. С целью наглядного объяснения машинного алгоритма, ниже приведены три варианта реализации процесса умножения десятичных чисел по известному со школьной скамьи алгоритму:

|

|

|

|

В первом варианте приведен привычный для нас порядок умножения, начиная с младшего разряда множителя и со сдвигом частичных произведений налево. Во втором варианте приведен порядок умножения, начиная со старшего разряда множителя и со сдвигом частичных произведений направо. В третьем варианте учтено, что возможное число разрядов результата умножения двух чисел с одинаковым числом разрядов (в нашем примере – четыре) в два раза больше, чем у множителей. Поэтому в начале операции значение произведения принято восьмиразрядным нулем. Для того чтобы частичные сложения осуществлялись над числами с одинаковым числом разрядов, первый множитель расширен до восьми разрядов (добавлением нулей слева) и операции сдвига (они указаны стрелками) осуществляются перед началом каждого частичного умножения. Именно такой алгоритм был принят для программной реализации умножения двухбайтных двоичных чисел:

- ввиду того, что результат умножения восьмиразрядных чисел будет шестнадцатиразрядным числом и в связи с тем, что частичные сложения выполняются также над шестнадцатиразрядными числами, в качестве шестнадцатиразрядного аккумулятора была принята регистровая пара HL, которая очищается в начале выполнения программы;

- в регистр E регистровой пары DE вводится первое число (множимое), а регистр D обнуляется, в результате чего множимое становится шестнадцатиразрядным числом;

- с целью обеспечения возможности сдвига, второе число (множитель) помещается в аккумуляторе (во избежания путаницы его в дальнейшем будем называть регистром A);

- для обеспечения контроля над числом операций сдвига число разрядов множителя (восемь) помещается в регистр С;

- перед осуществлением каждого частичного умножения накопившийся до этого результат (в регистровой паре HL) сдвигается влево (путем удваивания);

- очередное значение разряда множителя определяется путем сдвига содержимого регистра A (множителя) влево и в случае равенства его нулю –частичное умножение этим и завершается (т.е. предыдущим сдвигом регистровой пары HL), а при равенстве его единице – к содержимому регистровой пары HL добавляется содержимое регистровой пары DE.

После каждого частичного умножения содержимое счетчика сдвига убавляется на единицу и при равенстве его нулю – программа умножения завершает свою работу.

8.3 Рабочее задание

8.3.1 Изучить структуру сложной программы, содержащей в своем составе несколько подпрограмм:

- запустить программу симулятора и в открывшемся окне выбрать Tools/Assembler, а затем – File/New;

- ввести представленную ниже программу и сохранить ее под именем Stack (Стек);

;SUM=a1*a2+a3*a4+sum(ai,n,d)

LXI SP,0FFH

MVI B,0A0H

;mul1=a1*a2

IN 01H;first multiplier

MOV E,A

IN 02H;second multiplier

CALL MUL

PUSH H

CALL PER

NOP

;mul2=a3*a4

IN 01H;first multiplier

MOV E,A

IN 02H;second multiplier

CALL MUL

PUSH H

CALL PER

NOP

;sum(ai,n,d)

IN 01H;quantity - n

MOV C,A

IN 02H;step - d

MOV D,A

IN 01h;first operand - a1

MOV D,A

LXI H,0000H

CALL SUM

CALL PER

NOP

;S3

POP D

DAD D

POP D

DAD D

CALL PER

HLT

MUL: ;Multiplication (subroutine)

MVI D,00H

LXI H,0000H

MVI C,08H

M1: DAD H

RLC

JNC M2

DAD D

M2: DCR C

JNZ M1

RET

SUM: ;Cumulative Summation (subroutine)

CS3: MOV A,E

ADD D

MOV E,A

MOV A,L

ADD E

JNC CS4

INR H

CS4: MOV L,A

DCR C

JNZ CS3

RET

PER: ;Displaying on the Periphery

;and Writing on the Memory

MOV C,B

MVI B,00H

MOV A,L

OUT 03H

STAX B

INR C

MOV A,H

OUT 04H

STAX B

INR C

MOV B,C

RET

Основная часть программы состоит из следующих блоков: SUM – заголовок основной программы, где присваивается значение указателю стека SP и информация, предназначенная для организации работы подпрограммы вывода и отображения результатов. mul1 и mul2 – осуществляется ввод данных для умножения и вызывается подпрограмма умножения, а затем – подпрограмма отображения. sum – осуществляется ввод данных для суммирования и вызывается подпрограмма суммирования, а затем – подпрограмма отображения. S3 – вычисляет конечный результат, т.е. суммирует частичные результаты, полученные в предыдущих этапах.

В программе используются три подпрограммы: Multiplication – осуществляет умножение двух чисел, введенных перед вызовом подпрограммы; Cumulative Summation – определяет сумму задаваемых в основной программе n чисел; Displaying – осуществляет отображение полученных в подпрограммах результатов и сохраняет их в памяти.

- в окне Assembler выбрать Tools/Assemble&Load, а затем открыть окно Tools/Peripheral Devices. В открывшемся окне Peripheral Devices определить адреса портов между 01…04 и первые два порта (с адресами 01 и 02) установить на IN, а остальные на OUT;

- в основном окне симулятора выбрать Tools/Breakpoints Manager и установить контрольные точки после каждого блока основной части программы, т.е. в строках с командой NOP;

- в основном окне симулятора выбрать скорость моделирования (Rate/…) и запустить работу симулятора (Simulation/Start). После каждой остановки программы в контрольных точках проанализировать действия команд в выполненном блоке и полученные результаты (в регистрах микропроцессора и в соответствующих ячейках памяти);

- продолжить работу симулятора, выбрав скорость моделирования (Rate/…).

8.3.2 Проверить работу программы на реальной установке: