АЛМАТИНСКИЙ ИНСТИТУТ ЭНЕРГЕТИКИ И СВЯЗИ

Кафедра электроники и компьютерных технологий

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ

Методические указания к выполнению курсовой работы

для студентов всех форм обучения специальностей

050704 – Вычислительная техника и программное обеспечение,

050719 – Радиотехника, электроника и телекоммуникации

Алматы 2008

СОСТАВИТЕЛЬ: У.Т.Шанаев. Цифровые устройства и микропроцессоры. Методические указания к выполнению курсовой работы для студентов всех форм обучения специальностей 050704 – Вычислительная техника и программное обеспечение, 050719 – Радиотехника, электроника и телекоммуникации. – Алматы: 2008. – 21 с.

В методической разработке приводятся задания на курсовую работу по курсу «Цифровые устройства и микропроцессоры» и представлены методические указания к ее выполнению. Тематика этих заданий и предлагаемый порядок их выполнения в виде организации виртуальных исследований в программной среде Electronics Workbench направлены на повышение уровня теоретических знаний по изучаемой дисциплине и формированию практических навыков по проектированию и тестированию цифровых устройств. Они составлены в соответствии с требованиями квалификационной характеристики специалиста, Государственных стандартов, педагогико-психологических основ организации и проведения учебных занятий.

Методические указания к выполнению курсовой работы предназначены для студентов всех форм обучения специальностей 050704, 050719. Они могут быть использованы и при выполнении курсовой работы по идентичным темам аналогичных дисциплин, запланированных для других специальностей.

Введение

В курсовой работе по техническим дисциплинам ставится задача разработки схемы (т.е. проектирование) некоторого устройства, предназначенного для выполнения определенных функций. Сущность процесса проектирования кратко, но достаточно емко, определяется следующим образом. Проектирование – разработка технической документации, позволяющей изготовить заданное устройство в заданных условиях. В состав технической документации входят схемы спроектированного устройства в целом и его отдельных функциональных частей, а также соответствующие пояснения к этим схемам.

Характер проектирования существенно зависит от вида применяемой элементной базы. Данная курсовая работа выполняется на основе интегральных микросхем малой и средней степени интеграции (МИС, СИС). Проектирование на основе МИС, СИС – наиболее традиционный процесс, в котором используются как эвристические подходы, так и формализованные методики. Проектировщик (т.е. студент) задает структуру устройства на базе своих знаний, идей и освоения опыта предшественников (в нашем случае, по методическим указаниям, изложенным в иллюстративном примере), а при определении функций отдельных блоков пользуется и формальными методами. При этом требуется знание типовых функциональных узлов, их свойств и параметров.

При выполнении любой творческой работы, в том числе и при проектировании, необходимо придерживаться определенной стратегии. При проектировании цифровых устройств, содержащих множество отдельных функциональных компонентов, удобно придерживаться стратегии функциональной декомпозиции. При этом для системы в целом и ее блоков используется концепция “черного ящика”. Для “черного ящика” разрабатывается функциональная спецификация, включающая внешнее описание блока (входы и выходы) и внутреннее описание – функцию или алгоритм работы F = Ф (X, t), где X – вектор входных величин, F – вектор выходных величин, t – время. При декомпозиции функция Ф разбивается на более простые функции Ф1...Фк, между которыми должны быть установлены определенные связи, соответствующие принятому алгоритму реализации функции Ф. В результате разбиения в конечном счете получается структура. Переход от функции к структуре – синтез.

Синтез неоднозначен. Декомпозиция функций блоков выполняется до тех пор, пока не получатся типовые функции, каждая из которых может быть реализована той или иной микросхемой.

Полученный первоначально проект требует тщательной проверки, поэтому за этапом синтеза следует этап анализа, проводимого моделированием и теоретической верификацией. Моделирование имеет несколько уровней с разной степенью отображения свойств реального объекта. Оно может быть функциональным, проверяющим правильность логической структуры устройства, временным, учитывающим задержки сигналов в схемах устройства и т. д. В результате моделирования могут выявиться ошибки, требующие исправления, что придает процессу проектирования итеративный характер с возвратами к прежним этапам и введением в проект нужных коррекций.

К этому наглядному описанию процесса проектирования следует добавить лишь, отражая возможности современной элементной базы, что декомпозиция заканчивается при получении типовых функций, соответствующих тем или иным микросхемам или элементам функциональных библиотек программируемых БИС/СБИС.

Проектирование на основе схем программируемой логики высокой сложности выполняется только с помощью систем автоматизированного проектирования (САПР). Результаты концептуального синтеза вводятся в САПР, которая производит компиляцию проекта, т. е. синтезирует устройство в базисе библиотеки своих моделей. Далее производится конфигурирование микросхемы программируемой логики, после чего возможна реальная проверка работы устройства – физическое моделирование проекта. При успешном завершении физического моделирования устройство готово к установке в систему.

Рабочие задания к выполнению курсовой работы, предлагаемые в методическом руководстве и охватывающие по тематике различные разделы курса «Цифровые устройства и микропроцессоры», рекомендуется выполнить в виде виртуальных экспериментов, осуществляемых посредством моделирования проектируемых устройств в программной среде Electronics Workbench. Предлагаемая методика выполнения курсовой работы направлена на формирование у студентов практических навыков проектирования цифровых устройств и позволяет получить работоспособную схему заданного устройства. Данная методика выполнения курсовой работы проверена многолетней практикой преподавания автора и испытана временем.

По выполненному учебному исследованию студенты должны подготовить соответствующую пояснительную записку. Она должна содержать схемы спроектированного устройства и его отдельных функциональных блоков; схемы исследования их работы; определенные (измеренные и рассчитанные) параметры всего устройства и его блоков; графические построения; выводы по результатам выполненной работы.

1 Цели и задачи курсовой работы

Основной целью выполнения курсовой работы по курсу «Цифровые устройства и микропроцессоры» является освоение методики проектирования цифровых устройств и приобретение соответствующих практических навыков по моделированию этих устройств и процессов в них.

Достижение поставленной цели обеспечивается решением следующих задач:

- на основе тщательного анализа содержания технического задания определить общую структуру проектируемого устройства;

- провести декомпозицию проектируемого устройства, т.е. определить его основные функциональные блоки;

- собрать схемы каждого из функциональных блоков устройства с помощью средств, предоставляемых программной средой Electronics Workbench;

- определить порядок управления работой спроектированного устройства, т.е. установить последовательность формирования управляющих сигналов;

- исследовать временные соотношения между различными сигналами управления и при необходимости изменить эти соотношения.

2 Задания к выполнению курсовой работы

В курсовой работе необходимо спроектировать устройство по индивидуальному заданию с помощью системы моделирования Electronics Workbench и продемонстрировать его работу. В процессе разработки проектируемого устройства отдельные его блоки необходимо выполнить на основе микросхем, представленных в библиотеке элементов программы Electronics Workbench, и оформить их в виде подсхем с соответствующими названиями.

Ниже представлен перечень заданий к выполнению курсовой работы (таблица 1), которые разделены в три группы по начальным буквам фамилии студентов. Вариант индивидуального задания и дополнительные методические указания к его выполнению определяются по первой букве фамилии студента и по последней цифре номера его зачетной книжки (первая колонка). При выполнении многих из предложенных заданий необходим источник входной двоичной информации, в качестве которого можно использовать блок Data, из иллюстративного примера, описанного в методических рекомендациях. В некоторых заданиях требуется переключение между несколькими блоками (на входе или на выходе проектируемого устройства), это можно осуществить с помощью дешифратора (блок DC). Для подключения выходов одного из нескольких блоков к следующему блоку (например, к индикаторам) необходимо использовать буферные элементы (блок Buffer). Автор надеется, что студент, читающий эти строки, уже понял, что он очень много может почерпнуть из изучения иллюстративного примера, рассмотренного в излагаемых далее методических рекомендациях к выполнению курсовой работы.

Т а б л и ц а 1 – Перечень заданий к выполнению курсовой работы

|

№ |

Задание |

|

1. Начальная буква фамилии студента – А...З |

|

|

0 |

Разработать устройство ввода информации от шестнадцати клавиш на основе приоритетных шифраторов с сохранением нескольких введенных кодов в фиксированных, адресно определяемых ячейках. В качестве ячеек хранения сформированных кодов использовать регистры. |

|

1 |

Разработать устройство ввода информации от шестнадцати клавиш на основе приоритетных шифраторов с сохранением нескольких введенных чисел путем смещения их из ячейки в ячейку. В качестве ячеек хранения сформированных кодов использовать регистры. |

|

2 |

Разработать устройство, выполняющее логические операции над двумя четырехразрядными двоичными числами. Устройство должно обладать возможностями ввода операндов, переключения реализуемых функций и отображения операндов и результата выполнения выбранной операции. |

|

3 |

Разработать четырехразрядный сумматор для последовательных операндов. Устройство должно обладать возможностью ввода суммируемых чисел и отображения различных этапов преобразования. |

|

4 |

Разработать четырехразрядный параллельный сумматор с параллельным переносом. Устройство должно обладать возможностью ввода суммируемых чисел и отображения различных этапов преобразования. |

|

5 |

Разработать четырехразрядный накапливающий сумматор. Устройство должно обладать возможностью ввода суммируемого операнда и отображения различных этапов преобразования. |

|

6 |

Разработать универсальный логический модуль на основе мультиплексоров (УЛМ) для реализации четырех функций трех аргументов. Настройка УЛМ должна осуществляться константами 0 и 1, т.е. необходимо использовать алфавит {0,1}. Устройство должно обладать возможностью переклюючения реализуемых функций. |

|

7 |

Разработать универсальный логический модуль на основе мультиплексоров (УЛМ) для реализации четырех функций трех аргументов. Для настройки УЛМ необходимо использовать

расширенный алфавит {0,1, |

Продолжение таблицы 1

|

8 |

Разработать универсальный лоический модуль на основе мультиплексоров (УЛМ) для реализации двух функций четырех аргументов. Настройка УЛМ должна осуществляться константами 0 и 1, т.е. необходимо использовать алфавит {0,1}. Устройство должно обладать возможностью переключения реализуемых функций. |

|

9 |

Разработать универсальный логический модуль на основе мультиплексоров (УЛМ) для реализации двух функций четырех аргументов. Для настройки УЛМ необходимо использовать

расширенный алфавит {0,1, |

|

2. Начальная буква фамилии студента – И...С |

|

|

0 |

Разработать устройство параллель-ной передачи четырехразрядных двоичных чисел между несколькими портами с помощью буферных элементов. Устройство должно обладать возможностью первоначального ввода информации во входные порты, а также отображения содержимого всех портов. |

|

1 |

Разработать устройство параллельной передачи четырехразрядных двоичных чисел между несколькими портами на основе многоразрядного мультиплексора и демультиплексора. Устройство должно обладать возможностью первоначального ввода информации во входные порты, а также отображения содержимого всех портов. |

|

2 |

Разработать устройство последовательной передачи четырехразрядных двоичных чисел. Устройство должно обладать возможностью первоначального ввода информации во входной порт и отображения различных этапов преобразования. |

|

3 |

Разработать устройство передачи четырехразрядных двоичных чисел с выявлением одиночной ошибки на мажоритарных элементах. Устройство должно обладать возможностями первоначального ввода информации во входной порт, искусственного внесения ошибки в канал передачи и отображения информации на всех участках канала передачи. |

|

4 |

Разработать устройство передачи четырехразрядных двоичных чисел с выявлением одиночной ошибки и ее исправления методом контроля по модулю два. Устройство должно обладать возможностями первоначального ввода информации во входной порт, искусственного внесения ошибки в канал передачи и отображения информаций на всех участках канала передачи. |

Продолжение таблицы 1

|

5 |

Разработать четырехразрядный реверсивный счетчик с предустановкой на основе D-триггеров. Устройство должно обладать возможностями ввода предустановочного числа и отображения различных этапов преобразования. |

|

6 |

Разработать четырехразрядный реверсивный счетчик с предустановкой на основе JK-триггеров. Устройство должно обладать возможностями ввода предустановочного числа и отображения различных этапов преобразования. |

|

7 |

Разработать четырехразрядный универсальный регистр с предустановкой на основе D-триггеров. Устройство должно обладать возможностями ввода предустановочного числа и отображения различных этапов преобразования. |

|

8 |

Разработать четырехразрядный универсальный регистр с предустановкой на основе JK-триггеров. Устройство должно обладать возможностями ввода предустановочного числа и отображения различных этапов преобразования. |

|

9 |

Разработать четырехразрядный счетчик на основе JK-триггеров и логических элементов, работающий в двух режимах – как двоичный счетчик и как счетчик в коде Грея. Устройство должно обладать возможностями ввода предустановочного числа и отображения различных этапов преобразования. |

|

3. Начальная буква фамилии студента – Т...Я |

|

|

0 |

Разработать четырехразрядный счетчик на основе D-триггеров c мультиплексным управлением, работающий в двух режимах – как двоичный счетчик и как счетчик в коде Грея. Устройство должно обладать возможностями ввода предустановочного числа и отображения различных этапов преобразования. |

|

1 |

Разработать четырехразрядный счетчик по структуре с кодированием типа “1 из N”, работающий в двух режимах – как двоичный счетчик и как счетчик в коде Грея. Устройство должно обладать возможностями ввода предустановочного числа и отображения различных этапов преобразования. |

|

2 |

Разработать устройство передачи четырехразрядных двоичных чисел с выявлением одиночной ошибки и ее исправления с применением кодов Хемминга. Устройство должно обладать возможностями ввода предустановочного числа и отображения различных этапов преобразования. |

Продолжение таблицы 1

|

3 |

Разработать четырехразрядный реверсивный счетчик на основе JK-триггеров и с возможностью изменения модуля счета. Устройство должно обладать возможностями ввода модуля счета и отображения различных этапов преобразования. |

|

4 |

Разработать четырехразрядный реверсивный счетчик на основе D-триггеров и с возможностью изменения модуля счета. Устройство должно обладать возможностями ввода модуля счета и отображения различных этапов преобразования. |

|

5 |

Разработать устройство, выполняющее операции сложения и вычитания в дополнительном коде над двумя четырехразрядными двоичными числами. Устройство должно обладать возможностями ввода операндов и отображения различных этапов преобразования. |

|

6 |

Разработать устройство, выполняющее операции сложения и вычитания в обратном коде над двумя четырехразрядными двоичными числами. Устройство должно обладать возможностями ввода операндов и отображения различных этапов преобразования. |

|

7 |

Разработать устройство преобразования двухразрядных шестнадцатеричных чисел в десятеричные. Устройство должно обладать возможностями ввода преобразуемого числа и отображения различных этапов преобразования. |

|

8 |

Разработать запоминающее устройство с линейной структурой (т.е. по структуре 2D) для хранения восьми четырехразрядных слов на основе четырехразрядных регистров. Устройство должно обладать возможностями ввода операндов и отображения различных этапов преобразования. |

|

9 |

Разработать запоминающее устройство с линейной структурой (т.е. по структуре 2D) для хранения восьми четырехразрядных слов на основе JK-триггеров. Устройство должно обладать возможностями ввода операндов и отображения различных этапов преобразования. |

3 Методические рекомендации

С целью иллюстрации порядка выполнения курсовой работы рассмотрим процесс разработки устройства динамического вывода информации.

Техническое задание: Разработать устройство динамического вывода информации с возможностью демонстрации его работы.

3.1 Структура устройства

Исходя из содержания задания предполагается, что имеются несколько (например, четыре) узлов некоторого устройства, каждый из которых выдает на выходе двоичный код десятичного числа; назовем их источниками информации. Возможно, это – значение некоторой измеренной или вычисленной величины в виде четырехразрядного десятичного числа.

Для отображения этого четырехразрядного десятичного числа посредством десятичных символов необходимо, в первую очередь, преобразовать значение каждого разряда десятичного числа, т.е. двоичный код каждого из источников, в соответствующий 7-разрядный входной код индикатора (для краткости будем называть его 7-сегментным кодом), а затем подавать их во входы четырех 7-сегментных индикаторов. Изложенный способ отображения информации называется статическим выводом. Учитывая сложность преобразователя двоичного кода в 7-сегментный код (следовательно, и стоимости), можно сделать вывод о нецелесообразности применения данного метода, т.е. многократного использования преобразователя.

На практике для отображения многоразрядного десятичного числа применяют другой метод, называемый динамическим выводом. Суть его состоит в следующем. Двоичный код каждого из выводимых чисел поочередно подается на единственный преобразователь, а затем полученный 7-сегментный код поступает на соответствующий индикатор и отображается. Другими словами в определенный момент отображается только один символ. Учитывая инерционность зрительной памяти (вспомните частоту сменяемости кинокадров), можно подобрать частоту подключения источников к преобразователю, при котором можно не замечать сменяемость отображения, и наблюдателю будет казаться, что все индикаторы отображают информацию одновременно.

Исходя из изложенного можно определить общую структуру проектируемого устройства (обведенная часть рисунка 1). Ввиду того, что устройство должно иметь демонстрационные возможности, в качестве источников отображаемой информации используется отдельный блок памяти (Память данных), где хранятся эти двоичные коды. Соответствующая информация в ячейки этого блока памяти записываются с вспомогательного блока (Формирователь данных), формирующего двоичные коды чисел. На практике эти коды, разумеется, формировали бы сами источники.

Рисунок 1

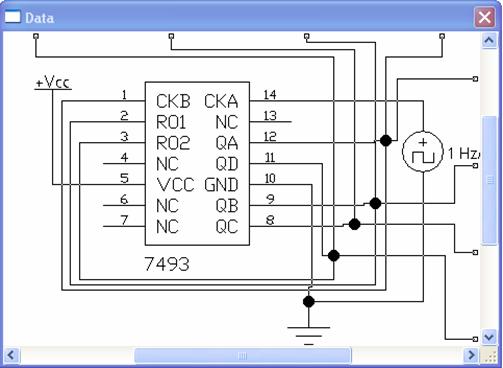

3.2 Формирователь данных – Data

В качестве формирователя данных используется простейший счетчик в виде микросхемы 7493. Эта микросхема содержит в своем составе два счетчика (одноразрядный со входом CKA и трехразрядный со входом CKB). Эти счетчики соединены последовательно для образования четырехразрядного счетчика и на вход первого из них (CKA) подключен генератор прямоугольных импульсов, работающий на частоте 1 Hz. С целью обеспечения модуля счета 10, выводы R01 и R02 счетчика подключены к соответствующим выходным выводам (1010=10102). Следовательно, это устройство будет формировать все четырехразрядные двоичные коды чисел от 0 до 9 с частотой 1 Hz, любой из которых можно будет сохранить в качестве кода отображаемого числа. Этот блок объединен в подсхему с названием Data (рисунок 2).

Рисунок 2

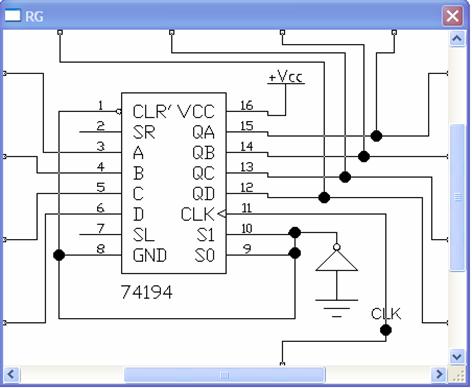

3.3 Память данных – RG

В качестве ячейки памяти данных, т.е. одного из источников отображаемых данных, используется универсальный регистр – микросхема 74194 (рисунок 3). Он постоянно поставлен на режим параллельной записи (S0=S1=1). Сигнал очистки отключен (CLR’=1). Этот блок объединен в подсхему под названием RG.

Блок памяти данных разработанного устройства составлен их четырех таких ячеек, данные в которые записываются со смещением их из одной ячейки в другую. Для этого выходы каждой ячейки подключены к информационным входам последующей ячейки. Управление записью в ячейки осуществляется сигналом CLK.

Рисунок 3

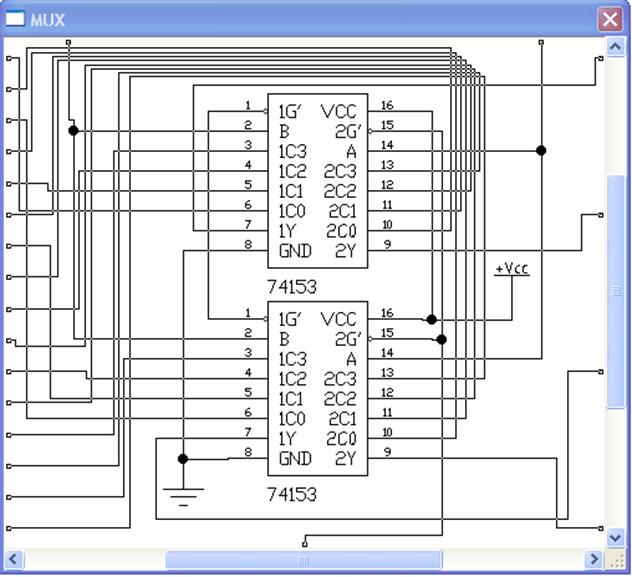

3.4 Переключатель данных – MUX

Переключатель данных в определенный момент должен передавать все четыре разряда данных одного источника на свои выходы, т.е. на преобразователь. Это можно обеспечить с помощью четырех параллельно работающих мультиплексоров со четырьмя информационными входами. Для этого были использованы две микросхемы 74153, содержащие в своем составе два таких мультиплексора. Эти микросхемы объединены в подсхему под названием MUX (рисунок 4). Выводы информационных входов мультиплексоров выведены из подсхемы в сгруппированном виде соответственно источникам данных (т.е. все выводы С0 – в одну группу, все С1 – в следующую группу и т.д.).

Примечание: при сборке схемы и объединении ее в подсхему, схема может выглядеть не так наглядно, как она изображена на рисунке; в этом случае правильность проведенных соединении проверяется выделением искомой линии (двойным нажатием).

Рисунок 4

Рисунок 4

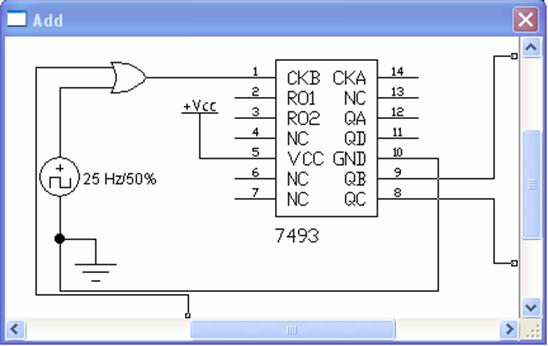

3.5 Формирователь адреса – Add

Переключение данных на информационных входах мультиплексоров осуществляется изменением их адресов. Для быстрого (с частотой 25 Hz) изменения адресов мультиплексоров был использован двухразрядный счетчик на основе микросхемы 7493, с подключенным к нему генератором. Этот блок объединен в подсхему с названием Add (рисунок 5).

Рисунок 5

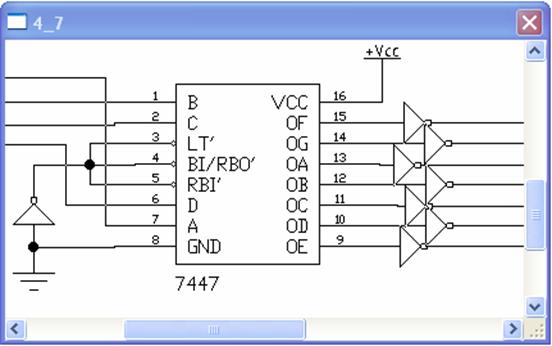

3.6 Преобразователь кода – 4_7

Функцию преобразования двоичного кода десятичных чисел в соответствующий 7-сегментный код выполняет микросхема 7447. Назначение его входных и выходных сигналов представлена в таблице 2.

Т а б л и ц а 2 – Микросхема 7447 (BCD-to-Seven-Segment Dec)

|

Inputs |

Outputs |

|||||||||||||

|

No |

LT’ |

RBI’ |

D |

C |

B |

A |

BI’/RBO’ |

a |

b |

c |

d |

e |

f |

g |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

1 |

1 |

x |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

|

2 |

1 |

x |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

|

3 |

1 |

x |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

|

4 |

1 |

x |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

5 |

1 |

x |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|

6 |

1 |

x |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

7 |

1 |

x |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

|

8 |

1 |

x |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

9 |

1 |

x |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

|

BI |

x |

x |

x |

x |

x |

x |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

RBI |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

LT |

0 |

x |

x |

x |

x |

x |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Для согласования уровней выходных сигналов преобразователя с необходимыми уровнями входных сигналов 7-сегментных индикаторов библиотеки программы Electronics Workbench к выходам преобразователя подключены инверторы. Этот блок объединен в подсхему с названием 4_7 (рисунок 6).

Рисунок 6

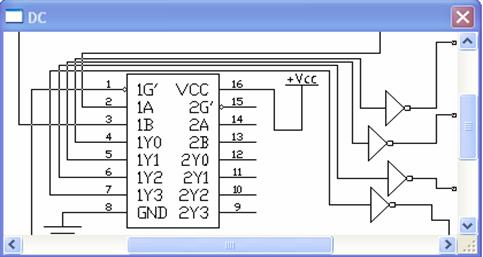

3.7 Дешифратор индикаторов – DC

Одновременность передачи входных данных с определенного источника и подачи при этом выходных сигналов преобразователя на соответствующий 7-сегментный индикатор обеспечивается дешифратором, работающим от того же адресного блока Add, что и переключатель данных. В качестве такого дешифратора используется один из дешифраторов из состава микросхемы 74139. его выходные сигналы инвертированы для согласования их уровня с уровнем управляющего сигнала буферных элементов, подключаемых далее. Данный блок объединен в подсхему с названием DC (рисунок 7).

Рисунок 7

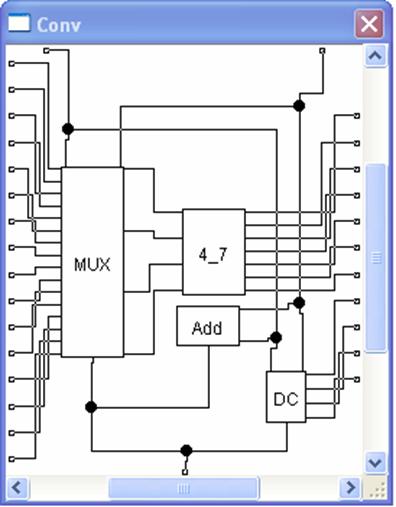

3.8 Преобразователь – Conv

Блоки MUX, Add, 4_7 и DC составляют основную часть проектируемого устройства и поэтому они были объединены в единый блок под названием Conv (рисунок 8).

Рисунок 8

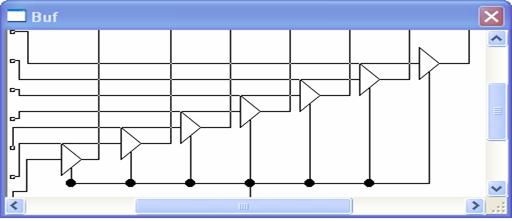

3.9 Буферные блоки – Buffer

Выходные сигналы преобразователя передаются к соответствующему 7-сегментному индикатору через буферные блоки. Режим пропускания соответствующего буферного блока обеспечивается дешифратором, рассмотренным ранее. Отдельный буферный блок составлен с помощью семи буферных элементов и объединен в подсхему с названием Buf (рисунок 9), а четыре таких блока объединены в подсхему с названием Buffer (рисунок 10).

Рисунок 9

Рисунок 10

3.10 Управляющий блок – Control

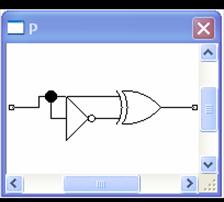

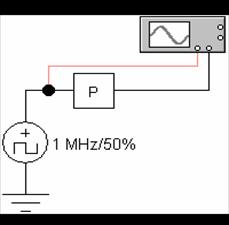

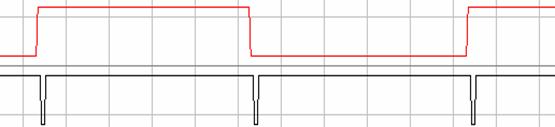

Управление устройством (рисунок 11) осуществляется с помощью двух ключей (клавиш): ключом С обеспечивается запись двоичных кодов в ячейки памяти, а ключ D переводит устройство в режим отображения (или наоборот). На линии сигнала С установлен формирователь одиночного импульса. Схема этого формирователя, схема исследования его работы и результат формирования одиночного импульса на каждое нажатие клавиши представлены на рисунке 12.

Рисунок 11

|

|

|

|

а |

б |

|

|

|

|

в |

|

Рисунок 12

3.11 Cхема устройства – Dynamic Display

Окончательная схема спроектированного устройства представлена на рисунке 13.

Рисунок 13

Проверка работы устройства осуществляется следующим образом:

- с помощью клавиши С ввести данные в регистры;

- клавишей D перевести устройство в режим отображения.

При частоте 25 Hz, установленной в блоке Add, характер сменяемости кадров отображения практически должен быть незаметен для наблюдения (вспомните частоту сменяемости кинокадров). Но на самом деле при наблюдении результатов данного моделирования проявляется более медленная скорость сменяемости кадров, что немного ухудшает его наглядность. Это объясняется скоростью моделирования самой системы Electronics Workbench.

Выводы

Спроектированная модель устройства динамического отображения многоразрядной цифровой информации показала свою работоспособность и эта схема может служить в качестве основы для практического изготовления этого устройства на микросхемах малой и средней степени интеграции или для создания его с помощью программируемой микросхемы.

1. Угрюмов Е. П. Цифровая схемотехника. – СПб.: БХВ-Петербург, 2004.

2. Бойко В.И. и др. Схемотехника электронных устройств. Цифровые устройства. – СПб.: БХВ-Петербург, 2004.

3. Сугано Т. Дж., Уидмер Н. С. Цифровые системы. Теория и практика: Пер. с англ. – М.: Издательский дом “Вильямс”, 2004.

4. Уэйкерли Дж. Ф. Проектирование цифровых устройств. – М.: Постмаркет, 2002.

5. Опадчий Ю. Ф., Глудкин О. П., Гуров А. И. Аналоговая и цифровая электроника / Под ред. О.П. Глудкина. – М.: Радио и связь, 2003.

6. Токхейм Р. Основы цифровой электроники: Пер. с. англ. – М.: Мир, 1988.

7. Шанаев О.Т. Система моделирования Electronic Workbench / на казахском и русском языках. – Алматы, 2003.

Содержание

1 Цели и задачи курсовой работы

2 Задания к выполнению курсовой работы

3.2 Формирователь данных – Data

3.4 Переключатель данных – MUX

3.5 Формирователь адреса – Add

3.6 Преобразователь кода – 4_7

3.7 Дешифратор индикаторов – DC

3.10 Управляющий блок – Control