АЛМАТИНСКИЙ ИНСТИТУТ ЭНЕРГЕТИКИ И СВЯЗИ

Кафедра электроники и компьютерных технологий

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ

Методические указания и задание к выполнению курсовой работы

для студентов всех форм обучения специальности 050719 – Радиотехника, электроника и телекоммуникации

СОСТАВИТЕЛЬ: С.Н.Петрищенко. Цифровые устройства и микропроцессоры. Методические указания и задание к выполнению курсовой работы для студентов всех форм обучения специальности 050719 – Радиотехника, электроника и телекоммуникации.

В методической разработке приводятся задание на курсовую работу и методические указания к ее выполнению по курсу «Цифровые устройства и микропроцессоры». Курсовая работа посвящена организации устройства сбора данных на микропроцессорной основе. При разработке микропроцессорного устройства необходимо составить его структурную схему, организовать на микросхемах оперативную память заданной емкости, написать по составленному алгоритму программу как на языке ассемблера, так и в машинных кодах и оценить быстродействие разработанного устройства.

1 Курсовая работа и методические указания к ее выполнению

Курсовая работа имеет цели закрепления и применения знаний, полученных при изучении курса «Цифровые устройства и микропроцессоры». Она посвящена принципам организации устройства сбора данных в виде микропроцессорного устройства. На начальном этапе изучения сложной микропроцессорной техники студенту необходимо использовать для организации вычислительного процесса сбора данных наиболее простую модель восьмиразрядного микропроцессора Intel 8080 (аналоги KP580ИК80 или КР580ВМ80А) или i8085 (аналог K1821BM85A).

При измерении каналов связи или приеме телеметрической информации в электронно-вычислительную машину (ЭВМ) часто возникает необходимость обеспечить сбор данных. При этом опрос аналоговых сигналов в виде напряжений или токов сопровождается их преобразованием в цифровую форму и размещением в некоторой области оперативной памяти (ОЗУ) с целью последующей обработки и отображения.

1.1 Задание к курсовой работе

Спроектировать устройство сбора данных (УСД), которое должно работать следующим образом: последовательно опрашивая аналоговые сигналы, поступающие на F входов коммутатора каналов (КК), необходимо с помощью аналого-цифрового преобразователя (АЦП) преобразовать эти сигналы в цифровую форму (двоичные слова разрядностью 1 байт=8бит) и разместить в некоторую область оперативного запоминающего устройства (ОЗУ), начиная с ячейки, имеющей адрес с символическим названием М.

УСД имеет в своем составе ОЗУ емкостью Q = N·n (N ячейка с разрядностью n) и форматом адресного слова 2 байта =16 бит. Синхронизация работы микропроцессорной системы осуществляется от генератора тактируемых импульсов (ГТИ). Частота синхронизации f=500 кГц.

Требуется:

а) проработать вопрос организации ОЗУ;

б) реализовать УСД в виде микропроцессорного устройства, выполненного на основе 8-разрядного микропроцессора (МП). При этом, текущий адрес очередного канала должен храниться, согласно заданному варианту таблицы 1, в регистре R. Микропроцессорное устройство необходимо довести до уровня структурной схемы, составить программу его функционирования на языке ассемблера, представить таблицу размещения программы в памяти, начиная с ячейки с адресом BEG, а также оформить программу в кодовых комбинациях (на машинном языке);

в) оценить быстродействие УСД .

Варианты индивидуальных заданий приведены в таблице 1.

Вариант индивидуального задания определяется по предпоследней (Nпред ) и последней (Nпосл ) цифрам номера студенческого билета.

Т а б л и ц а 1

|

Nпред |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

F10 |

6 |

8 |

7 |

9 |

10 |

12 |

11 |

13 |

15 |

14 |

|

R |

D |

E |

C |

B |

D |

C |

E |

B |

E |

D |

|

Nпосл |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

М |

0732 |

04F6 |

7520 |

003C |

01AE |

0701 |

3611 |

01B0 |

012A |

03E5 |

|

Q |

2048 x 8 |

8192 x 8 |

32768 x 8 |

512 x 8 |

1024 X 8 |

2048 x 8 |

32768 x 8 |

512 x 8 |

32768 x 8 |

1024 x 8 |

|

ВЕG |

0316 |

1A4D |

56B8 |

0021 |

01D8 |

03B6 |

4C82 |

006A |

031A |

071A |

1.2 Методические указания к выполнению курсовой работы

Методика решения поставленной задачи построена на выполнении следующего примера. Пусть исходные данные для проектирования УСД имеют следующие значения: F = 1610 ; М = 21А0h; Q = 64K·8, то есть 64·1024 = 65536 ячеек разрядностью 1 байт; R = B; BEG = 21C8h .

1.2.1 Организация оперативного запоминающего устройства (ОЗУ)

Оперативная память организована на базе больших интегральных схем (БИС) полупроводниковых ОЗУ.

Выбор БИС осуществляют, исходя из разных критериев:

- минимизация аппаратных затрат (число корпусов);

- минимизация потребляемой мощности;

- повышение быстродействия МПС и других.

Число микросхем m оперативной памяти требуемой емкости Мт определяют по формуле

![]() m = Mт / M1

m = Mт / M1

где М1 – емкость одной выбранной микросхемы.

При наращивании разрядности организуют линейки. Количество микросхем в каждой линейке

m1 = n т / n

где n т – требуемая разрядность;

n – разрядность выбранной микросхемы.

Количество линеек mл определяют по формуле

mл = m / m1 .

![]()

![]()

![]()

![]() Для активизации

одной из двух линеек применяют логический элемент НЕ или, при большем

количестве линеек, дешифратор, на входы которого подается двоичный код адреса

линейки. Выходы дешифратора соединяют с входами СS (выбор кристалла)

всех микросхем. При СS = 1 обращение к микросхемам в данной линейке

будет заблокировано (режим хранения). При СS = 0 - обращение

разрешается. При формировании сигнала СS используют

незадействованные старшие разряды адресной шины.

Для активизации

одной из двух линеек применяют логический элемент НЕ или, при большем

количестве линеек, дешифратор, на входы которого подается двоичный код адреса

линейки. Выходы дешифратора соединяют с входами СS (выбор кристалла)

всех микросхем. При СS = 1 обращение к микросхемам в данной линейке

будет заблокировано (режим хранения). При СS = 0 - обращение

разрешается. При формировании сигнала СS используют

незадействованные старшие разряды адресной шины.

![]()

![]()

![]()

![]() Для обеспечения

режима записи двоичных слов или их чтения в микросхемах ОЗУ предусмотрены входы RD/WR (чтение/запись).

Причем, при RD/WR = 0 обеспечивается режим записи, при RD/WR = 1 - режим чтения.

Для обеспечения

режима записи двоичных слов или их чтения в микросхемах ОЗУ предусмотрены входы RD/WR (чтение/запись).

Причем, при RD/WR = 0 обеспечивается режим записи, при RD/WR = 1 - режим чтения.

В таблице 2 приведены основные параметры некоторых микросхем оперативной памяти.

Т а б л и ц а 2

|

Тип микросхемы |

Емкость |

Время цикла (выборки), нс |

Потребляемая мощность, мВт |

Напряжение питания, В |

Технология |

|

К155РУ5 |

256Х1 |

90 |

< 735 |

5 |

ТТЛ |

|

КР537РУ13А |

1КХ4 |

120 |

350 |

5 |

КМДП |

|

КР541РУ5 |

1КХ8 |

(55) |

< 500 |

5 |

ИИЛ-ТТЛ |

|

КР537РУ10 |

2КХ8 |

220 |

350 |

5 |

КМДП |

|

КМ132РУ13А |

2КХ8 |

(55) |

900 |

5 |

n-МДП |

|

К537 РУ14А |

4КХ1 |

110 |

250 |

5 |

КМДП |

|

КМ132РУ12А |

4КХ4 |

(50) |

700 |

5 |

n-МДП |

|

КР132РУ6А |

16КХ1 |

75 |

400 |

5 |

n-МДП |

|

КМ132РУ10А |

64КХ1 |

90 |

420 |

5 |

n-МДП |

Исходя из минимизации аппаратных затрат выберем из таблицы 1 микросхему ОЗУ КМ132РУ10А. Она содержит 64К ячеек с разрядностью 1 бит. Для построения ОЗУ емкостью 64КХ8 потребуется 8 таких микросхем, так как

.

.

На рисунке 1 приведена схема построения такого ОЗУ. У каждой микросхемы количество адресных входов А = 16, так как 216 обеспечивает адресацию 65536 ячеек памяти разрядностью 1 бит. При организации восьми микросхем ОЗУ в одну линейку получается заданная емкость Q = 64K·8.

![]() Для активизации одновременно всех восьми микросхем необходимо

обеспечить подачу логического нуля на все их входы, обозначенные как CS . По входам DI (data input) идет запись, а по DO (data output)–

считывание информации, записанной в микросхемы памяти.

Для активизации одновременно всех восьми микросхем необходимо

обеспечить подачу логического нуля на все их входы, обозначенные как CS . По входам DI (data input) идет запись, а по DO (data output)–

считывание информации, записанной в микросхемы памяти.

:

◊

0

Рисунок 1

1.2.2 Реализация УСД в виде микропроцессорного устройства на базе 8-разрядного микропроцессора.

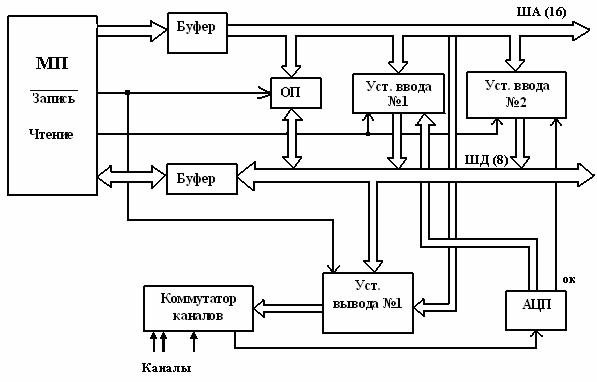

Структурная схема УСД, построенного в виде микропроцессорного устройства (МПУ), представлена на рисунке 2. Кроме микропроцессора, АЦП, оперативной памяти (ОП) и коммутатора аналоговых каналов, схема МПУ содержит два устройства ввода и одно устройство вывода данных, роль которых могут выполнять программно-управляемые регистры-порты, например, многорежимные буферные регистры (МБР) К589ИР12.В таком варианте МПУ и шина управления может состоять всего из двух линий: ЗАПИСЬ и ЧТЕНИЕ.

На схеме рисунка 2 для простоты не показан триггер-флаг АЦП (Тфл), который вырабатывает сигнал окончания (ОК) преобразования в АЦП.

Начальный адрес 2IAOh ячейки памяти области OП, отведенной для сбора данных, будем хранить в паре регистров HL. Текущий адрес аналогового канала в соответствии с заданием будем помещать в регистр В (в нашем примере в соответствии с заданием R = В).

Рисунок 2

Рисунок 2

Примем порядок опроса аналоговых каналов, начиная с канала, имеющего номер (адрес) 0. Чтобы обеспечить формирование признака завершения цикла сбора данных, в регистр D поместим число F (число аналоговых каналов). В нашем примере F = 1610. Тогда блок-схема алгоритма сбора данных будет иметь вид рисунка 3.

Дадим краткие пояснения к блок- схеме. В блоке I в пару регистров HL загружается начальный адрес M = 21АОh. В блоке 2 в регистр D загружается число 1610 (10h ). В блоке 3 регистр R = B служит счетчиком адресов аналоговых каналов. В него загружается адрес первого канала ØØh. Затем этот адрес через аккумулятор и устройство вывода № I (блоки 4 и 5) поступает на адресный вход коммутатора, как показано на рисунке 2. Коммутатор подключает первый канал ко входу АЦП и запускает последний. МПУ переходит в режим ожидания окончания акта преобразования в АЦП (блоки 6, 7 и 8). Сигнал с выхода ОК (окончание) АЦП заносится в младший разряд регистра-порта ввода №2. Пока ОК=0, акт в АЦП не окончен. В этом случае блоки 6+8 обеспечивают запись триггер-флага с нуля и прохождение программы по малому циклу. Данный режим выполнения программы продолжается до тех пор, пока сигнал ОК на выходе АЦП не станет равным 1. Так обеспечивается режим ожидания. Как только ОК станет равным 1, то после выполнения команды блока 8 С=1 осуществляется запись данных с выхода АЦП в устройство ввода № 1 и через аккумулятор микропроцессора в заданную ячейку оперативной памяти (блоки 9 и 10).

Рисунок 3

Далее формируется адрес следующих: ячейки памяти (блок 11) и аналогового канала (блок 12). Новый адрес канала засылается в аккумулятор (блок 13). В блоке 14 выполняется операция сравнения содержимого регистров В и D. Равенство В = D = 0 говорит о том, что все каналы опрошены и срабатывает нулевой признак z = 1, цикл сбора данных завершен. Если z = 0, то осуществляется опрос следующего канала, так как при выполнении операции сравнения содержимое аккумулятора остается неизменным, то есть в нем по-прежнему содержится адрес следующего канала, загруженный в блок 13. Таким образом , пока адрес очередного аналогового канала, сформированный в регистре В, в блоке 12, остается меньше IÆ16 , обеспечивается прохождение программы по большому циклу. Программа на языке ассемблера представлена в таблице 3.

Т а б л и ц а 3

|

№ команды Команды |

Метка |

Мнемокод |

Операнд (ы) |

Комментарий |

Байты |

Циклы |

Такты |

|

1 |

|

LXI |

H,21A0h |

HL ← 21A0h |

3 |

3 |

10 |

|

2 |

|

MVI |

D,10h |

D ← 10h |

2 |

2 |

7 |

|

3 |

|

MVI |

B,00h |

B ← 00h |

2 |

2 |

7 |

|

4 |

|

MOV |

A,B |

A ← B |

1 |

1 |

5 |

|

5 |

К2 |

OUT |

1 |

Устр.выв.№1 ← (A) |

2 |

3 |

10 |

|

6 |

К1 |

IN |

2 |

A ← Устр.ввода № 2 |

2 |

3 |

10 |

|

7 |

|

RRC |

|

A ← Сдв.П (А) |

1 |

1 |

4 |

|

8 |

|

JNC |

K1 |

Блок 8 УП |

3 |

3 |

10 |

|

9 |

|

IN |

1 |

А ← Устр.ввода № 1 |

2 |

3 |

10 |

|

10 |

|

MOV |

M,A |

M ← (A) |

1 |

2 |

7 |

|

11 |

|

INX |

H |

HL ← (HL) + 1 |

1 |

1 |

5 |

|

12 |

|

INR |

B |

B ← (B) + 1 |

1 |

1 |

5 |

|

13 |

|

MOV |

A,B |

A ← (B) |

1 |

1 |

5 |

|

14 |

|

CMP |

D |

(A) - (D) |

1 |

1 |

4 |

|

15 |

|

JNZ |

K2 |

Блок 15 УП |

3 |

3 |

10 |

В комментарии таблицы 3 использованы сокращения: Сдв.П (А) - сдвиг вправо содержимого регистра А ( аккумулятора ), УП – условный переход.

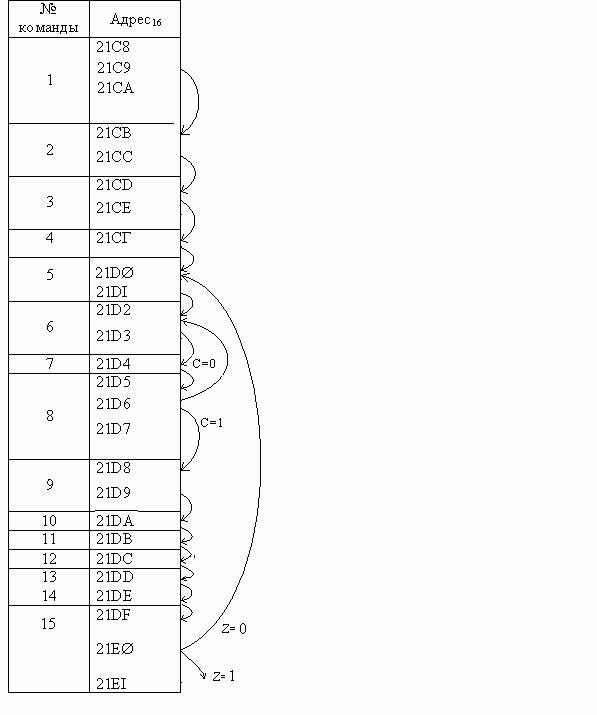

Размещение программы представлено в таблице 4.

Т а б л и ц а 4

Число ячеек ОП, отводимых под команду, определяется числом байтов в команде. В таблице 4 стрелками показана последовательность выполнения команд. В командах условного перехода, где последующее выполнение той или иной команды зависит от условия (признака), указаны пары стрелок, рядом с которыми значения сигналов-условий.

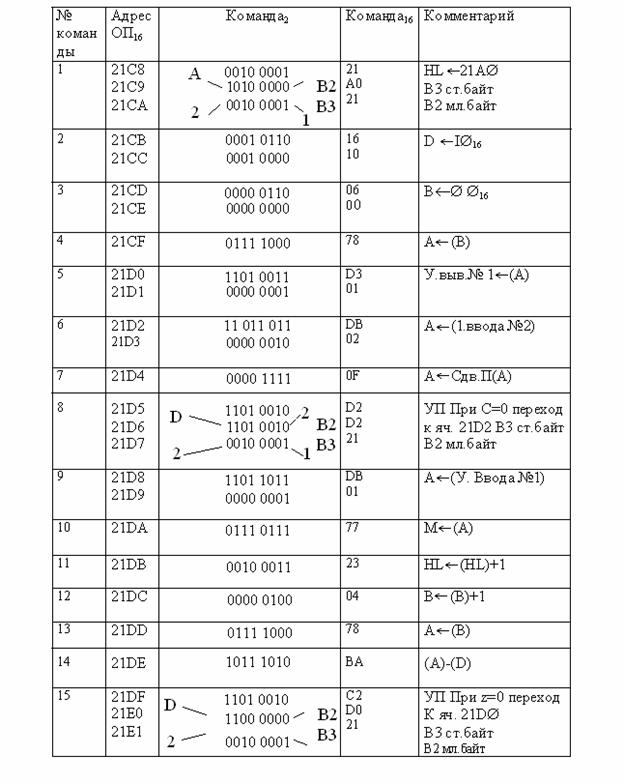

В таблице 5 представлена программа в кодовых комбинациях.

Т а б л и ц а 5

1.2.3 Оценка быстродействия микропроцессорного устройства

Для оценки

быстродействия микропроцессорного устройства будем считать, что максимальная

длительность преобразования АЦП меньше длительности периода синхроимпульсов ![]() , поэтому временем

прохода по малому циклу можно пренебречь.

, поэтому временем

прохода по малому циклу можно пренебречь.

В соответствии с таблицей 3 на выполнение команд 1 ÷ 4 требуется 10+7+7+5=29 тактов.

На один проход по большому циклу (на выполнение команд 5 ÷ 15) нужно 10+10+4+10+10+7+5+5+5+4+10=80 тактов. Всего таких проходов F=1610, что требует 80∙16=1280 тактов. В итоге длительность цикла сбора данных составит t = (29+1280) ∙2 мкс=2618 мкс.

Список литературы

1. Бойко В.И., Гуржий А.Н., Жуйков В.Я. и др. Схемотехника электронных устройств. Цифровые устройства.- СПб.: БХВ – Петербург, 2004. – 512 с.

2. Бойко В.И., Гуржий А.Н., Жуйков В.Я. и др. Схемотехника электронных устройств. Микропроцессоры и микроконтроллеры.- СПб.: БХВ – Петербург, 2004. – 464 с.

3. Калабеков Б.А. Цифровые устройства и микропроцессорные системы. Учебник для техникумов связи.- М.: Горячая линия –Телеком, 2000. – 336 с.

4. Лебедев О.Н. и др. Изделия электронной техники. Цифровые микросхемы. Микросхемы памяти. ЦАП и АЦП: Справочник.- М.:Радио и связь, 1994. – 248 с.

5. Лебедев О.Н. Применение микросхем памяти в электронных устройствах: Справочное пособие. – М.: Радио и связь, 1994. – 216 с.

6. Гольденберг Л.М. и др. Цифровые устройства и микропроцессорные системы. Задачи и упражнения: Учебное пособие. - М.: Радио и связь,1992 . - 256 с.

7. Цифровая и вычислительная техника: Учебник под ред. Э.В.Евреинова.- М.: Радио и связь, 1991. - 464 с.

8. Пухальский Г.И. Проектирование микропроцессорных систем. Учебное пособие для вузов.- СПб.: Политехника, 2001.–544 с.

9. Угрюмов Е.П. Цифровая схемотехника.- СПб.: БХВ – Санкт-Петербург, 2000. - 528 с.

10. Калабеков Б.А. Микропроцессоры и их применение в системах передачи и обработки сигналов. – М.: Радио и связь, 1988. – 368 с.

Содержание

1 Курсовая работа и методические указания к ее выполнению

1.1 Задание к курсовой работе

1.2 Методические указания к выполнению курсовой работы

1.2.1 Организация оперативного запоминающего устройства

1.2.2 Реализация УСД в виде микропроцессорного устройства на базе 8-разрядного микропроцессора.

1.2.3 Оценка быстродействия микропроцессорного устройства

Список литературы