АЛМАТИНСКИЙ ИНСТИТУТ ЭНЕРГЕТИКИ И СВЯЗИ

Кафедра электроники и компьютерных технологий

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ

Методические указания к выполнению лабораторных работ

для студентов всех форм обучения специальностей

050704 – Вычислительная техника и программное обеспечение,

050719 – Радиотехника, электроника и телекоммуникации

Алматы 2008

СОСТАВИТЕЛЬ: У.Т.Шанаев. Цифровые устройства и микропроцессоры. Методические указания к выполнению лабораторных работ для студентов всех форм обучения специальностей 050704 – Вычислительная техника и программное обеспечение, 050719 – Радиотехника, электроника и телекоммуникации. – Алматы: 2008. – 41 с.

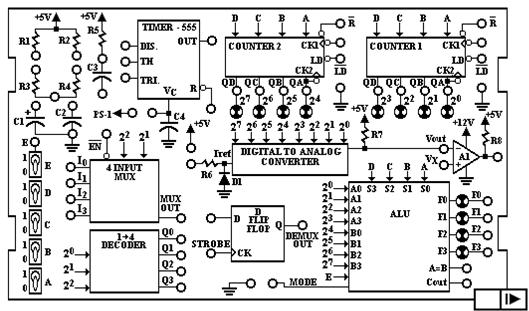

В методических указаниях представлены описания лабораторных работ по исследованию характеристик элементов и устройств цифровой электроники, выполнение которых определяет фундаментальную основу профессионального образования по первой части курса “Цифровые устройства и микропроцессоры”. Они составлены в соответствии с требованиями квалификационной характеристики специалиста, Государственных стандартов, педагогико-психологических основ организации и проведения лабораторных занятий. Предлагаемые лабораторные работы выполняются как посредством организации практических экспериментов на стенде PU-2000 фирмы Degem Systems, так и путем проведения виртуальных исследований с помощью системы моделирования Electronics Workbench.

Методические указания к лабораторным работам предназначены для студентов всех форм обучения специальностей 050704, 050719. Они могут быть использованы и для организации лабораторных занятий по идентичным темам аналогичных дисциплин, запланированных для других специальностей.

Введение

В предлагаемом в методическом руководстве к лабораторным занятиям представлены два типа рабочих заданий, отличающихся по характеру выполнения, и объединенных в соответствующие подразделы. Задания первого типа выполняются посредством проведения практических измерений и наблюдений на стенде PU-2000 фирмы Degem Systems, а второй тип заданий организовываются в виде виртуальных экспериментов, выполняемых посредством моделирования исследуемых устройств в программной среде Electronics Workbench. При этом часть заданий второго типа выносятся в качестве задания для самостоятельной работы студентов (СРС). Предлагаемая методика организации лабораторных занятий проверена многолетней практикой преподавания автора и испытана временем.

Различные формы организации учебного исследования обеспечивают более глубокие знания студентов по теории изучаемых элементов и устройств цифровой электроники и способствуют формированию у них практических навыков по проведению практических и моделирующих экспериментов.

Выполнения учебных исследований как в виде практических, так и виде виртуальных экспериментов создает возможность для организации лабораторных занятий в случае недостаточной обеспеченности лабораторным оборудованием. В таком случае одной половине студентов учебной группы можно предложить выполнение практической части эксперимента, а другой – выполнить виртуальные исследования, а затем им поменять учебные задания. Предлагаемые в методическом руководстве задания по выполнению виртуальных исследований с помощью системы моделирования Electronics Workbench в достаточном объеме обеспечивают выполнение целей и задач лабораторных занятий, что создает условия и для самостоятельного применения их в случае учебно-производственной необходимости (например, в случае отсутствия лабораторного оборудования).

По выполненному учебному исследованию студенты должны подготовить отчет. Отчет должен содержать схемы исследования, измеренные и рассчитанные данные, графические построения, определенные (измеренные и рассчитанные) параметры исследуемого элемента или устройства, выводы по результатам выполненных экспериментов, результаты выполнения задания на СРС и краткие ответы на вопросы.

1 Лабораторная работа №1. Логические элементы

1.1 Цель работы:

- определение взаимозависимости уровней входных и выходных сигналов основных логических элементов;

- освоение способов наращивания числа входов логических элементов;

- освоение различных методов и средств, применяемых для исследования цифровых устройств.

1.2 Рабочее задание

1.2.1 Исследования на стенде Degem Systems

1.2.1.1 Исследовать логику работы элементов NOT, AND, OR, размещенных на плате EB-131.

1.2.1.2 Проверить возможности наращивания числа входов логических элементов AND и OR.

1.2.1.3 Исследовать логику работы элементов NAND, NOR, XOR, размещенных на плате EB-132.

1.2.2 Исследования в системе моделирования Electronics Workbench

1.2.2.1 Исследовать логику работы элементов NOT, AND, OR, NAND, NOR, XOR, XNOR.

1.2.2.2 Проанализировать работу микросхемы логического элемента, предложенного преподавателем.

1.3 Оборудование рабочего места:

- лабораторный стенд PU-2000;

- съемные платы EB-131 и EB-132;

- соединительные провода и перемычки;

- компьютер с загруженной программной средой Electronics Workbench.

1.4 Методические указания к выполнению работы

1.4.1. Краткие сведения из теории и практические рекомендации

Логические элементы – устройства, реализующие логические функции. Они выпускаются в виде микросхем, содержащих в своем составе несколько однотипных логических элементов.

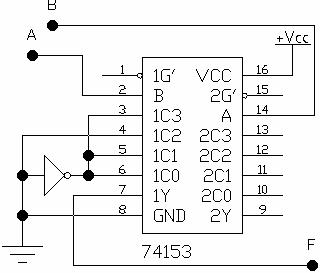

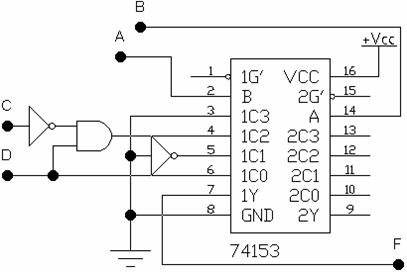

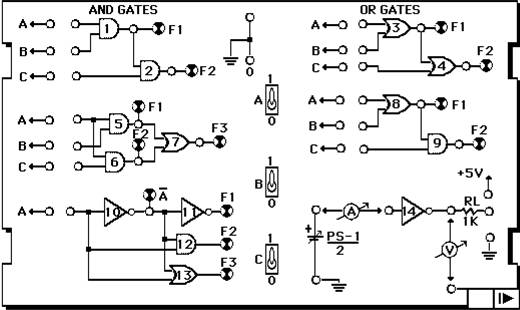

Как сказано в введении, первая часть лабораторного исследования проводится на стенде, на котором могут быть установлены различные платы, содержащие в своем составе некоторое количество определенных микросхем. Экспериментальные исследования в данной лабораторной работе проводятся с помощью съемных плат ЕB-131 и EB-132 (рисунки 1.1 и 1.2), на поверхности которых изображены условно-графические обозначения элементов с соответствующими выводами в виде гнезд для соединений, а сами микросхемы размещены в нижней невидимой стороне платы. Соединения их с соответствующими переключателями уровней (А, В, С) осуществляются с помощью соединительных проводов и перемычек. На панелях размещены схемы с фиксированными соединениями, предоставляющие возможности исследования логики их работы.

Рисунок 1.1

Рисунок 1.2

Наиболее простой метод исследования характера работы логического элемента заключается в подаче всевозможных комбинаций логических уровней на его входы и наблюдении уровня выходного сигнала. Именно этим методом мы будем пользоваться для определения свойств логических элементов, т.е. построения их таблицы истинности.

Вторая часть лабораторного исследования проводится посредством моделирования в программной среде Electronics Workbench, т.е. путем осуществления виртуальных экспериментов. В программную среду Electronics Workbench введены достаточно разнообразный набор инструментальных средств, которые предоставляют весьма широкие возможности для проведения экспериментальных исследований. Некоторые из этих средств мы используем в наших экспериментах и тем самым будем осваивать методику их применения.

В первом опыте моделирования мы будем пользоваться тем же методом, который применялся в экспериментах на стенде, т.е. будем подавать с помощью переключателей всевозможные комбинации логических уровней на входы исследуемых элементов и наблюдать уровни их выходных сигналов.

Более наглядный результат можно получить путем подачи на входы элемента прямоугольные импульсы различной частоты и наблюдением и сопоставлением временных диаграмм входных и выходного сигналов элемента с помощью логического анализатора (Logic Analyzer). Этот метод предложен для проведения второго моделирующего эксперимента (с микросхемой логического элемента). Освоение этих методов закладывает основу для организации дальнейших исследований, где они будут применяться в различных сочетаниях в зависимости от типа исследуемых устройств и характера их управляющих сигналов.

Еще одно средство, которое необходимо взять в свое вооружение, это – создание подсхем. Одним из достоинств таких подсхем является возможность их повторного и многократного использования и в других экспериментах путем переноса их из одного файла в другой. Другим достоинством использования подсхем является возможность представления объемных схем в виде нескольких функциональных блоков структурной схемы, что несомненно способствует их наглядности. В этой работе, в качестве первого опыта, предлагается создать подсхему источника логических уровней.

1.4.2. Порядок выполнения рабочего задания

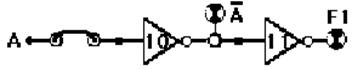

К п.1.2.1.1. Установите плату EB-131 на лабораторный стенд и исследуйте логику работы элемента NOT (рисунок 1.3), двухвходовых элементов AND (рисунок 1.4) и OR (рисунок 1.5), подавая различные уровни на их входы с помощью переключателей и наблюдая за результатом на выходе F1. Результаты этого и всех последующих исследований на стенде запишите в таблицу 1.1.

Т а б л и ц а 1.1

|

|

|

|

NOT А |

AND |

OR |

NAND |

NOR |

XOR |

||

|

A |

B |

C |

F1 |

F1 |

F2 |

F1 |

F2 |

|||

|

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

|

|

|

|

|

|

|

|

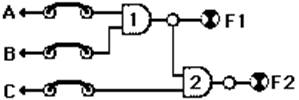

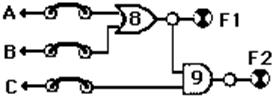

К п.1.2.1.2. Результат наращивания числа входов логических элементов до трех, полученных соединением двух двухвходовых элементов (рисунки 1.4 и 1.5) можно наблюдать на выходе F2.

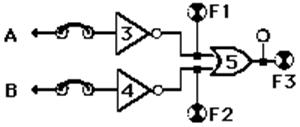

Рисунок 1.3

Рисунок 1.4

Рисунок 1.5

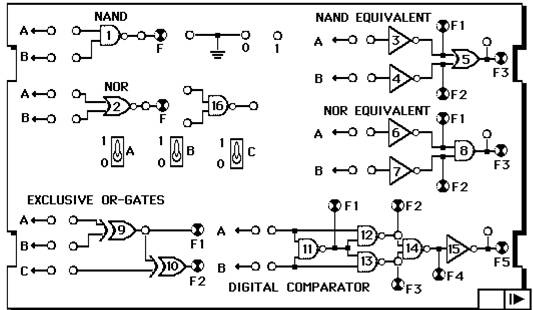

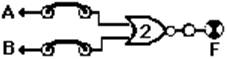

К п.1.2.1.3. Установите плату EB-132 на лабораторный стенд и исследуйте логику работы двухвходовых элементов NAND (рисунок 1.6), NOR (рисунок 1.7) и XOR (рисунок 1.8).

Рисунок 1.6

Рисунок 1.7

Рисунок 1.8

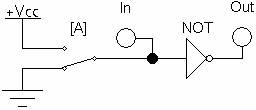

К п.1.2.2.1. Соберите схему для исследования элемента NOT, представленную на рисунке 1.9, и исследуйте логику его работы, подавая на его вход сигналы различного уровня с помощью переключателя. Результаты этого и всех последующих экспериментов на моделирование запишите в таблицу 1.2.

Рисунок 1.9

Т а б л и ц а 1.2

|

A |

B |

NOT А |

AND |

NAND |

OR |

NOR |

XOR |

XNOR |

|

0 |

0 |

|

|

|

|

|

|

|

|

0 |

1 |

|

|

|

|

|

|

|

|

1 |

0 |

|

|

|

|

|

|

|

|

1 |

1 |

|

|

|

|

|

|

|

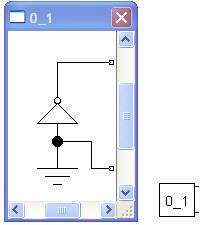

С целью ускорения построения схем изучаемых устройств в дальнейших экспериментах и проведения соответствующих исследований будем использовать различные вспомогательные средства, оформленные в виде подсхем. В качестве одного из таких средств создайте источник логических уровней под названием “0_1” (рисунок 1.10).

Рисунок 1.10

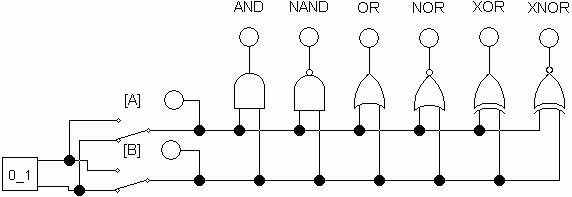

Соберите схему для комбинированного исследования двухвходовых логических элементов (рисунок 1.11) и исследуйте логику их работы.

Рисунок 1.11

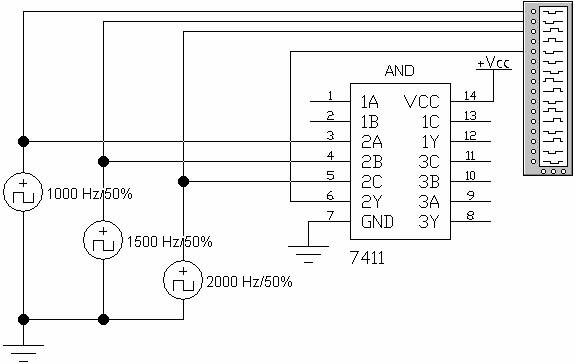

К п.1.2.2.2. На рисунке 1.12 представлена схема исследования микросхемы трехвходового элемента AND c помощью логического анализатора (Logic Analyzer). Соберите аналогичную схему для исследования работы микросхемы одного из трехвходовых элементов, предложенного преподавателем, и проанализируйте работу одного из элементов этой микросхемы. Результаты анализа скопируйте в отчет.

Рисунок 1.12

1.5 Вопросы

1. Опишите логику работы исследованных в лабораторной работе логических элементов.

2. Как осуществляется наращивание числа входов элементов AND и OR?

3. Как можно осуществить наращивание числа входов элементов NAND и NOR?

4. Опишите методику проведения исследований с помощью логического анализатора.

2 Лабораторная работа №2. Комбинационные устройства

2.1 Цель работы:

- изучение и усвоение законов и соотношений алгебры логики;

- освоение методики построения схем комбинационных устройств на основе логических элементов;

- освоение методики работы с логическим преобразователем.

2.2 Рабочее задание

2.2.1 Исследования на стенде Degem Systems

2.2.1.1 Исследовать логику работы комбинационных схем на съемной плате EB-131.

2.2.1.2 Исследовать логику работы комбинационных схем на съемной плате EB-132.

2.2.2 Исследования в системе моделирования Electronics Workbench

2.2.2.1 Построить схемы предложенного преподавателем устройства, реализующую таблично заданную функцию, на основе базовых элементов и на основе элементов NAND.

2.2.2.2 Изучить методику построения схемы комбинационного устройства с помощью логического преобразователя (Logic Converter) и реализовать предыдущую схему с его помощью.

2.3 Оборудование рабочего места:

- лабораторный стенд PU-2000;

- съемные платы EB-131 и EB-132;

- соединительные провода и перемычки;

- компьютер с загруженной программной средой Electronics Workbench.

2.4 Методические указания к выполнению работы

2.4.1 Краткие сведения из теории и практические рекомендации

Комбинационными устройствами называются устройства, выходные сигналы которых определяются только комбинацией входных сигналов. Синтез схемы комбинационного устройства осуществляется в определенной последовательности, который состоит из следующих этапов:

- словесное задание функции устройства;

- построение таблицы истинности устройства;

- представление функции устройства логическим выражением;

- минимизация полученного логического выражения;

- построение схемы устройства.

Проиллюстрируем эти действия на примере таблично заданной функции (таблица 2.1).

Т а б л и ц а 2.1

|

A |

B |

C |

F |

|

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

![]() .

.

Схема, реализующая заданную функцию на основе базовых элементов (с дополнительными элементами, необходимыми для ее исследования) представлена на рисунке 2.1, а схема на основе элементов NAND – на рисунке 2.2 .

Рисунок 2.1

Рисунок 2.2

В программу Electronics Workbench встроен прибор под названием “логический преобразователь” (Logic Converter), с помощью которого можно проделать все перечисленные этапы синтеза схемы комбинационного устройства. На рисунке 2.3 последовательно представлены этапы синтеза, реализованные с помощью логического преобразователя.

Рисунок 2.3

При анализе существующей схемы по результатам ее исследования составляется таблица истинности устройства и по ней, при необходимости, определяется логическое выражение.

2.4.2 Порядок выполнения рабочего задания

Эксперименты на стенде выполняются в виде анализа представленных на плате схем.

К п.2.2.1.1. Установите плату EB-131 на лабораторный стенд и исследуйте логику работы схемы, представленной на рисунке 2.4. Результаты исследования запишите в таблицу 2.2.

Рисунок 2.4

Т а б л и ц а 2.2

|

A |

B |

C |

F3 |

|

0 |

0 |

0 |

|

|

0 |

0 |

1 |

|

|

0 |

1 |

0 |

|

|

0 |

1 |

1 |

|

|

1 |

0 |

0 |

|

|

1 |

0 |

1 |

|

|

1 |

1 |

0 |

|

|

1 |

1 |

1 |

|

По построенной таблице истинности устройства напишите соответствующее логическое выражение для его выходного сигнала (F3) и минимизируйте его. Проверьте соответствие полученного выражения исследованной схеме.

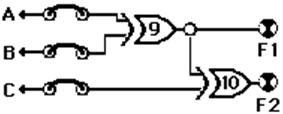

Исследуйте логику работы схемы, представленной на рисунке 2.5. Результаты исследования запишите в таблицу 2.3.

Рисунок 2.5

Т а б л и ц а 2.3

|

A |

B |

C |

F2 |

|

0 |

0 |

0 |

|

|

0 |

0 |

1 |

|

|

0 |

1 |

0 |

|

|

0 |

1 |

1 |

|

|

1 |

0 |

0 |

|

|

1 |

0 |

1 |

|

|

1 |

1 |

0 |

|

|

1 |

1 |

1 |

|

По построенной таблице истинности устройства напишите соответствующее логическое выражение для его выходного сигнала (F2) и минимизируйте его. Проверьте соответствие полученного выражения исследованной схеме.

К п.2.2.1.2. Установите плату EB-132 на лабораторный стенд и исследуйте логику работы схемы, представленной на рисунке 2.6. Результаты исследования запишите в таблицу 2.4.

Рисунок 2.6

Т а б л и ц а 2.4

|

A |

B |

F3 |

|

0 |

0 |

|

|

0 |

1 |

|

|

1 |

0 |

|

|

1 |

1 |

|

По построенной таблице истинности устройства напишите соответствующее логическое выражение для его выходного сигнала (F3) и проверьте соответствие полученного выражения исследованной схеме. Функцию какого элемента выполняет данная схема?

Исследуйте логику работы схемы, представленной на рисунке 2.7. Результаты исследования запишите в таблицу 2.5.

Рисунок 2.7

Т а б л и ц а 2.5

|

A |

B |

F3 |

|

0 |

0 |

|

|

0 |

1 |

|

|

1 |

0 |

|

|

1 |

1 |

|

По построенной таблице истинности устройства напишите соответствующее логическое выражение для его выходного сигнала (F3) и проверьте соответствие полученного выражения исследованной схеме. Функцию какого элемента выполняет данная схема?

Исследуйте логику работы схемы, представленной на рисунке 2.8. Результаты исследования запишите в таблицу 2.6.

Рисунок 2.8

Т а б л и ц а 2.6

|

A |

B |

C |

F2 |

|

0 |

0 |

0 |

|

|

0 |

0 |

1 |

|

|

0 |

1 |

0 |

|

|

0 |

1 |

1 |

|

|

1 |

0 |

0 |

|

|

1 |

0 |

1 |

|

|

1 |

1 |

0 |

|

|

1 |

1 |

1 |

|

По построенной таблице истинности устройства напишите соответствующее логическое выражение для его выходного сигнала (F2) и проверьте соответствие полученного выражения исследованной схеме. Функцию какого элемента выполняет данная схема?

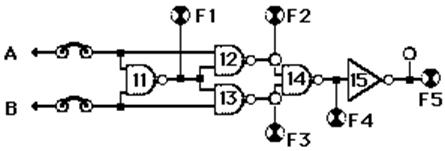

Исследуйте логику работы компаратора, представленного на рисунке 2.9. Результаты исследования запишите в таблицу 2.7.

Рисунок 2.9

Т а б л и ц а 2.7

|

A |

B |

F1 |

F2 |

F3 |

F4 |

F5 |

|

0 |

0 |

|

|

|

|

|

|

0 |

1 |

|

|

|

|

|

|

1 |

0 |

|

|

|

|

|

|

1 |

1 |

|

|

|

|

|

По построенной таблице истинности устройства напишите соответствующие логические выражения для каждого выходного сигнала (F1-F5). К выполнению каких функций соответствуют значения сигналов на этих выходах?

К п.2.2.2.1. Постройте схему одного из таблично заданных устройств (по предложенному преподавателем варианту из таблицы 2.8), последовательно выполнив все этапы синтеза по аналогии с представленным выше иллюстративным примером. Проанализируйте ее работу, дополнив схему необходимыми для исследования элементами.

Т а б л и ц а 2.8

|

A |

B |

C |

F1 |

F2 |

F3 |

F4 |

|

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

1 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

1 |

1 |

К п.2.2.2.2. Постройте схему устройства, предложенного в предыдущем пункте варианта, с помощью логического преобразователя (по аналогии с приведенным выше иллюстративным примером).

2.5 Вопросы

1. Объясните логику работы каждого из исследованных на стенде схем.

2. Объясните возможности реализации функций элементов NAND и NOR с помощью базовых элементов.

3. Объясните порядок синтеза схем комбинационных устройств.

4. Каким образом необходимо преобразовать логическое выражение для построения схемы на основе элементов NAND?

5. Объясните методику применения логического преобразователя для построения схем комбинационных устройств.

6. Можно ли использовать логический преобразователь для построения схем комбинационных устройств с несколькими выходами? Если да, то как?

3 Лабораторная работа №3. Дешифраторы и мультиплексоры

3.1 Цель работы

- освоение принципов работы дешифратора;

- освоение режимов работы мультиплексора;

- освоение способов применения дешифратора для реализации логических функций;

- освоение методов настройки универсального логического модуля на основе мультиплексора.

3.2 Рабочее задание

3.2.1 Исследования на стенде Degem Systems

3.2.1.1 Исследовать логику работы дешифратора.

3.2.1.2 Исследовать режимы работы мультиплексора.

3.2.2 Исследования в системе моделирования Electronics Workbench

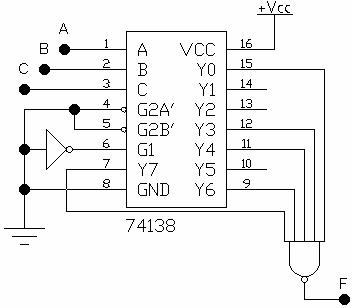

3.2.2.1 Исследовать работу дешифратора 74138.

3.2.2.2 Исследовать работу мультиплексора 74153.

3.2.2.3 Реализовать функцию комбинационного устройства (осуществленного в предыдущей работе на основе логических элементов) на основе дешифратора 74138.

3.2.2.4 Реализовать функцию комбинационного устройства (осуществленного в предыдущей работе на основе логических элементов) на основе мультиплексора 74153.

3.3 Оборудование рабочего места:

- лабораторный стенд PU-2000;

- съемные платы EB-134 и EB-132;

- соединительные провода и перемычки;

- компьютер с загруженной программной средой Electronics Workbench.

3.4 Методические указания к выполнению работы

3.4.1 Краткие сведения из теории и практические рекомендации

Дешифратор – устройство, которое в зависимости от значения двоичного кода, подаваемого на его входы (эти входы называются адресными входами – A1, A0), активизирует один из своих выходов (Q3 – Q0). Другими словами, каждый из выходов дешифратора соответствует определенному двоичному коду (адресу). Следовательно, число адресных входов (n) и выходов (m) дешифратора связаны соотношением m = 2n. Кроме адресных входов дешифратор обычно снабжается одним или несколькими дополнительными входами, уровни сигналов на которых определяют рабочее состояние дешифратора. Эти входы называются управляющими (разрешающими) входами (EN).

Дешифратор можно использовать для реализации логических функций. Эту

возможность проиллюстрируем на приведенном в предыдущей работе примере. Анализируя

логическое выражение ![]() , описывающее логику работы устройства,

можно видеть, что конъюнкции, входящие в это выражение, соответствуют активируемым

выходам дешифратора. Отсюда следует, что для реализации этой функции достаточно

соединить соответствующие выходы дешифратора на входы пятивходового элемента OR. Это относится к случаю дешифратора с прямыми выходами.

Для реализации этой функции на основе дешифратора с инверсными выходами

необходимо преобразовать логическое выражение по правилу де Моргана. Полученное

в результате такого преобразования выражение

, описывающее логику работы устройства,

можно видеть, что конъюнкции, входящие в это выражение, соответствуют активируемым

выходам дешифратора. Отсюда следует, что для реализации этой функции достаточно

соединить соответствующие выходы дешифратора на входы пятивходового элемента OR. Это относится к случаю дешифратора с прямыми выходами.

Для реализации этой функции на основе дешифратора с инверсными выходами

необходимо преобразовать логическое выражение по правилу де Моргана. Полученное

в результате такого преобразования выражение ![]() показывает,

что в этом случае необходимо использовать элемент NAND

(рисунок 3.1). Таким же способом можно реализовать еще несколько функций на основе

одного и того же дешифратора.

показывает,

что в этом случае необходимо использовать элемент NAND

(рисунок 3.1). Таким же способом можно реализовать еще несколько функций на основе

одного и того же дешифратора.

Рисунок 3.1

Мультиплексор имеет следующие типы входов – управляющие, адресные и информационные входы. Мультиплексор – устройство, которое в зависимости от адреса выбирает один из входных информационных сигналов и отправляет его на свой выход. Следовательно, число адресных входов (n) и число информационных входов (m) мультиплексора связаны соотношением m = 2n. Мультиплексор зачастую используется в качестве переключателя, который передает цифровые сигналы по одной линии, в различные моменты времени, определяемые его управляющим двоичным кодом (адресом).

На основе мультиплексора можно создать универсальный логический модуль (УЛМ), с помощью которого можно реализовать весьма разнообразные функции. Проиллюстрируем различные методы настройки УЛМ на примерах реализаций функций двух, трех и четырех переменных на основе мультиплексора 4-1 (таблицы 3.1-3.3 и рисунки 3.2-3.4).

|

Т а б л и ц а 3.1

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

Рисунок 3.2 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Т а б л и ц а 3.2

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

Рисунок 3.3 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Т а б л и ц а 3.3

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

Рисунок 3.4 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

3.4.2 Порядок выполнения рабочего задания

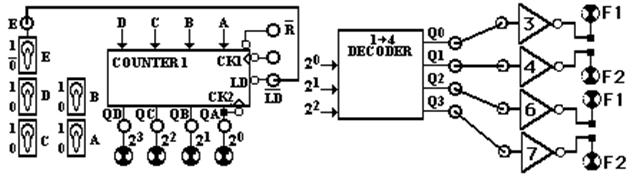

Практическая часть этой лабораторной работы выполняется на плате EB-134 (рисунок 3.5), на котором размещены исследуемые нами дешифратор и мультиплексор.

Рисунок 3.5

К п.3.2.1.1. Вставьте съемную плату EB-134 в лабораторный стенд и выполните соединения, необходимые для исследования работы дешифратора (рисунок 3.6). Счетчик 1 здесь используется в качестве регистра хранения с параллельной загрузкой и применяется для подачи на дешифратор адресного кода (22 à A1, 21 à A0) и управляющего сигнала (20 à EN). Эти соединения выполнены внутренне на самой плате. Для наблюдения за уровнями выходных сигналов дешифратора используются светодиоды, размещенные на плате EB-132. Для этого плато EB-132 необходимо разместить рядом с основным стендом и объединить с ним по питанию.

Рисунок 3.6

Двоичное число, загружаемое в счетчик,

устанавливается с помощью соответствующих переключателей и фиксируется сигналом

![]() , подаваемого

от переключателя Е.

, подаваемого

от переключателя Е.

Изменяя содержимое счетчика, тем самым и уровни входных сигналов (адресный код и управляющий сигнал), составьте таблицу истинности дешифратора (таблица 3.4).

Т а б л и ц а 3.4

|

E (20) |

A1 (22) |

A0 (21) |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

|

|

|

|

|

0 |

0 |

1 |

|

|

|

|

|

0 |

1 |

0 |

|

|

|

|

|

0 |

1 |

1 |

|

|

|

|

|

1 |

0 |

0 |

|

|

|

|

|

1 |

0 |

1 |

|

|

|

|

|

1 |

1 |

0 |

|

|

|

|

|

1 |

1 |

1 |

|

|

|

|

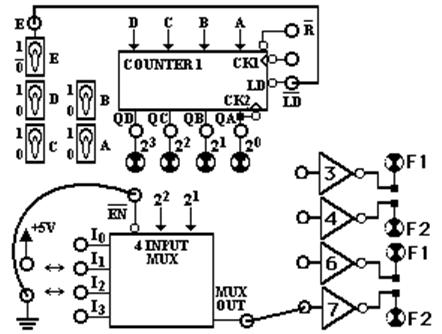

К п.3.2.1.2. Выполните соединения, необходимые для исследования режимов работы мультиплексора (рисунок 3.7). Счетчик 1 здесь используется для подачи на мультиплексор адресного кода (22 à A1, 21 à A0). Эти соединения выполнены внутренне на самой плате. Для активизации выхода мультиплексора, его разрешающий вход (EN) должен быть подключен к “общему проводу”.

Рисунок 3.7

Изменяя при каждом варианте адресного кода уровни сигнала на информационных входах мультиплексора, запишите результаты наблюдения за уровнем его выходного сигнала в таблицу 3.5.

Т а б л и ц а 3.5

|

A1 (22) |

A0 (21) |

OUT |

|

0 |

0 |

|

|

0 |

1 |

|

|

1 |

0 |

|

|

1 |

1 |

|

К п.3.2.2.1. Исследуйте работу дешифратора 74138 по схеме на рисунке 3.8). Здесь для подачи адресного кода дешифратора использован счетчик. Ввиду того, что это является вспомогательным средством, впрямую не относящимся к теме исследования, был использован условный счетчик, а не конкретная микросхема. Часть схемы, составленная с помощью элементов XOR и NOT, представляет собой устройство, которое формирует одиночный импульс на каждое нажатие клавиши. Его рекомендуется объединить в виде подсхемы (например, под названием “Pulse”) для использования в дальнейших экспериментах.

Рисунок 3.8

К п.3.2.2.2. Исследуйте работу мультиплексора 74153 с помощью логического анализатора (рисунок 3.9). Здесь счетчик 1 используется для подачи информационных сигналов, а счетчик 2 – для адресных кодов и разрешающего сигнала.

К пп. 3.2.2.3 и 3.2.2.4. Постройте схему одного из таблично заданных устройств (по предложенному преподавателем варианту из таблицы 3.6) на основе дешифратора 74138 и мультиплексора 74153. Проанализируйте их работу, дополнив схемы необходимыми для исследования элементами.

Эти задания разрешается выполнить в качестве самостоятельной работы во внеаудиторное время. Для этого необходимо изучить иллюстративные примеры из п. 3.4.1. Разработанные схемы и результаты их проверки необходимо включить в отчет.

Рисунок 3.9

Т а б л и ц а 3.6

|

A |

B |

C |

F1 |

F2 |

F3 |

F4 |

|

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

1 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

1 |

1 |

3.5 Вопросы

1. Объясните принципы работы дешифратора.

2. Создайте схему дешифратора на основе логических элементов с указанными преподавателем характеристиками.

3. Объясните режимы работы мультиплексора.

4. Создайте схему мультиплексора на основе логических элементов и дешифратора.

5. Объясните метод настройки УЛМ, когда число переменных реализуемой функции равно числу адресных входов мультиплексора.

6. Объясните методы настройки УЛМ, когда число переменных реализуемой функции больше числа адресных входов мультиплексора.

4 Лабораторная работа №4. Триггеры

4.1 Цель работы:

- освоение принципов построения и режимов работы асинхронных триггеров;

- освоение принципов построения и режимов работы синхронных триггеров со статическим управлением;

- освоение режимов работы синхронных триггеров с динамическим управлением.

4.2 Рабочее задание

4.2.1 Исследования на стенде Degem Systems

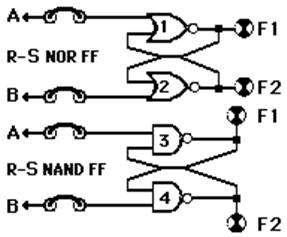

4.2.1.1 Исследовать режимы работы асинхронных RS-триггеров на элементах NOR и NAND.

4.2.1.2 Исследовать режимы работы D-триггера.

4.2.1.3 Исследовать режимы работы JK-триггера.

4.2.2 Исследования в системе моделирования Electronics Workbench

4.2.2.1 Построить схему синхронного RS-триггера на элементах NAND и исследовать режимы его работы.

4.2.2.2 Проанализировать режимы работы D-триггера.

4.2.2.3 Проанализировать работу D-триггера в счетном режиме.

4.2.2.4 Проанализировать режимы работы JK-триггера.

4.3 Оборудование рабочего места:

- лабораторный стенд PU-2000;

- съемная плата EB-133;

- соединительные провода и перемычки;

- компьютер с загруженной программной средой Electronics Workbench.

4.4 Методические указания к выполнению работы

4.4.1. Краткие сведения из теории и практические рекомендации

Триггеры являются устройствами, которые имеют два устойчивых состояния, и предназначенные для хранения одноразрядного двоичного числа. По принципу действия они подразделяются на асинхронные и синхронные. Синхронизация работы триггера может осуществляться уровнем или перепадом синхросигнала; соответственно различают триггеры со статическим и динамическим управлением.

4.4.2. Порядок выполнения рабочего задания

К п.4.2.1.1. Установите плату EB-133 на лабораторный стенд и выполните соединения входов асинхронных RS-триггеров на элементах NOR и NAND к переключателям уровней входных сигналов (рисунок 4.1). Исследуйте режимы работы этих триггеров, изменяя уровни входных сигналов в той последовательности, как приведено в таблице 4.1.

Рисунок 4.1

Т а б л и ц а 4.1

|

на элементах NOR |

на элементах NAND |

||||||||

|

A ( ) |

B ( ) |

F1 (Q) |

F2 (Q’) |

режим |

A ( ) |

B ( ) |

F1 (Q) |

F2 (Q’) |

режим |

|

1 |

0 |

|

|

|

0 |

1 |

|

|

|

|

0 |

|

|

|

1 |

|

|

|

|

|

|

1 |

|

|

|

|

0 |

|

|

|

|

|

0 |

|

|

|

|

1 |

|

|

|

|

|

1 |

1 |

|

|

|

0 |

0 |

|

|

|

|

0 |

0 |

|

|

|

1 |

1 |

|

|

|

|

1 |

1 |

|

|

|

0 |

0 |

|

|

|

|

0 |

0 |

|

|

|

1 |

1 |

|

|

|

Проанализировав полученные результаты, напишите соответствующие входным сигналам режимы работы исследованных триггеров и определите названия входов (R, S), отметив их в скобках, рядом с названиями переключателей. Режимы работы исследованных триггеров представьте в краткой табличной форме.

К п.4.2.1.2. Выполните соединения, необходимые для исследования D-триггера (рисунок 4.2).

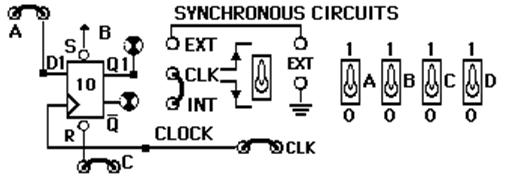

Рисунок 4.2

Устанавливая различные уровни на информационном входе D1 триггера с помощью переключателя А, изменяйте уровень сигнала на входе CLK. Обратите внимание на направление перепада сигнала на входе CLK, при котором происходит изменение состояния триггера, и отметьте его. Результаты наблюдения напишите в таблицу 4.2.

Т а б л и ц а 4.2

|

R |

S |

CLK |

A (D1) |

Q1 |

(Q1)’ |

режим |

|

|

|

|

0 |

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

1 |

|

|

|

Исследуйте влияние уровня сигнала на входах R и S на состояние триггера, с помощью соответствующих переключателей.

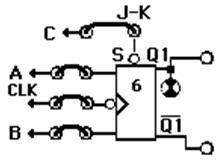

К п.4.2.1.3. Выполните соединения, необходимые для исследования JK-триггера (рисунок 4.3).

Рисунок 4.3

Устанавливая различные наборы сигналов на входах A и B, изменяйте уровень сигнала на входе CLK. Обратите внимание на направление перепада сигнала на входе CLK, при котором происходит изменение состояния триггера, и отметьте его. Результаты наблюдения напишите в таблицу 4.3.

Т а б л и ц а 4.3

|

CLK |

A ( ) |

B ( ) |

Q1 |

(Q1)’ |

режим |

|

|

0 |

0 |

|

|

|

|

0 |

1 |

|

|

|

|

|

1 |

0 |

|

|

|

|

|

1 |

1 |

|

|

|

Исследуйте влияние уровня сигнала на входе S на состояние триггера, с помощью соответствующего переключателя.

Проанализировав полученные результаты, напишите соответствующие входным сигналам режимы работы триггера и определите названия входов (J, K), отметив их в скобках, рядом с названиями переключателей.

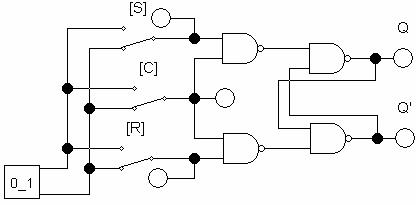

К п.4.2.2.1. Постройте схему синхронного RS-триггера на элементах NAND (рисунок 4.4) и исследуйте режимы его работы. Результаты исследования напишите в таблицу 4.4.

Рисунок 4.4

Т а б л и ц а 4.4

|

C |

S |

R |

Q |

Q’ |

C |

S |

R |

Q |

Q’ |

|

0 |

0 |

0 |

|

|

1 |

0 |

0 |

|

|

|

0 |

0 |

1 |

|

|

1 |

0 |

1 |

|

|

|

0 |

1 |

0 |

|

|

1 |

1 |

0 |

|

|

|

0 |

1 |

1 |

|

|

1 |

1 |

1 |

|

|

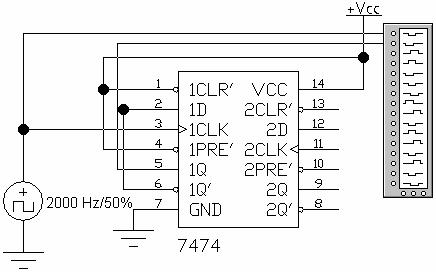

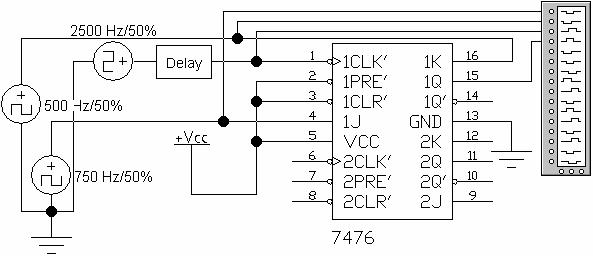

К п.4.2.2.2. Исследуйте режимы работы одного из D-триггеров в микросхеме 7474 (рисунок 4.5) с помощью логического анализатора.

Рисунок 4.5

В начале анализа переключатели R и S должны быть установлены в единичное состояние. В процессе анализа быстрым двойным нажатием одного из клавиш, соответствующих этим переключателям, осуществите установку и очистку триггера. Полученный с помощью анализатора результат скопируйте в отчет.

К п.4.2.2.3. Для того, чтобы использовать D-триггер в счетном режиме, его инверсный выход необходимо замкнуть на информационный вход (рисунок 4.6). Проанализируйте его работу и результат анализа скопируйте.

Рисунок 4.6

К п.4.2.2.4. Проанализируйте работу JK-триггера 7474 (рисунок 4.7) и результат анализа скопируйте.

Рисунок 4.7

4.5 Вопросы

1. Объясните структуру и режимы работы асинхронного RS-триггера с прямыми входами.

2. Объясните структуру и режимы работы асинхронного RS-триггера с инверсными входами.

3. Постройте схему асинхронного RS-триггера с прямыми входами на элементах NAND.

4. Объясните структуру и режимы работы синхронного RS-триггера со статическим управлением.

5. В чем состоит различие статического и динамического управления триггерами?

6. Как использовать D-триггер в качестве счетного триггера?

7. Как использовать JK-триггер в качестве счетного триггера?

8. Какие функции выполняют сигналы на входах R и S микросхем D- и JK-триггеров?

5 Лабораторная работа №5. Последовательностные устройства

5.1 Цель работы:

- освоение различных режимов ввода информации в регистры;

- освоение принципов работы и структурных различий суммирующих и вычитающих счетчиков;

- освоение структурных принципов изменения модуля счета счетчика;

- освоение структурных принципов построения кольцевого счетчика;

- ознакомление с принципом формирования синхросигналов.

5.2 Рабочее задание

5.2.1 Исследования на стенде Degem Systems

5.2.1.1 Исследовать режимы последовательного и параллельного вводов информации в регистры.

5.2.1.2 Исследовать работу асинхронных суммирующих и вычитающих счетчиков.

5.2.1.3 Исследовать работу формирователя импульсов.

5.2.1.4 Исследовать работу кольцевого счетчика.

5.2.2 Исследования в системе моделирования Electronics Workbench

5.2.2.1 Исследовать принципы работы двоичного счетчика и возможности структурного изменения модуля счета.

5.2.2.2 Исследовать режимы работы реверсивного счетчика.

5.2.2.3 Исследовать режимы работы универсального регистра.

5.3 Оборудование рабочего места:

- лабораторный стенд PU-2000;

- съемная плата EB-133;

- соединительные провода и перемычки;

- компьютер с загруженной программной средой Electronics Workbench.

5.4 Методические указания к выполнению работы

5.4.1 Краткие сведения из теории и практические рекомендации

Последовательностными устройствами называются устройства, выходные сигналы которых определяются комбинацией входных сигналов и их предыдущими состояниями, т.е. это – устройства с памятью. Типичными представителями последовательностных устройств являются регистры и счетчики.

Регистры – устройства для хранения многоразрядного слова. Регистры могут быть построены с помощью любых триггеров (например, D-триггеров). По способу ввода информации различают регистры с последовательным вводом (сдвиговый регистр) и с параллельным вводом. В первом случае многоразрядная информация подается на вход первого триггера разряд за разрядом, а на входы следующих триггеров информация поступает с выхода предыдущего триггера. Запись входных информаций в соответствующие триггеры осуществляется синхросигналом, подаваемым на все триггеры одновременно. Следовательно, последовательный ввод четырехразрядного слова в регистр осуществляется подачей четырех синхросигналов. Во втором случае каждый бит информации подается на вход соответствующего триггера и запись их осуществляется одним синхросигналом.

Во второй части лабораторного занятия предлагается исследовать режимы работы универсального регистра, который включает режимы параллельной загрузки, сдвига налево и направо, и разумеется, хранения.

Счетчики – устройства, предназначенные для подсчитывания числа поступающих на их вход импульсов. Изменение состояния счетчика осуществляется по фронту или по срезу импульсов. Счетчики могут быть построены с помощью счетных триггеров. Напоминаем, что для использования D-триггера в режиме счета его инверсный выход необходимо замкнуть на информационный вход, а счетный режим JK-триггеров обеспечивается единичными уровнями на его информационных входах.

В наборе микросхем программы EWb имеется двоичный счетчик 7493, который состоит из структурно разъединенных одноразрядного и трехразрядного счетчиков. Предлагается этот счетчик использовать в дальнейших экспериментах в качестве источника четырехразрядной двоичной информации, соответственно оформив его вместе с подсоединенным генератором в виде подсхемы.

Реверсивный счетчик 74169 может быть использован как суммирующий или вычитающий счетчик, он также обладает возможностью параллельной загрузки.

Еще одним представителем последовательностных устройств, предлагаемых к исследованию, являются формирователи синхросигналов, используемые в устройствах управления. Их основной функцией является формирование импульсов (синхросигналов) в определенной заранее заданной последовательности.

5.4.2 Порядок выполнения рабочего задания

К п.5.2.1.1. Установите плату EB-133 на лабораторный стенд и выполните соединения для исследования сдвигового регистра (рисунок 5.1). Установите переключатели B и C на “1”.

Установите переключатель A на “0” и подайте несколько синхроимпульсов, чтобы сбросить все четыре триггера.

Осуществите запись числа 1101, подавая на вход регистра значения битов, начиная со старшего разряда, и подавая синхросигнал после подачи каждого бита.

Рисунок 5.1

Для исследования порядка параллельного ввода информации в регистр подключите пять проводов к выводам A, B, C, D и CLK регистра, как показано на рисунке 5.2. Этим достигается соединение переключателей к соответствующим выводам регистра.

Рисунок 5.2

Установив с помощью переключателей A, B, C, D некоторый двоичный код на информационных входах регистра, зафиксируйте его сигналом от переключателя CLK. Обратите внимание на направление переключения переключателя CLK, при котором происходит запись информации в регистр.

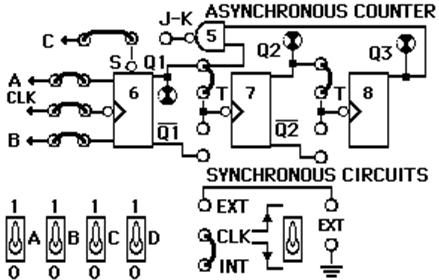

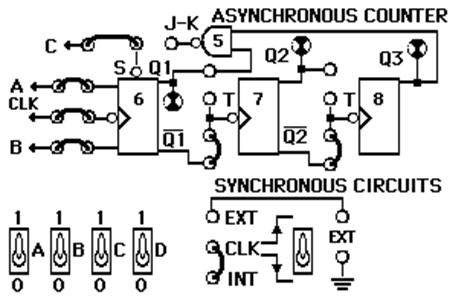

К п.5.2.1.2. Выполните соединения, обеспечивающие схему трехразрядного асинхронного суммирующего счетчика на JK-триггерах (рисунок 5.3). С помощью переключателей A, B и C установите входные сигналы первого триггера так, чтобы он находился в счетном режиме, т.е. установите A = B = C = 1.

Рисунок 5.3

Подавая сигналы синхронизации с помощью переключателя CLK, запишите состояния триггеров в таблицу 5.1. Обратите внимание на момент изменения сигнала CLK, при котором происходит изменение состояния триггеров, и отметьте это.

Т а б л и ц а 5.1

|

CLK |

Q3 |

Q2 |

Q1 |

|

CLK |

Q3 |

Q2 |

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Измените схему асинхронного счетчика, для того, чтобы остановить счет на заранее определенном значении (рисунок 5.4).

Рисунок 5.4

Подавая сигнал синхронизации с помощью переключателя CLK, запишите состояния триггеров в таблицу 5.2.

Т а б л и ц а 5.2

|

CLK |

Q3 |

Q2 |

Q1 |

|

CLK |

Q3 |

Q2 |

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

По полученным результатам сделайте вывод о характере работы данного счетчика.

Соберите схему трехразрядного асинхронного вычитающего счетчика на JK-триггерах (рисунок 5.5).

Рисунок 5.5

Изменяя сигнал синхронизации с помощью переключателя CLK, запишите состояния триггеров в таблицу 5.3.

Т а б л и ц а 5.3

|

CLK |

Q3 |

Q2 |

Q1 |

|

CLK |

Q3 |

Q2 |

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

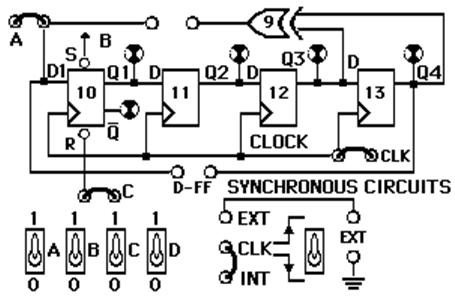

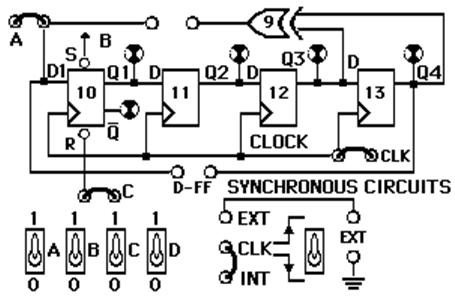

К п.5.2.1.3. Соберите схему, представленную на рисунке 5.6. Эта схема соответствует цепи синхронизации на D-триггерах, которая генерирует последовательность сигналов синхронизации из 15 различных состояний.

Рисунок 5.6

Установите переключатель A на “0”, а переключатели B и C на “1”. Подайте несколько синхроимпульсов, чтобы сбросить все 4 триггера.

Установите переключатель А на “1” и подайте один синхроимпульс, чтобы установить первый триггер на “1”. Отсоедините провод А и подключите его к выходу элемента 9. Эта цепь синхронно изменяет состояние выходов триггеров по сигналам синхронизации, прикладываемым к их входам CLK.

Используя переключатель CLK для изменения состояния на синхронизирующем входе, заполните таблицу состояний устройства (таблица 5.4).

Т а б л и ц а 5.4

|

№ |

Q4 |

Q3 |

Q2 |

Q1 |

|

№ |

Q4 |

Q3 |

Q2 |

Q1 |

|

1 |

|

|

|

|

|

12 |

|

|

|

|

|

2 |

|

|

|

|

|

13 |

|

|

|

|

|

3 |

|

|

|

|

|

14 |

|

|

|

|

|

4 |

|

|

|

|

|

15 |

|

|

|

|

|

5 |

|

|

|

|

|

16 |

|

|

|

|

|

6 |

|

|

|

|

|

17 |

|

|

|

|

|

7 |

|

|

|

|

|

18 |

|

|

|

|

|

8 |

|

|

|

|

|

19 |

|

|

|

|

|

9 |

|

|

|

|

|

20 |

|

|

|

|

|

10 |

|

|

|

|

|

21 |

|

|

|

|

|

11 |

|

|

|

|

|

22 |

|

|

|

|

По полученным данным постройте временные диаграммы работы устройства (рисунок 5.7). Просмотрев построенные временные диаграммы, обратите внимание, что выходные значения Q изменяются только на фронтах синхроимпульса (при возрастании).

Рисунок 5.7

К п.5.2.1.4. Для того, чтобы приступить к следующему эксперименту, возвратите схему в первоначальное состояние, изображенное на рисунке 5.6. Установите переключатель A на “0”, а переключатели B и C на “1”. Подайте несколько синхроимпульсов, чтобы сбросить все 4 триггера. Отсоедините провод от входа A и подключите провод обратной связи (между Q4 и входом D1), как показано на рисунке 5.8. Эта цепь пускает по кругу информационные импульсы, подаваемые на первый триггер, с каждым полученным импульсом синхронизации. Последний триггер передает сигнал на первый – отсюда название “кольцевой счетчик”.

Рисунок 5.8

На мгновение установите переключатель B на “0” и сразу обратно на “1”. Используя переключатель CLK для изменения состояния на синхронизирующем входе, заполните таблицу состояний устройства (таблица 5.5).

Т а б л и ц а 5.5

|

№ |

Q4 |

Q3 |

Q2 |

Q1 |

|

1 |

|

|

|

|

|

2 |

|

|

|

|

|

3 |

|

|

|

|

|

4 |

|

|

|

|

По полученным данным постройте временные диаграммы работы устройства (рисунок 5.9).

Рисунок 5.9

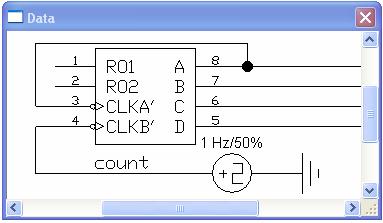

К п.5.2.2.1. Соберите схему по рисунку 5.10. Подавая тактовые сигналы с помощью клавиши С, исследуйте работу счетчика. Проверьте назначение сигналов на выводах R01 и R02 триггера.

Рисунок 5.10

Для использования в качестве источника данных в дальнейших экспериментах создайте подсхему “Data”, объединяющую счетчик с генератором с частотой 1 Hz (рисунок 5.11).

Рисунок 5.11

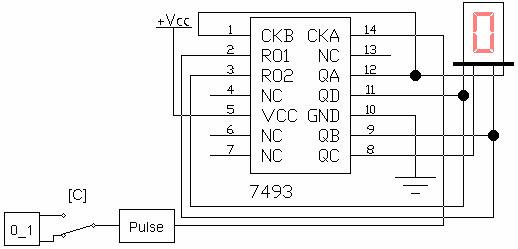

Проверьте модуль счета счетчика, представленного на рисунке 5.12.

Рисунок 5.12

К п.5.2.2.2. Соберите схему для исследования режимов работы реверсивного счетчика 74169 (рисунок 5.13). Проанализируйте режимы его работы.

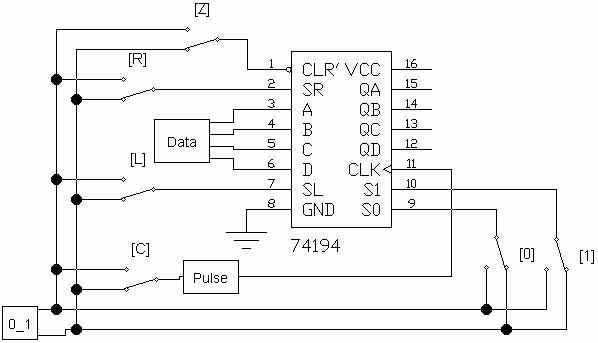

Рисунок 5.13

К п.5.2.2.2. Соберите схему для исследования режимов работы универсального регистра 74194 (рисунок 5.14). Проанализируйте режимы его работы.

Рисунок 5.14

5.5 Вопросы

1. Поясните принципы последовательного ввода информации в регистр.

2. Поясните принципы параллельного ввода информации в регистр.

3. Как можно получить счетчик с модулем счета 13?

4. Чем структурно различаются суммирующий и вычитающий счетчики?

5. Опишите принципы работы формирователя синхроимпульсов.

Список литературы

1. Угрюмов Е. П. Цифровая схемотехника. – СПб.: БХВ-Петербург, 2004.

2. Бойко В.И. и др. Схемотехника электронных устройств. Цифровые устройства. – СПб.: БХВ-Петербург, 2004.

3. Сугано Т. Дж., Уидмер Н. С. Цифровые системы. Теория и практика: Пер. с англ. – М.: Издательский дом “Вильямс”, 2004.

4. Опадчий Ю. Ф., Глудкин О. П., Гуров А. И. Аналоговая и цифровая электроника / Под ред. О.П. Глудкина. – М.: Радио и связь, 2003.

5. Токхейм Р. Основы цифровой электроники: Пер. с. англ. – М.: Мир, 1988.

6. Шанаев О.Т. Система моделирования Electronic Workbench / на казахском и русском языках. – Алматы, 2003.

СОДЕРЖАНИЕ

1 Лабораторная работа №1. Логические элементы

2 Лабораторная работа №2. Комбинационные устройства

3 Лабораторная работа №3. Дешифраторы и мультиплексоры

4 Лабораторная работа №4. Триггеры